# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f809-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Registers

| SFR | Definition 8.1 | . ADC0CF: ADC0 Configuration                               | . 50 |

|-----|----------------|------------------------------------------------------------|------|

| SFR | Definition 8.2 | . ADC0H: ADC0 Data Word MSB                                | . 51 |

| SFR | Definition 8.3 | . ADC0L: ADC0 Data Word LSB                                | . 51 |

| SFR | Definition 8.4 | . ADC0CN: ADC0 Control                                     | . 52 |

| SFR | Definition 8.5 | . ADC0GTH: ADC0 Greater-Than Data High Byte                | . 53 |

| SFR | Definition 8.6 | . ADC0GTL: ADC0 Greater-Than Data Low Byte                 | . 53 |

| SFR | Definition 8.7 | . ADC0LTH: ADC0 Less-Than Data High Byte                   | . 54 |

| SFR | Definition 8.8 | . ADC0LTL: ADC0 Less-Than Data Low Byte                    | . 54 |

|     |                | . ADC0MX: AMUX0 Channel Select                             |      |

| SFR | Definition 10. | 1. REF0CN: Voltage Reference Control                       | . 62 |

| SFR | Definition 11. | 1. REG0CN: Voltage Regulator Control                       | . 64 |

|     |                | 1. CPT0CN: Comparator0 Control                             |      |

|     |                | 2. CPT0MD: Comparator0 Mode Selection                      |      |

|     |                | 3. CPT0MX: Comparator0 MUX Selection                       |      |

| SFR | Definition 13. | 1. CS0CN: Capacitive Sense Control                         | . 75 |

|     |                | 2. CS0CF: Capacitive Sense Configuration                   |      |

|     |                | 3. CS0DH: Capacitive Sense Data High Byte                  |      |

|     |                | 4. CS0DL: Capacitive Sense Data Low Byte                   |      |

|     |                | 5. CS0SS: Capacitive Sense Auto-Scan Start Channel         |      |

|     |                | 6. CS0SE: Capacitive Sense Auto-Scan End Channel           |      |

|     |                | 7. CS0THH: Capacitive Sense Comparator Threshold High Byte |      |

|     |                | 8. CS0THL: Capacitive Sense Comparator Threshold Low Byte  |      |

|     |                | 9. CS0MX: Capacitive Sense Mux Channel Select              |      |

|     |                | 1. DPL: Data Pointer Low Byte                              |      |

|     |                | 2. DPH: Data Pointer High Byte                             |      |

|     |                | 3. SP: Stack Pointer                                       |      |

|     |                | 4. ACC: Accumulator                                        |      |

|     |                | 5. B: B Register                                           |      |

|     |                | 6. PSW: Program Status Word                                |      |

|     |                | 1. HWID: Hardware Identification Byte                      |      |

|     |                | 2. DERIVID: Derivative Identification Byte                 |      |

|     |                | 3. REVID: Hardware Revision Identification Byte            |      |

|     |                | 1. IE: Interrupt Enable                                    |      |

|     |                | 2. IP: Interrupt Priority                                  |      |

|     |                | 3. EIE1: Extended Interrupt Enable 1                       |      |

|     |                | 4. EIE2: Extended Interrupt Enable 2                       |      |

|     |                | 5. EIP1: Extended Interrupt Priority 1                     |      |

|     |                | 6. EIP2: Extended Interrupt Priority 2                     |      |

|     |                | 7. IT01CF: INT0/INT1 Configuration                         |      |

|     |                | 1. PSCTL: Program Store R/W Control                        |      |

|     |                | 2. FLKEY: Flash Lock and Key                               |      |

|     |                | 1. PCON: Power Control                                     |      |

| SFR | Definition 21. | 1. VDM0CN: VDD Monitor Control                             | 126  |

| SFR Definition 21.2. RSTSRC: Reset Source                        | . 128 |

|------------------------------------------------------------------|-------|

| SFR Definition 22.1. CLKSEL: Clock Select                        | . 130 |

| SFR Definition 22.2. OSCICL: Internal H-F Oscillator Calibration | . 131 |

| SFR Definition 22.3. OSCICN: Internal H-F Oscillator Control     | . 132 |

| SFR Definition 22.4. OSCXCN: External Oscillator Control         | . 134 |

| SFR Definition 23.1. XBR0: Port I/O Crossbar Register 0          | . 148 |

| SFR Definition 23.2. XBR1: Port I/O Crossbar Register 1          | . 149 |

| SFR Definition 23.3. P0MASK: Port 0 Mask Register                | . 151 |

| SFR Definition 23.4. P0MAT: Port 0 Match Register                | . 151 |

| SFR Definition 23.5. P1MASK: Port 1 Mask Register                | . 152 |

| SFR Definition 23.6. P1MAT: Port 1 Match Register                |       |

| SFR Definition 23.7. P0: Port 0                                  | . 153 |

| SFR Definition 23.8. P0MDIN: Port 0 Input Mode                   | . 154 |

| SFR Definition 23.9. P0MDOUT: Port 0 Output Mode                 | . 154 |

| SFR Definition 23.10. P0SKIP: Port 0 Skip                        | . 155 |

| SFR Definition 23.11. P1: Port 1                                 |       |

| SFR Definition 23.12. P1MDIN: Port 1 Input Mode                  | . 156 |

| SFR Definition 23.13. P1MDOUT: Port 1 Output Mode                | . 156 |

| SFR Definition 23.14. P1SKIP: Port 1 Skip                        | . 157 |

| SFR Definition 23.15. P2: Port 2                                 |       |

| SFR Definition 23.16. P2MDOUT: Port 2 Output Mode                | . 158 |

| SFR Definition 24.1. CRC0CN: CRC0 Control                        |       |

| SFR Definition 24.2. CRC0IN: CRC Data Input                      | . 164 |

| SFR Definition 24.3. CRC0DATA: CRC Data Output                   | . 164 |

| SFR Definition 24.4. CRC0AUTO: CRC Automatic Control             | . 165 |

| SFR Definition 24.5. CRC0CNT: CRC Automatic Flash Sector Count   | . 165 |

| SFR Definition 24.6. CRC0FLIP: CRC Bit Flip                      | . 166 |

| SFR Definition 25.1. SPI0CFG: SPI0 Configuration                 |       |

| SFR Definition 25.2. SPI0CN: SPI0 Control                        |       |

| SFR Definition 25.3. SPI0CKR: SPI0 Clock Rate                    | . 176 |

| SFR Definition 25.4. SPI0DAT: SPI0 Data                          | . 176 |

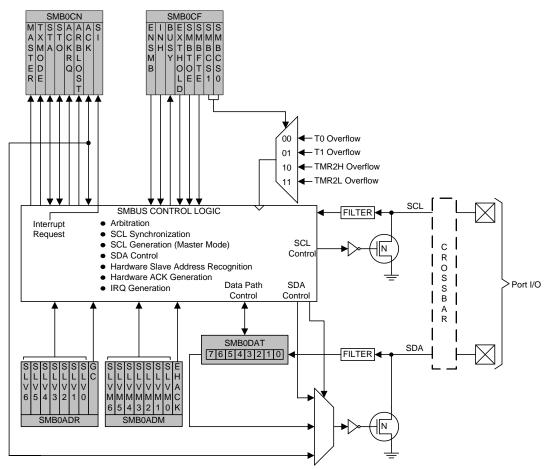

| SFR Definition 26.1. SMB0CF: SMBus Clock/Configuration           | . 186 |

| SFR Definition 26.2. SMB0CN: SMBus Control                       |       |

| SFR Definition 26.3. SMB0ADR: SMBus Slave Address                | . 191 |

| SFR Definition 26.4. SMB0ADM: SMBus Slave Address Mask           | . 191 |

| SFR Definition 26.5. SMB0DAT: SMBus Data                         | . 192 |

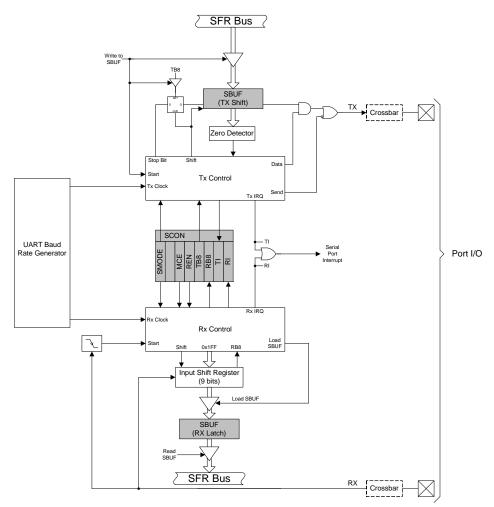

| SFR Definition 27.1. SCON0: Serial Port 0 Control                | . 206 |

| SFR Definition 27.2. SBUF0: Serial (UART0) Port Data Buffer      | . 207 |

| SFR Definition 28.1. CKCON: Clock Control                        |       |

| SFR Definition 28.2. TCON: Timer Control                         | . 215 |

| SFR Definition 28.3. TMOD: Timer Mode                            | . 216 |

| SFR Definition 28.4. TL0: Timer 0 Low Byte                       |       |

| SFR Definition 28.5. TL1: Timer 1 Low Byte                       |       |

| SFR Definition 28.6. TH0: Timer 0 High Byte                      |       |

| SFR Definition 28.7. TH1: Timer 1 High Byte                      |       |

| <b>č</b> ,                                                       |       |

### **Table 7.6. Flash Electrical Characteristics**

| Parameter                                          | Conditions                            | Min   | Тур   | Max | Units  |

|----------------------------------------------------|---------------------------------------|-------|-------|-----|--------|

| Flash Size (Note 1)                                | C8051F80x and C8051F810/1             |       | 16384 |     | bytes  |

|                                                    | C8051F812/3/4/5/6/7/8/9 and C8051F82x |       | 8192  |     | bytes  |

|                                                    | C8051F830/1/2/3/4/5                   |       | 4096  |     | bytes  |

| Endurance (Erase/Write)                            |                                       | 10000 |       |     | cycles |

| Erase Cycle Time                                   | 25 MHz Clock                          | 15    | 20    | 26  | ms     |

| Write Cycle Time                                   | 25 MHz Clock                          | 15    | 20    | 26  | μs     |

| Clock Speed during Flash<br>Write/Erase Operations |                                       | 1     | —     | —   | MHz    |

| Note: Includes Security Lock By                    | rte.                                  | •     | •     | •   | •      |

## Table 7.7. Internal High-Frequency Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                 | Conditions                                                       | Min | Тур  | Max | Units |

|---------------------------|------------------------------------------------------------------|-----|------|-----|-------|

| Oscillator Frequency      | IFCN = 11b                                                       | 24  | 24.5 | 25  | MHz   |

| Oscillator Supply Current | 25 °C, V <sub>DD</sub> = 3.0 V,<br>OSCICN.7 = 1,<br>OCSICN.5 = 0 |     | 350  | 650 | μA    |

### Table 7.8. Capacitive Sense Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified.

| Parameter                       | Conditions                                     | Min | Тур | Max | Units |

|---------------------------------|------------------------------------------------|-----|-----|-----|-------|

| Conversion Time                 | Single Conversion                              | 26  | 38  | 50  | μs    |

| Capacitance per Code            |                                                |     | 1   |     | fF    |

| External Capacitive Load        |                                                | —   | _   | 45  | pF    |

| Quantization Noise <sup>1</sup> | RMS                                            |     | 3   |     | fF    |

|                                 | Peak-to-Peak                                   | —   | 20  | —   | fF    |

| Supply Current                  | CS module bias current, 25 °C                  |     | 40  | 60  | μA    |

|                                 | CS module alone, maximum code<br>output, 25 °C | —   | 75  | 105 | μA    |

|                                 | Wake-on-CS Threshold <sup>2</sup> , 25 °C      | —   | 150 | 165 | μA    |

Notes:

1. RMS Noise is equivalent to one standard deviation. Peak-to-peak noise encompasses ±3.3 standard deviations.

2. Includes only current from regulator, CS module, and MCU in suspend mode.

| Mnemonic                    | Description                                | Bytes | Clock<br>Cycles |  |

|-----------------------------|--------------------------------------------|-------|-----------------|--|

| XRL direct, #data           | Exclusive-OR immediate to direct byte      | 3     | 3               |  |

| CLR A                       | Clear A                                    | 1     | 1               |  |

| CPL A                       | Complement A                               | 1     | 1               |  |

| RL A                        | Rotate A left                              | 1     | 1               |  |

| RLC A                       | Rotate A left through Carry                | 1     | 1               |  |

| RR A                        | Rotate A right                             | 1     | 1               |  |

| RRC A                       | Rotate A right through Carry               | 1     | 1               |  |

| SWAP A                      | Swap nibbles of A                          | 1     | 1               |  |

| Data Transfer               | -                                          | L.    | 1               |  |

| MOV A, Rn                   | Move Register to A                         | 1     | 1               |  |

| MOV A, direct               | Move direct byte to A                      | 2     | 2               |  |

| MOV A, @Ri                  | Move indirect RAM to A                     | 1     | 2               |  |

| MOV A, #data                | Move immediate to A                        | 2     | 2               |  |

| MOV Rn, A                   | Move A to Register                         | 1     | 1               |  |

| MOV Rn, direct              | Move direct byte to Register               | 2     | 2               |  |

| MOV Rn, #data               | Move immediate to Register                 | 2     | 2               |  |

| MOV direct, A               | Move A to direct byte                      | 2     | 2               |  |

| MOV direct, Rn              | Move Register to direct byte               | 2     | 2               |  |

| MOV direct, direct          | Move direct byte to direct byte            | 3     | 3               |  |

| MOV direct, @Ri             | Move indirect RAM to direct byte           | 2     | 2               |  |

| MOV direct, #data           | Move immediate to direct byte              | 3     | 3               |  |

| MOV @Ri, A                  | Move A to indirect RAM                     | 1     | 2               |  |

| MOV @Ri, direct             | Move direct byte to indirect RAM           | 2     | 2               |  |

| MOV @Ri, #data              | Move immediate to indirect RAM             | 2     | 2               |  |

| MOV DPTR, #data16           | Load DPTR with 16-bit constant             | 3     | 3               |  |

| MOVC A, @A+DPTR             | Move code byte relative DPTR to A          | 1     | 3               |  |

| MOVC A, @A+PC               | Move code byte relative PC to A            | 1     | 3               |  |

| MOVX A, @Ri                 | Move external data (8-bit address) to A    | 1     | 3               |  |

| MOVX @Ri, A                 | Move A to external data (8-bit address)    | 1     | 3               |  |

| MOVX A, @DPTR               | Move external data (16-bit address) to A   | 1     | 3               |  |

| MOVX @DPTR, A               | Move A to external data (16-bit address)   | 1     | 3               |  |

| PUSH direct                 | Push direct byte onto stack                | 2     | 2               |  |

| POP direct                  | Pop direct byte from stack                 | 2     | 2               |  |

| XCH A, Rn                   | Exchange Register with A                   | 1     | 1               |  |

| XCH A, direct               | Exchange direct byte with A                | 2     | 2               |  |

| XCH A, @Ri                  | Exchange indirect RAM with A               | 1     | 2               |  |

| XCHD A, @Ri                 | Exchange low nibble of indirect RAM with A | 1     | 2               |  |

| <b>Boolean Manipulation</b> | -                                          | L.    | 1               |  |

| CLR C                       | Clear Carry                                | 1     | 1               |  |

| CLR bit                     | Clear direct bit                           | 2     | 2               |  |

| SETB C                      | Set Carry                                  | 1     | 1               |  |

| SETB bit                    | Set direct bit                             | 2     | 2               |  |

| CPL C                       | Complement Carry                           | 1     | 1               |  |

| CPL bit                     | Complement direct bit                      | 2     | 2               |  |

Table 14.1. CIP-51 Instruction Set Summary (Continued)

# SFR Definition 14.5. B: B Register

| -     |                                     | -           |   |   |          |   |   |   |  |  |  |  |  |

|-------|-------------------------------------|-------------|---|---|----------|---|---|---|--|--|--|--|--|

| Bit   | 7                                   | 6           | 5 | 4 | 3        | 2 | 1 | 0 |  |  |  |  |  |

| Nam   | e                                   | B[7:0]      |   |   |          |   |   |   |  |  |  |  |  |

| Туре  | •                                   | R/W         |   |   |          |   |   |   |  |  |  |  |  |

| Rese  | et 0                                | 0           | 0 | 0 | 0        | 0 | 0 | 0 |  |  |  |  |  |

| SFR A | SFR Address = 0xF0; Bit-Addressable |             |   |   |          |   |   |   |  |  |  |  |  |

| Bit   | Name                                |             |   |   | Function |   |   |   |  |  |  |  |  |

| 7:0   | B[7:0]                              | B Register. |   |   |          |   |   |   |  |  |  |  |  |

| This register serves as a second accumulator for certain arithmetic operations. |

|---------------------------------------------------------------------------------|

| I This redister serves as a second accumulator for certain animmetic operations |

|                                                                                 |

whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 15.1 illustrates the data memory organization of the C8051F80x-83x.

### 15.2.1.1. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 14.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

### 15.2.1.2. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

#### MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 15.2.1.3. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

# SFR Definition 18.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

## SFR Address = 0xA8; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | Enable Serial Peripheral Interface (SPI0) Interrupt.<br>This bit sets the masking of the SPI0 interrupts.<br>0: Disable all SPI0 interrupts.<br>1: Enable interrupt requests generated by SPI0.                                                                       |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | Enable Timer 1 Interrupt.<br>This bit sets the masking of the Timer 1 interrupt.<br>0: Disable all Timer 1 interrupt.<br>1: Enable interrupt requests generated by the TF1 flag.                                                                                      |

| 2   | EX1   | Enable External Interrupt 1.<br>This bit sets the masking of External Interrupt 1.<br>0: Disable external interrupt 1.<br>1: Enable interrupt requests generated by the INT1 input.                                                                                   |

| 1   | ET0   | Enable Timer 0 Interrupt.<br>This bit sets the masking of the Timer 0 interrupt.<br>0: Disable all Timer 0 interrupt.<br>1: Enable interrupt requests generated by the TF0 flag.                                                                                      |

| 0   | EX0   | Enable External Interrupt 0.<br>This bit sets the masking of External Interrupt 0.<br>0: Disable external interrupt 0.<br>1: Enable interrupt requests generated by the INTO input.                                                                                   |

## 21.1. Power-On Reset

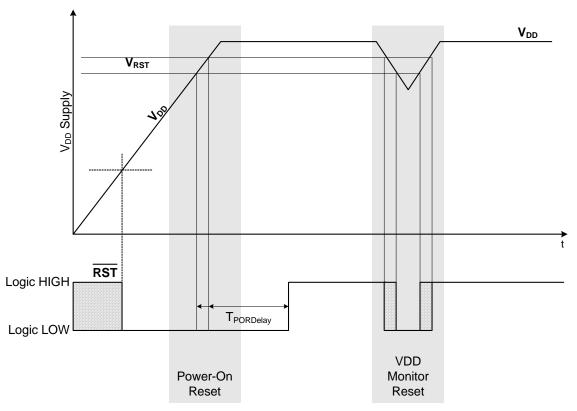

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. A delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 21.2. plots the power-on and V<sub>DD</sub> monitor reset timing. The maximum V<sub>DD</sub> ramp time is 1 ms; slower ramp times may cause the device to be released from reset before V<sub>DD</sub> reaches the V<sub>RST</sub> level. For ramp times less than 1 ms, the power-on reset delay (T<sub>PORDelay</sub>) is typically less than 10 ms.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is enabled and selected as a reset source following a power-on reset.

Figure 21.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

| Special<br>Function<br>Signals<br>(Control<br>Signals)<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK) | P0.0 Skipped    | AGND AGND    | P0.2 Skipped XTAL1 N | P0.3 Skipped |               | 5            | CNVSTR 9    | 7          |      |      | 2   | 3   | 4 <sup>1</sup> | 5 <sup>1</sup> | 6 <sup>1</sup> | <b>7</b> <sup>1</sup> | Signal Unavailable to Crossbar |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|----------------------|--------------|---------------|--------------|-------------|------------|------|------|-----|-----|----------------|----------------|----------------|-----------------------|--------------------------------|--|

| Function<br>SignalsTX0RX0RX0SCKMISOMOSINSS2SDASCLCP0ACP0ASYSCLKCEX0CEX1CEX2ECIT1Pin Skip<br>SettingsIn this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Skipped         | AGND         |                      | Skipped      |               |              | CNVSTR      |            |      |      |     |     |                |                |                |                       | Crossbar                       |  |

| RX0<br>SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0 Skipped    |              | P0.2 Skipped         | P0.3 Skipped |               |              |             |            |      |      |     |     |                |                |                |                       | Crossbar                       |  |

| SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P0.0 Skipped    |              | P0.2 Skipped         | P0.3 Skipped |               |              |             |            |      |      |     |     |                |                |                |                       | Crossbar                       |  |

| MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped    |              | P0.2 Skipped         | P0.3 Skipped |               |              |             |            |      |      |     |     |                |                |                |                       | Crossbar                       |  |

| MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skipped    |              | P0.2 Skipped         | P0.3 Skipped |               |              |             |            |      |      |     |     |                |                |                |                       | Crossbar                       |  |

| NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped    |              | P0.2 Skipped         | P0.3 Skipped |               |              |             |            |      |      |     |     |                |                |                |                       | Crossl                         |  |

| SDA<br>SCL<br>CP00<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P0.0 Skipped    |              | P0.2 Skipped         | P0.3 Skipped |               |              |             |            |      |      |     |     |                |                |                |                       | ō                              |  |

| SCL<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P0.0 Skipped    |              | P0.2 Skipped         | P0.3 Skipped |               |              |             |            |      |      |     |     |                |                |                |                       |                                |  |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skippe     |              | P0.2 Skippe          | P0.3 Skippe  |               |              |             |            |      |      |     |     |                |                |                |                       | e to                           |  |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Ski        |              | P0.2 Ski             | P0.3 Ski     |               |              |             |            |      |      |     |     |                |                |                |                       | able                           |  |

| CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0            |              | P0.2                 | P0.3         |               |              |             |            |      |      |     |     |                |                |                |                       | vail                           |  |

| CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ط<br> <br> <br> |              | ₫.                   | ۹.           |               |              |             |            |      |      |     |     |                |                |                |                       | Jna                            |  |

| CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |              |                      |              |               |              |             |            |      |      |     |     |                |                |                |                       | al                             |  |