# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                             |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f810-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Registers

| SFR | Definition 8.1 | . ADC0CF: ADC0 Configuration                               | . 50 |

|-----|----------------|------------------------------------------------------------|------|

| SFR | Definition 8.2 | . ADC0H: ADC0 Data Word MSB                                | . 51 |

| SFR | Definition 8.3 | . ADC0L: ADC0 Data Word LSB                                | . 51 |

| SFR | Definition 8.4 | . ADC0CN: ADC0 Control                                     | . 52 |

| SFR | Definition 8.5 | . ADC0GTH: ADC0 Greater-Than Data High Byte                | . 53 |

| SFR | Definition 8.6 | . ADC0GTL: ADC0 Greater-Than Data Low Byte                 | . 53 |

| SFR | Definition 8.7 | . ADC0LTH: ADC0 Less-Than Data High Byte                   | . 54 |

| SFR | Definition 8.8 | . ADC0LTL: ADC0 Less-Than Data Low Byte                    | . 54 |

|     |                | . ADC0MX: AMUX0 Channel Select                             |      |

| SFR | Definition 10. | 1. REF0CN: Voltage Reference Control                       | . 62 |

| SFR | Definition 11. | 1. REG0CN: Voltage Regulator Control                       | . 64 |

|     |                | 1. CPT0CN: Comparator0 Control                             |      |

|     |                | 2. CPT0MD: Comparator0 Mode Selection                      |      |

|     |                | 3. CPT0MX: Comparator0 MUX Selection                       |      |

| SFR | Definition 13. | 1. CS0CN: Capacitive Sense Control                         | . 75 |

|     |                | 2. CS0CF: Capacitive Sense Configuration                   |      |

|     |                | 3. CS0DH: Capacitive Sense Data High Byte                  |      |

|     |                | 4. CS0DL: Capacitive Sense Data Low Byte                   |      |

|     |                | 5. CS0SS: Capacitive Sense Auto-Scan Start Channel         |      |

|     |                | 6. CS0SE: Capacitive Sense Auto-Scan End Channel           |      |

|     |                | 7. CS0THH: Capacitive Sense Comparator Threshold High Byte |      |

|     |                | 8. CS0THL: Capacitive Sense Comparator Threshold Low Byte  |      |

|     |                | 9. CS0MX: Capacitive Sense Mux Channel Select              |      |

|     |                | 1. DPL: Data Pointer Low Byte                              |      |

|     |                | 2. DPH: Data Pointer High Byte                             |      |

|     |                | 3. SP: Stack Pointer                                       |      |

|     |                | 4. ACC: Accumulator                                        |      |

|     |                | 5. B: B Register                                           |      |

|     |                | 6. PSW: Program Status Word                                |      |

|     |                | 1. HWID: Hardware Identification Byte                      |      |

|     |                | 2. DERIVID: Derivative Identification Byte                 |      |

|     |                | 3. REVID: Hardware Revision Identification Byte            |      |

|     |                | 1. IE: Interrupt Enable                                    |      |

|     |                | 2. IP: Interrupt Priority                                  |      |

|     |                | 3. EIE1: Extended Interrupt Enable 1                       |      |

|     |                | 4. EIE2: Extended Interrupt Enable 2                       |      |

|     |                | 5. EIP1: Extended Interrupt Priority 1                     |      |

|     |                | 6. EIP2: Extended Interrupt Priority 2                     |      |

|     |                | 7. IT01CF: INT0/INT1 Configuration                         |      |

|     |                | 1. PSCTL: Program Store R/W Control                        |      |

|     |                | 2. FLKEY: Flash Lock and Key                               |      |

|     |                | 1. PCON: Power Control                                     |      |

| SFR | Definition 21. | 1. VDM0CN: VDD Monitor Control                             | 126  |

| SFR Definition 21.2. RSTSRC: Reset Source                        | . 128 |

|------------------------------------------------------------------|-------|

| SFR Definition 22.1. CLKSEL: Clock Select                        | . 130 |

| SFR Definition 22.2. OSCICL: Internal H-F Oscillator Calibration | . 131 |

| SFR Definition 22.3. OSCICN: Internal H-F Oscillator Control     | . 132 |

| SFR Definition 22.4. OSCXCN: External Oscillator Control         | . 134 |

| SFR Definition 23.1. XBR0: Port I/O Crossbar Register 0          | . 148 |

| SFR Definition 23.2. XBR1: Port I/O Crossbar Register 1          | . 149 |

| SFR Definition 23.3. P0MASK: Port 0 Mask Register                | . 151 |

| SFR Definition 23.4. P0MAT: Port 0 Match Register                | . 151 |

| SFR Definition 23.5. P1MASK: Port 1 Mask Register                | . 152 |

| SFR Definition 23.6. P1MAT: Port 1 Match Register                |       |

| SFR Definition 23.7. P0: Port 0                                  | . 153 |

| SFR Definition 23.8. P0MDIN: Port 0 Input Mode                   | . 154 |

| SFR Definition 23.9. P0MDOUT: Port 0 Output Mode                 | . 154 |

| SFR Definition 23.10. P0SKIP: Port 0 Skip                        | . 155 |

| SFR Definition 23.11. P1: Port 1                                 |       |

| SFR Definition 23.12. P1MDIN: Port 1 Input Mode                  | . 156 |

| SFR Definition 23.13. P1MDOUT: Port 1 Output Mode                | . 156 |

| SFR Definition 23.14. P1SKIP: Port 1 Skip                        | . 157 |

| SFR Definition 23.15. P2: Port 2                                 |       |

| SFR Definition 23.16. P2MDOUT: Port 2 Output Mode                | . 158 |

| SFR Definition 24.1. CRC0CN: CRC0 Control                        |       |

| SFR Definition 24.2. CRC0IN: CRC Data Input                      | . 164 |

| SFR Definition 24.3. CRC0DATA: CRC Data Output                   | . 164 |

| SFR Definition 24.4. CRC0AUTO: CRC Automatic Control             | . 165 |

| SFR Definition 24.5. CRC0CNT: CRC Automatic Flash Sector Count   | . 165 |

| SFR Definition 24.6. CRC0FLIP: CRC Bit Flip                      | . 166 |

| SFR Definition 25.1. SPI0CFG: SPI0 Configuration                 |       |

| SFR Definition 25.2. SPI0CN: SPI0 Control                        |       |

| SFR Definition 25.3. SPI0CKR: SPI0 Clock Rate                    | . 176 |

| SFR Definition 25.4. SPI0DAT: SPI0 Data                          | . 176 |

| SFR Definition 26.1. SMB0CF: SMBus Clock/Configuration           | . 186 |

| SFR Definition 26.2. SMB0CN: SMBus Control                       |       |

| SFR Definition 26.3. SMB0ADR: SMBus Slave Address                | . 191 |

| SFR Definition 26.4. SMB0ADM: SMBus Slave Address Mask           | . 191 |

| SFR Definition 26.5. SMB0DAT: SMBus Data                         | . 192 |

| SFR Definition 27.1. SCON0: Serial Port 0 Control                | . 206 |

| SFR Definition 27.2. SBUF0: Serial (UART0) Port Data Buffer      | . 207 |

| SFR Definition 28.1. CKCON: Clock Control                        |       |

| SFR Definition 28.2. TCON: Timer Control                         | . 215 |

| SFR Definition 28.3. TMOD: Timer Mode                            | . 216 |

| SFR Definition 28.4. TL0: Timer 0 Low Byte                       |       |

| SFR Definition 28.5. TL1: Timer 1 Low Byte                       |       |

| SFR Definition 28.6. TH0: Timer 0 High Byte                      |       |

| SFR Definition 28.7. TH1: Timer 1 High Byte                      |       |

| <b>č</b> ,                                                       |       |

## 7. Electrical Characteristics

### 7.1. Absolute Maximum Specifications

#### Table 7.1. Absolute Maximum Ratings

| Parameter                                                           | Conditions | Min  | Тур | Max | Units |

|---------------------------------------------------------------------|------------|------|-----|-----|-------|

| Ambient temperature under bias                                      |            | -55  |     | 125 | °C    |

| Storage Temperature                                                 |            | -65  | _   | 150 | °C    |

| Voltage on $\overline{RST}$ or any Port I/O Pin with respect to GND |            | -0.3 | _   | 5.8 | V     |

| Voltage on V <sub>DD</sub> with respect to GND                      |            | -0.3 |     | 4.2 | V     |

| Maximum Total current through V <sub>DD</sub><br>and GND            |            |      | _   | 500 | mA    |

| Maximum output current sunk by RST or any Port pin                  |            | —    | _   | 100 | mA    |

| <b>Note:</b> Stresses above those listed under "A                   | <b>.</b> . |      |     | •   |       |

This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **10.1. External Voltage References**

To use an external voltage reference, REFSL[1:0] should be set to 00. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference.

#### **10.2.** Internal Voltage Reference Options

A 1.65 V high-speed reference is included on-chip. The high speed internal reference is selected by setting REFSL[1:0] to 11. When selected, the high speed internal reference will be automatically enabled on an as-needed basis by ADC0.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide ADC0 with added dynamic range at the cost of reduced power supply noise rejection. To use the 1.8 to 3.6 V power supply voltage ( $V_{DD}$ ) or the 1.8 V regulated digital supply voltage as the reference source, REFSL[1:0] should be set to 01 or 10, respectively.

#### 10.3. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for ADC0 is taken from the P0.1/AGND pin. Any external sensors sampled by ADC0 should be referenced to the P0.1/AGND pin. The separate analog ground reference option is enabled by setting REFGND to 1. Note that when using this option, P0.1/AGND must be connected to the same potential as GND.

#### 10.4. Temperature Sensor Enable

The TEMPE bit in register REF0CN enables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

### SFR Definition 10.1. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4     | 3   | 2     | 1     | 0 |

|-------|---|---|--------|-------|-----|-------|-------|---|

| Name  |   |   | REFGND | REFSL |     | TEMPE | BIASE |   |

| Туре  | R | R | R/W    | R/W   | R/W | R/W   | R/W   | R |

| Reset | 0 | 0 | 0      | 1     | 0   | 0     | 0     | 0 |

SFR Address = 0xD1

| Bit | Name   | Function                                                                            |

|-----|--------|-------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                     |

| 5   | REFGND | Analog Ground Reference.                                                            |

|     |        | Selects the ADC0 ground reference.                                                  |

|     |        | 0: The ADC0 ground reference is the GND pin.                                        |

|     |        | 1: The ADC0 ground reference is the P0.1/AGND pin.                                  |

| 4:3 | REFSL  | Voltage Reference Select.                                                           |

|     |        | Selects the ADC0 voltage reference.                                                 |

|     |        | 00: The ADC0 voltage reference is the P0.0/VREF pin.                                |

|     |        | 01: The ADC0 voltage reference is the VDD pin.                                      |

|     |        | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.        |

|     |        | 11: The ADC0 voltage reference is the internal 1.65 V high speed voltage reference. |

| 2   | TEMPE  | Temperature Sensor Enable.                                                          |

|     |        | Enables/Disables the internal temperature sensor.                                   |

|     |        | 0: Temperature Sensor Disabled.                                                     |

|     |        | 1: Temperature Sensor Enabled.                                                      |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                          |

|     |        | 0: Internal Bias Generator off.                                                     |

|     |        | 1: Internal Bias Generator on.                                                      |

| 0   | Unused | Read = 0b; Write = Don't Care.                                                      |

## SFR Definition 11.1. REG0CN: Voltage Regulator Control

| Bit   | 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|-----|-----|-----|-----|-----|-----|-----|

| Name  | STOPCF |     |     |     |     |     |     |     |

| Туре  | R/W    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOPCF   | Stop Mode Configuration.                                                                                                                                                                                                                                                            |

|     |          | This bit configures the regulator's behavior when the device enters STOP mode.<br>0: Regulator is still active in STOP mode. Any enabled reset source will reset the<br>device.<br>1: Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset<br>the device. |

| 6:0 | Reserved | Must write to 000000b.                                                                                                                                                                                                                                                              |

## SFR Definition 12.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/W         |   |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

SFR Address = 0x9B

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0–.                                                    |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

#### 14.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should always be written to the value indicated in the SFR description. Future product versions may use these bits to implement new features in which case the reset value of the bit will be the indicated value, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

#### SFR Definition 14.1. DPL: Data Pointer Low Byte

| Bit           | 7             | 6           | 5                 | 4             | 3           | 2   | 1 | 0 |  |  |

|---------------|---------------|-------------|-------------------|---------------|-------------|-----|---|---|--|--|

| Name DPL[7:0] |               |             |                   |               |             |     |   |   |  |  |

| Type R/W      |               |             |                   |               |             |     |   |   |  |  |

| Rese          | et O          | 0           | 0                 | 0             | 0           | 0   | 0 | 0 |  |  |

| SFR A         | Address = 0x8 | 2           |                   |               |             |     |   |   |  |  |

| Bit           | Name          | Function    |                   |               |             |     |   |   |  |  |

| 7:0           | DPL[7:0]      | Data Pointe | Data Pointer Low. |               |             |     |   |   |  |  |

|               |               | The DPL reg | gister is the lo  | ow byte of th | e 16-bit DP | TR. |   |   |  |  |

#### SFR Definition 14.2. DPH: Data Pointer High Byte

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|----------|---|---|---|---|---|---|---|--|--|

| Name  | DPH[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W      |   |   |   |   |   |   |   |  |  |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0x83

| Bit | Name     | Function                                              |

|-----|----------|-------------------------------------------------------|

| 7:0 | DPH[7:0] | Data Pointer High.                                    |

|     |          | The DPH register is the high byte of the 16-bit DPTR. |

8. Restore previous interrupt state.

Steps 4–6 must be repeated for each 512-byte page to be erased.

**Note:** Flash security settings may prevent erasure of some Flash pages, such as the reserved area and the page containing the lock bytes. For a summary of Flash security settings and restrictions affecting Flash erase operations, please see Section "19.3. Security Options" on page 114.

#### 19.1.3. Flash Write Procedure

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed should be erased before a new value is written.

The recommended procedure for writing a single byte in Flash is as follows:

- 1. Save current interrupt state and disable interrupts.

- 2. Ensure that the Flash byte has been erased (has a value of 0xFF).

- 3. Set the PSWE bit (register PSCTL).

- 4. Clear the PSEE bit (register PSCTL).

- 5. Write the first key code to FLKEY: 0xA5.

- 6. Write the second key code to FLKEY: 0xF1.

- 7. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- 8. Clear the PSWE bit.

- 9. Restore previous interrupt state.

Steps 5–7 must be repeated for each byte to be written.

**Note:** Flash security settings may prevent writes to some areas of Flash, such as the reserved area. For a summary of Flash security settings and restrictions affecting Flash write operations, please see Section "19.3. Security Options" on page 114.

#### 19.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction.

**Note:** MOVX read instructions always target XRAM.

#### **19.3. Security Options**

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, and erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock all Flash pages, starting at page 0, by writing a non-0xFF value to the lock byte. Note that writing a non-0xFF value to the lock byte will lock all pages of FLASH from reads, writes, and erases, including the page containing the lock byte.

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 19.1 summarizes the Flash security

#### 22.2. Programmable Internal High-Frequency (H-F) Oscillator

All C8051F80x-83x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICL register as defined by SFR Definition 22.2.

On C8051F80x-83x devices, OSCICL is factory calibrated to obtain a 24.5 MHz base frequency.

The internal oscillator output frequency may be divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

The precision oscillator supports a spread spectrum mode which modulates the output frequency in order to reduce the EMI generated by the system. When enabled (SSE = 1), the oscillator output frequency is modulated by a stepped triangle wave whose frequency is equal to the oscillator frequency divided by 384 (63.8 kHz using the factory calibration). The maximum deviation from the center frequency is  $\pm 0.75\%$ . The output frequency updates occur every 32 cycles and the step size is typically 0.25% of the center frequency.

#### SFR Definition 22.2. OSCICL: Internal H-F Oscillator Calibration

| Bit   | 7           | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|-------|-------------|--------|--------|--------|--------|--------|--------|--------|--|

| Name  | OSCICL[6:0] |        |        |        |        |        |        |        |  |

| Туре  | R/W         |        |        |        |        |        |        |        |  |

| Reset | Varies      | Varies | Varies | Varies | Varies | Varies | Varies | Varies |  |

SFR Address = 0xB3

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0 | OSCICL[7:0] | Internal Oscillator Calibration Bits.                                                                                                                                                                                                                                                                     |

|     |             | These bits determine the internal oscillator period. When set to 00000000b, the H-F oscillator operates at its fastest setting. When set to 1111111b, the H-F oscillator operates at its slowest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24.5 MHz. |

### 23.3. Priority Crossbar Decoder

The Priority Crossbar Decoder assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

Because of the nature of the Priority Crossbar Decoder, not all peripherals can be located on all port pins. Figure 23.4 maps peripherals to the potential port pins on which the peripheral I/O can appear.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to P0.0 if VREF is used, P0.1 if AGND is used, P0.3 and/or P0.2 if the external oscillator circuit is enabled, P0.6 if the ADC is configured to use the external conversion start signal (CNVSTR), and any selected ADC, Comparator, or Capacitive Sense inputs. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin.

Registers XBR0, XBR1, and XBR2 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when a UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

| Bit      | Set by Hardware When:                                                                                                                                                                                                                                                                                   | Cleared by Hardware When:                                                      |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| MASTER   | <ul> <li>A START is generated.</li> </ul>                                                                                                                                                                                                                                                               | <ul> <li>A STOP is generated.</li> </ul>                                       |

| MASIER   |                                                                                                                                                                                                                                                                                                         | <ul> <li>Arbitration is lost.</li> </ul>                                       |

|          | <ul> <li>START is generated.</li> </ul>                                                                                                                                                                                                                                                                 | <ul> <li>A START is detected.</li> </ul>                                       |

| TXMODE   | <ul> <li>SMB0DAT is written before the start of an</li> </ul>                                                                                                                                                                                                                                           | <ul> <li>Arbitration is lost.</li> </ul>                                       |

| TANIO DE | SMBus frame.                                                                                                                                                                                                                                                                                            | <ul> <li>SMB0DAT is not written before the start of an SMBus frame.</li> </ul> |

| STA      | <ul> <li>A START followed by an address byte is received.</li> </ul>                                                                                                                                                                                                                                    | Must be cleared by software.                                                   |

| STO      | <ul> <li>A STOP is detected while addressed as a<br/>slave.</li> </ul>                                                                                                                                                                                                                                  | A pending STOP is generated.                                                   |

|          | Arbitration is lost due to a detected STOP.                                                                                                                                                                                                                                                             |                                                                                |

| ACKRQ    | <ul> <li>A byte has been received and an ACK<br/>response value is needed (only when<br/>hardware ACK is not enabled).</li> </ul>                                                                                                                                                                       | <ul> <li>After each ACK cycle.</li> </ul>                                      |

| ARBLOST  | <ul> <li>A repeated START is detected as a<br/>MASTER when STA is low (unwanted<br/>repeated START).</li> <li>SCL is sensed low while attempting to<br/>generate a STOP or repeated START<br/>condition.</li> </ul>                                                                                     | Each time SI is cleared.                                                       |

|          | <ul> <li>SDA is sensed low while transmitting a 1<br/>(excluding ACK bits).</li> </ul>                                                                                                                                                                                                                  |                                                                                |

| ACK      | <ul> <li>The incoming ACK value is low<br/>(ACKNOWLEDGE).</li> </ul>                                                                                                                                                                                                                                    | <ul> <li>The incoming ACK value is high<br/>(NOT ACKNOWLEDGE).</li> </ul>      |

| SI       | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> <li>A byte has been transmitted and an ACK/NACK received.</li> <li>A byte has been received.</li> <li>A START or repeated START followed by a slave address + R/W has been received.</li> <li>A STOP has been received.</li> </ul> | <ul> <li>Must be cleared by software.</li> </ul>                               |

Table 26.3. Sources for Hardware Changes to SMB0CN

#### 26.4.3. Hardware Slave Address Recognition

The SMBus hardware has the capability to automatically recognize incoming slave addresses and send an ACK without software intervention. Automatic slave address recognition is enabled by setting the EHACK bit in register SMB0ADM to 1. This will enable both automatic slave address recognition and automatic hardware ACK generation for received bytes (as a master or slave). More detail on automatic hardware ACK generation can be found in Section 26.4.2.2.

The registers used to define which address(es) are recognized by the hardware are the SMBus Slave Address register (SFR Definition 26.3) and the SMBus Slave Address Mask register (SFR Definition 26.4). A single address or range of addresses (including the General Call Address 0x00) can be specified using these two registers. The most-significant seven bits of the two registers are used to define which addresses will be ACKed. A 1 in bit positions of the slave address mask SLVM[6:0] enable a comparison between the received slave address and the hardware's slave address SLV[6:0] for those bits. A 0 in a bit of the slave address mask means that bit will be treated as a "don't care" for comparison purposes. In this

case, either a 1 or a 0 value are acceptable on the incoming slave address. Additionally, if the GC bit in register SMB0ADR is set to 1, hardware will recognize the General Call Address (0x00). Table 26.4 shows some example parameter settings and the slave addresses that will be recognized by hardware under those conditions.

| Hardware Slave Address<br>SLV[6:0] | Slave Address Mask<br>SLVM[6:0] | GC bit | Slave Addresses Recognized by<br>Hardware |

|------------------------------------|---------------------------------|--------|-------------------------------------------|

| 0x34                               | 0x7F                            | 0      | 0x34                                      |

| 0x34                               | 0x7F                            | 1      | 0x34, 0x00 (General Call)                 |

| 0x34                               | 0x7E                            | 0      | 0x34, 0x35                                |

| 0x34                               | 0x7E                            | 1      | 0x34, 0x35, 0x00 (General Call)           |

| 0x70                               | 0x73                            | 0      | 0x70, 0x74, 0x78, 0x7C                    |

Table 26.4. Hardware Address Recognition Examples (EHACK = 1)

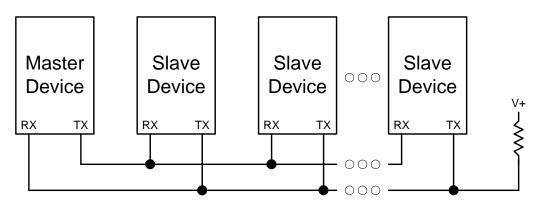

#### 27.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 27.6. UART Multi-Processor Mode Interconnect Diagram

### SFR Definition 28.1. CKCON: Clock Control

| Bit   | 7 | 6 | 5    | 4    | 3   | 2   | 1        | 0 |

|-------|---|---|------|------|-----|-----|----------|---|

| Name  |   |   | T2MH | T2ML | T1M | ТОМ | SCA[1:0] |   |

| Туре  | R | R | R/W  | R/W  | R/W | R/W | R/W      |   |

| Reset | 0 | 0 | 0    | 0    | 0   | 0   | 0        | 0 |

#### SFR Address = 0x8E

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused   | Read = 0b; Write = Don't care                                                                                                                                                                                                                                                                                                                             |

| 5   | T2MH     | Timer 2 High Byte Clock Select.Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.1: Timer 2 high byte uses the system clock.                                                                                                                      |

| 4   | T2ML     | <ul> <li>Timer 2 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |

| 3   | T1       | <b>Timer 1 Clock Select.</b><br>Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                                     |

| 2   | T0       | Timer 0 Clock Select.Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].1: Counter/Timer 0 uses the system clock.                                                                                                                                        |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.These bits control the Timer 0/1 Clock Prescaler:00: System clock divided by 1201: System clock divided by 410: System clock divided by 4811: External clock divided by 8 (synchronized with the system clock)                                                                                                                    |

## SFR Definition 28.11. TMR2L: Timer 2 Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | TMR2L[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |

## SFR Definition 28.12. TMR2H Timer 2 High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | TMR2H[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xCD

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                                                                                   |

|     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2H contains the 8-bit high byte timer value. |

## SFR Definition 29.1. PCA0CN: PCA0 Control

| Bit   | 7   | 6   | 5 | 4 | 3 | 2    | 1    | 0    |

|-------|-----|-----|---|---|---|------|------|------|

| Name  | CF  | CR  |   |   |   | CCF2 | CCF1 | CCF0 |

| Туре  | R/W | R/W | R | R | R | R/W  | R/W  | R/W  |

| Reset | 0   | 0   | 0 | 0 | 0 | 0    | 0    | 0    |

#### SFR Address = 0xD8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | CF     | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                                   |  |  |  |  |

|     |        | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000.<br>When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the<br>CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared<br>by hardware and must be cleared by software. |  |  |  |  |

| 6   | CR     | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                                     |  |  |  |  |

|     |        | This bit enables/disables the PCA Counter/Timer.                                                                                                                                                                                                                                                                   |  |  |  |  |

|     |        | 0: PCA Counter/Timer disabled.                                                                                                                                                                                                                                                                                     |  |  |  |  |

|     |        | 1: PCA Counter/Timer enabled.                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 5:3 | Unused | Read = 000b, Write = Don't care.                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 2   | CCF2   | PCA Module 2 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |  |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF2 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |  |

| 1   | CCF1   | PCA Module 1 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |  |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF1 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |  |

| 0   | CCF0   | PCA Module 0 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |  |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF0 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |  |

## SFR Definition 29.2. PCA0MD: PCA0 Mode

| Bit                | 7      | 6                                                                                  | 5     | 4 | 3    | 2    | 1    | 0   |

|--------------------|--------|------------------------------------------------------------------------------------|-------|---|------|------|------|-----|

| Nam                | e CIDL | WDTE                                                                               | WDLCK |   | CPS2 | CPS1 | CPS0 | ECF |

| Туре               | e R/W  | R/W                                                                                | R/W   | R | R/W  | R/W  | R/W  | R/W |

| Rese               | et O   | 1                                                                                  | 0     | 0 | 0    | 0    | 0    | 0   |

| SFR Address = 0xD9 |        |                                                                                    |       |   |      |      |      |     |

| Bit                | Name   | Function                                                                           |       |   |      |      |      |     |

| 7                  | CIDL   | PCA Counter/Timer Idle Control.                                                    |       |   |      |      |      |     |

|                    |        | Specifies PCA behavior when CPU is in idle mode.                                   |       |   |      |      |      |     |

|                    |        | 0: PCA continues to function normally while the system controller is in Idle mode. |       |   |      |      |      |     |

|                    |        | 1: PCA operation is suspended while the system controller is in idle mode.         |       |   |      |      |      |     |

| 6                  | WDTE   | Watchdog Timer Enable.                                                             |       |   |      |      |      |     |

|                    |        | If this bit is set, PCA Module 2 is used as the watchdog timer.                    |       |   |      |      |      |     |

|                    |        | 0: Watchdog Timer disabled.                                                        |       |   |      |      |      |     |

|                    |        | 1: PCA Module 2 enabled as Watchdog Timer.                                         |       |   |      |      |      |     |

| 5                  | WDLCK  | Watchdog Timer Lock.                                                               |       |   |      |      |      |     |

| 5                  | VULCK  |                                                                                    |       |   |      |      |      |     |

|                    |        | This bit locks/unlocks the Watchdog Timer Enable. When WDLCK is set, the Watchdog  |       |   |      |      |      |     |

Timer may not be disabled until the next system reset.

|                                                                                                                                                                                                 |          | 0: Watchdog Timer Enable unlocked.<br>1: Watchdog Timer Enable locked.         |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------|--|--|--|--|

| 4                                                                                                                                                                                               | Unused   | Read = 0b, Write = Don't care.                                                 |  |  |  |  |

| 3:1                                                                                                                                                                                             | CPS[2:0] | PCA Counter/Timer Pulse Select.                                                |  |  |  |  |

|                                                                                                                                                                                                 |          | These bits select the timebase source for the PCA counter                      |  |  |  |  |

|                                                                                                                                                                                                 |          | 000: System clock divided by 12                                                |  |  |  |  |

|                                                                                                                                                                                                 |          | 001: System clock divided by 4                                                 |  |  |  |  |

|                                                                                                                                                                                                 |          | 010: Timer 0 overflow                                                          |  |  |  |  |

|                                                                                                                                                                                                 |          | 011: High-to-low transitions on ECI (max rate = system clock divided by 4)     |  |  |  |  |

|                                                                                                                                                                                                 |          | 100: System clock                                                              |  |  |  |  |

|                                                                                                                                                                                                 |          | 101: External clock divided by 8 (synchronized with the system clock)          |  |  |  |  |

|                                                                                                                                                                                                 |          | 11x: Reserved                                                                  |  |  |  |  |

| 0                                                                                                                                                                                               | ECF      | PCA Counter/Timer Overflow Interrupt Enable.                                   |  |  |  |  |

|                                                                                                                                                                                                 |          | This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.    |  |  |  |  |

|                                                                                                                                                                                                 |          | 0: Disable the CF interrupt.                                                   |  |  |  |  |

|                                                                                                                                                                                                 |          | 1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is |  |  |  |  |

|                                                                                                                                                                                                 |          | set.                                                                           |  |  |  |  |

| <b>Note:</b> When the WDTE bit is set to 1, the other bits in the PCA0MD register cannot be modified. To change the contents of the PCA0MD register, the Watchdog Timer must first be disabled. |          |                                                                                |  |  |  |  |

## SFR Definition 29.3. PCA0PWM: PCA0 PWM Configuration

| Bit   | 7     | 6    | 5    | 4 | 3     | 2          | 1 | 0 |

|-------|-------|------|------|---|-------|------------|---|---|

| Name  | ARSEL | ECOV | COVF |   | EAR16 | CLSEL[1:0] |   |   |

| Туре  | R/W   | R/W  | R/W  | R | R/W   | R/W        |   |   |

| Reset | 0     | 0    | 0    | 0 | 0     | 0          | 0 | 0 |

SFR Address = 0xF7

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |               |  |  |  |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------|--|--|--|

| 7   | ARSEL      | Auto-Reload Register Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |               |  |  |  |

|     |            | This bit selects whether to read and write the normal PCA capture/compare registers (PCA0CPn), or the Auto-Reload registers at the same SFR addresses. This function is used to define the reload value for 9-bit through 15-bit PWM mode and 16-bit PWM mode. In all other modes, the Auto-Reload registers have no function.<br>0: Read/Write Capture/Compare Registers at PCA0CPHn and PCA0CPLn.<br>1: Read/Write Auto-Reload Registers at PCA0CPHn and PCA0CPLn.                                                |                                |               |  |  |  |

| 6   | ECOV       | Cycle Overflow Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |               |  |  |  |

|     |            | This bit sets the masking of the Cycle Overflow Flag (COVF) interrupt.<br>0: COVF will not generate PCA interrupts.                                                                                                                                                                                                                                                                                                                                                                                                 |                                |               |  |  |  |

| _   | 00)/5      | 1: A PCA interrupt will be gene                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | erated when COVF is set.       |               |  |  |  |

| 5   | COVF       | Cycle Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |               |  |  |  |

|     |            | <ul> <li>This bit indicates an overflow of the nth bit (n= 9 through 15) of the main PCA counter (PCA0). The specific bit used for this flag depends on the setting of the CLSEL bits.</li> <li>The bit can be set by hardware or software, but must be cleared by software.</li> <li>0: No overflow has occurred since the last time this bit was cleared.</li> <li>1: An overflow has occurred since the last time this bit was cleared.</li> </ul>                                                               |                                |               |  |  |  |

| 4   | Unused     | Read = 0b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |               |  |  |  |

| 3   | EAR16      | 16-Bit PWM Auto-Reload Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |               |  |  |  |

|     |            | This bit controls the Auto-Reload feature in 16-bit PWM mode, which loads the PCA0CPn capture/compare registers with the values from the Auto-Reload registers at the same SFR addresses on an overflow of the PCA counter (PCA0). This setting affects all PCA channels that are configured to use 16-bit PWM mode.<br>0: 16-bit PWM mode Auto-Reload is disabled. This default setting is backwards-compatible with the 16-bit PWM mode available on other devices.<br>1: 16-bit PWM mode Auto-Reload is enabled. |                                |               |  |  |  |

| 2:0 | CLSEL[2:0] | Cycle Length Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |               |  |  |  |

|     |            | When 16-bit PWM mode is not selected, these bits select the length of the PWM cycle, from 8 to 15 bits. This affects all channels configured for PWM which are not using 16-bit PWM mode. These bits are ignored for individual channels configured to16-bit PWM mode.                                                                                                                                                                                                                                              |                                |               |  |  |  |

|     |            | 000: 8 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 011: 11 bits.                  | 110: 14 bits. |  |  |  |

|     |            | 001: 9 bits.<br>010: 10 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100: 12 bits.<br>101: 13 bits. | 111: 15 bits. |  |  |  |

## **DOCUMENT CHANGE LIST**

### **Revision 0.2 to Revision 1.0**

- Updated Electrical Specification Tables to reflect production characterization data.

- Added Minimum SYSCLK specification for writing or erasing Flash.

- Added caution for going into suspend with wake source active (Section 20.3)

- Corrected VDM0CN reset values to "Varies".

- Removed mention of IDAC in Pinout table.