# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f811-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

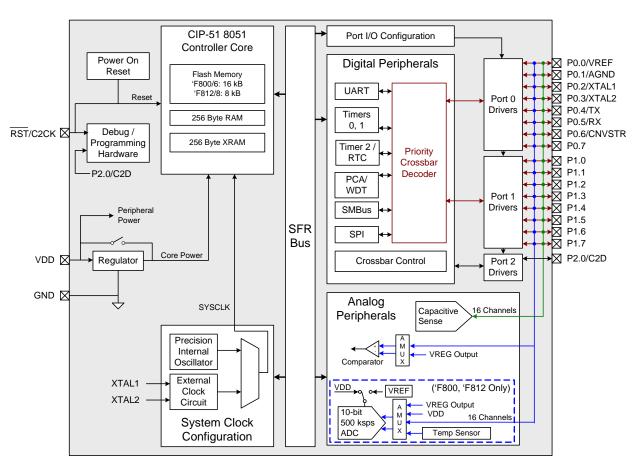

Figure 1.1. C8051F800, C8051F806, C8051F812, C8051F818 Block Diagram

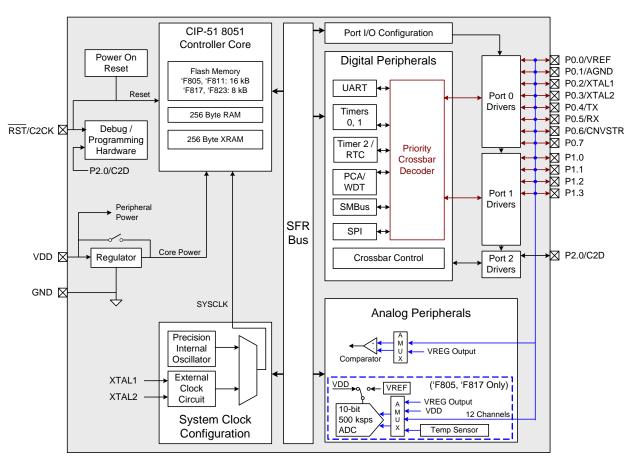

Figure 1.6. C8051F805, C8051F811, C8051F817, C8051F823 Block Diagram

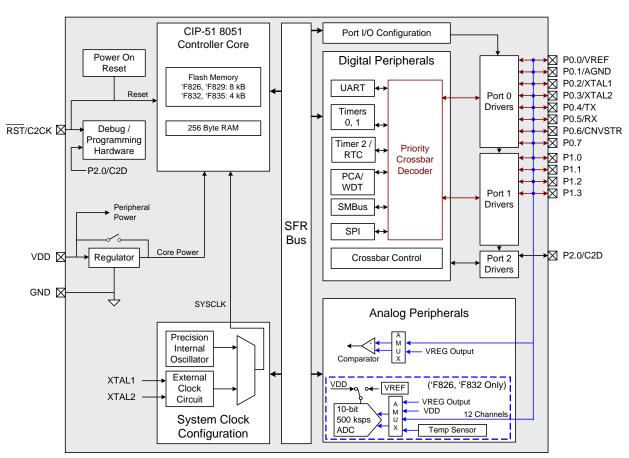

Figure 1.9. C8051F826, C8051F829, C8051F832, C8051F835 Block Diagram

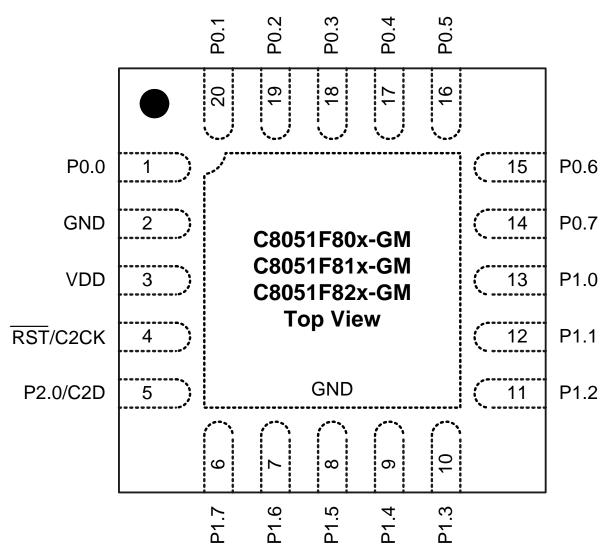

Figure 3.1. QFN-20 Pinout Diagram (Top View)

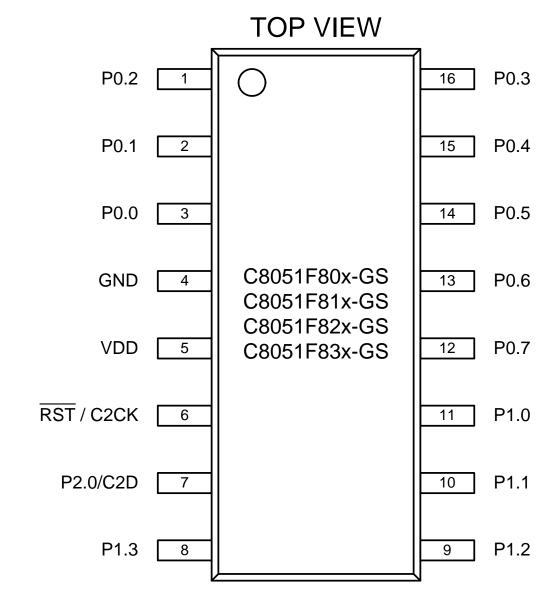

Figure 3.3. SOIC-16 Pinout Diagram (Top View)

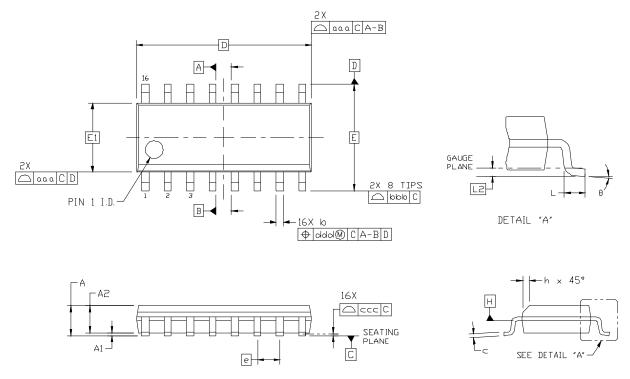

## 6. SOIC-16 Package Specifications

Figure 6.1. SOIC-16 Package Drawing

| Dimension | Min      | Nom      | Max  |  | Dimension | Min  | Nom      | Ма  |

|-----------|----------|----------|------|--|-----------|------|----------|-----|

| A         | _        |          | 1.75 |  | L         | 0.40 |          | 1.2 |

| A1        | 0.10     |          | 0.25 |  | L2        |      | 0.25 BSC |     |

| A2        | 1.25     |          | _    |  | h         | 0.25 |          | 0.5 |

| b         | 0.31     |          | 0.51 |  | θ         | 0°   |          | 80  |

| С         | 0.17     |          | 0.25 |  | aaa       |      | 0.10     |     |

| D         |          | 9.90 BSC |      |  | bbb       |      | 0.20     |     |

| E         | 6.00 BSC |          |      |  | CCC       | 0.10 |          |     |

| E1        |          | 3.90 BSC |      |  | ddd       |      | 0.25     |     |

| е         |          | 1.27 BSC |      |  | <b>L</b>  |      |          |     |

### Table 6.1. SOIC-16 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MS-012, Variation AC.

Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

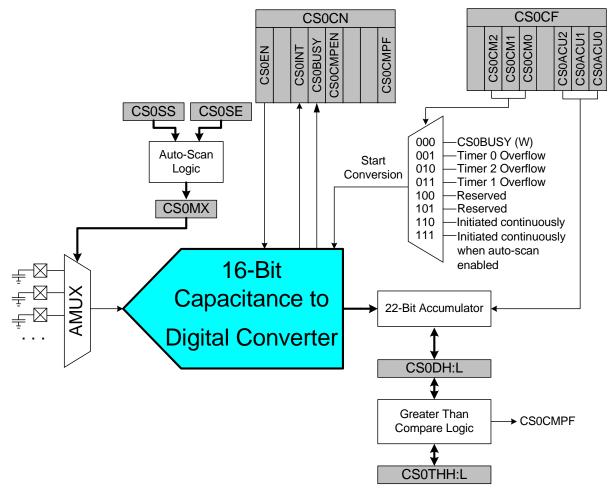

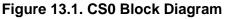

## 13. Capacitive Sense (CS0)

The Capacitive Sense subsystem included on the C8051F800/1/3/4/6/7/9, C8051F810/2/3/5/6/8/9, C8051F821/2/4/5/7/8, C8051F830/1/3/4 uses a capacitance-to-digital circuit to determine the capacitance on a port pin. The module can take measurements from different port pins using the module's analog multiplexer. The multiplexer supports up to 16 channels. See SFR Definition 13.9. "CSOMX: Capacitive Sense Mux Channel Select" on page 81 for channel availability for specific part numbers. The module is enabled only when the CS0EN bit (CS0CN) is set to 1. Otherwise the module is in a low-power shutdown state. The module can be configured to take measurements on one port pin or a group of port pins, using auto-scan. An accumulator can be configured to accumulate multiple conversions on an input channel. Interrupts can be generated when CS0 completes a conversion or when the measured value crosses a threshold defined in CS0THH:L.

## SFR Definition 13.3. CS0DH: Capacitive Sense Data High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | CS0DH[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R          | R | R | R | R | R | R | R |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xAC

| Bit | Name  | Description                                                                    |

|-----|-------|--------------------------------------------------------------------------------|

| 7:0 | CS0DH | CS0 Data High Byte.                                                            |

|     |       | Stores the high byte of the last completed 16-bit Capacitive Sense conversion. |

## SFR Definition 13.4. CS0DL: Capacitive Sense Data Low Byte

| Bit   | 7 | 6 | 5 | 4    | 3      | 2 | 1 | 0 |

|-------|---|---|---|------|--------|---|---|---|

| Name  |   |   |   | CS0D | L[7:0] |   |   |   |

| Туре  | R | R | R | R    | R      | R | R | R |

| Reset | 0 | 0 | 0 | 0    | 0      | 0 | 0 | 0 |

SFR Address = 0xAB

| Bit | Name  | Description                                                                   |

|-----|-------|-------------------------------------------------------------------------------|

| 7:0 | CS0DL | CS0 Data Low Byte.                                                            |

|     |       | Stores the low byte of the last completed 16-bit Capacitive Sense conversion. |

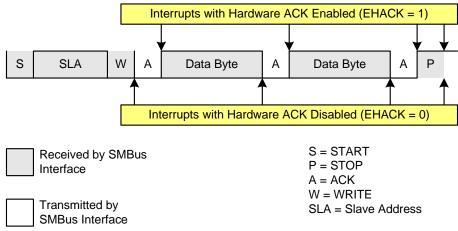

## **17. Special Function Registers**

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F80x-83x's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F80x-83x. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 17.1 lists the SFRs implemented in the C8051F80x-83x device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g., P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 17.2, for a detailed description of each register.

| F8 | SPI0CN | PCA0L    | PCA0H    | PCA0CPL0 | PCA0CPH0 | P0MAT   | P0MASK   | VDM0CN   |

|----|--------|----------|----------|----------|----------|---------|----------|----------|

| F0 | В      | P0MDIN   | P1MDIN   | EIP1     | EIP2     |         |          | PCA0PWM  |

| E8 | ADC0CN | PCA0CPL1 | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 | P1MAT   | P1MASK   | RSTSRC   |

| E0 | ACC    | XBR0     | XBR1     |          | IT01CF   |         | EIE1     | EIE2     |

| D8 | PCA0CN | PCA0MD   | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 | CRC0IN  | CRC0DATA |          |

| D0 | PSW    | REF0CN   | CRC0AUTO | CRC0CNT  | P0SKIP   | P1SKIP  | SMB0ADM  | SMB0ADR  |

| C8 | TMR2CN | REG0CN   | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H   | CRC0CN   | CRC0FLIP |

| C0 | SMB0CN | SMB0CF   | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL | ADC0LTH  |          |

| B8 | IP     | CS0SS    | CS0SE    | ADC0MX   | ADC0CF   | ADC0L   | ADC0H    |          |

| B0 | CS0CN  | OSCXCN   | OSCICN   | OSCICL   |          | HWID    | REVID    | FLKEY    |

| A8 | IE     | CLKSEL   |          | CS0DL    | CS0DH    | DERVID  |          |          |

| A0 | P2     | SPI0CFG  | SPI0CKR  | SPI0DAT  | POMDOUT  | P1MDOUT | P2MDOUT  |          |

| 98 | SCON0  | SBUF0    |          | CPT0CN   | CS0MX    | CPT0MD  | CS0CF    | CPT0MX   |

| 90 | P1     |          |          |          |          |         | CS0THL   | CS0THH   |

| 88 | TCON   | TMOD     | TL0      | TL1      | TH0      | TH1     | CKCON    | PSCTL    |

| 80 | P0     | SP       | DPL      | DPH      |          |         |          | PCON     |

|    | 0(8)   | 1(9)     | 2(A)     | 3(B)     | 4(C)     | 5(D)    | 6(E)     | 7(F)     |

### Table 17.1. Special Function Register (SFR) Memory Map

Note: SFR Addresses ending in 0x0 or 0x8 are bit-addressable locations, and can be used with bitwise instructions.

## 18.3. INTO and INT1 External Interrupts

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "28.1. Timer 0 and Timer 1" on page 211) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 18.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see Section "23.3. Priority Crossbar Decoder" on page 143 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

## 19. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 7.6 for complete Flash memory electrical characteristics.

### 19.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "30. C2 Interface" on page 244.

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before programming Flash memory using MOVX, Flash programming operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software. For detailed guidelines on programming Flash from firmware, please see Section "19.4. Flash Write and Erase Guidelines" on page 115.

**Note:** A minimum SYSCLK frequency is required for writing or erasing Flash memory, as detailed in "7. Electrical Characteristics" on page 39.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled and enabled as a reset source in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor is disabled, or not enabled as a reset source, will cause a Flash Error device reset.

#### 19.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 19.2.

### 19.1.2. Flash Erase Procedure

The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- 1. Save current interrupt state and disable interrupts.

- 2. Set the PSEE bit (register PSCTL).

- 3. Set the PSWE bit (register PSCTL).

- 4. Write the first key code to FLKEY: 0xA5.

- 5. Write the second key code to FLKEY: 0xF1.

- 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- 7. Clear the PSWE and PSEE bits.

| Special<br>Function<br>Signals<br>(Control<br>Signals)<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK) | P0.0 Skipped                                                                                                                                                                                                                                     | AGND AGND | P0.2 Skipped XTAL1 N | P0.3 Skipped |  | 5            | CNVSTR 9    | 7          |      |      | 2   | 3   | 4 <sup>1</sup> | 5 <sup>1</sup> | 6 <sup>1</sup> | <b>7</b> <sup>1</sup> | Signal Unavailable to Crossbar |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|--------------|--|--------------|-------------|------------|------|------|-----|-----|----------------|----------------|----------------|-----------------------|--------------------------------|

| Function<br>SignalsTX0RX0RX0SCKMISOMOSINSS2SDASCLCP0ASYSCLKCEX0CEX1CEX2ECIT1Pin Skip<br>SettingsIn this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Skipped                                                                                                                                                                                                                                          | AGND      |                      | Skipped      |  |              | CNVSTR      |            |      |      |     |     |                |                |                |                       | Crossbar                       |

| RX0<br>SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0 Skipped                                                                                                                                                                                                                                     |           | P0.2 Skipped         | P0.3 Skipped |  |              |             |            |      |      |     |     |                |                |                |                       | Crossbar                       |

| SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P0.0 Skipped                                                                                                                                                                                                                                     |           | P0.2 Skipped         | P0.3 Skipped |  |              |             |            |      |      |     |     |                |                |                |                       | Crossbar                       |

| MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped                                                                                                                                                                                                                                     |           | P0.2 Skipped         | P0.3 Skipped |  |              |             |            |      |      |     |     |                |                |                |                       | Crossbar                       |

| MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skipped                                                                                                                                                                                                                                     |           | P0.2 Skipped         | P0.3 Skipped |  |              |             |            |      |      |     |     |                |                |                |                       | Crossbar                       |

| NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped                                                                                                                                                                                                                                     |           | P0.2 Skipped         | P0.3 Skipped |  |              |             |            |      |      |     |     |                |                |                |                       | Crossl                         |

| SDA<br>SCL<br>CP00<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P0.0 Skipped                                                                                                                                                                                                                                     |           | P0.2 Skipped         | P0.3 Skipped |  |              |             |            |      |      |     |     |                |                |                |                       | ō                              |

| SCL<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P0.0 Skipped                                                                                                                                                                                                                                     |           | P0.2 Skipped         | P0.3 Skipped |  |              |             |            |      |      |     |     |                |                |                |                       |                                |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skippe                                                                                                                                                                                                                                      |           | P0.2 Skippe          | P0.3 Skippe  |  |              |             |            |      |      |     |     |                |                |                |                       | e to                           |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Ski                                                                                                                                                                                                                                         |           | P0.2 Ski             | P0.3 Ski     |  |              |             |            |      |      |     |     |                |                |                |                       | able                           |

| CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0                                                                                                                                                                                                                                             |           | P0.2                 | P0.3         |  |              |             |            |      |      |     |     |                |                |                |                       | vail                           |

| CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ط<br> <br> <br>                                                                                                                                                                                                                                  |           | ₫.                   | ۹.           |  |              |             |            |      |      |     |     |                |                |                |                       | Jna                            |

| CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                  |           |                      |              |  |              |             |            |      |      |     |     |                |                |                |                       | al                             |

| CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                  |           |                      |              |  |              |             |            |      |      |     |     |                |                |                |                       | sign                           |

| ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                  |           |                      |              |  |              |             |            |      |      |     |     |                |                |                |                       | 0                              |

| T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                |           |                      |              |  |              |             |            |      |      |     |     |                |                |                |                       |                                |