Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Last Time Buy                                                  |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                          |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 16x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 24-QSOP                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f813-gu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Table 18.1. Interrupt Summary                                                | 104 |

|-----|------------------------------------------------------------------------------|-----|

| 19. | . Flash Memory                                                               |     |

|     | Table 19.1. Flash Security Summary                                           | 115 |

| 20. | . Power Management Modes                                                     |     |

| 21. | . Reset Sources                                                              |     |

| 22. | . Oscillators and Clock Selection                                            |     |

| 23. | . Port Input/Output                                                          |     |

|     | Table 23.1. Port I/O Assignment for Analog Functions                         |     |

|     | Table 23.2. Port I/O Assignment for Digital Functions                        |     |

|     | Table 23.3. Port I/O Assignment for External Digital Event Capture Functions | 142 |

| 24. | . Cyclic Redundancy Check Unit (CRC0)                                        |     |

|     | Table 24.1. Example 16-bit CRC Outputs                                       |     |

|     | Table 24.2. Example 32-bit CRC Outputs                                       | 161 |

| 25. | . Enhanced Serial Peripheral Interface (SPI0)                                |     |

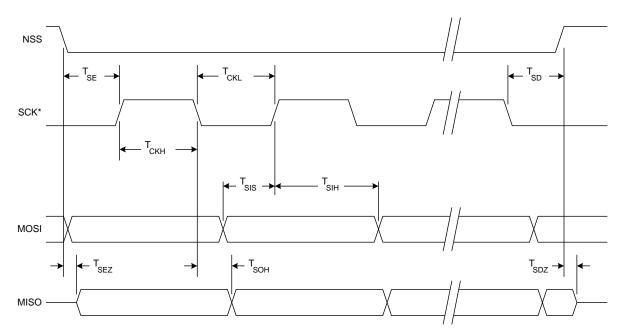

|     | Table 25.1. SPI Slave Timing Parameters                                      | 179 |

| 26. | . SMBus                                                                      |     |

|     | Table 26.1. SMBus Clock Source Selection                                     |     |

|     | Table 26.2. Minimum SDA Setup and Hold Times                                 |     |

|     | Table 26.3. Sources for Hardware Changes to SMB0CN                           | 189 |

|     | Table 26.4. Hardware Address Recognition Examples (EHACK = 1)                | 190 |

|     | Table 26.5. SMBus Status Decoding With Hardware ACK Generation Disabled      |     |

|     | (EHACK = 0)                                                                  | 197 |

|     | Table 26.6. SMBus Status Decoding With Hardware ACK Generation Enabled       |     |

|     | (EHACK = 1)                                                                  | 199 |

| 27. | . UARTO                                                                      |     |

|     | Table 27.1. Timer Settings for Standard Baud Rates                           |     |

|     | Using The Internal 24.5 MHz Oscillator                                       | 208 |

|     | Table 27.2. Timer Settings for Standard Baud Rates                           |     |

|     | Using an External 22.1184 MHz Oscillator                                     | 208 |

| 28. | . Timers                                                                     |     |

| 29. | . Programmable Counter Array                                                 |     |

|     | Table 29.1. PCA Timebase Input Options                                       | 226 |

|     | Table 29.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare M       | od- |

|     | ules <sup>1,2,3,4,5,6</sup>                                                  | 228 |

|     | Table 29.3. Watchdog Timer Timeout Intervals1                                |     |

| 20  | C2 Interface                                                                 |     |

# 2. Ordering Information

All C8051F80x-83x devices have the following features:

- 25 MIPS (Peak)

- Calibrated Internal Oscillator

- SMBus/I2C

- Enhanced SPI

- UART

- Programmable counter array (3 channels)

- 3 Timers (16-bit)

- 1 Comparator

- Pb-Free (RoHS compliant) package

In addition to the features listed above, each device in the C8051F80x-83x family has a set of features that vary across the product line. See Table 2.1 for a complete list of the unique feature sets for each device in the family.

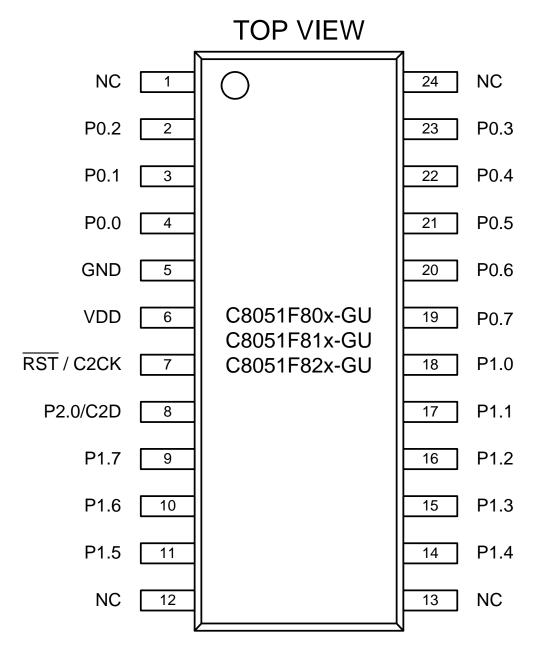

Figure 3.2. QSOP-24 Pinout Diagram (Top View)

## 7.2. Electrical Characteristics

**Table 7.2. Global Electrical Characteristics**

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                                          | Conditions                                                                                                                                                                                                                                                                                                                               | Min              | Тур                                  | Max                       | Units                      |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------|---------------------------|----------------------------|

| Supply Voltage                                                     |                                                                                                                                                                                                                                                                                                                                          | 1.8              | 3.0                                  | 3.6                       | V                          |

| Digital Supply Current with CPU Active (Normal Mode <sup>1</sup> ) | $V_{DD}$ = 1.8 V, Clock = 25 MHz<br>$V_{DD}$ = 1.8 V, Clock = 1 MHz<br>$V_{DD}$ = 1.8 V, Clock = 32 kHz<br>$V_{DD}$ = 3.0 V, Clock = 25 MHz<br>$V_{DD}$ = 3.0 V, Clock = 1 MHz<br>$V_{DD}$ = 3.0 V, Clock = 32 kHz                                                                                                                       | _<br>_<br>_<br>_ | 4.6<br>1.2<br>135<br>5.5<br>1.3      | 6.0<br>—<br>—<br>6.5<br>— | mA<br>mA<br>μA<br>mA<br>mA |

| Digital Supply Current with CPU Inactive (Idle Mode <sup>1</sup> ) | $\begin{split} &V_{DD} = 1.8 \text{ V, Clock} = 25 \text{ MHz} \\ &V_{DD} = 1.8 \text{ V, Clock} = 1 \text{ MHz} \\ &V_{DD} = 1.8 \text{ V, Clock} = 32 \text{ kHz} \\ &V_{DD} = 3.0 \text{ V, Clock} = 25 \text{ MHz} \\ &V_{DD} = 3.0 \text{ V, Clock} = 1 \text{ MHz} \\ &V_{DD} = 3.0 \text{ V, Clock} = 32 \text{ kHz} \end{split}$ |                  | 2<br>190<br>100<br>2.3<br>335<br>115 | 2.6<br>—<br>—<br>2.8<br>— | mA<br>µA<br>µA<br>mA<br>µA |

| Digital Supply Current (shutdown)                                  | Oscillator not running (stop mode),<br>Internal Regulator Off, 25 °C                                                                                                                                                                                                                                                                     | _                | 0.5                                  | 2                         | μA                         |

|                                                                    | Oscillator not running (stop or suspend mode), Internal Regulator On, 25 °C                                                                                                                                                                                                                                                              | _                | 105                                  | 140                       | μΑ                         |

| Digital Supply RAM Data<br>Retention Voltage                       |                                                                                                                                                                                                                                                                                                                                          | _                | 1.3                                  | _                         | V                          |

| Specified Operating Temperature Range                              |                                                                                                                                                                                                                                                                                                                                          | -40              | _                                    | +85                       | °C                         |

| SYSCLK (system clock frequency)                                    | See Note 2                                                                                                                                                                                                                                                                                                                               | 0                |                                      | 25                        | MHz                        |

| Tsysl (SYSCLK low time)                                            |                                                                                                                                                                                                                                                                                                                                          | 18               | _                                    | _                         | ns                         |

| Tsysh (SYSCLK high time)                                           |                                                                                                                                                                                                                                                                                                                                          | 18               | _                                    | _                         | ns                         |

#### Notes

- 1. Includes bias current for internal voltage regulator.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

## 8.1. Output Code Formatting

The ADC measures the input voltage with reference to GND. The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit. Conversion codes are represented as 10-bit unsigned integers. Inputs are measured from 0 to VREF x 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to 0.

| Input Voltage    | Right-Justified ADC0H:ADC0L (AD0LJST = 0) | Left-Justified ADC0H:ADC0L (AD0LJST = 1) |

|------------------|-------------------------------------------|------------------------------------------|

| VREF x 1023/1024 | 0x03FF                                    | 0xFFC0                                   |

| VREF x 512/1024  | 0x0200                                    | 0x8000                                   |

| VREF x 256/1024  | 0x0100                                    | 0x4000                                   |

| 0                | 0x0000                                    | 0x0000                                   |

#### 8.2. 8-Bit Mode

Setting the ADC08BE bit in register ADC0CF to 1 will put the ADC in 8-bit mode. In 8-bit mode, only the 8 MSBs of data are converted, and the ADC0H register holds the results. The AD0LJST bit is ignored for 8-bit mode. 8-bit conversions take two fewer SAR clock cycles than 10-bit conversions, so the conversion is completed faster, and a 500 ksps sampling rate can be achieved with a slower SAR clock.

#### 8.3. Modes of Operation

ADC0 has a maximum conversion speed of 500 ksps. The ADC0 conversion clock is a divided version of the system clock, determined by the ADOSC bits in the ADC0CF register.

#### 8.3.1. Starting a Conversion

A conversion can be initiated in one of six ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 1 overflow

- 5. A rising edge on the CNVSTR input signal

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. When Timer 2 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2 is in 16-bit mode. See Section "28. Timers" on page 209 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as a Port I/O pin. When the CNVSTR input is used as the ADC0 conversion source, the associated pin should be skipped by the Digital Crossbar. See Section "23. Port Input/Output" on page 138 for details on Port I/O configuration.

## SFR Definition 8.2. ADC0H: ADC0 Data Word MSB

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | ADC0H[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## SFR Address = 0xBE

| Bit | Name       | Function                                                                                                 |

|-----|------------|----------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                          |

|     |            | For AD0LJST = 0: Bits 7–2 will read 000000b. Bits 1–0 are the upper 2 bits of the 10-bit ADC0 Data Word. |

|     |            | For AD0LJST = 1: Bits 7–0 are the most-significant bits of the 10-bit ADC0 Data Word.                    |

|     |            | Note: In 8-bit mode AD0LJST is ignored, and ADC0H holds the 8-bit data word.                             |

## SFR Definition 8.3. ADC0L: ADC0 Data Word LSB

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|-----|---|---|---|---|---|---|

| Name  | ADC0L[7:0] |     |   |   |   |   |   |   |

| Туре  |            | R/W |   |   |   |   |   |   |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

## SFR Address = 0xBD

| Bit | Name       | Function                                                                              |

|-----|------------|---------------------------------------------------------------------------------------|

| 7:0 | ADC0L[7:0] | ADC0 Data Word Low-Order Bits.                                                        |

|     |            | For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the 10-bit Data Word.               |

|     |            | For AD0LJST = 1: Bits 7–6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will |

|     |            | always read 0.                                                                        |

|     |            | Note: In 8-bit mode AD0LJST is ignored, and ADC0L will read back 00000000b.           |

## 8.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

## SFR Definition 8.5. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit   | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|-----|---|---|---|---|---|---|

| Name  | ADC0GTH[7:0] |     |   |   |   |   |   |   |

| Туре  |              | R/W |   |   |   |   |   |   |

| Reset | 1            | 1   | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0xC4

| Bit | Name         | Function                                     |

|-----|--------------|----------------------------------------------|

| 7:0 | ADC0GTH[7:0] | ADC0 Greater-Than Data Word High-Order Bits. |

## SFR Definition 8.6. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit   | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|-----|---|---|---|---|---|---|

| Name  | ADC0GTL[7:0] |     |   |   |   |   |   |   |

| Туре  |              | R/W |   |   |   |   |   |   |

| Reset | 1            | 1   | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0xC3

| Bit | Name         | Function                                    |

|-----|--------------|---------------------------------------------|

| 7:0 | ADC0GTL[7:0] | ADC0 Greater-Than Data Word Low-Order Bits. |

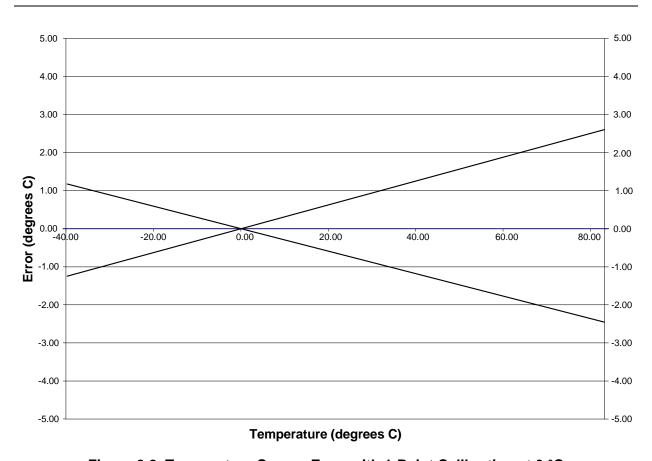

Figure 9.2. Temperature Sensor Error with 1-Point Calibration at 0 °C

#### 22.3.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 22.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation 22.2, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and  $V_{DD} = the$  MCU power supply in volts.

## **Equation 22.2. C Mode Oscillator Frequency**

$$f = (KF)/(R \times V_{DD})$$

For example: Assume  $V_{DD} = 3.0 \text{ V}$  and f = 150 kHz:

$f = KF / (C \times VDD)$ 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 22.4 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

## 23.1. Port I/O Modes of Operation

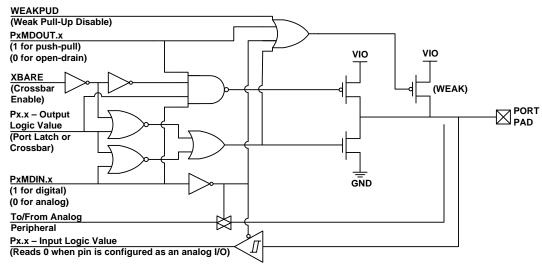

Port pins P0.0–P1.7 use the Port I/O cell shown in Figure 23.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN and PnMDOUT registers. Port pin P2.0 can be configured by software for digital I/O using the P2MDOUT register. On reset, all Port I/O cells default to a high impedance state with weak pull-ups enabled. Until the crossbar is enabled (XBARE = 1), both the high and low port I/O drive circuits are explicitly disabled on all crossbar pins.

#### 23.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, Capacitive Sense input, external oscillator input/output, VREF output, or AGND connection should be configured for analog I/O (PnMDIN.n = 0, Pn.n = 1). When a pin is configured for analog I/O, its weak pullup, digital driver, and digital receiver are disabled. To prevent the low port I/o drive circuit from pulling the pin low, a '1' should be written to the corresponding port latch (Pn.n = 1). Port pins configured for analog I/O will always read back a value of 0 regardless of the actual voltage on the pin.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital I/O may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

#### 23.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

Figure 23.2. Port I/O Cell Block Diagram

SILICON LAR

#### 23.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN). If the pin is in analog mode, a '1' must also be written to the corresponding Port Latch (Pn).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals (XBR0, XBR1).

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All port pins in analog mode must have a '1' set in the corresponding Port Latch register. All pins default to digital inputs on reset. See SFR Definition 23.8 and SFR Definition 23.12 for the PnMDIN register details.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to 1 enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility will determine the Port I/O pin-assignments based on the XBRn Register settings.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. Port output drivers are disabled while the Crossbar is disabled.

# SFR Definition 23.8. P0MDIN: Port 0 Input Mode

| Bit   | 7   | 6 | 5 | 4    | 3       | 2 | 1 | 0 |  |

|-------|-----|---|---|------|---------|---|---|---|--|

| Name  |     |   |   | P0MD | IN[7:0] |   |   |   |  |

| Туре  | R/W |   |   |      |         |   |   |   |  |

| Reset | 1   | 1 | 1 | 1    | 1       | 1 | 1 | 1 |  |

## SFR Address = 0xF1

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                                                                                                                                                                                       |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. In order for the P0.n pin to be in analog mode, there MUST be a '1' in the Port Latch register corresponding to that pin.  0: Corresponding P0.n pin is configured for analog mode.  1: Corresponding P0.n pin is not configured for analog mode. |

# SFR Definition 23.9. P0MDOUT: Port 0 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2     | 1 | 0 |  |

|-------|--------------|---|---|---|---|-------|---|---|--|

| Name  | P0MDOUT[7:0] |   |   |   |   |       |   |   |  |

| Туре  | R/W          |   |   |   |   |       |   |   |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 0 0 |   |   |  |

#### SFR Address = 0xA4

| Bit | Name         | Function                                                                       |

|-----|--------------|--------------------------------------------------------------------------------|

| 7:0 | P0MDOUT[7:0] | Output Configuration Bits for P0.7–P0.0 (respectively).                        |

|     |              | These bits are ignored if the corresponding bit in register P0MDIN is logic 0. |

|     |              | 0: Corresponding P0.n Output is open-drain.                                    |

|     |              | 1: Corresponding P0.n Output is push-pull.                                     |

# SFR Definition 23.12. P1MDIN: Port 1 Input Mode

| Bit   | 7   | 6  | 5  | 4    | 3                | 2 | 1 | 0 |  |  |  |

|-------|-----|----|----|------|------------------|---|---|---|--|--|--|

| Name  |     |    |    | P1MD | IN[7:0]          |   |   |   |  |  |  |

| Туре  | R/W |    |    |      |                  |   |   |   |  |  |  |

| Reset | 1*  | 1* | 1* | 1*   | 1* 1* 1* 1 1 1 1 |   |   |   |  |  |  |

## SFR Address = 0xF2

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDIN[7:0] | Analog Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. In order for the P1.n pin to be in analog mode, there MUST be a 1 in the Port Latch register corresponding to that pin.  0: Corresponding P1.n pin is configured for analog mode.  1: Corresponding P1.n pin is not configured for analog mode.  Note: P1.4–P1.7 are not available on 16-pin packages, with the reset value of 0000b for P1MDIN[7:4]. |

# SFR Definition 23.13. P1MDOUT: Port 1 Output Mode

| Bit   | 7 | 6   | 5 | 4     | 3       | 2 | 1 | 0 |  |

|-------|---|-----|---|-------|---------|---|---|---|--|

| Name  |   |     |   | P1MDO | UT[7:0] |   |   |   |  |

| Туре  |   | R/W |   |       |         |   |   |   |  |

| Reset | 0 | 0   | 0 | 0     | 0       | 0 | 0 | 0 |  |

## SFR Address = 0xA5

| Bit | Name         | Function                                                                       |

|-----|--------------|--------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                        |

|     |              | These bits are ignored if the corresponding bit in register P1MDIN is logic 0. |

|     |              | 0: Corresponding P1.n Output is open-drain.                                    |

|     |              | 1: Corresponding P1.n Output is push-pull.                                     |

|     |              | Note: P1.4–P1.7 are not available on 16-pin packages.                          |

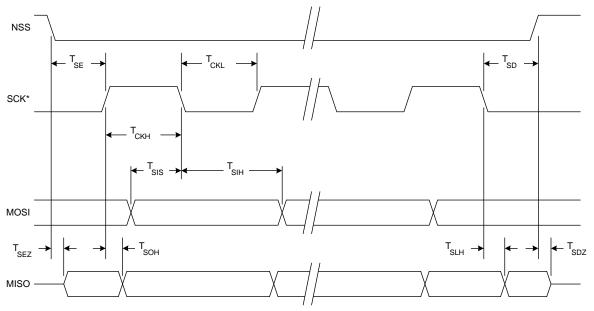

<sup>\*</sup> SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 25.10. SPI Slave Timing (CKPHA = 0)

<sup>\*</sup> SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 25.11. SPI Slave Timing (CKPHA = 1)

Table 26.6. SMBus Status Decoding With Hardware ACK Generation Enabled (EHACK = 1)

|                    | Val                      | ues | Rea                     | d |                                                              |                                                                                                               |     | lues<br>Vrit |     | itus<br>ected                  |

|--------------------|--------------------------|-----|-------------------------|---|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|--------------|-----|--------------------------------|

| Mode               | Mode<br>Status<br>Vector |     | ACKRQ<br>ARBLOST<br>ACK |   | Current SMbus State                                          | Typical Response Options                                                                                      | STA | STO          | ACK | Next Status<br>Vector Expected |

|                    | 1110                     | 0   | 0                       | Х | A master START was generated.                                | Load slave address + R/W into SMB0DAT.                                                                        | 0   | 0            | Χ   | 1100                           |

|                    |                          |     |                         |   | A master data or address byte                                | Set STA to restart transfer.                                                                                  | 1   | 0            | Χ   | 1110                           |

| ē                  |                          | 0   | 0                       | 0 | was transmitted; NACK received.                              | Abort transfer.                                                                                               | 0   | 1            | Χ   |                                |

| smitt              |                          |     |                         |   |                                                              | Load next data byte into SMB0DAT.                                                                             | 0   | 0            | Χ   | 1100                           |

| Iran               |                          |     |                         |   |                                                              | End transfer with STOP.                                                                                       | 0   | 1            | Х   | _                              |

| Master Transmitter | 1100                     | 0 0 | 0                       | 1 | A master data or address byte was transmitted; ACK received. | End transfer with STOP and start another transfer.                                                            | 1   | 1            | Χ   | _                              |

| Ž                  |                          |     |                         |   |                                                              | Send repeated START.                                                                                          | 1   | 0            | Х   | 1110                           |

|                    |                          |     |                         |   |                                                              | Switch to Master Receiver Mode (clear SI without writing new data to SMB0DAT). Set ACK for initial data byte. | 0   | 0            | 1   | 1000                           |

|                    |                          |     |                         |   |                                                              | Set ACK for next data byte;<br>Read SMB0DAT.                                                                  | 0   | 0            | 1   | 1000                           |

|                    |                          | 0   | 0                       | 1 | A master data byte was                                       | Set NACK to indicate next data byte as the last data byte; Read SMB0DAT.                                      | 0   | 0            | 0   | 1000                           |

| er                 |                          |     |                         |   | received; ACK sent.                                          | Initiate repeated START.                                                                                      | 1   | 0            | 0   | 1110                           |

| Master Receiver    | 1000                     | ,   |                         |   |                                                              | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI).                                | 0   | 0            | X   | 1100                           |

| aste               |                          |     |                         |   |                                                              | Read SMB0DAT; send STOP.                                                                                      | 0   | 1            | 0   | _                              |

| Ř                  |                          |     |                         |   | A master data byte was                                       | Read SMB0DAT; Send STOP followed by START.                                                                    | 1   | 1            | 0   | 1110                           |

|                    |                          | 0   | 0                       | 0 | received; NACK sent (last                                    | Initiate repeated START.                                                                                      | 1   | 0            | 0   | 1110                           |

|                    |                          |     |                         |   | byte).                                                       | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI).                                | 0   | 0            | X   | 1100                           |

Table 26.6. SMBus Status Decoding With Hardware ACK Generation Enabled (EHACK = 1) (Continued)

|                            | Valu                        | es F                            | Rea   | d                           |                                                                                       |                                                        |       | lues<br>Vrit |                                | tus<br>ected |                                               |                                                                    |   |   |        |      |

|----------------------------|-----------------------------|---------------------------------|-------|-----------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|-------|--------------|--------------------------------|--------------|-----------------------------------------------|--------------------------------------------------------------------|---|---|--------|------|

| Mode                       | Status Vector ACKRQ ARBLOST |                                 | ACK   | Current SMbus State         | Typical Response Options                                                              | STA                                                    | STO   | ACK          | Next Status<br>Vector Expected |              |                                               |                                                                    |   |   |        |      |

| ī.                         |                             | 0                               | 0     | 0                           | A slave byte was transmitted; NACK received.                                          | No action required (expecting STOP condition).         | 0     | 0            | Х                              | 0001         |                                               |                                                                    |   |   |        |      |

| smitte                     | 0100                        | 0                               | 0     | 1                           | A slave byte was transmitted; ACK received.                                           | Load SMB0DAT with next data byte to transmit.          | 0     | 0            | Х                              | 0100         |                                               |                                                                    |   |   |        |      |

| Slave Transmitter          |                             | 0                               | 1     | Х                           | A Slave byte was transmitted; error detected.                                         | No action required (expecting Master to end transfer). | 0     | 0            | Х                              | 0001         |                                               |                                                                    |   |   |        |      |

| Slav                       | 0101                        | 0                               | Х     | Х                           | An illegal STOP or bus error was detected while a Slave Transmission was in progress. | Clear STO.                                             | 0     | 0            | Х                              | _            |                                               |                                                                    |   |   |        |      |

|                            | 0 0 >                       |                                 | 0 0 X |                             | 0 0 X                                                                                 |                                                        | 0 0 X |              | 0 0                            |              | A slave address + R/W was received; ACK sent. | If Write, Set ACK for first data byte.  If Read, Load SMB0DAT with | 0 | 0 | 1<br>X | 0000 |

|                            |                             |                                 |       |                             | rosorros, rearesona                                                                   | data byte                                              | U     |              |                                | 0100         |                                               |                                                                    |   |   |        |      |

|                            | 0010                        |                                 |       |                             | Lost arbitration as master;                                                           | If Write, Set ACK for first data byte.                 | 0     | 0            | 1                              | 0000         |                                               |                                                                    |   |   |        |      |

| iver                       |                             | 0                               | 1     | X                           | slave address + R/W received;<br>ACK sent.                                            | If Read, Load SMB0DAT with data byte                   | 0     | 0            | Х                              | 0100         |                                               |                                                                    |   |   |        |      |

| Sec                        |                             |                                 |       |                             |                                                                                       | Reschedule failed transfer                             | 1     | 0            | Х                              | 1110         |                                               |                                                                    |   |   |        |      |

| Slave Receiver             | 0001                        | 0                               | 0     | Х                           | A STOP was detected while addressed as a Slave Transmitter or Slave Receiver.         | Clear STO.                                             | 0     | 0            | X                              |              |                                               |                                                                    |   |   |        |      |

|                            |                             | 0                               | 1     | Х                           | Lost arbitration while attempting a STOP.                                             | No action required (transfer complete/aborted).        | 0     | 0            | 0                              |              |                                               |                                                                    |   |   |        |      |

|                            | 0000                        | •                               | •     | ~                           | A clave bute week received                                                            | Set ACK for next data byte;<br>Read SMB0DAT.           | 0     | 0            | 1                              | 0000         |                                               |                                                                    |   |   |        |      |

|                            | 0000                        | 0                               | 0     | ^                           | A slave byte was received.                                                            | Set NACK for next data byte;<br>Read SMB0DAT.          | 0     | 0            | 0                              | 0000         |                                               |                                                                    |   |   |        |      |

| ion                        | 0010                        | 0                               | 1     | Х                           | Lost arbitration while attempt-                                                       | Abort failed transfer.                                 | 0     | 0            | Х                              | _            |                                               |                                                                    |   |   |        |      |

| diti                       | 0010                        | )                               | Ľ     |                             | ing a repeated START.                                                                 | Reschedule failed transfer.                            | 1     | 0            | Χ                              | 1110         |                                               |                                                                    |   |   |        |      |

| ပ္ပ                        | 0001                        | 0 1 X Lost arbitration due to a |       |                             | Abort failed transfer.                                                                | 0                                                      | 0     | Χ            | _                              |              |                                               |                                                                    |   |   |        |      |

| ō                          | 0001                        |                                 |       |                             | detected STOP.                                                                        | Reschedule failed transfer.                            | 1     | 0            | Χ                              | 1110         |                                               |                                                                    |   |   |        |      |

| <b>Bus Error Condition</b> | 0000                        | 0                               | 1     | Х                           | Lost arbitration while transmit-                                                      | Abort failed transfer.                                 | 0     | 0            | Χ                              | _            |                                               |                                                                    |   |   |        |      |

| Bus                        | 3300                        | ting a data byte as master.     |       | ting a data byte as master. | Reschedule failed transfer.                                                           | 1                                                      | 0     | Х            | 1110                           |              |                                               |                                                                    |   |   |        |      |

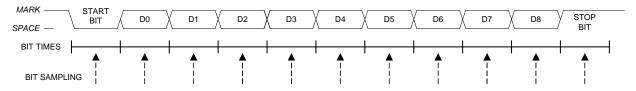

#### 27.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to 1. If the above conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set to 1. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to 1.

Figure 27.5. 9-Bit UART Timing Diagram

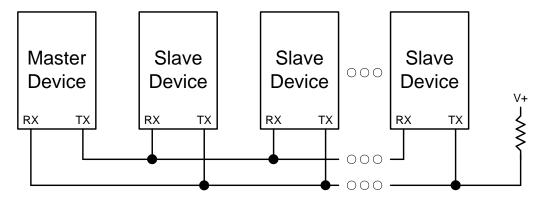

## 27.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 27.6. UART Multi-Processor Mode Interconnect Diagram

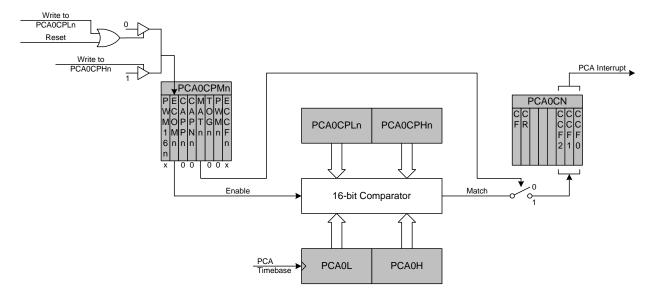

#### 29.3.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 29.5. PCA Software Timer Mode Diagram

# SFR Definition 29.4. PCA0CPMn: PCA0 Capture/Compare Mode

| Bit   | 7      | 7 6 5 |       | 4     | 3    | 2    | 1    | 0     |

|-------|--------|-------|-------|-------|------|------|------|-------|

| Name  | PWM16n | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn |

| Туре  | R/W    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W   |

| Reset | 0      | 0     | 0     | 0     | 0    | 0    | 0    | 0     |

SFR Addresses: PCA0CPM0 = 0xDA, PCA0CPM1 = 0xDB, PCA0CPM2 = 0xDC

|       |                         | PCA0CPM0 = 0xDA, PCA0CPM1 = 0xDB, PCA0CPM2 = 0xDC                                                                                                                             |  |  |  |  |  |  |

|-------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit   | Name                    | Function                                                                                                                                                                      |  |  |  |  |  |  |

| 7     | PWM16n                  | 16-bit Pulse Width Modulation Enable.                                                                                                                                         |  |  |  |  |  |  |

|       |                         | This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.                                                                                                     |  |  |  |  |  |  |

|       |                         | 0: 8 to 15-bit PWM selected.                                                                                                                                                  |  |  |  |  |  |  |

|       |                         | 1: 16-bit PWM selected.                                                                                                                                                       |  |  |  |  |  |  |

| 6     | ECOMn                   | Comparator Function Enable.                                                                                                                                                   |  |  |  |  |  |  |

|       |                         | This bit enables the comparator function for PCA module n when set to 1.                                                                                                      |  |  |  |  |  |  |

| 5     | CAPPn                   | Capture Positive Function Enable.                                                                                                                                             |  |  |  |  |  |  |

|       |                         | This bit enables the positive edge capture for PCA module n when set to 1.                                                                                                    |  |  |  |  |  |  |

| 4     | CAPNn                   | Capture Negative Function Enable.                                                                                                                                             |  |  |  |  |  |  |

|       |                         | This bit enables the negative edge capture for PCA module n when set to 1.                                                                                                    |  |  |  |  |  |  |

| 3     | MATn                    | Match Function Enable.                                                                                                                                                        |  |  |  |  |  |  |

|       |                         | This bit enables the match function for PCA module n when set to 1. When enabled,                                                                                             |  |  |  |  |  |  |

|       |                         | matches of the PCA counter with a module's capture/compare register cause the CCFn                                                                                            |  |  |  |  |  |  |

|       |                         | bit in PCA0MD register to be set to logic 1.                                                                                                                                  |  |  |  |  |  |  |

| 2     | TOGn                    | Toggle Function Enable.                                                                                                                                                       |  |  |  |  |  |  |

|       |                         | This bit enables the toggle function for PCA module n when set to 1. When enabled,                                                                                            |  |  |  |  |  |  |

|       |                         | matches of the PCA counter with a module's capture/compare register cause the logic level on the CEXn pin to toggle. If the PWMn bit is also set to logic 1, the module oper- |  |  |  |  |  |  |

|       |                         | ates in Frequency Output Mode.                                                                                                                                                |  |  |  |  |  |  |

| 1     | PWMn                    | Pulse Width Modulation Mode Enable.                                                                                                                                           |  |  |  |  |  |  |

| '     | LAAIAIII                | This bit enables the PWM function for PCA module n when set to 1. When enabled, a                                                                                             |  |  |  |  |  |  |

|       |                         | pulse width modulated signal is output on the CEXn pin. 8 to 15-bit PWM is used if                                                                                            |  |  |  |  |  |  |

|       |                         | PWM16n is cleared; 16-bit mode is used if PWM16n is set to logic 1. If the TOGn bit is                                                                                        |  |  |  |  |  |  |

|       |                         | also set, the module operates in Frequency Output Mode.                                                                                                                       |  |  |  |  |  |  |

| 0     | ECCFn                   | Capture/Compare Flag Interrupt Enable.                                                                                                                                        |  |  |  |  |  |  |

|       |                         | This bit sets the masking of the Capture/Compare Flag (CCFn) interrupt.                                                                                                       |  |  |  |  |  |  |

|       |                         | 0: Disable CCFn interrupts.                                                                                                                                                   |  |  |  |  |  |  |

|       |                         | 1: Enable a Capture/Compare Flag interrupt request when CCFn is set.                                                                                                          |  |  |  |  |  |  |

| Note: |                         | VDTE bit is set to 1, the PCA0CPM2 register cannot be modified, and module 2 acts as the                                                                                      |  |  |  |  |  |  |

|       | -                       | mer. To change the contents of the PCA0CPM2 register or the function of module 2, the Watchdog                                                                                |  |  |  |  |  |  |

|       | Timer must be disabled. |                                                                                                                                                                               |  |  |  |  |  |  |