Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Not For New Designs                                             |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f818-gmr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

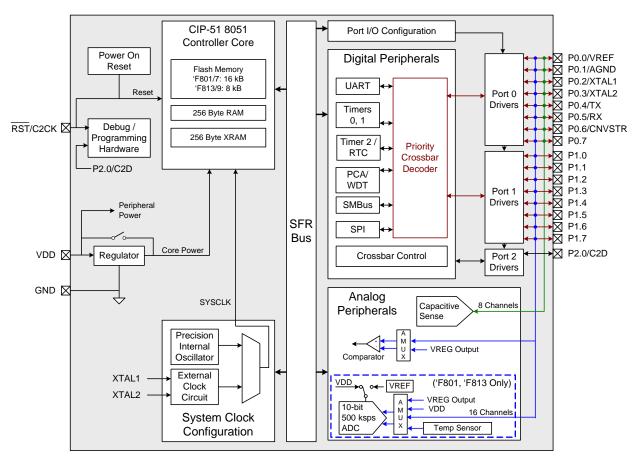

Figure 1.2. C8051F801, C8051F807, C8051F813, C8051F819 Block Diagram

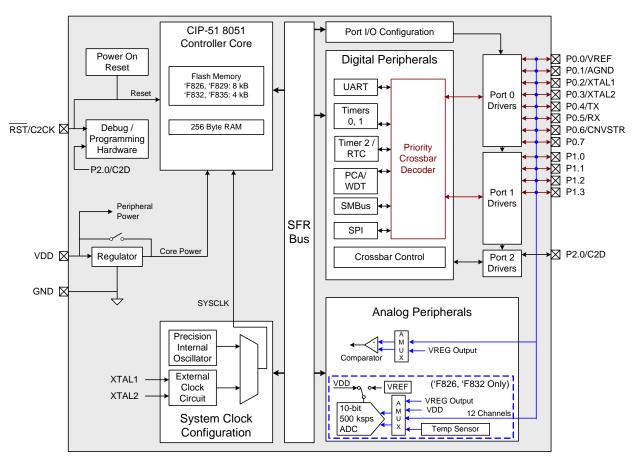

Figure 1.9. C8051F826, C8051F829, C8051F832, C8051F835 Block Diagram

## 7. Electrical Characteristics

# 7.1. Absolute Maximum Specifications

**Table 7.1. Absolute Maximum Ratings**

| Parameter                                              | Conditions | Min         | Тур | Max | Units |

|--------------------------------------------------------|------------|-------------|-----|-----|-------|

| Ambient temperature under bias                         |            | <b>-</b> 55 | _   | 125 | °C    |

| Storage Temperature                                    |            | -65         | _   | 150 | °C    |

| Voltage on RST or any Port I/O Pin with respect to GND |            | -0.3        | _   | 5.8 | V     |

| Voltage on V <sub>DD</sub> with respect to GND         |            | -0.3        | _   | 4.2 | V     |

| Maximum Total current through V <sub>DD</sub> and GND  |            | _           | _   | 500 | mA    |

| Maximum output current sunk by RST or any Port pin     |            | _           | _   | 100 | mA    |

**Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### Table 7.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameters          | Conditions                                     | Min                    | Тур                   | Max | Units |

|---------------------|------------------------------------------------|------------------------|-----------------------|-----|-------|

| Output High Voltage | I <sub>OH</sub> = -3 mA, Port I/O push-pull    | $V_{DD} - 0.7$         | _                     | —   | V     |

|                     | $I_{OH} = -10 \mu A$ , Port I/O push-pull      | V <sub>DD</sub> - 0.1  |                       |     | V     |

|                     | $I_{OH} = -10 \text{ mA}$ , Port I/O push-pull |                        | V <sub>DD</sub> - 0.8 | _   | V     |

| Output Low Voltage  | I <sub>OL</sub> = 8.5 mA                       | _                      | _                     | 0.6 | V     |

|                     | $I_{OL} = 10 \mu A$                            | _                      | _                     | 0.1 | V     |

|                     | $I_{OL} = 25 \text{ mA}$                       | _                      | 1.0                   | _   | V     |

| Input High Voltage  |                                                | 0.75 x V <sub>DD</sub> | _                     | _   | V     |

| Input Low Voltage   |                                                | _                      | _                     | 0.6 | V     |

| Input Leakage       | Weak Pullup Off                                | -1                     |                       | 1   | μA    |

| Current             | Weak Pullup On, V <sub>IN</sub> = 0 V          | _                      | 15                    | 50  | μΑ    |

### **Table 7.4. Reset Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                                             | Conditions                                                                      | Min                    | Тур  | Max                   | Units    |

|-------------------------------------------------------|---------------------------------------------------------------------------------|------------------------|------|-----------------------|----------|

| RST Output Low Voltage                                | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 1.8 V to 3.6 V                   | _                      | _    | 0.6                   | V        |

| RST Input High Voltage                                |                                                                                 | 0.75 x V <sub>DD</sub> | _    | _                     | V        |

| RST Input Low Voltage                                 |                                                                                 | _                      | _    | 0.3 x V <sub>DD</sub> | $V_{DD}$ |

| RST Input Pullup Current                              | RST = 0.0 V                                                                     | _                      | 25   | 50                    | μA       |

| V <sub>DD</sub> POR Ramp Time                         |                                                                                 | _                      | _    | 1                     | ms       |

| V <sub>DD</sub> Monitor Threshold (V <sub>RST</sub> ) |                                                                                 | 1.7                    | 1.75 | 1.8                   | V        |

| Missing Clock Detector<br>Timeout                     | Time from last system clock rising edge to reset initiation                     | 100                    | 500  | 1000                  | μs       |

| Reset Time Delay                                      | Delay between release of any reset source and code execution at location 0x0000 | _                      | _    | 30                    | μs       |

| Minimum RST Low Time to Generate a System Reset       |                                                                                 | 15                     | _    | _                     | μs       |

| V <sub>DD</sub> Monitor Turn-on Time                  | $V_{DD} = V_{RST} - 0.1 V$                                                      | _                      | 50   |                       | μs       |

| V <sub>DD</sub> Monitor Supply Current                |                                                                                 | _                      | 20   | 30                    | μΑ       |

## **Table 7.5. Internal Voltage Regulator Electrical Characteristics**

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter           | Conditions | Min | Тур | Max | Units |

|---------------------|------------|-----|-----|-----|-------|

| Input Voltage Range |            | 1.8 | _   | 3.6 | V     |

| Bias Current        |            | _   | 50  | 65  | μA    |

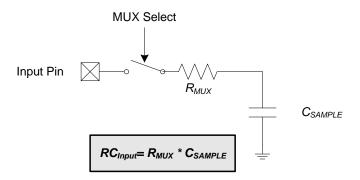

#### 8.3.3. Settling Time Requirements

A minimum tracking time is required before each conversion to ensure that an accurate conversion is performed. This tracking time is determined by any series impedance, including the AMUX0 resistance, the the ADC0 sampling capacitance, and the accuracy required for the conversion. In delayed tracking mode, three SAR clocks are used for tracking at the start of every conversion. For many applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 8.3 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 8.1. See Table 7.9 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

### **Equation 8.1. ADC0 Settling Time Requirements**

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance. n is the ADC resolution in bits (10).

Note: See electrical specification tables for  $R_{\text{MUX}}$  and  $C_{\text{SAMPLE}}$  parameters.

Figure 8.3. ADC0 Equivalent Input Circuits

# SFR Definition 8.9. ADC0MX: AMUX0 Channel Select

| Bit   | 7 | 6 | 5 | 4          | 3 | 2 | 1 | 0 |

|-------|---|---|---|------------|---|---|---|---|

| Name  |   |   |   | AMX0P[3:0] |   |   |   |   |

| Туре  | R | R | R | R/W        |   |   |   |   |

| Reset | 0 | 0 | 0 | 1          | 1 | 1 | 1 | 1 |

### SFR Address = 0xBB

| Bit | Name       |                    | Function                        |                |  |  |

|-----|------------|--------------------|---------------------------------|----------------|--|--|

| 7:5 | Unused     | Read = 000b; Write | e = Don't Care.                 |                |  |  |

| 4:0 | AMX0P[4:0] | AMUX0 Positive Ir  | AMUX0 Positive Input Selection. |                |  |  |

|     |            |                    | 20-Pin and 24-Pin Devices       | 16-Pin Devices |  |  |

|     |            | 00000:             | P0.0                            | P0.0           |  |  |

|     |            | 00001:             | P0.1                            | P0.1           |  |  |

|     |            | 00010:             | P0.2                            | P0.2           |  |  |

|     |            | 00011:             | P0.3                            | P0.3           |  |  |

|     |            | 00100:             | P0.4                            | P0.4           |  |  |

|     |            | 00101:             | P0.5                            | P0.5           |  |  |

|     |            | 00110:             | P0.6                            | P0.6           |  |  |

|     |            | 00111:             | P0.7                            | P0.7           |  |  |

|     |            | 01000              | P1.0                            | P1.0           |  |  |

|     |            | 01001              | P1.1                            | P1.1           |  |  |

|     |            | 01010              | P1.2                            | P1.2           |  |  |

|     |            | 01011              | P1.3                            | P1.3           |  |  |

|     |            | 01100              | P1.4                            | Reserved.      |  |  |

|     |            | 01101              | P1.5                            | Reserved.      |  |  |

|     |            | 01110              | P1.6                            | Reserved.      |  |  |

|     |            | 01111              | P1.7                            | Reserved.      |  |  |

|     |            | 10000:             | Temp Sensor                     | Temp Sensor    |  |  |

|     |            | 10001:             | VREG Output                     | VREG Output    |  |  |

|     |            | 10010:             | VDD                             | VDD            |  |  |

|     |            | 10011:             | GND                             | GND            |  |  |

|     |            | 10100 – 11111:     | no input selected               |                |  |  |

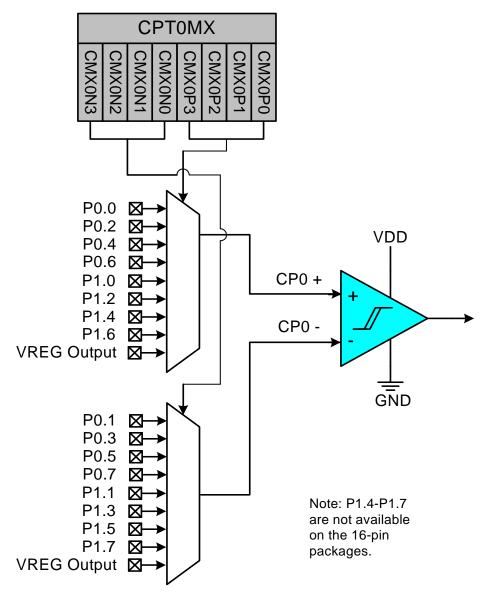

### 12.1. Comparator Multiplexer

C8051F80x-83x devices include an analog input multiplexer to connect Port I/O pins to the comparator inputs. The Comparator0 inputs are selected in the CPT0MX register (SFR Definition 12.3). The CMX0P3—CMX0P0 bits select the Comparator0 positive input; the CMX0N3—CMX0N0 bits select the Comparator0 negative input. **Important Note About Comparator Inputs:** The Port pins selected as comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see Section "23.6. Special Function Registers for Accessing and Configuring Port I/O" on page 152).

Figure 12.3. Comparator Input Multiplexer Block Diagram

# **Table 17.2. Special Function Registers (Continued)**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register    | Address | Description                       | Page |

|-------------|---------|-----------------------------------|------|

| P1MAT 0xED  |         | P1 Match                          | 152  |

| P1MDIN 0xF2 |         | Port 1 Input Mode Configuration   | 156  |

| P1MDOUT     | 0xA5    | Port 1 Output Mode Configuration  | 156  |

| P1SKIP      | 0xD5    | Port 1 Skip                       | 157  |

| P2          | 0xA0    | Port 2 Latch                      | 157  |

| P2MDOUT     | 0xA6    | Port 2 Output Mode Configuration  | 158  |

| PCA0CN      | 0xD8    | PCA Control                       | 238  |

| PCA0CPH0    | 0xFC    | PCA Capture 0 High                | 243  |

| PCA0CPH1    | 0xEA    | PCA Capture 1 High                | 243  |

| PCA0CPH2    | 0xEC    | PCA Capture 2 High                | 243  |

| PCA0CPL0    | 0xFB    | PCA Capture 0 Low                 | 243  |

| PCA0CPL1    | 0xE9    | PCA Capture 1 Low                 | 243  |

| PCA0CPL2    | 0xEB    | PCA Capture 2 Low                 | 243  |

| PCA0CPM0    | 0xDA    | PCA Module 0 Mode Register        | 241  |

| PCA0CPM1    | 0xDB    | PCA Module 1 Mode Register        | 241  |

| PCA0CPM2    | 0xDC    | PCA Module 2 Mode Register        | 241  |

| PCA0H       | 0xFA    | PCA Counter High                  | 242  |

| PCA0L       | 0xF9    | PCA Counter Low                   | 242  |

| PCA0MD      | 0xD9    | PCA Mode                          | 239  |

| PCA0PWM     | 0xF7    | PCA PWM Configuration             | 240  |

| PCON        | 0x87    | Power Control                     | 122  |

| PSCTL       | 0x8F    | Program Store R/W Control         | 118  |

| PSW         | 0xD0    | Program Status Word               | 91   |

| REF0CN      | 0xD1    | Voltage Reference Control         | 62   |

| REG0CN      | 0xC9    | Voltage Regulator Control         | 64   |

| REVID 0xB6  |         | Revision ID                       | 96   |

| RSTSRC 0xEF |         | Reset Source Configuration/Status | 128  |

# SFR Definition 19.1. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

### SFR Address =0x8F

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1   | PSEE   | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |        | Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.  0: Flash program memory erasure disabled.  1: Flash program memory erasure enabled. |

| 0   | PSWE   | Program Store Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |        | Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.  0: Writes to Flash program memory disabled.  1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.                                                                                                                                                     |

## 21.5. Comparator Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

### 21.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "29.4. Watchdog Timer Mode" on page 236; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to '1'. The state of the RST pin is unaffected by this reset.

#### 21.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above address 0x3DFF.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above address 0x3DFF.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0x3DFF.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "19.3. Security Options" on page 114).

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 21.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

# SFR Definition 21.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | C0RSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

### SFR Address = 0xEF

| Bit   | Name       | Description                                                                                    | Write                                                                                                                                                                           | Read                                                                                                                                           |

|-------|------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                        | Don't care.                                                                                                                                                                     | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                        | N/A                                                                                                                                                                             | Set to 1 if Flash read/write/erase error caused the last reset.                                                                                |

| 5     | C0RSEF     | Comparator0 Reset Enable and Flag.                                                             | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                           | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                                 | Writing a 1 forces a system reset.                                                                                                                                              | Set to 1 if last reset was caused by a write to SWRSF.                                                                                         |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                     | N/A                                                                                                                                                                             | Set to 1 if Watchdog Timer overflow caused the last reset.                                                                                     |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                     | Writing a 1 enables the Missing Clock Detector. The MCD triggers a reset if a missing clock condition is detected.                                                              | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the V <sub>DD</sub> monitor as a reset source. Writing 1 to this bit before the V <sub>DD</sub> monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                             | N/A                                                                                                                                                                             | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                           | s register                                                                                                                                                                      | 1                                                                                                                                              |

Table 23.1. Port I/O Assignment for Analog Functions

| Analog Function                                       | Potentially Assignable<br>Port Pins | SFR(s) used for<br>Assignment  |

|-------------------------------------------------------|-------------------------------------|--------------------------------|

| ADC Input                                             | P0.0-P1.7                           | ADC0MX, PnSKIP,<br>PnMDIN      |

| Comparator0 Input                                     | P0.0-P1.7                           | CPT0MX, PnSKIP,<br>PnMDIN      |

| CS0 Input                                             | P0.0–P1.7                           | CS0MX, CS0SS,<br>CS0SE, PnMDIN |

| Voltage Reference (VREF0)                             | P0.0                                | REF0CN, P0SKIP,<br>PnMDIN      |

| Ground Reference (AGND)                               | P0.1                                | REF0CN, P0SKIP                 |

| External Oscillator in Crystal Mode (XTAL1)           | P0.2                                | OSCXCN, POSKIP,<br>POMDIN      |

| External Oscillator in RC, C, or Crystal Mode (XTAL2) | P0.3                                | OSCXCN, POSKIP,<br>POMDIN      |

#### 23.2.2. Assigning Port I/O Pins to Digital Functions

Any Port pins not assigned to analog functions may be assigned to digital functions or used as GPIO. Most digital functions rely on the Crossbar for pin assignment; however, some digital functions bypass the Crossbar in a manner similar to the analog functions listed above. **Port pins used by these digital functions and any Port pins selected for use as GPIO should have their corresponding bit in PnSKIP set to 1.** Table 23.2 shows all available digital functions and the potential mapping of Port I/O to each digital function.

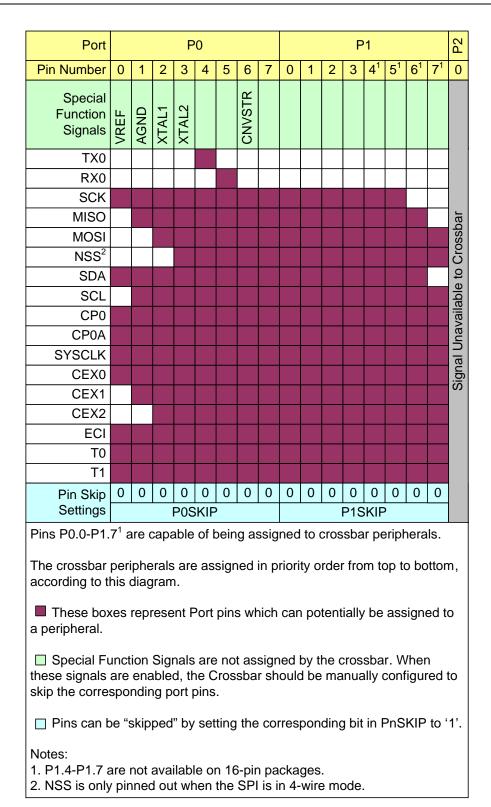

### 23.3. Priority Crossbar Decoder

The Priority Crossbar Decoder assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

Because of the nature of the Priority Crossbar Decoder, not all peripherals can be located on all port pins. Figure 23.4 maps peripherals to the potential port pins on which the peripheral I/O can appear.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to P0.0 if VREF is used, P0.1 if AGND is used, P0.3 and/or P0.2 if the external oscillator circuit is enabled, P0.6 if the ADC is configured to use the external conversion start signal (CNVSTR), and any selected ADC, Comparator, or Capacitive Sense inputs. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin.

Registers XBR0, XBR1, and XBR2 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when a UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

Figure 23.4. Priority Crossbar Decoder Potential Pin Assignments

## 25.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 25.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 25.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 25.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

### 25.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- 1. NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- 2. NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- 3. NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 25.2, Figure 25.3, and Figure 25.4 for typical connection diagrams of the various operational modes. **Note that the setting of NSSMD bits affects the pinout of the device.** When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "23. Port Input/Output" on page 138 for general purpose port I/O and crossbar information.

#### 25.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag

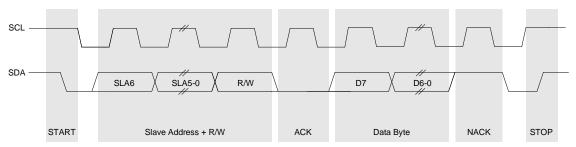

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 26.3 illustrates a typical SMBus transaction.

Figure 26.3. SMBus Transaction

#### 26.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 26.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "26.3.5. SCL High (SMBus Free) Timeout" on page 183). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 26.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 26.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMBOCF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to

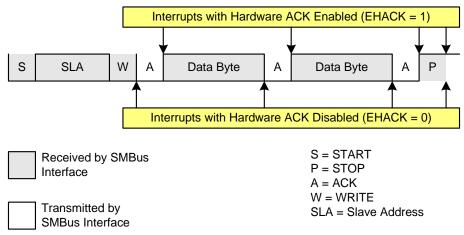

#### 26.5.3. Write Sequence (Slave)

195

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 26.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the "data byte transferred" interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 26.7. Typical Slave Write Sequence

### 29.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high-speed output, frequency output, 8-bit through 15-bit pulse width modulator, or 16-bit pulse width modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 29.2 summarizes the bit settings in the PCA0CPMn and PCA0PWM registers used to select the PCA capture/compare module's operating mode. Note that all modules set to use 8-bit through 15-bit PWM mode must use the same cycle length (8–15 bits). Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

Table 29.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules 1,2,3,4,5,6

| Operational Mode                              |   |   |   | PCA0CPMn |   |   |   |   |   |   | PCA0PWM |   |   |     |  |  |

|-----------------------------------------------|---|---|---|----------|---|---|---|---|---|---|---------|---|---|-----|--|--|

| Bit Number                                    | 7 | 6 | 5 | 4        | 3 | 2 | 1 | 0 | 7 | 6 | 5       | 4 | 3 | 2-0 |  |  |

| Capture triggered by positive edge on CEXn    | Χ | Χ | 1 | 0        | 0 | 0 | 0 | Α | 0 | Χ | В       | Χ | Χ | XXX |  |  |

| Capture triggered by negative edge on CEXn    | Χ | Х | 0 | 1        | 0 | 0 | 0 | Α | 0 | Х | В       | Χ | Χ | XXX |  |  |

| Capture triggered by any transition on CEXn   | Χ | Х | 1 | 1        | 0 | 0 | 0 | Α | 0 | Х | В       | Χ | Χ | XXX |  |  |

| Software Timer                                | Χ | С | 0 | 0        | 1 | 0 | 0 | Α | 0 | Χ | В       | Χ | Χ | XXX |  |  |

| High Speed Output                             | Χ | С | 0 | 0        | 1 | 1 | 0 | Α | 0 | Χ | В       | Χ | Χ | XXX |  |  |

| Frequency Output                              | Χ | С | 0 | 0        | 0 | 1 | 1 | Α | 0 | Χ | В       | Χ | Χ | XXX |  |  |

| 8-Bit Pulse Width Modulator <sup>7</sup>      | 0 | С | 0 | 0        | Е | 0 | 1 | Α | 0 | Χ | В       | Χ | Χ | 000 |  |  |

| 9-Bit Pulse Width Modulator <sup>7</sup>      | 0 | С | 0 | 0        | Ε | 0 | 1 | Α | D | Х | В       | Χ | Χ | 001 |  |  |

| 10-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0 | 0        | Е | 0 | 1 | Α | D | Х | В       | Χ | Χ | 010 |  |  |

| 11-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0 | 0        | Е | 0 | 1 | Α | D | Х | В       | Χ | Χ | 011 |  |  |

| 12-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0 | 0        | Ε | 0 | 1 | Α | D | Х | В       | Χ | Χ | 100 |  |  |

| 13-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0 | 0        | Ε | 0 | 1 | Α | D | Х | В       | Χ | Χ | 101 |  |  |

| 14-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0 | 0        | Е | 0 | 1 | Α | D | Х | В       | Χ | Χ | 110 |  |  |

| 15-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0 | 0        | Е | 0 | 1 | Α | D | Χ | В       | Χ | Χ | 111 |  |  |

| 16-Bit Pulse Width Modulator                  | 1 | С | 0 | 0        | Е | 0 | 1 | Α | 0 | Χ | В       | Χ | 0 | XXX |  |  |

| 16-Bit Pulse Width Modulator with Auto-Reload | 1 | С | 0 | 0        | Е | 0 | 1 | Α | D | Χ | В       | Χ | 1 | XXX |  |  |

#### Notes:

228

- **1.** X = Don't Care (no functional difference for individual module if 1 or 0).

- **2.** A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

- 3. B = Enable 8th through 15th bit overflow interrupt (Depends on setting of CLSEL[2:0]).

- **4.** C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

- **5.** D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- 6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

- 7. All modules set to 8-bit through 15-bit PWM mode use the same cycle length setting.

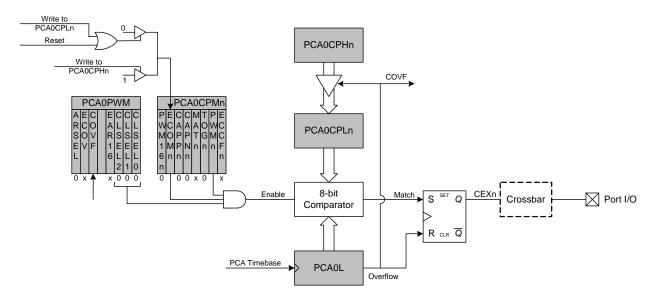

#### 29.3.5.1. 8-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 8-bit PWM mode is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 29.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. This synchronous update feature allows software to asynchronously write a new PWM high time, which will then take effect on the following PWM period.

Setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to 000b enables 8-Bit Pulse Width Modulator mode. If the MATn bit is set to 1, the CCFn flag for the module will be set each time an 8-bit comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 256 PCA clock cycles. The duty cycle for 8-Bit PWM Mode is given in Equation 29.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(256 - PCA0CPHn)}{256}$$

### **Equation 29.2. 8-Bit PWM Duty Cycle**

Using Equation 29.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 29.8. PCA 8-Bit PWM Mode Diagram

# SFR Definition 29.1. PCA0CN: PCA0 Control

| Bit   | 7   | 6   | 5 | 4 | 3 | 2    | 1    | 0    |

|-------|-----|-----|---|---|---|------|------|------|

| Name  | CF  | CR  |   |   |   | CCF2 | CCF1 | CCF0 |

| Туре  | R/W | R/W | R | R | R | R/W  | R/W  | R/W  |

| Reset | 0   | 0   | 0 | 0 | 0 | 0    | 0    | 0    |

SFR Address = 0xD8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CF     | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                          |

|     |        | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000. When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software. |

| 6   | CR     | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                            |

|     |        | This bit enables/disables the PCA Counter/Timer.                                                                                                                                                                                                                                                          |

|     |        | 0: PCA Counter/Timer disabled.                                                                                                                                                                                                                                                                            |

|     |        | 1: PCA Counter/Timer enabled.                                                                                                                                                                                                                                                                             |

| 5:3 | Unused | Read = 000b, Write = Don't care.                                                                                                                                                                                                                                                                          |

| 2   | CCF2   | PCA Module 2 Capture/Compare Flag.                                                                                                                                                                                                                                                                        |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF2 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                        |

| 1   | CCF1   | PCA Module 1 Capture/Compare Flag.                                                                                                                                                                                                                                                                        |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF1 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                        |

| 0   | CCF0   | PCA Module 0 Capture/Compare Flag.                                                                                                                                                                                                                                                                        |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF0 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                        |