# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                   |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 24-QSOP                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f820-gur |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

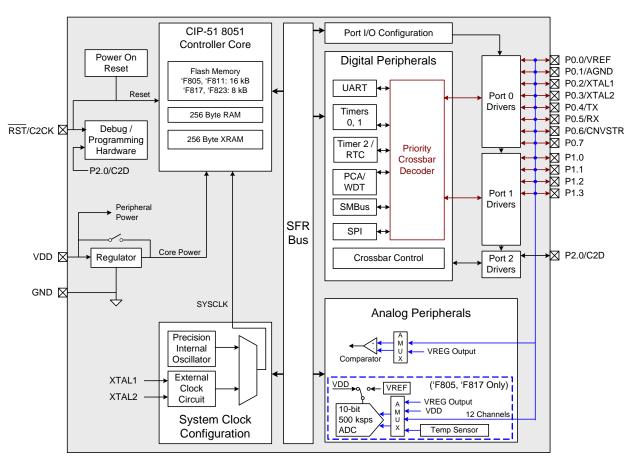

## C8051F80x-83x

Figure 1.6. C8051F805, C8051F811, C8051F817, C8051F823 Block Diagram

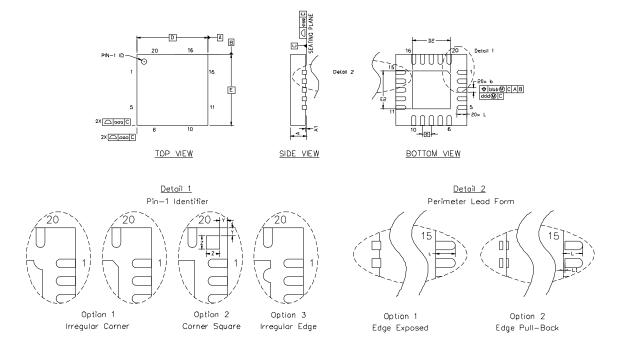

## 4. QFN-20 Package Specifications

## Figure 4.1. QFN-20 Package Drawing

| Min       |           |           |           |           |               |                 |                   |

|-----------|-----------|-----------|-----------|-----------|---------------|-----------------|-------------------|

|           | Тур       | Max       |           | Dimension | Min           | Тур             | Max               |

| 0.80      | 0.90      | 1.00      |           | L         | 0.45          | 0.55            | 0.65              |

| 0.00      | 0.02      | 0.05      |           | L1        | 0.00          | —               | 0.15              |

| 0.18      | 0.25      | 0.30      |           | aaa       | _             | —               | 0.15              |

| 4.00 BSC. |           |           |           | bbb       |               | —               | 0.10              |

| 2.00      | 2.15      | 2.25      |           | ddd       | _             | —               | 0.05              |

|           | 0.50 BSC. |           |           | eee       |               | —               | 0.08              |

| 4.00 BSC. |           |           |           | Z         | _             | 0.43            | _                 |

|           |           |           |           |           |               |                 |                   |

|           | 2.00      | 0.50 BSC. | 0.50 BSC. | 0.50 BSC. | 0.50 BSC. eee | 0.50 BSC. eee — | 0.50 BSC. eee — — |

### Table 4.1. QFN-20 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VGGD except for custom features D2, E2, Z, Y, and L which are toleranced per supplier designation.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## Table 7.10. Power Management Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                 | Conditions | Min | Тур | Мах | Units   |

|---------------------------|------------|-----|-----|-----|---------|

| Idle Mode Wake-Up Time    |            | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time |            | _   | 500 | _   | ns      |

### Table 7.11. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter                | Conditions                      | Min | Тур  | Max | Units |

|--------------------------|---------------------------------|-----|------|-----|-------|

| Linearity                |                                 | -   | 1    | —   | °C    |

| Slope                    |                                 | —   | 2.43 | _   | mV/°C |

| Slope Error*             |                                 |     | ±45  | —   | µV/°C |

| Offset                   | Temp = 0 °C                     | —   | 873  | —   | mV    |

| Offset Error*            | Temp = 0 °C                     |     | 14.5 | —   | mV    |

| *Note: Represents one st | andard deviation from the mean. |     |      |     |       |

### Table 7.12. Voltage Reference Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V; -40 to +85 °C unless otherwise specified.

| Parameter                                       | Conditions                           | Min  | Тур  | Max      | Units |  |  |  |  |

|-------------------------------------------------|--------------------------------------|------|------|----------|-------|--|--|--|--|

| Internal High Speed Reference (REFSL[1:0] = 11) |                                      |      |      |          |       |  |  |  |  |

| Output Voltage                                  | 25 °C ambient                        | 1.55 | 1.65 | 1.75     | V     |  |  |  |  |

| Turn-on Time                                    |                                      | —    | —    | 1.7      | μs    |  |  |  |  |

| Supply Current                                  |                                      |      | 180  |          | μA    |  |  |  |  |

|                                                 | External Reference (REF0E = 0)       |      |      |          |       |  |  |  |  |

| Input Voltage Range                             |                                      | 0    | —    | $V_{DD}$ |       |  |  |  |  |

| Input Current                                   | Sample Rate = 500 ksps; VREF = 3.0 V |      | 7    | _        | μA    |  |  |  |  |

## SFR Definition 13.7. CS0THH: Capacitive Sense Comparator Threshold High Byte

| Bit   | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Name  | CS0THH[7:0] |     |     |     |     |     |     |     |  |  |

| Туре  | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

SFR Address = 0x97

| Bit | Name        | Description                                                                       |

|-----|-------------|-----------------------------------------------------------------------------------|

| 7:0 | CS0THH[7:0] | CS0 Comparator Threshold High Byte.                                               |

|     |             | High byte of the 16-bit value compared to the Capacitive Sense conversion result. |

## SFR Definition 13.8. CS0THL: Capacitive Sense Comparator Threshold Low Byte

| Bit   | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Name  | CS0THL[7:0] |     |     |     |     |     |     |     |  |  |

| Туре  | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

SFR Address = 0x96

| Bit | Name        | Description                                                                      |

|-----|-------------|----------------------------------------------------------------------------------|

| 7:0 | CS0THL[7:0] | CS0 Comparator Threshold Low Byte.                                               |

|     |             | Low byte of the 16-bit value compared to the Capacitive Sense conversion result. |

| Mnemonic                                                         | Description                                         | Bytes | Clock<br>Cycles |

|------------------------------------------------------------------|-----------------------------------------------------|-------|-----------------|

| ANL C, bit                                                       | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit                                                      | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit                                                       | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit                                                      | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit                                                       | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C                                                       | Move Carry to direct bit                            | 2     | 2               |

| JC rel                                                           | Jump if Carry is set                                | 2     | 2/3             |

| JNC rel                                                          | Jump if Carry is not set                            | 2     | 2/3             |

| JB bit, rel                                                      | Jump if direct bit is set                           | 3     | 3/4             |

| JNB bit, rel                                                     | Jump if direct bit is not set                       | 3     | 3/4             |

| JBC bit, rel                                                     | Jump if direct bit is set and clear bit             | 3     | 3/4             |

| Program Branching                                                |                                                     |       |                 |

| ACALL addr11                                                     | Absolute subroutine call                            | 2     | 3               |

| LCALL addr16                                                     | Long subroutine call                                | 3     | 4               |

| RET                                                              | Return from subroutine                              | 1     | 5               |

| RETI                                                             | Return from interrupt                               | 1     | 5               |

| AJMP addr11                                                      | Absolute jump                                       | 2     | 3               |

| LJMP addr16                                                      | Long jump                                           | 3     | 4               |

| SJMP rel                                                         | Short jump (relative address)                       | 2     | 3               |

| JMP @A+DPTR                                                      | Jump indirect relative to DPTR                      | 1     | 3               |

| JZ rel                                                           | Jump if A equals zero                               | 2     | 2/3             |

| JNZ rel                                                          | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel                                              | Compare direct byte to A and jump if not equal      | 3     | 4/5             |

| CJNE A, #data, rel                                               | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel                                              | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel Compare immediate to indirect and jum equal |                                                     | 3     | 4/5             |

| DJNZ Rn, rel                                                     | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel                                                 | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                                                              | No operation                                        | 1     | 1               |

## SFR Definition 14.5. B: B Register

| -     |              | -             |       |    |   |   |   |   |  |  |

|-------|--------------|---------------|-------|----|---|---|---|---|--|--|

| Bit   | 7            | 6             | 5     | 4  | 3 | 2 | 1 | 0 |  |  |

| Nam   | e            | B[7:0]        |       |    |   |   |   |   |  |  |

| Туре  | •            |               |       | R/ | W |   |   |   |  |  |

| Rese  | et 0         | 0             | 0     | 0  | 0 | 0 | 0 | 0 |  |  |

| SFR A | ddress = 0xF | 0; Bit-Addres | sable |    |   |   |   |   |  |  |

| Bit   | Name         | Function      |       |    |   |   |   |   |  |  |

| 7:0   | B[7:0]       | B Register.   |       |    |   |   |   |   |  |  |

| This register serves as a second accumulator for certain arithmetic operations. |

|---------------------------------------------------------------------------------|

| I This redister serves as a second accumulator for certain animmetic operations |

|                                                                                 |

## 18. Interrupts

The C8051F80x-83x includes an extended interrupt system supporting a total of 15 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE–EIE1). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

## SFR Definition 18.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7        | 6        | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|----------|----------|------|-------|-------|--------|------|-------|

| Name  | Reserved | Reserved | ECP0 | EADC0 | EPCA0 | EWADC0 | EMAT | ESMB0 |

| Туре  | W        | W        | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0        | 0        | 0    | 0     | 0     | 0      | 0    | 0     |

SFR Address = 0xE6

| Bit | Name     | Function                                                                                                                                                                                                                                                                          |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved | Must write 0.                                                                                                                                                                                                                                                                     |

| 6   | Reserved | Reserved.                                                                                                                                                                                                                                                                         |

|     |          | Must write 0.                                                                                                                                                                                                                                                                     |

| 5   | ECP0     | <ul> <li>Enable Comparator0 (CP0) Interrupt.</li> <li>This bit sets the masking of the CP0 rising edge or falling edge interrupt.</li> <li>0: Disable CP0 interrupts.</li> <li>1: Enable interrupt requests generated by the CP0RIF and CP0FIF flags.</li> </ul>                  |

| 4   | EADC0    | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 3   | EPCA0    | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 2   | EWADC0   | <ul> <li>Enable Window Comparison ADC0 interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 1   | EMAT     | Enable Port Match Interrupts.<br>This bit sets the masking of the Port Match event interrupt.<br>0: Disable all Port Match interrupts.<br>1: Enable interrupt requests generated by a Port Match.                                                                                 |

| 0   | ESMB0    | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

## SFR Definition 20.1. PCON: Power Control

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1   | 0    |

|-------|---------|---|---|---|---|---|-----|------|

| Name  | GF[5:0] |   |   |   |   |   |     | IDLE |

| Туре  | R/W     |   |   |   |   |   | R/W | R/W  |

| Reset | 0       | 0 | 0 | 0 |   |   |     |      |

SFR Address = 0x87

| Bit | Name    | Function                                                                                                                                                                                                                                                               |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.                                                                                                                                                                                                                                             |

|     |         | These are general purpose flags for use under software control.                                                                                                                                                                                                        |

| 1   | STOP    | Stop Mode Select.                                                                                                                                                                                                                                                      |

|     |         | Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.<br>1: CPU goes into Stop mode (internal oscillator stopped).                                                                                                                   |

| 0   | IDLE    | IDLE: Idle Mode Select.<br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts,<br>Serial Ports, and Analog Peripherals are still active.) |

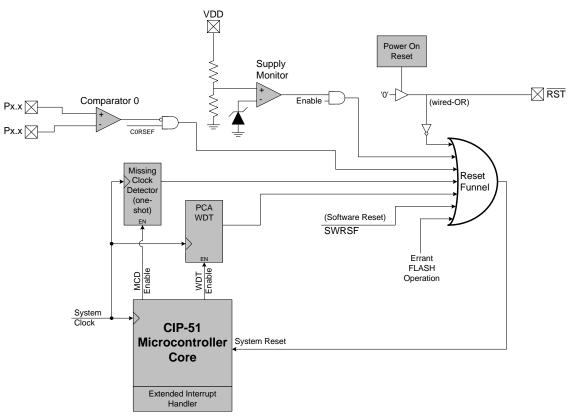

## 21. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 21.1. Reset Sources

| Digital Function                                                    | Potentially Assignable Port Pins                                                                                                                      | SFR(s) used for<br>Assignment |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| UART0, SPI0, SMBus,<br>SYSCLK, PCA0 (CEX0-2<br>and ECI), T0, or T1. | Any Port pin available for assignment by the Crossbar. This includes P0.0 - P1.7 <sup>2</sup> pins which have their PnSKIP bit set to 0. <sup>1</sup> | XBR0, XBR1                    |

| Any pin used for GPIO                                               | P0.0-P2.0 <sup>2</sup>                                                                                                                                | PnSKIP                        |

|                                                                     | ys assign UART0 pins to P0.4 and P0.5.<br>not available on the 16-pin packages.                                                                       |                               |

## Table 23.2. Port I/O Assignment for Digital Functions

### 23.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions

External digital event capture functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The digital event capture functions do not require dedicated pins and will function on both GPIO pins (PnSKIP = 1) and pins in use by the Crossbar (PnSKIP = 0). External digital event capture functions cannot be used on pins configured for analog I/O. Table 23.3 shows all available external digital event capture functions.

### Table 23.3. Port I/O Assignment for External Digital Event Capture Functions

| Digital Function              | Potentially Assignable Port Pins                                    | SFR(s) used for<br>Assignment  |  |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------|--------------------------------|--|--|--|--|--|

| External Interrupt 0          | P0.0–P0.7                                                           | IT01CF                         |  |  |  |  |  |

| External Interrupt 1          | P0.0–P0.7                                                           | IT01CF                         |  |  |  |  |  |

| Port Match                    | P0.0–P1.7 <sup>*</sup>                                              | P0MASK, P0MAT<br>P1MASK, P1MAT |  |  |  |  |  |

| Note: Port pins P1.4–P1.7 are | Note: Port pins P1.4–P1.7 are not available on the 16-pin packages. |                                |  |  |  |  |  |

## 24.1. 16-bit CRC Algorithm

The C8051F80x-83x CRC unit calculates the 16-bit CRC MSB-first, using a poly of 0x1021. The following describes the 16-bit CRC algorithm performed by the hardware:

- 1. XOR the most-significant byte of the current CRC result with the input byte. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x0000 or 0xFFFF).

- 2. If the MSB of the CRC result is set, left-shift the CRC result, and then XOR the CRC result with the polynomial (0x1021).

- 3. If the MSB of the CRC result is not set, left-shift the CRC result.

- 4. Repeat at Step 2 for the number of input bits (8).

For example, the 16-bit C8051F80x-83x CRC algorithm can be described by the following code:

```

unsigned short UpdateCRC (unsigned short CRC_acc, unsigned char CRC_input) {

unsigned char i;

// loop counter

#define POLY 0x1021

// Create the CRC "dividend" for polynomial arithmetic (binary arithmetic

// with no carries)

CRC_acc = CRC_acc ^ (CRC_input << 8);</pre>

// "Divide" the poly into the dividend using CRC XOR subtraction

// CRC_acc holds the "remainder" of each divide

// Only complete this division for 8 bits since input is 1 byte

for (i = 0; i < 8; i++)

{

// Check if the MSB is set (if MSB is 1, then the POLY can "divide"

// into the "dividend")

if ((CRC_acc & 0x8000) == 0x8000)

{

// if so, shift the CRC value, and XOR "subtract" the poly

CRC_acc = CRC_acc << 1;</pre>

CRC_acc ^= POLY;

}

else

{

// if not, just shift the CRC value

CRC_acc = CRC_acc << 1;</pre>

}

}

return CRC_acc; // Return the final remainder (CRC value)

}

```

Table 24.1 lists example input values and the associated outputs using the 16-bit C8051F80x-83x CRC algorithm (an initial value of 0xFFFF is used):

| Input                        | Output |

|------------------------------|--------|

| 0x63                         | 0xBD35 |

| 0xAA, 0xBB, 0xCC             | 0x6CF6 |

| 0x00, 0x00, 0xAA, 0xBB, 0xCC | 0xB166 |

#### Table 24.1. Example 16-bit CRC Outputs

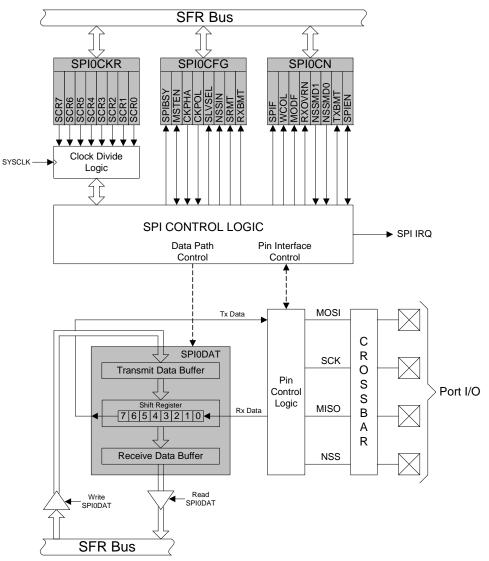

## 25. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

## C8051F80x-83x

#### 26.5.3. Write Sequence (Slave)

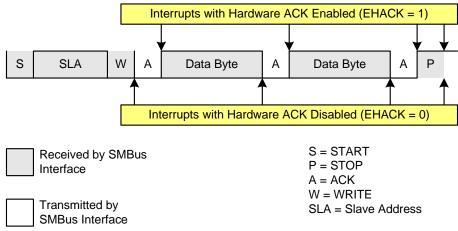

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 26.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the "data byte transferred" interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 26.7. Typical Slave Write Sequence

#### 27.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to 1. If the above conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set to 1. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to 1.

## 28.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section "18.2. Interrupt Register Descriptions" on page 104); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section "18.2. Interrupt Register (Section "18.2. Interrupt Register (Section "18.2. Interrupt Register Descriptions" on page 104); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section "18.2. Interrupt Register Descriptions" on page 104). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 28.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 in TCON is set and an interrupt will occur if Timer 0 interrupts are enabled.

The C/T0 bit in the TMOD register selects the counter/timer's clock source. When C/T0 is set to logic 1, high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register (Refer to Section "23.3. Priority Crossbar Decoder" on page 143 for information on selecting and configuring external I/O pins). Clearing C/T selects the clock defined by the T0M bit in register CKCON. When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 28.1).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 in the TMOD register is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 18.7). Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0 (see Section "18.2. Interrupt Register Descriptions" on page 104), facilitating pulse width measurements

| TR0                  | GATE0 | INT0 | Counter/Timer |  |  |  |  |

|----------------------|-------|------|---------------|--|--|--|--|

| 0                    | Х     | Х    | Disabled      |  |  |  |  |

| 1                    | 0     | Х    | Enabled       |  |  |  |  |

| 1                    | 1     | 0    | Disabled      |  |  |  |  |

| 1                    | 1     | 1    | Enabled       |  |  |  |  |

| Note: X = Don't Care |       |      |               |  |  |  |  |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal INT1 is used with Timer 1; the INT1 polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 18.7).

## SFR Definition 28.2. TCON: Timer Control

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7            | 6                                                                                                                                                                                                                                                                       | 5                                                                                                                                                                                                                                       | 4   | 3        | 2                                | 1   | 0   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|----------------------------------|-----|-----|--|

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TF1          | TR1                                                                                                                                                                                                                                                                     | IE1                                                                                                                                                                                                                                     | IT1 | IE0      | IT0                              |     |     |  |

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W          | R/W                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                     | R/W | R/W      | R/W                              | R/W | R/W |  |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>0</td> <td>0</td> |              |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |     |          |                                  | 0   | 0   |  |

| SFR A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ddress = 0x8 | 38; Bit-Addres                                                                                                                                                                                                                                                          | sable                                                                                                                                                                                                                                   |     |          |                                  |     |     |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Name         |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |     | Function |                                  |     |     |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TF1          | Timer 1 Ov                                                                                                                                                                                                                                                              | erflow Flag                                                                                                                                                                                                                             | •   |          |                                  |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |     |          | his flag can b<br>ors to the Tim |     |     |  |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TR1          | Timer 1 Ru                                                                                                                                                                                                                                                              | n Control.                                                                                                                                                                                                                              |     |          |                                  |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | Timer 1 is e                                                                                                                                                                                                                                                            | Timer 1 is enabled by setting this bit to 1.                                                                                                                                                                                            |     |          |                                  |     |     |  |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TF0          | Timer 0 Overflow Flag.                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                         |     |          |                                  |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                                                                                                                                                                                                                                                         | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                           |     |          |                                  |     |     |  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TR0          | Timer 0 Ru                                                                                                                                                                                                                                                              | n Control.                                                                                                                                                                                                                              |     |          |                                  |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | Timer 0 is e                                                                                                                                                                                                                                                            | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                            |     |          |                                  |     |     |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IE1          | External In                                                                                                                                                                                                                                                             | terrupt 1.                                                                                                                                                                                                                              |     |          |                                  |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | can be clea                                                                                                                                                                                                                                                             | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode. |     |          |                                  |     |     |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IT1          | Interrupt 1                                                                                                                                                                                                                                                             | Type Select                                                                                                                                                                                                                             | t.  |          |                                  |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | This bit selects whether the configured /INT1 interrupt will be edge or level sensitive.<br>/INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see<br>SFR Definition 18.7).<br>0: /INT1 is level triggered.<br>1: /INT1 is edge triggered. |                                                                                                                                                                                                                                         |     |          |                                  |     |     |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IE0          | External In                                                                                                                                                                                                                                                             | terrupt 0.                                                                                                                                                                                                                              |     |          |                                  |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | can be clea                                                                                                                                                                                                                                                             | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode. |     |          |                                  |     |     |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IT0          | Interrupt 0                                                                                                                                                                                                                                                             | Type Select                                                                                                                                                                                                                             | •   |          |                                  |     |     |  |

This bit selects whether the configured INT0 interrupt will be edge or level sensitive.

INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFR Definition 18.7).

0: INT0 is level triggered.

1: INT0 is edge triggered.

## 29.2. PCA0 Interrupt Sources

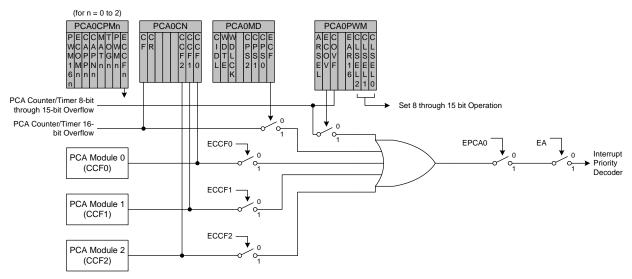

Figure 29.3 shows a diagram of the PCA interrupt tree. There are five independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th through 15th bit of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, and CCF2), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit in the IE register and the EPCA0 bit in the EIE1 register to logic 1.

Figure 29.3. PCA Interrupt Block Diagram

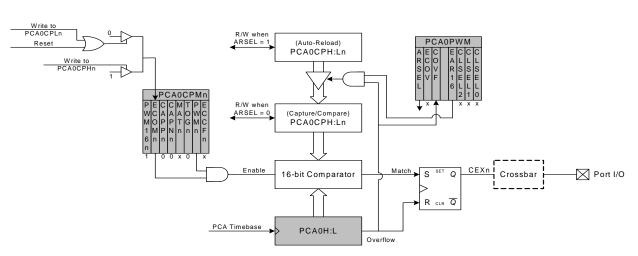

#### 29.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8-bit through 15-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register.

The duty cycle of the PWM output signal can be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0. This synchronous update feature allows software to asynchronously write a new PWM high time, which will then take effect on the following PWM period.

For backwards-compatibility with the 16-bit PWM mode available on other devices, the PWM duty cycle can also be changed without using the "Auto-Reload" register. To output a varying duty cycle without using the "Auto-Reload" register, new value writes should be synchronized with PCA CCFn match interrupts. Match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 29.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(65536 - PCA0CPn)}{65536}$$

**Equation 29.4. 16-Bit PWM Duty Cycle** Using Equation 29.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is

0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 29.10. PCA 16-Bit PWM Mode

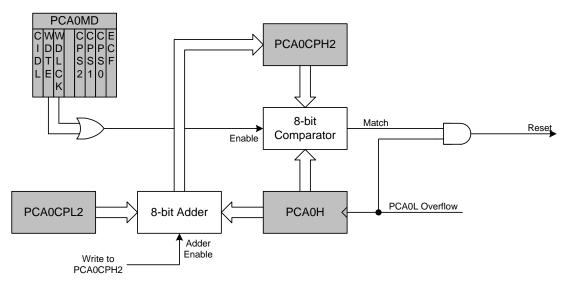

## 29.4. Watchdog Timer Mode

A programmable watchdog timer (WDT) function is available through the PCA Module 2. The WDT is used to generate a reset if the time between writes to the WDT update register (PCA0CPH2) exceed a specified limit. The WDT can be configured and enabled/disabled as needed by software.