# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f822-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 23.1. Port I/O Modes of Operation                                           |     |

|----|-----------------------------------------------------------------------------|-----|

|    | 23.1.1. Port Pins Configured for Analog I/O                                 |     |

|    | 23.1.2. Port Pins Configured For Digital I/O                                |     |

|    | 23.1.3. Interfacing Port I/O to 5 V Logic                                   | 140 |

|    | 23.2. Assigning Port I/O Pins to Analog and Digital Functions               | 140 |

|    | 23.2.1. Assigning Port I/O Pins to Analog Functions                         | 140 |

|    | 23.2.2. Assigning Port I/O Pins to Digital Functions                        | 141 |

|    | 23.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions | 142 |

|    | 23.3. Priority Crossbar Decoder                                             |     |

|    | 23.4. Port I/O Initialization                                               |     |

|    | 23.5. Port Match                                                            |     |

|    | 23.6. Special Function Registers for Accessing and Configuring Port I/O     |     |

| 24 | Cyclic Redundancy Check Unit (CRC0)                                         |     |

|    | 24.1. 16-bit CRC Algorithm                                                  |     |

|    | 24.2. 32-bit CRC Algorithm.                                                 |     |

|    | 24.3. Preparing for a CRC Calculation                                       |     |

|    | 24.4. Performing a CRC Calculation                                          |     |

|    | 24.5. Accessing the CRC0 Result                                             |     |

|    | 24.6. CRC0 Bit Reverse Feature                                              |     |

| 25 | Enhanced Serial Peripheral Interface (SPI0)                                 |     |

|    | 25.1. Signal Descriptions                                                   |     |

|    | 25.1.1. Master Out, Slave In (MOSI)                                         |     |

|    | 25.1.2. Master In, Slave Out (MISO)                                         |     |

|    | 25.1.3. Serial Clock (SCK)                                                  |     |

|    | 25.1.4. Slave Select (NSS)                                                  |     |

|    | 25.2. SPI0 Master Mode Operation                                            |     |

|    | 25.3. SPI0 Slave Mode Operation                                             |     |

|    | 25.4. SPI0 Interrupt Sources                                                |     |

|    | 25.5. Serial Clock Phase and Polarity                                       | 171 |

|    | 25.6. SPI Special Function Registers                                        |     |

| 26 | SMBus                                                                       |     |

|    | 26.1. Supporting Documents                                                  |     |

|    | 26.2. SMBus Configuration                                                   |     |

|    | 26.3. SMBus Operation                                                       |     |

|    | 26.3.1. Transmitter Vs. Receiver.                                           | 182 |

|    | 26.3.2. Arbitration                                                         |     |

|    | 26.3.3. Clock Low Extension                                                 |     |

|    | 26.3.4. SCL Low Timeout                                                     |     |

|    | 26.3.5. SCL High (SMBus Free) Timeout                                       |     |

|    | 26.4. Using the SMBus                                                       |     |

|    | 26.4.1. SMBus Configuration Register                                        |     |

|    | 26.4.2. SMB0CN Control Register                                             |     |

|    | 26.4.2.1. Software ACK Generation                                           |     |

|    | 26.4.2.2. Hardware ACK Generation                                           |     |

|    | 26.4.3. Hardware Slave Address Recognition                                  |     |

|    | 5                                                                           |     |

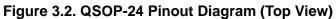

#### 8.5. ADC0 Analog Multiplexer

ADC0 on the C8051F800/1/2/3/4/5, C8051F812/3/4/5/6/7, C8051F824/5/6, and C8051F830/1/2 uses an analog input multiplexer to select the positive input to the ADC. Any of the following may be selected as the positive input: Port 0 or Port 1 I/O pins, the on-chip temperature sensor, or the positive power supply ( $V_{DD}$ ). The ADC0 input channel is selected in the ADC0MX register described in SFR Definition 8.9.

Figure 8.6. ADC0 Multiplexer Block Diagram

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set the corresponding bit in register PnMDIN to 0. To force the Crossbar to skip a Port pin, set the corresponding bit in register PnSKIP to 1. See Section "23. Port Input/Output" on page 138 for more Port I/O configuration details.

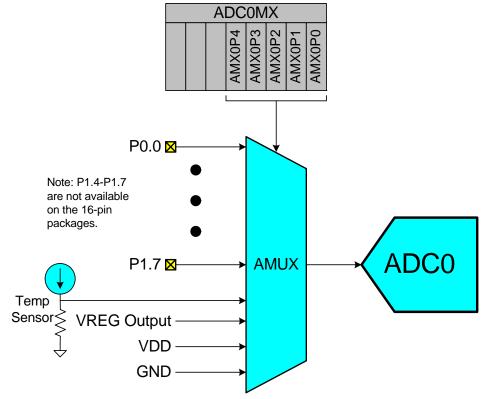

## 10. Voltage and Ground Reference Options

The voltage reference MUX is configurable to use an externally connected voltage reference, the on-chip voltage reference, or one of two power supply voltages (see Figure 10.1). The ground reference MUX allows the ground reference for ADC0 to be selected between the ground pin (GND) or a port pin dedicated to analog ground (P0.1/AGND).

The voltage and ground reference options are configured using the REF0CN SFR described on page 62. Electrical specifications are can be found in the Electrical Specifications Chapter.

**Important Note About the V<sub>REF</sub> and AGND Inputs:** Port pins are used as the external V<sub>REF</sub> and AGND inputs. When using an external voltage reference, P0.0/VREF should be configured as an analog input and skipped by the Digital Crossbar. When using AGND as the ground reference to ADC0, P0.1/AGND should be configured as an analog input and skipped by the Digital Crossbar. Refer to Section "23. Port Input/Output" on page 138 for complete Port I/O configuration details. The external reference voltage must be within the range  $0 \le V_{REF} \le V_{DD}$  and the external ground reference must be at the same DC voltage potential as GND.

Figure 10.1. Voltage Reference Functional Block Diagram

### SFR Definition 10.1. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4   | 3   | 2     | 1     | 0 |

|-------|---|---|--------|-----|-----|-------|-------|---|

| Name  |   |   | REFGND | REI | -SL | TEMPE | BIASE |   |

| Туре  | R | R | R/W    | R/W | R/W | R/W   | R/W   | R |

| Reset | 0 | 0 | 0      | 1   | 0   | 0     | 0     | 0 |

SFR Address = 0xD1

| Bit | Name   | Function                                                                            |

|-----|--------|-------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                     |

| 5   | REFGND | Analog Ground Reference.                                                            |

|     |        | Selects the ADC0 ground reference.                                                  |

|     |        | 0: The ADC0 ground reference is the GND pin.                                        |

|     |        | 1: The ADC0 ground reference is the P0.1/AGND pin.                                  |

| 4:3 | REFSL  | Voltage Reference Select.                                                           |

|     |        | Selects the ADC0 voltage reference.                                                 |

|     |        | 00: The ADC0 voltage reference is the P0.0/VREF pin.                                |

|     |        | 01: The ADC0 voltage reference is the VDD pin.                                      |

|     |        | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.        |

|     |        | 11: The ADC0 voltage reference is the internal 1.65 V high speed voltage reference. |

| 2   | TEMPE  | Temperature Sensor Enable.                                                          |

|     |        | Enables/Disables the internal temperature sensor.                                   |

|     |        | 0: Temperature Sensor Disabled.                                                     |

|     |        | 1: Temperature Sensor Enabled.                                                      |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                          |

|     |        | 0: Internal Bias Generator off.                                                     |

|     |        | 1: Internal Bias Generator on.                                                      |

| 0   | Unused | Read = 0b; Write = Don't Care.                                                      |

## 11. Voltage Regulator (REG0)

C8051F80x-83x devices include an internal voltage regulator (REG0) to regulate the internal core supply to 1.8 V from a  $V_{DD}$  supply of 1.8 to 3.6 V. A power-saving mode is built into the regulator to help reduce current consumption in low-power applications. This mode is accessed through the REG0CN register (SFR Definition 11.1). Electrical characteristics for the on-chip regulator are specified in Table 7.5 on page 41

Under default conditions, when the device enters STOP mode the internal regulator will remain on. This allows any enabled reset source to generate a reset for the device and bring the device out of STOP mode. For additional power savings, the STOPCF bit can be used to shut down the regulator and the internal power network of the device when the part enters STOP mode. When STOPCF is set to 1, the RST pin or a full power cycle of the device are the only methods of generating a reset.

## SFR Definition 14.6. PSW: Program Status Word

| Bit   | 7   | 6   | 5   | 4       | 3 | 2   | 1   | 0      |

|-------|-----|-----|-----|---------|---|-----|-----|--------|

| Name  | CY  | AC  | F0  | RS[1:0] |   | OV  | F1  | PARITY |

| Туре  | R/W | R/W | R/W | R/W     |   | R/W | R/W | R      |

| Reset | 0   | 0   | 0   | 0       | 0 | 0   | 0   | 0      |

#### SFR Address = 0xD0; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CY      | Carry Flag.                                                                                                                                                                                               |

|     |         | This bit is set when the last arithmetic operation resulted in a carry (addition) or a borrow (subtraction). It is cleared to logic 0 by all other arithmetic operations.                                 |

| 6   | AC      | Auxiliary Carry Flag.                                                                                                                                                                                     |

|     |         | This bit is set when the last arithmetic operation resulted in a carry into (addition) or a borrow from (subtraction) the high order nibble. It is cleared to logic 0 by all other arithmetic operations. |

| 5   | F0      | User Flag 0.                                                                                                                                                                                              |

|     |         | This is a bit-addressable, general purpose flag for use under software control.                                                                                                                           |

| 4:3 | RS[1:0] | Register Bank Select.                                                                                                                                                                                     |

|     |         | These bits select which register bank is used during register accesses.                                                                                                                                   |

|     |         | 00: Bank 0, Addresses 0x00-0x07                                                                                                                                                                           |

|     |         | 01: Bank 1, Addresses 0x08-0x0F                                                                                                                                                                           |

|     |         | 10: Bank 2, Addresses 0x10-0x17<br>11: Bank 3, Addresses 0x18-0x1F                                                                                                                                        |

| 2   | OV      | Overflow Flag.                                                                                                                                                                                            |

|     |         | This bit is set to 1 under the following circumstances:                                                                                                                                                   |

|     |         | An ADD, ADDC, or SUBB instruction causes a sign-change overflow.                                                                                                                                          |

|     |         | <ul> <li>A MUL instruction results in an overflow (result is greater than 255).</li> <li>A DIV instruction causes a divide-by-zero condition.</li> </ul>                                                  |

|     |         | The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all other cases.                                                                                                          |

| 1   | F1      | User Flag 1.                                                                                                                                                                                              |

|     |         | This is a bit-addressable, general purpose flag for use under software control.                                                                                                                           |

| 0   | PARITY  | Parity Flag.                                                                                                                                                                                              |

|     |         | This bit is set to logic 1 if the sum of the eight bits in the accumulator is odd and cleared if the sum is even.                                                                                         |

## **16. In-System Device Identification**

The C8051F80x-83x has SFRs that identify the device family and derivative. These SFRs can be read by firmware at runtime to determine the capabilities of the MCU that is executing code. This allows the same firmware image to run on MCUs with different memory sizes and peripherals, and dynamically changing functionality to suit the capabilities of that MCU.

In order for firmware to identify the MCU, it must read three SFRs. HWID describes the MCU's family, DERIVID describes the specific derivative within that device family, and REVID describes the hardware revision of the MCU.

#### SFR Definition 16.1. HWID: Hardware Identification Byte

| Bit   | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------|---|---|---|---|---|---|

| Name  |   | HWID[7:0] |   |   |   |   |   |   |

| Туре  | R | R         | R | R | R | R | R | R |

| Reset | 0 | 0         | 1 | 0 | 0 | 0 | 1 | 1 |

#### SFR Address = 0xB5

| Bit | Name      | Description                                                                         |

|-----|-----------|-------------------------------------------------------------------------------------|

| 7:0 | HWID[7:0] | Hardware Identification Byte.                                                       |

|     |           | Describes the MCU family.<br>0x23: Devices covered in this document (C8051F80x-83x) |

## SFR Definition 16.2. DERIVID: Derivative Identification Byte

| Bit   | 7      | 6            | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------------|--------|--------|--------|--------|--------|--------|

| Name  |        | DERIVID[7:0] |        |        |        |        |        |        |

| Туре  | R      | R            | R      | R      | R      | R      | R      | R      |

| Reset | Varies | Varies       | Varies | Varies | Varies | Varies | Varies | Varies |

SFR Address = 0xAD

| Bit | Name         | Description                                                        |

|-----|--------------|--------------------------------------------------------------------|

| 7:0 | DERIVID[7:0] | Derivative Identification Byte.                                    |

|     |              | Shows the C8051F80x-83x derivative being used.                     |

|     |              | 0xD0: C8051F800; 0xD1: C8051F801; 0xD2: C8051F802; 0xD3: C8051F803 |

|     |              | 0xD4: C8051F804; 0xD5: C8051F805; 0xD6: C8051F806; 0xD7: C8051F807 |

|     |              | 0xD8: C8051F808; 0xD9: C8051F809; 0xDA: C8051F810; 0xDB: C8051F811 |

|     |              | 0xDC: C8051F812; 0xDD: C8051F813; 0xDE: C8051F814; 0xDF: C8051F815 |

|     |              | 0xE0: C8051F816; 0xE1: C8051F817; 0xE2: C8051F818; 0xE3: C8051F819 |

|     |              | 0xE4: C8051F820; 0xE5: C8051F821; 0xE6: C8051F822; 0xE7: C8051F823 |

|     |              | 0xE8: C8051F824; 0xE9: C8051F825; 0xEA: C8051F826; 0xEB: C8051F827 |

|     |              | 0xEC: C8051F828; 0xED: C8051F829; 0xEE: C8051F830; 0xEF: C8051F831 |

|     |              | 0xF0: C8051F832; 0xF1: C8051F833; 0xF2: C8051F834; 0xF3: C8051F835 |

### SFR Definition 16.3. REVID: Hardware Revision Identification Byte

| Bit   | 7      | 6          | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|------------|--------|--------|--------|--------|--------|--------|

| Name  |        | REVID[7:0] |        |        |        |        |        |        |

| Туре  | R      | R          | R      | R      | R      | R      | R      | R      |

| Reset | Varies | Varies     | Varies | Varies | Varies | Varies | Varies | Varies |

SFR Address = 0xB6

| Bit | Name       | Description                                                                              |

|-----|------------|------------------------------------------------------------------------------------------|

| 7:0 | REVID[7:0] | Hardware Revision Identification Byte.                                                   |

|     |            | Shows the C8051F80x-83x hardware revision being used.<br>For example, 0x00 = Revision A. |

## **17. Special Function Registers**

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F80x-83x's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F80x-83x. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 17.1 lists the SFRs implemented in the C8051F80x-83x device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g., P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 17.2, for a detailed description of each register.

| F8 | SPI0CN | PCA0L    | PCA0H    | PCA0CPL0 | PCA0CPH0 | P0MAT   | P0MASK   | VDM0CN   |

|----|--------|----------|----------|----------|----------|---------|----------|----------|

| F0 | В      | P0MDIN   | P1MDIN   | EIP1     | EIP2     |         |          | PCA0PWM  |

| E8 | ADC0CN | PCA0CPL1 | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 | P1MAT   | P1MASK   | RSTSRC   |

| E0 | ACC    | XBR0     | XBR1     |          | IT01CF   |         | EIE1     | EIE2     |

| D8 | PCA0CN | PCA0MD   | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 | CRC0IN  | CRC0DATA |          |

| D0 | PSW    | REF0CN   | CRC0AUTO | CRC0CNT  | P0SKIP   | P1SKIP  | SMB0ADM  | SMB0ADR  |

| C8 | TMR2CN | REG0CN   | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H   | CRC0CN   | CRC0FLIP |

| C0 | SMB0CN | SMB0CF   | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL | ADC0LTH  |          |

| B8 | IP     | CS0SS    | CS0SE    | ADC0MX   | ADC0CF   | ADC0L   | ADC0H    |          |

| B0 | CS0CN  | OSCXCN   | OSCICN   | OSCICL   |          | HWID    | REVID    | FLKEY    |

| A8 | IE     | CLKSEL   |          | CS0DL    | CS0DH    | DERVID  |          |          |

| A0 | P2     | SPI0CFG  | SPI0CKR  | SPI0DAT  | POMDOUT  | P1MDOUT | P2MDOUT  |          |

| 98 | SCON0  | SBUF0    |          | CPT0CN   | CS0MX    | CPT0MD  | CS0CF    | CPT0MX   |

| 90 | P1     |          |          |          |          |         | CS0THL   | CS0THH   |

| 88 | TCON   | TMOD     | TL0      | TL1      | TH0      | TH1     | CKCON    | PSCTL    |

| 80 | P0     | SP       | DPL      | DPH      |          |         |          | PCON     |

|    | 0(8)   | 1(9)     | 2(A)     | 3(B)     | 4(C)     | 5(D)    | 6(E)     | 7(F)     |

#### Table 17.1. Special Function Register (SFR) Memory Map

Note: SFR Addresses ending in 0x0 or 0x8 are bit-addressable locations, and can be used with bitwise instructions.

The following guidelines are recommended for any system that contains routines which write or erase Flash from code.

#### 19.4.1. VDD Maintenance and the VDD Monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Make certain that the minimum VDD rise time specification of 1 ms is met. If the system cannot meet this rise time specification, then add an external VDD brownout circuit to the RST pin of the device that holds the device in reset until VDD reaches the minimum device operating voltage and re-asserts RST if VDD drops below the minimum device operating voltage.

- 3. Keep the on-chip VDD Monitor enabled and enable the VDD Monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the VDD Monitor and enabling the VDD Monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories website.

- **Note:** On C8051F80x-83x devices, both the VDD Monitor and the VDD Monitor reset source must be enabled to write or erase Flash without generating a Flash Error Device Reset.

On C8051F80x-83x devices, both the VDD Monitor and the VDD Monitor reset source are enabled by hardware after a power-on reset.

- 4. As an added precaution, explicitly enable the VDD Monitor and enable the VDD Monitor as a reset source inside the functions that write and erase Flash memory. The VDD Monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- 5. Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct, but "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 19.4.2. PSWE Maintenance

- 1. Reduce the number of places in code where the PSWE bit (b0 in PSCTL) is set to a 1. There should be exactly one routine in code that sets PSWE to a 1 to write Flash bytes and one routine in code that sets both PSWE and PSEE both to a 1 to erase Flash pages.

- 2. Minimize the number of variable accesses while PSWE is set to a 1. Handle pointer address updates and loop maintenance outside the "PSWE = 1;... PSWE = 0;" area. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories website.

- 3. Disable interrupts prior to setting PSWE to a 1 and leave them disabled until after PSWE has been reset to 0. Any interrupts posted during the Flash write or erase operation will be serviced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

- Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 5. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

## 23. Port Input/Output

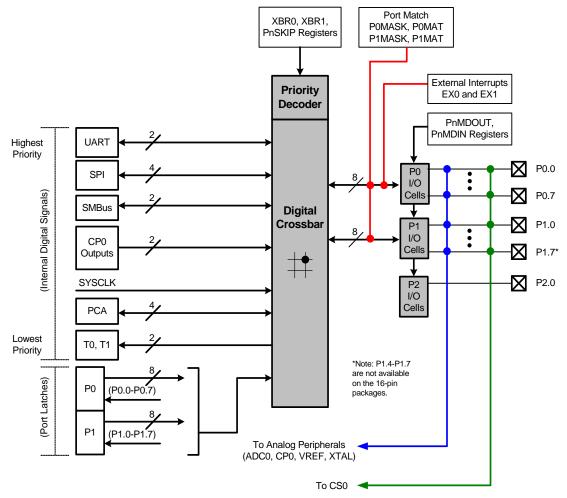

Digital and analog resources are available through 17 I/O pins (24-pin and 20-pin packages) or 13 I/O pins (16-pin packages). Port pins P0.0–P1.7 can be defined as general-purpose I/O (GPIO) or assigned to one of the internal digital resources as shown in Figure 23.4. Port pin P2.0 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 23.5). The registers XBR0 and XBR1, defined in SFR Definition 23.1 and SFR Definition 23.2, are used to select internal digital functions.

All Port I/Os are 5 V tolerant (refer to Figure 23.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Section "7. Electrical Characteristics" on page 39.

Figure 23.1. Port I/O Functional Block Diagram

### SFR Definition 23.12. P1MDIN: Port 1 Input Mode

| Bit   | 7           | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|-------------------|---|---|---|---|---|---|--|--|

| Name  | P1MDIN[7:0] |                   |   |   |   |   |   |   |  |  |

| Туре  | R/W         |                   |   |   |   |   |   |   |  |  |

| Reset | 1*          | 1* 1* 1* 1* 1 1 1 |   |   |   |   |   |   |  |  |

SFR Address = 0xF2

| Bit | Name        | Function                                                                                                                                                                                                                            |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDIN[7:0] | Analog Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                             |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. In order for the P1.n pin to be in analog mode, there MUST be a 1 in the Port Latch register corresponding to that pin. |

|     |             | 0: Corresponding P1.n pin is configured for analog mode.                                                                                                                                                                            |

|     |             | 1: Corresponding P1.n pin is not configured for analog mode.                                                                                                                                                                        |

|     |             | Note: P1.4–P1.7 are not available on 16-pin packages, with the reset value of 0000b for P1MDIN[7:4].                                                                                                                                |

#### SFR Definition 23.13. P1MDOUT: Port 1 Output Mode

| Bit   | 7            | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|-----------------|---|---|---|---|---|---|--|

| Name  | P1MDOUT[7:0] |                 |   |   |   |   |   |   |  |

| Туре  |              | R/W             |   |   |   |   |   |   |  |

| Reset | 0            | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

SFR Address = 0xA5

| Bit | Name         | Function                                                                       |

|-----|--------------|--------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                        |

|     |              | These bits are ignored if the corresponding bit in register P1MDIN is logic 0. |

|     |              | 0: Corresponding P1.n Output is open-drain.                                    |

|     |              | 1: Corresponding P1.n Output is push-pull.                                     |

|     |              | <b>Note:</b> P1.4–P1.7 are not available on 16-pin packages.                   |

### SFR Definition 24.1. CRC0CN: CRC0 Control

| Bit   | 7   | 6   | 5   | 4       | 3        | 2       | 1            | 0 |

|-------|-----|-----|-----|---------|----------|---------|--------------|---|

| Name  |     |     |     | CRC0SEL | CRC0INIT | CRC0VAL | CRC0PNT[1:0] |   |

| Туре  | R/W | R/W | R/W | R/W     | R/W      | R/W     | R/W          |   |

| Reset | 0   | 0   | 0   | 0       | 0        | 0       | 0            | 0 |

SFR Address = 0xCE

| Bit | Name         | Function                                                                                                                                                                                                                                 |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused       | Read = 000b; Write = Don't Care.                                                                                                                                                                                                         |

| 4   | CRC0SEL      | CRC0 Polynomial Select Bit.                                                                                                                                                                                                              |

|     |              | This bit selects the CRC0 polynomial and result length (32-bit or 16-bit).<br>0: CRC0 uses the 32-bit polynomial 0x04C11DB7 for calculating the CRC result.<br>1: CRC0 uses the 16-bit polynomial 0x1021 for calculating the CRC result. |

| 3   | CRC0INIT     | CRC0 Result Initialization Bit.                                                                                                                                                                                                          |

|     |              | Writing a 1 to this bit initializes the entire CRC result based on CRC0VAL.                                                                                                                                                              |

| 2   | CRC0VAL      | CRC0 Set Value Initialization Bit.                                                                                                                                                                                                       |

|     |              | This bit selects the set value of the CRC result.                                                                                                                                                                                        |

|     |              | 0: CRC result is set to 0x00000000 on write of 1 to CRC0INIT.                                                                                                                                                                            |

|     |              | 1: CRC result is set to 0xFFFFFFF on write of 1 to CRC0INIT.                                                                                                                                                                             |

| 1:0 | CRC0PNT[1:0] | CRC0 Result Pointer.                                                                                                                                                                                                                     |

|     |              | Specifies the byte of the CRC result to be read/written on the next access to CRC0DAT. The value of these bits will auto-increment upon each read or write. For CRC0SEL = 0:                                                             |

|     |              | 00: CRC0DAT accesses bits 7–0 of the 32-bit CRC result.                                                                                                                                                                                  |

|     |              | 01: CRC0DAT accesses bits 15–8 of the 32-bit CRC result.                                                                                                                                                                                 |

|     |              | 10: CRC0DAT accesses bits 23–16 of the 32-bit CRC result.                                                                                                                                                                                |

|     |              | 11: CRC0DAT accesses bits 31–24 of the 32-bit CRC result.<br>For CRC0SEL = 1:                                                                                                                                                            |

|     |              | 00: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.                                                                                                                                                                                  |

|     |              | 01: CRC0DAT accesses bits 15–8 of the 16-bit CRC result.                                                                                                                                                                                 |

|     |              | 10: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.                                                                                                                                                                                  |

|     |              | 11: CRC0DAT accesses bits 15-8 of the 16-bit CRC result.                                                                                                                                                                                 |

| SMBCS1 | SMBCS0 | SMBus Clock Source         |  |  |  |  |

|--------|--------|----------------------------|--|--|--|--|

| 0      | 0      | Timer 0 Overflow           |  |  |  |  |

| 0      | 1      | Timer 1 Overflow           |  |  |  |  |

| 1      | 0      | Timer 2 High Byte Overflow |  |  |  |  |

| 1      | 1      | Timer 2 Low Byte Overflow  |  |  |  |  |

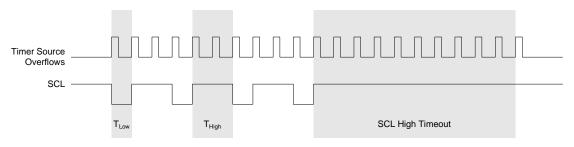

#### Table 26.1. SMBus Clock Source Selection

The SMBCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 26.1. Note that the selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in Section "28. Timers" on page 209.

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

#### Equation 26.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 26.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 26.2.

$$BitRate = \frac{f_{ClockSourceOverflow}}{3}$$

#### Equation 26.2. Typical SMBus Bit Rate

Figure 26.4 shows the typical SCL generation described by Equation 26.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 26.1.

Figure 26.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 26.2 shows the minimum setup.

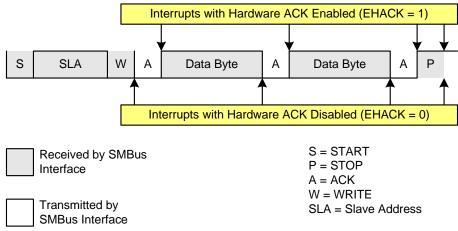

#### 26.5.3. Write Sequence (Slave)

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 26.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the "data byte transferred" interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 26.7. Typical Slave Write Sequence

## SFR Definition 28.6. TH0: Timer 0 High Byte

| Bit           | 7            | 6                                                        | 5 | 4 | 3        | 2 | 1 | 0 |  |  |

|---------------|--------------|----------------------------------------------------------|---|---|----------|---|---|---|--|--|

| Name TH0[7:0] |              |                                                          |   |   |          |   |   |   |  |  |

| Type R/W      |              |                                                          |   |   |          |   |   |   |  |  |

| Rese          | <b>t</b> 0   | 0 0 0 0 0 0 0                                            |   |   |          |   |   |   |  |  |

| SFR A         | ddress = 0x8 | С                                                        |   |   |          |   |   |   |  |  |

| Bit           | Name         |                                                          |   |   | Function |   |   |   |  |  |

| 7:0           | TH0[7:0]     | Timer 0 High Byte.                                       |   |   |          |   |   |   |  |  |

|               |              | The TH0 register is the high byte of the 16-bit Timer 0. |   |   |          |   |   |   |  |  |

## SFR Definition 28.7. TH1: Timer 1 High Byte

| Bit                | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------------------|---------------|---|---|---|---|---|---|---|--|

| Name               | TH1[7:0]      |   |   |   |   |   |   |   |  |

| Туре               | R/W           |   |   |   |   |   |   |   |  |

| Reset              | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Address = 0x8D |               |   |   |   |   |   |   |   |  |

| Bit                | Name Function |   |   |   |   |   |   |   |  |

| Bit | Name     | Function                                                 |

|-----|----------|----------------------------------------------------------|

| 7:0 | TH1[7:0] | Timer 1 High Byte.                                       |

|     |          | The TH1 register is the high byte of the 16-bit Timer 1. |

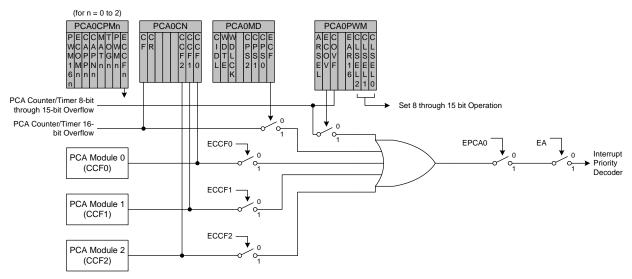

#### 29.2. PCA0 Interrupt Sources

Figure 29.3 shows a diagram of the PCA interrupt tree. There are five independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th through 15th bit of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, and CCF2), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit in the IE register and the EPCA0 bit in the EIE1 register to logic 1.

Figure 29.3. PCA Interrupt Block Diagram

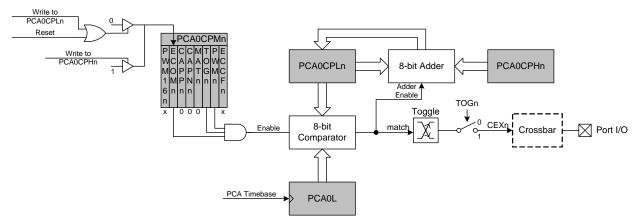

#### 29.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 29.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### **Equation 29.1. Square Wave Frequency Output**

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. The MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

Figure 29.7. PCA Frequency Output Mode

#### 29.3.5. 8-bit through 15-bit Pulse Width Modulator Modes

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer, and the setting of the PWM cycle length (8, 9, 10, 11, 12, 13, 14, or 15-bits). For backwards-compatibility with the 8-bit PWM mode available on other devices, the 8-bit PWM mode operates slightly different than 9, 10, 11, 12, 13, 14, and 15-bit PWM modes. It is important to note that all channels configured for 8-bit through 15-bit PWM mode will use the same cycle length. For example, it is not possible to configure one channel for 8-bit PWM mode and another for 11-bit mode. However, other PCA channels can be configured to Pin Capture, High-Speed Output, Software Timer, Frequency Output, or 16-bit PWM mode independently.

## SFR Definition 29.4. PCA0CPMn: PCA0 Capture/Compare Mode

| Bit   | 7                                         | 6                                                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                 | 4                             | 3             | 2            | 1             | 0            |  |

|-------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|--------------|---------------|--------------|--|

| Nam   | e PWM16                                   | n ECOMn                                                                                                                                                                                                                                                                                                             | CAPPn                                                                                                                                                                                                                                                                             | CAPNn                         | MATn          | TOGn         | PWMn          | ECCFn        |  |

| Туре  | R/W                                       | R/W                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                               | R/W                           | R/W           | R/W          | R/W           | R/W          |  |

| Rese  | et 0                                      | 0                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                 | 0                             | 0             | 0            | 0             | 0            |  |

| SFR A | Addresses: I                              | <br>PCA0CPM0 = (                                                                                                                                                                                                                                                                                                    | )xDA, PCA0                                                                                                                                                                                                                                                                        | L<br>CPM1 = 0xD               | B, PCA0CP     | M2 = 0xDC    |               |              |  |

| Bit   | Name                                      |                                                                                                                                                                                                                                                                                                                     | Function                                                                                                                                                                                                                                                                          |                               |               |              |               |              |  |

| 7     | PWM16n                                    | 16-bit Pulse V                                                                                                                                                                                                                                                                                                      | Vidth Modu                                                                                                                                                                                                                                                                        | lation Enab                   | le.           |              |               |              |  |

|       |                                           | This bit enable                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   |                               | se Width Mo   | dulation mo  | de is enable  | d.           |  |

|       |                                           | 0: 8 to 15-bit F<br>1: 16-bit PWM                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                   | ed.                           |               |              |               |              |  |

| 6     | ECOMn                                     |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   | abla                          |               |              |               |              |  |

| 6     | ECOMIN                                    | Comparator F<br>This bit enable                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   |                               | on for BCA m  | odulo o wha  | on cot to 1   |              |  |

| 5     | CAPPn                                     | Capture Posi                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                 |                               |               |              |               |              |  |

| 5     | UAI 11                                    | This bit enable                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   |                               | ure for PCA   | module n wl  | hen set to 1  |              |  |

| 4     | CAPNn                                     | Capture Nega                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                 |                               |               |              |               |              |  |

|       | 0, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, | This bit enable                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   |                               | oture for PCA | v module n w | /hen set to 1 |              |  |

| 3     | MATn                                      | Match Functi                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                   |                               |               |              |               |              |  |

|       |                                           | This bit enable<br>matches of the<br>bit in PCA0ME                                                                                                                                                                                                                                                                  | PCA count                                                                                                                                                                                                                                                                         | er with a mo                  | dule's captur |              |               |              |  |

| 2     | TOGn                                      | Toggle Funct                                                                                                                                                                                                                                                                                                        | ion Enable.                                                                                                                                                                                                                                                                       |                               |               |              |               |              |  |

|       |                                           | This bit enable<br>matches of the<br>level on the C<br>ates in Freque                                                                                                                                                                                                                                               | e PCA count<br>EXn pin to to                                                                                                                                                                                                                                                      | er with a mo<br>oggle. If the | dule's captu  | re/compare   | register caus | se the logic |  |

| 1     | PWMn                                      | Pulse Width I                                                                                                                                                                                                                                                                                                       | Modulation                                                                                                                                                                                                                                                                        | Mode Enab                     | le.           |              |               |              |  |

|       |                                           | This bit enables the PWM function for PCA module n when set to 1. When enabled, a pulse width modulated signal is output on the CEXn pin. 8 to 15-bit PWM is used if PWM16n is cleared; 16-bit mode is used if PWM16n is set to logic 1. If the TOGn bit is also set, the module operates in Frequency Output Mode. |                                                                                                                                                                                                                                                                                   |                               |               |              |               |              |  |

| 0     | ECCFn                                     | Capture/Com                                                                                                                                                                                                                                                                                                         | pare Flag Ir                                                                                                                                                                                                                                                                      | nterrupt Ena                  | able.         |              |               |              |  |

|       |                                           | This bit sets the masking of the Capture/Compare Flag (CCFn) interrupt.<br>0: Disable CCFn interrupts.                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                   |                               |               |              |               |              |  |

| Note: | watchdog ti                               | VDTE bit is set to                                                                                                                                                                                                                                                                                                  | 1: Enable a Capture/Compare Flag interrupt request when CCFn is set.<br>DTE bit is set to 1, the PCA0CPM2 register cannot be modified, and module 2 acts as the<br>ner. To change the contents of the PCA0CPM2 register or the function of module 2, the Watchdog<br>be disabled. |                               |               |              |               |              |  |