# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 8KB (8K × 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f824-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 28.8. TMR2CN: Timer 2 Control                     | 222 |

|------------------------------------------------------------------|-----|

| SFR Definition 28.9. TMR2RLL: Timer 2 Reload Register Low Byte   | 223 |

| SFR Definition 28.10. TMR2RLH: Timer 2 Reload Register High Byte | 223 |

| SFR Definition 28.11. TMR2L: Timer 2 Low Byte                    | 224 |

| SFR Definition 28.12. TMR2H Timer 2 High Byte                    | 224 |

| SFR Definition 29.1. PCA0CN: PCA0 Control                        | 238 |

| SFR Definition 29.2. PCA0MD: PCA0 Mode                           | 239 |

| SFR Definition 29.3. PCA0PWM: PCA0 PWM Configuration             | 240 |

| SFR Definition 29.4. PCA0CPMn: PCA0 Capture/Compare Mode         | 241 |

| SFR Definition 29.5. PCA0L: PCA0 Counter/Timer Low Byte          | 242 |

| SFR Definition 29.6. PCA0H: PCA0 Counter/Timer High Byte         | 242 |

| SFR Definition 29.7. PCA0CPLn: PCA0 Capture Module Low Byte      | 243 |

| SFR Definition 29.8. PCA0CPHn: PCA0 Capture Module High Byte     | 243 |

| C2 Register Definition 30.1. C2ADD: C2 Address                   | 244 |

| C2 Register Definition 30.3. REVID: C2 Revision ID               | 245 |

| C2 Register Definition 30.2. DEVICEID: C2 Device ID              | 245 |

| C2 Register Definition 30.4. FPCTL: C2 Flash Programming Control | 246 |

| C2 Register Definition 30.5. FPDAT: C2 Flash Programming Data    | 246 |

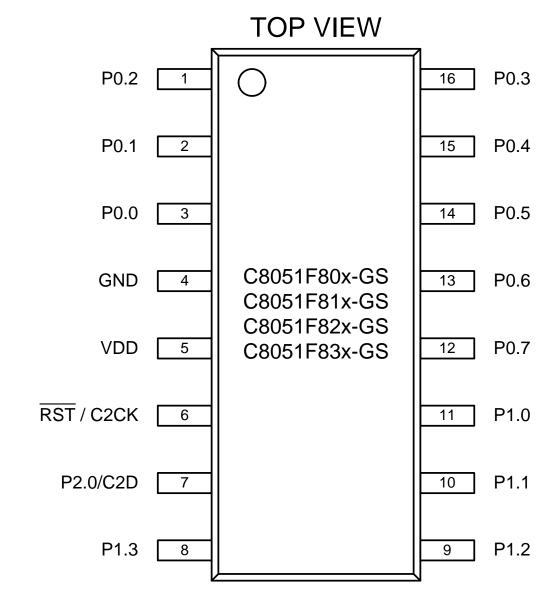

Figure 3.3. SOIC-16 Pinout Diagram (Top View)

### Table 7.10. Power Management Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                 | Conditions | Min | Тур | Мах | Units   |

|---------------------------|------------|-----|-----|-----|---------|

| Idle Mode Wake-Up Time    |            | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time |            | _   | 500 | _   | ns      |

### Table 7.11. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter                | Conditions                      | Min | Тур  | Max | Units |

|--------------------------|---------------------------------|-----|------|-----|-------|

| Linearity                |                                 | -   | 1    | —   | °C    |

| Slope                    |                                 | —   | 2.43 | _   | mV/°C |

| Slope Error*             |                                 |     | ±45  | —   | µV/°C |

| Offset                   | Temp = 0 °C                     | —   | 873  | —   | mV    |

| Offset Error*            | Temp = 0 °C                     |     | 14.5 | —   | mV    |

| *Note: Represents one st | andard deviation from the mean. |     |      |     |       |

### Table 7.12. Voltage Reference Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V; -40 to +85 °C unless otherwise specified.

| Parameter                                       | Conditions                           | Min  | Тур  | Max      | Units |  |

|-------------------------------------------------|--------------------------------------|------|------|----------|-------|--|

| Internal High Speed Reference (REFSL[1:0] = 11) |                                      |      |      |          |       |  |

| Output Voltage                                  | 25 °C ambient                        | 1.55 | 1.65 | 1.75     | V     |  |

| Turn-on Time                                    |                                      | —    | —    | 1.7      | μs    |  |

| Supply Current                                  |                                      |      | 180  |          | μA    |  |

|                                                 | External Reference (REF0E = 0)       |      |      |          |       |  |

| Input Voltage Range                             |                                      | 0    | —    | $V_{DD}$ |       |  |

| Input Current                                   | Sample Rate = 500 ksps; VREF = 3.0 V |      | 7    | _        | μA    |  |

#### 8.4.1. Window Detector Example

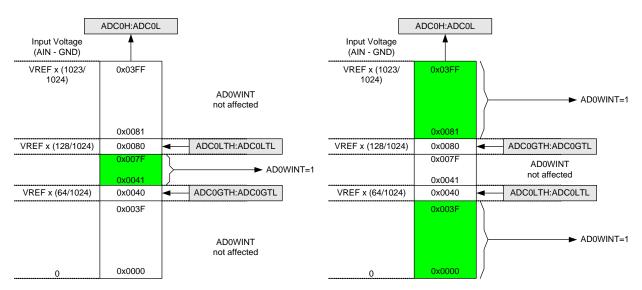

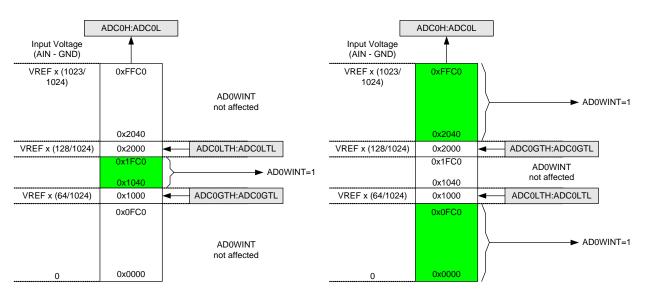

Figure 8.4 shows two example window comparisons for right-justified data. with ADC0LTH:ADC0LTL = 0x0080 (128d) and ADC0GTH:ADC0GTL = 0x0040 (64d). The input voltage can range from 0 to VREF x (1023/1024) with respect to GND, and is represented by a 10-bit unsigned integer value. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0040 < ADC0H:ADC0L < 0x0080). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0040 or ADC0H:ADC0L > 0x0080). Figure 8.5 shows an example using left-justified data with the same comparison values.

Figure 8.4. ADC Window Compare Example: Right-Justified Data

Figure 8.5. ADC Window Compare Example: Left-Justified Data

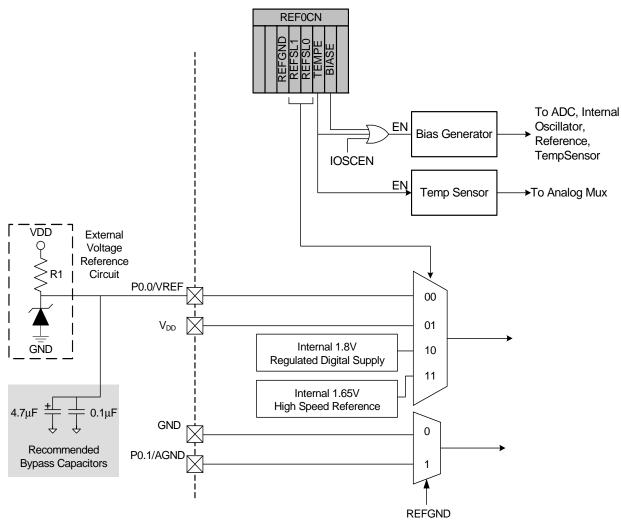

## 10. Voltage and Ground Reference Options

The voltage reference MUX is configurable to use an externally connected voltage reference, the on-chip voltage reference, or one of two power supply voltages (see Figure 10.1). The ground reference MUX allows the ground reference for ADC0 to be selected between the ground pin (GND) or a port pin dedicated to analog ground (P0.1/AGND).

The voltage and ground reference options are configured using the REF0CN SFR described on page 62. Electrical specifications are can be found in the Electrical Specifications Chapter.

**Important Note About the V<sub>REF</sub> and AGND Inputs:** Port pins are used as the external V<sub>REF</sub> and AGND inputs. When using an external voltage reference, P0.0/VREF should be configured as an analog input and skipped by the Digital Crossbar. When using AGND as the ground reference to ADC0, P0.1/AGND should be configured as an analog input and skipped by the Digital Crossbar. Refer to Section "23. Port Input/Output" on page 138 for complete Port I/O configuration details. The external reference voltage must be within the range  $0 \le V_{REF} \le V_{DD}$  and the external ground reference must be at the same DC voltage potential as GND.

Figure 10.1. Voltage Reference Functional Block Diagram

| Mnemonic             | Description                                                            | Bytes | Clock<br>Cycles |

|----------------------|------------------------------------------------------------------------|-------|-----------------|

| ANL C, bit           | AND direct bit to Carry                                                | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry                                  | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                                                 | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                                   | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                                               | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                                               | 2     | 2               |

| JC rel               | Jump if Carry is set                                                   | 2     | 2/3             |

| JNC rel              | Jump if Carry is not set                                               | 2     | 2/3             |

| JB bit, rel          | Jump if direct bit is set                                              | 3     | 3/4             |

| JNB bit, rel         | Jump if direct bit is not set                                          | 3     | 3/4             |

| JBC bit, rel         | Jump if direct bit is set and clear bit                                | 3     | 3/4             |

| Program Branching    |                                                                        |       |                 |

| ACALL addr11         | CALL addr11 Absolute subroutine call                                   |       |                 |

| LCALL addr16         | Long subroutine call                                                   | 3     | 4               |

| RET                  | Return from subroutine                                                 | 1     | 5               |

| RETI                 | Return from interrupt                                                  | 1     | 5               |

| AJMP addr11          | Absolute jump                                                          | 2     | 3               |

| LJMP addr16          | Long jump                                                              | 3     | 4               |

| SJMP rel             | Short jump (relative address)                                          | 2     | 3               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                                         | 1     | 3               |

| JZ rel               | Jump if A equals zero                                                  | 2     | 2/3             |

| JNZ rel              | Jump if A does not equal zero                                          | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal                         | 3     | 4/5             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal                           | 3     | 3/4             |

| CJNE Rn, #data, rel  | INE Rn, #data, rel Compare immediate to Register and jump if not equal |       | 3/4             |

| CJNE @Ri, #data, rel | NE @Ri, #data, rel Compare immediate to indirect and jump if not equal |       | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero                                | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero                             | 3     | 3/4             |

| NOP                  | No operation                                                           | 1     | 1               |

## SFR Definition 14.5. B: B Register

| Bit   | 7                                   | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------------------------------|-------------|---|---|---|---|---|---|--|--|

| Nam   | e                                   | B[7:0]      |   |   |   |   |   |   |  |  |

| Туре  | •                                   | R/W         |   |   |   |   |   |   |  |  |

| Rese  | et 0                                | 0           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A | SFR Address = 0xF0; Bit-Addressable |             |   |   |   |   |   |   |  |  |

| Bit   | Name                                | ne Function |   |   |   |   |   |   |  |  |

| 7:0   | B[7:0]                              | B Register. |   |   |   |   |   |   |  |  |

| This register serves as a second accumulator for certain arithmetic operations. |

|---------------------------------------------------------------------------------|

| I This redister serves as a second accumulator for certain animmetic operations |

|                                                                                 |

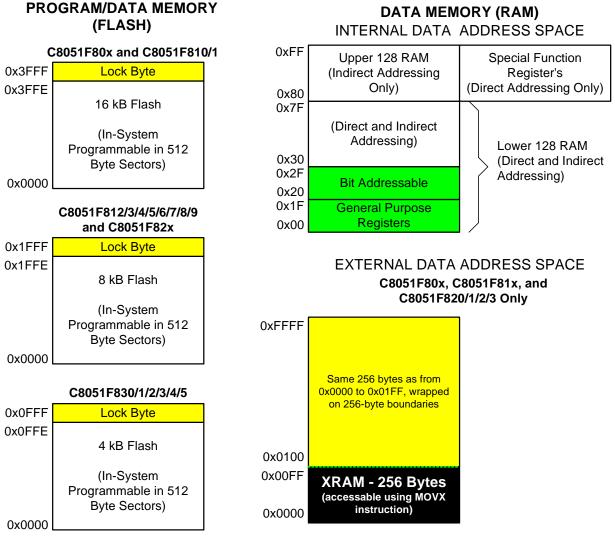

## **15. Memory Organization**

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization of the C8051F80x-83x device family is shown in Figure 15.1

Figure 15.1. C8051F80x-83x Memory Map

## **16. In-System Device Identification**

The C8051F80x-83x has SFRs that identify the device family and derivative. These SFRs can be read by firmware at runtime to determine the capabilities of the MCU that is executing code. This allows the same firmware image to run on MCUs with different memory sizes and peripherals, and dynamically changing functionality to suit the capabilities of that MCU.

In order for firmware to identify the MCU, it must read three SFRs. HWID describes the MCU's family, DERIVID describes the specific derivative within that device family, and REVID describes the hardware revision of the MCU.

### SFR Definition 16.1. HWID: Hardware Identification Byte

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------|---|---|---|---|---|---|---|--|

| Name  | HWID[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R         | R | R | R | R | R | R | R |  |

| Reset | 0         | 0 | 1 | 0 | 0 | 0 | 1 | 1 |  |

#### SFR Address = 0xB5

| Bit | Name      | Description                                                                         |

|-----|-----------|-------------------------------------------------------------------------------------|

| 7:0 | HWID[7:0] | Hardware Identification Byte.                                                       |

|     |           | Describes the MCU family.<br>0x23: Devices covered in this document (C8051F80x-83x) |

## **17. Special Function Registers**

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F80x-83x's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F80x-83x. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 17.1 lists the SFRs implemented in the C8051F80x-83x device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g., P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 17.2, for a detailed description of each register.

| F8 | SPI0CN | PCA0L    | PCA0H    | PCA0CPL0 | PCA0CPH0 | P0MAT   | P0MASK   | VDM0CN   |

|----|--------|----------|----------|----------|----------|---------|----------|----------|

| F0 | В      | P0MDIN   | P1MDIN   | EIP1     | EIP2     |         |          | PCA0PWM  |

| E8 | ADC0CN | PCA0CPL1 | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 | P1MAT   | P1MASK   | RSTSRC   |

| E0 | ACC    | XBR0     | XBR1     |          | IT01CF   |         | EIE1     | EIE2     |

| D8 | PCA0CN | PCA0MD   | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 | CRC0IN  | CRC0DATA |          |

| D0 | PSW    | REF0CN   | CRC0AUTO | CRC0CNT  | P0SKIP   | P1SKIP  | SMB0ADM  | SMB0ADR  |

| C8 | TMR2CN | REG0CN   | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H   | CRC0CN   | CRC0FLIP |

| C0 | SMB0CN | SMB0CF   | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL | ADC0LTH  |          |

| B8 | IP     | CS0SS    | CS0SE    | ADC0MX   | ADC0CF   | ADC0L   | ADC0H    |          |

| B0 | CS0CN  | OSCXCN   | OSCICN   | OSCICL   |          | HWID    | REVID    | FLKEY    |

| A8 | IE     | CLKSEL   |          | CS0DL    | CS0DH    | DERVID  |          |          |

| A0 | P2     | SPI0CFG  | SPI0CKR  | SPI0DAT  | POMDOUT  | P1MDOUT | P2MDOUT  |          |

| 98 | SCON0  | SBUF0    |          | CPT0CN   | CS0MX    | CPT0MD  | CS0CF    | CPT0MX   |

| 90 | P1     |          |          |          |          |         | CS0THL   | CS0THH   |

| 88 | TCON   | TMOD     | TL0      | TL1      | TH0      | TH1     | CKCON    | PSCTL    |

| 80 | P0     | SP       | DPL      | DPH      |          |         |          | PCON     |

|    | 0(8)   | 1(9)     | 2(A)     | 3(B)     | 4(C)     | 5(D)    | 6(E)     | 7(F)     |

### Table 17.1. Special Function Register (SFR) Memory Map

Note: SFR Addresses ending in 0x0 or 0x8 are bit-addressable locations, and can be used with bitwise instructions.

## SFR Definition 18.5. EIP1: Extended Interrupt Priority 1

| Bit   | 7        | 6             | 5    | 4     | 3                    | 2   | 1     | 0 |

|-------|----------|---------------|------|-------|----------------------|-----|-------|---|

| Name  | Reserved | Reserved      | PCP0 | PPCA0 | A0 PADC0 PWADC0 PMAT |     | PSMB0 |   |

| Туре  | W        | W R/W R/W R/W |      | R/W   | R/W                  | R/W | R/W   |   |

| Reset | 0        | 0             | 0    | 0     | 0                    | 0   | 0     | 0 |

SFR Address = 0xF3

| Bit | Name         | Function                                                                                                                                                     |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Reserved     | Must write 0.                                                                                                                                                |

| 5   | PCP0         | Comparator0 (CP0) Interrupt Priority Control.                                                                                                                |

|     |              | This bit sets the priority of the CP0 rising edge or falling edge interrupt.                                                                                 |

|     |              | 0: CP0 interrupt set to low priority level.                                                                                                                  |

|     |              | 1: CP0 interrupt set to high priority level.                                                                                                                 |

| 4   | PPCA0        | Programmable Counter Array (PCA0) Interrupt Priority Control.                                                                                                |

|     |              | This bit sets the priority of the PCA0 interrupt.                                                                                                            |

|     |              | 0: PCA0 interrupt set to low priority level.                                                                                                                 |

|     | <b>B4B00</b> | 1: PCA0 interrupt set to high priority level.                                                                                                                |

| 3   | PADC0        | ADC0 Conversion Complete Interrupt Priority Control.                                                                                                         |

|     |              | This bit sets the priority of the ADC0 Conversion Complete interrupt.                                                                                        |

|     |              | <ul><li>0: ADC0 Conversion Complete interrupt set to low priority level.</li><li>1: ADC0 Conversion Complete interrupt set to high priority level.</li></ul> |

| 2   | PWADC0       |                                                                                                                                                              |

| 2   | PWADCU       | ADC0 Window Comparator Interrupt Priority Control.<br>This bit sets the priority of the ADC0 Window interrupt.                                               |

|     |              | 0: ADC0 Window interrupt set to low priority level.                                                                                                          |

|     |              | 1: ADC0 Window interrupt set to high priority level.                                                                                                         |

| 1   | PMAT         | Port Match Interrupt Priority Control.                                                                                                                       |

|     | 1 101/31     | This bit sets the priority of the Port Match Event interrupt.                                                                                                |

|     |              | 0: Port Match interrupt set to low priority level.                                                                                                           |

|     |              | 1: Port Match interrupt set to high priority level.                                                                                                          |

| 0   | PSMB0        | SMBus (SMB0) Interrupt Priority Control.                                                                                                                     |

|     |              | This bit sets the priority of the SMB0 interrupt.                                                                                                            |

|     |              | 0: SMB0 interrupt set to low priority level.                                                                                                                 |

|     |              | 1: SMB0 interrupt set to high priority level.                                                                                                                |

### 20.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ s.

### 20.3. Suspend Mode

Suspend mode allows a system running from the internal oscillator to go to a very low power state similar to Stop mode, but the processor can be awakened by certain events without requiring a reset of the device. Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into Suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in Suspend mode. The exception to this is the Port Match feature and Timer 3, when it is run from an external oscillator source.

The clock divider bits CLKDIV[2:0] in register CLKSEL must be set to "divide by 1" when entering suspend mode.

Suspend mode can be terminated by five types of events, a port match (described in Section "23.5. Port Match" on page 150), a Timer 2 overflow (described in Section "28.2. Timer 2" on page 219), a comparator low output (if enabled), a capacitive sense greater-than comparator event, or a device reset event. In order to run Timer 3 in suspend mode, the timer must be configured to clock from the external clock source. When suspend mode is terminated, the device will continue execution on the instruction following the one that set the SUSPEND bit. If the wake event (port match or Timer 2 overflow) was configured to generate an interrupt, the interrupt will be serviced upon waking the device. If suspend mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

**Note:** The device will still enter suspend mode if a wake source is "pending", and the device will not wake on such pending sources. It is important to ensure that the intended wake source will trigger after the device enters suspend mode. For example, if a CS0 conversion completes and the interrupt fires before the device is in suspend mode, that interrupt cannot trigger the wake event. Because port match events are level-sensitive, pre-existing port match events will trigger a wake, as long as the match condition is still present when the device enters suspend.

### SFR Definition 22.4. OSCXCN: External Oscillator Control

| Bit   | 7      | 6 | 5          | 4  | 3 | 2         | 0 |  |  |

|-------|--------|---|------------|----|---|-----------|---|--|--|

| Name  | XTLVLD | Х | (OSCMD[2:0 | )] |   | XFCN[2:0] |   |  |  |

| Туре  | R      |   | R/W        |    | R | R/W       |   |  |  |

| Reset | 0      | 0 | 0 0 0 0 0  |    |   |           | 0 |  |  |

SFR Address = 0xB1

| Bit | Name        |         |                                                                                  | Function                                  |                 |  |  |  |  |  |  |

|-----|-------------|---------|----------------------------------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|--|

| 7   | XTLVLD      | Crystal | Oscillator Valid Flag.                                                           |                                           |                 |  |  |  |  |  |  |

|     |             | •       | nly when XOSCMD = 11                                                             |                                           |                 |  |  |  |  |  |  |

|     |             | -       | al Oscillator is unused or                                                       | •                                         |                 |  |  |  |  |  |  |

|     |             | ,       | al Oscillator is running ar                                                      |                                           |                 |  |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa | I Oscillator Mode Selec                                                          | ct.                                       |                 |  |  |  |  |  |  |

|     |             |         | ernal Oscillator circuit of                                                      |                                           |                 |  |  |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                                                           |                                           |                 |  |  |  |  |  |  |

|     |             |         | External CMOS Clock Mode with divide by 2 stage.                                 |                                           |                 |  |  |  |  |  |  |

|     |             |         | RC Oscillator Mode.                                                              |                                           |                 |  |  |  |  |  |  |

|     |             |         | : Capacitor Oscillator Mode.                                                     |                                           |                 |  |  |  |  |  |  |

|     |             | -       | ): Crystal Oscillator Mode.<br>: Crystal Oscillator Mode with divide by 2 stage. |                                           |                 |  |  |  |  |  |  |

|     |             |         |                                                                                  |                                           |                 |  |  |  |  |  |  |

| 3   | Unused      |         | Read = 0; Write = Don't Care                                                     |                                           |                 |  |  |  |  |  |  |

| 2:0 | XFCN[2:0]   |         | I Oscillator Frequency                                                           |                                           |                 |  |  |  |  |  |  |

|     |             |         | -                                                                                | uency for Crystal or RC r                 | node.           |  |  |  |  |  |  |

|     |             |         | ording to the desired K F                                                        |                                           |                 |  |  |  |  |  |  |

|     |             | XFCN    | Crystal Mode                                                                     | RC Mode                                   | C Mode          |  |  |  |  |  |  |

|     |             | 000     | f ≤ 32 kHz                                                                       | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |  |

|     |             | 001     | 32 kHz < f ≤ 84 kHz                                                              | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |  |

|     |             | 010     | 84 kHz < f ≤ 225 kHz                                                             | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |  |

|     |             | 011     | 225 kHz < f ≤ 590 kHz                                                            | 100 kHz < f ≤ 200 kHz                     | K Factor = 22   |  |  |  |  |  |  |

|     |             | 100     | 590 kHz < f ≤ 1.5 MHz                                                            | 200 kHz < f $\leq$ 400 kHz                | K Factor = 65   |  |  |  |  |  |  |

|     |             | 101     | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$                                          | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |  |  |

|     |             | 110     | $4 \text{ MHz} < f \le 10 \text{ MHz}$                                           | 800 kHz $<$ f $\leq$ 1.6 MHz              | K Factor = 664  |  |  |  |  |  |  |

|     |             | 111     | 10 MHz < f ≤ 30 MHz                                                              | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |  |

### SFR Definition 23.16. P2MDOUT: Port 2 Output Mode

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0          |

|-------|---|---|---|---|---|---|---|------------|

| Name  |   |   |   |   |   |   |   | P2MDOUT[0] |

| Туре  | R | R | R | R | R | R | R | R/W        |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0          |

SFR Address = 0xA6

| Bit | Name       | Function                                                      |

|-----|------------|---------------------------------------------------------------|

| 7:1 | Unused     | Read = 0000000b; Write = Don't Care                           |

| 0   | P2MDOUT[0] | Output Configuration Bits for P2.0.                           |

|     |            | 0: P2.0 Output is open-drain.<br>1: P2.0 Output is push-pull. |

## SFR Definition 25.1. SPI0CFG: SPI0 Configuration

| Bit   | 7      | 6     | 5     | 4     | 3      | 2     | 1    | 0     |

|-------|--------|-------|-------|-------|--------|-------|------|-------|

| Name  | SPIBSY | MSTEN | СКРНА | CKPOL | SLVSEL | NSSIN | SRMT | RXBMT |

| Туре  | R      | R/W   | R/W   | R/W   | R      | R     | R    | R     |

| Reset | 0      | 0     | 0     | 0     | 0      | 1     | 1    | 1     |

SFR Address = 0xA1

| Bit   | Name           | Function                                                                                                     |

|-------|----------------|--------------------------------------------------------------------------------------------------------------|

| 7     | SPIBSY         | SPI Busy.                                                                                                    |

|       |                | This bit is set to logic 1 when a SPI transfer is in progress (master or slave mode).                        |

| 6     | MSTEN          | Master Mode Enable.                                                                                          |

|       |                | 0: Disable master mode. Operate in slave mode.                                                               |

|       |                | 1: Enable master mode. Operate as a master.                                                                  |

| 5     | CKPHA          | SPI0 Clock Phase.                                                                                            |

|       |                | 0: Data centered on first edge of SCK period.*                                                               |

|       |                | 1: Data centered on second edge of SCK period.*                                                              |

| 4     | CKPOL          | SPI0 Clock Polarity.                                                                                         |

|       |                | 0: SCK line low in idle state.                                                                               |

|       |                | 1: SCK line high in idle state.                                                                              |

| 3     | SLVSEL         | Slave Selected Flag.                                                                                         |

|       |                | This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected                       |

|       |                | slave. It is cleared to logic 0 when NSS is high (slave not selected). This bit does                         |

|       |                | not indicate the instantaneous value at the NSS pin, but rather a de-glitched ver-<br>sion of the pin input. |

| 2     | NSSIN          | NSS Instantaneous Pin Input.                                                                                 |

|       |                | This bit mimics the instantaneous value that is present on the NSS port pin at the                           |

|       |                | time that the register is read. This input is not de-glitched.                                               |

| 1     | SRMT           | Shift Register Empty (valid in slave mode only).                                                             |

|       |                | This bit will be set to logic 1 when all data has been transferred in/out of the shift                       |

|       |                | register, and there is no new information available to read from the transmit buffer                         |

|       |                | or write to the receive buffer. It returns to logic 0 when a data byte is transferred to                     |

|       |                | the shift register from the transmit buffer or by a transition on SCK. SRMT = 1 when in Master Mode.         |

| 0     | RXBMT          | Receive Buffer Empty (valid in slave mode only).                                                             |

|       |                | This bit will be set to logic 1 when the receive buffer has been read and contains no                        |

|       |                | new information. If there is new information available in the receive buffer that has                        |

|       |                | not been read, this bit will return to logic 0. RXBMT = 1 when in Master Mode.                               |

| Note: | In slave mode, | data on MOSI is sampled in the center of each data bit. In master mode, data on MISO is                      |

|       |                | YSCLK before the end of each data bit, to provide maximum settling time for the slave device.                |

|       | See Table 25.1 | for timing parameters.                                                                                       |

# Table 26.5. SMBus Status Decoding With Hardware ACK Generation Disabled (EHACK = 0)(Continued)

|                            | Va     | alue   | es F  | Rea            | d                                                  |                                                                                             |                                                            |     | lues<br>Vrit |      | itus<br>ected                  |

|----------------------------|--------|--------|-------|----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|--------------|------|--------------------------------|

| Mode                       | Status | Vector | ACKRQ | ARBLOST        | ACK                                                | Current SMbus State                                                                         | Typical Response Options                                   | STA | STO          | ACK  | Next Status<br>Vector Expected |

| er                         |        |        | 0     | 0              | 0                                                  | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).             | 0   | 0            | Х    | 0001                           |

| smitte                     | 010    | 00     | 0     | 0              | 0 1 A slave byte was transmitted;<br>ACK received. |                                                                                             | Load SMB0DAT with next data byte to transmit.              | 0   | 0            | Х    | 0100                           |

| Slave Transmitter          |        |        | 0     | 1              | Х                                                  | A Slave byte was transmitted; error detected.                                               | No action required (expecting Master to end transfer).     | 0   | 0            | Х    | 0001                           |

| Slav                       | 010    | )1     | 0     | х              | x                                                  | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                 | 0   | 0            | Х    |                                |

|                            |        |        |       |                |                                                    |                                                                                             | If Write, Acknowledge received address                     | 0   | 0            | 1    | 0000                           |

|                            |        |        | 1     | 0              | Х                                                  | A slave address + R/W was received; ACK requested.                                          | If Read, Load SMB0DAT with data byte; ACK received address | 0   | 0            | 1    | 0100                           |

|                            |        |        |       |                |                                                    |                                                                                             | NACK received address.                                     | 0   | 0            | 0    | —                              |

|                            | 0010   |        |       |                |                                                    | If Write, Acknowledge received address                                                      | 0                                                          | 0   | 1            | 0000 |                                |

| eiver                      |        |        |       | 1              | х                                                  | Lost arbitration as master;<br>slave address + R/W received;                                | If Read, Load SMB0DAT with data byte; ACK received address | 0   | 0            | 1    | 0100                           |

| ece                        |        |        |       | ACK requested. |                                                    | ACK requested.                                                                              | NACK received address.                                     | 0   | 0            | 0    | —                              |

| Slave Receiver             |        |        |       |                |                                                    |                                                                                             | Reschedule failed transfer;<br>NACK received address.      | 1   | 0            | 0    | 1110                           |

| S                          | 000    | )1     | 0     | 0              | х                                                  | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                 | 0   | 0            | Х    | _                              |

|                            |        | -      | 1     | 1              | Х                                                  | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).            | 0   | 0            | 0    |                                |

|                            | 000    | 00     | 1     | 0              | х                                                  | A slave byte was received;<br>ACK requested.                                                | Acknowledge received byte;<br>Read SMB0DAT.                | 0   | 0            | 1    | 0000                           |

|                            |        |        |       |                |                                                    | ACR lequested.                                                                              | NACK received byte.                                        | 0   | 0            | 0    | —                              |

| uo                         | 001    | 0      | 0     | 1              | Х                                                  | Lost arbitration while attempt-                                                             | Abort failed transfer.                                     | 0   | 0            | Х    |                                |

| diti                       | 001    |        | U     | 1              | Λ                                                  | ing a repeated START.                                                                       | Reschedule failed transfer.                                | 1   | 0            | Х    | 1110                           |

| Con                        | 000    | )1     | 0     | 1              | Х                                                  | Lost arbitration due to a                                                                   | Abort failed transfer.                                     | 0   | 0            | Х    | —                              |

| or                         | 000    | , ,    | U     | 1              | Λ                                                  | detected STOP.                                                                              | Reschedule failed transfer.                                | 1   | 0            | Х    | 1110                           |

| <b>Bus Error Condition</b> | 000    | 0      | 1     | 1              | Х                                                  | Lost arbitration while transmit-                                                            | Abort failed transfer.                                     | 0   | 0            | 0    | —                              |

| Bus                        | 000    | .0     | I     | 1              | ^                                                  | ting a data byte as master.                                                                 | Reschedule failed transfer.                                | 1   | 0            | 0    | 1110                           |

|                 | Valu                           | es I  | Rea     | d                       |                                                    |                                                                                                                        |   | lues<br>Vrit |      | itus<br>iected                 |

|-----------------|--------------------------------|-------|---------|-------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|--------------|------|--------------------------------|

| Mode            | Status<br>Vector               | ACKRQ | ARBLOST | ACK                     | Current SMbus State                                |                                                                                                                        |   | STO          | ACK  | Next Status<br>Vector Expected |

|                 | 1110                           | 0     | 0       | Х                       | A master START was gener-<br>ated.                 | Load slave address + R/W into SMB0DAT.                                                                                 | 0 | 0            | Х    | 1100                           |

|                 |                                |       | _       | _                       | A master data or address byte                      | Set STA to restart transfer.                                                                                           | 1 | 0            | Х    | 1110                           |

| er              |                                | 0     | 0       | 0                       | was transmitted; NACK received.                    | Abort transfer.                                                                                                        | 0 | 1            | Х    | —                              |

| smitte          |                                |       |         |                         |                                                    | Load next data byte into<br>SMB0DAT.                                                                                   | 0 | 0            | Х    | 1100                           |

| ran             | Master Transmitter<br>1100 0 0 |       |         | End transfer with STOP. | 0                                                  | 1                                                                                                                      | Х | _            |      |                                |

| aster T         |                                | 0     | 0       | 1                       | A master data or address byte was transmitted; ACK | End transfer with STOP and start another transfer.                                                                     | 1 | 1            | Х    | _                              |

| Ř               |                                | Ŭ     | Ŭ       |                         | received.                                          | Send repeated START.                                                                                                   | 1 | 0            | Х    | 1110                           |

|                 |                                |       |         |                         |                                                    | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT). Set ACK for initial<br>data byte. | 0 | 0            | 1    | 1000                           |

|                 |                                |       |         |                         |                                                    | Set ACK for next data byte;<br>Read SMB0DAT.                                                                           | 0 | 0            | 1    | 1000                           |

|                 |                                | 0     | 0       | 1                       | A master data byte was                             | Set NACK to indicate next data<br>byte as the last data byte;<br>Read SMB0DAT.                                         | 0 | 0            | 0    | 1000                           |

| er              |                                |       |         |                         | received; ACK sent.                                | Initiate repeated START.                                                                                               | 1 | 0            | 0    | 1110                           |

| Aaster Receiver | 1000                           |       |         |                         |                                                    | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI).                                         | 0 | 0            | Х    | 1100                           |

| aste            |                                |       |         |                         |                                                    | Read SMB0DAT; send STOP.                                                                                               | 0 | 1            | 0    | —                              |

| Ŵ               |                                |       |         | A master data byte was  | Read SMB0DAT; Send STOP followed by START.         | 1                                                                                                                      | 1 | 0            | 1110 |                                |

|                 |                                | 0     | 0       | 0                       | received; NACK sent (last                          | Initiate repeated START.                                                                                               | 1 | 0            | 0    | 1110                           |

|                 |                                |       |         |                         | byte).                                             | Switch to Master Transmitter<br>Mode (write to SMB0DAT before<br>clearing SI).                                         | 0 | 0            | Х    | 1100                           |

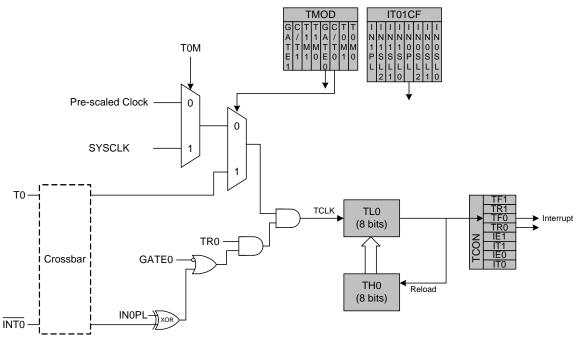

Figure 28.2. T0 Mode 2 Block Diagram

### 28.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates or overflow conditions for other peripherals. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

## SFR Definition 28.6. TH0: Timer 0 High Byte

| Bit   | 7            | 6                                                        | 5                  | 4   | 3        | 2 | 1 | 0 |  |  |  |

|-------|--------------|----------------------------------------------------------|--------------------|-----|----------|---|---|---|--|--|--|

| Name  | 9            |                                                          |                    | TH0 | [7:0]    |   |   |   |  |  |  |

| Туре  | •            |                                                          |                    | R/  | W        |   |   |   |  |  |  |

| Rese  | <b>t</b> 0   | 0                                                        | 0                  | 0   | 0        | 0 | 0 | 0 |  |  |  |

| SFR A | ddress = 0x8 | С                                                        |                    |     |          |   |   |   |  |  |  |

| Bit   | Name         |                                                          |                    |     | Function |   |   |   |  |  |  |

| 7:0   | TH0[7:0]     | Timer 0 Hig                                              | Timer 0 High Byte. |     |          |   |   |   |  |  |  |

|       |              | The THO register is the high byte of the 16-bit Timer 0. |                    |     |          |   |   |   |  |  |  |

## SFR Definition 28.7. TH1: Timer 1 High Byte

| Bit                | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|---------------|---|---|---|---|---|---|---|

| Name               | TH1[7:0]      |   |   |   |   |   |   |   |

| Туре               | R/W           |   |   |   |   |   |   |   |

| Reset              | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0x8D |               |   |   |   |   |   |   |   |

| Bit                | Name Function |   |   |   |   |   |   |   |

| Bit | Name     | Function                                                 |  |  |  |  |

|-----|----------|----------------------------------------------------------|--|--|--|--|

| 7:0 | TH1[7:0] | Timer 1 High Byte.                                       |  |  |  |  |

|     |          | The TH1 register is the high byte of the 16-bit Timer 1. |  |  |  |  |

## SFR Definition 28.11. TMR2L: Timer 2 Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | TMR2L[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name       | Function                                                                                                                                          |  |  |  |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |  |  |  |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |  |  |  |

## SFR Definition 28.12. TMR2H Timer 2 High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | TMR2H[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xCD

| Bit | Name       | Function                                                                                                                                            |  |  |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                                                                                   |  |  |  |

|     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2H contains the 8-bit high byte timer value. |  |  |  |