Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Not For New Designs                                             |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f825-gsr |

## **List of Tables** 1. System Overview 2. Ordering Information 3. Pin Definitions 4. QFN-20 Package Specifications 5. QSOP-24 Package Specifications 6. SOIC-16 Package Specifications 7. Electrical Characteristics Table 7.2. Global Electrical Characteristics .......40 Table 7.4. Reset Electrical Characteristics ......41 8. 10-Bit ADC (ADC0) 9. Temperature Sensor 10. Voltage and Ground Reference Options 11. Voltage Regulator (REG0) 12. Comparator0 13. Capacitive Sense (CS0) 14. CIP-51 Microcontroller Table 14.1. CIP-51 Instruction Set Summary ......84 15. Memory Organization 16. In-System Device Identification 17. Special Function Registers Table 17.1. Special Function Register (SFR) Memory Map ...... 97 18. Interrupts

# C8051F80x-83x

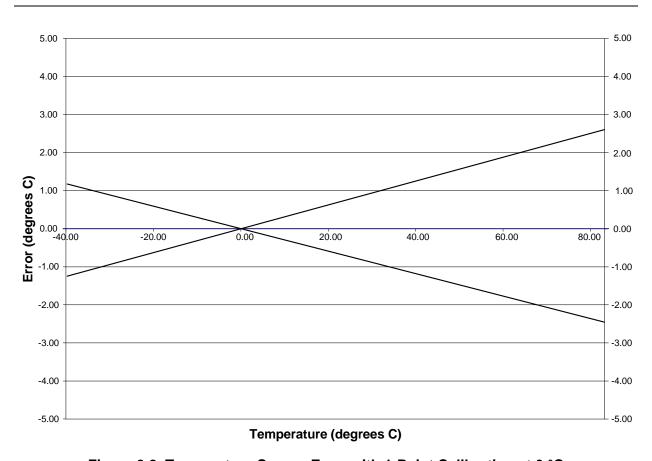

Figure 9.2. Temperature Sensor Error with 1-Point Calibration at 0 °C

## SFR Definition 12.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

### SFR Address = 0x9B

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0                                                      |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## 16. In-System Device Identification

The C8051F80x-83x has SFRs that identify the device family and derivative. These SFRs can be read by firmware at runtime to determine the capabilities of the MCU that is executing code. This allows the same firmware image to run on MCUs with different memory sizes and peripherals, and dynamically changing functionality to suit the capabilities of that MCU.

In order for firmware to identify the MCU, it must read three SFRs. HWID describes the MCU's family, DERIVID describes the specific derivative within that device family, and REVID describes the hardware revision of the MCU.

## SFR Definition 16.1. HWID: Hardware Identification Byte

| Bit   | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------|---|---|---|---|---|---|--|--|--|

| Name  |   | HWID[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  | R | R         | R | R | R | R | R | R |  |  |  |

| Reset | 0 | 0         | 1 | 0 | 0 | 0 | 1 | 1 |  |  |  |

#### SFR Address = 0xB5

| Bit | Name      | Description                                                                      |

|-----|-----------|----------------------------------------------------------------------------------|

| 7:0 | HWID[7:0] | Hardware Identification Byte.                                                    |

|     |           | Describes the MCU family. 0x23: Devices covered in this document (C8051F80x-83x) |

## SFR Definition 18.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xA8; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                               |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | Enable All Interrupts. Globally enables/disables all interrupts. It overrides individual interrupt mask settings. 0: Disable all interrupt sources. 1: Enable each interrupt according to its individual mask setting. |

| 6   | ESPI0 | Enable Serial Peripheral Interface (SPI0) Interrupt. This bit sets the masking of the SPI0 interrupts. 0: Disable all SPI0 interrupts. 1: Enable interrupt requests generated by SPI0.                                 |

| 5   | ET2   | Enable Timer 2 Interrupt. This bit sets the masking of the Timer 2 interrupt. 0: Disable Timer 2 interrupt. 1: Enable interrupt requests generated by the TF2L or TF2H flags.                                          |

| 4   | ES0   | Enable UART0 Interrupt. This bit sets the masking of the UART0 interrupt. 0: Disable UART0 interrupt. 1: Enable UART0 interrupt.                                                                                       |

| 3   | ET1   | Enable Timer 1 Interrupt. This bit sets the masking of the Timer 1 interrupt. 0: Disable all Timer 1 interrupt. 1: Enable interrupt requests generated by the TF1 flag.                                                |

| 2   | EX1   | Enable External Interrupt 1. This bit sets the masking of External Interrupt 1. 0: Disable external interrupt 1. 1: Enable interrupt requests generated by the INT1 input.                                             |

| 1   | ET0   | Enable Timer 0 Interrupt. This bit sets the masking of the Timer 0 interrupt. 0: Disable all Timer 0 interrupt. 1: Enable interrupt requests generated by the TF0 flag.                                                |

| 0   | EX0   | Enable External Interrupt 0. This bit sets the masking of External Interrupt 0. 0: Disable external interrupt 0. 1: Enable interrupt requests generated by the INTO input.                                             |

## SFR Definition 18.6. EIP2: Extended Interrupt Priority 2

| Bit   | 7        | 6        | 5        | 4        | 3        | 2        | 1      | 0      |

|-------|----------|----------|----------|----------|----------|----------|--------|--------|

| Name  | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | PSCGRT | PSCCPT |

| Туре  | R        | R        | R        | R        | R        | R        | R/W    | R/W    |

| Reset | 0        | 0        | 0        | 0        | 0        | 0        | 0      | 0      |

### SFR Address = 0xF4

| Bit | Name     | Function                                                                              |

|-----|----------|---------------------------------------------------------------------------------------|

| 7:2 | Reserved |                                                                                       |

| 1   | PSCGRT   | Capacitive Sense Greater Than Comparator Priority Control.                            |

|     |          | This bit sets the priority of the Capacitive Sense Greater Than Comparator interrupt. |

|     |          | 0: CS0 Greater Than Comparator interrupt set to low priority level.                   |

|     |          | 1: CS0 Greater Than Comparator set to high priority level.                            |

| 0   | PSCCPT   | Capacitive Sense Conversion Complete Priority Control.                                |

|     |          | This bit sets the priority of the Capacitive Sense Conversion Complete interrupt.     |

|     |          | 0: CS0 Conversion Complete set to low priority level.                                 |

|     |          | 1: CS0 Conversion Complete set to high priority level.                                |

## 21.2. Power-Fail Reset / V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 21.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is enabled and selected as a reset source after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is disabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be disabled after the reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it should be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. In some applications, this reset may be undesirable. If this is not desirable in the application, a delay should be introduced between enabling the monitor and selecting it as a reset source. The procedure for enabling the  $V_{DD}$  monitor and configuring it as a reset source from a disabled state is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = 1).

- 2. If necessary, wait for the V<sub>DD</sub> monitor to stabilize.

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 21.2 for  $V_{DD}$  monitor timing; note that the power-on-reset delay is not incurred after a  $V_{DD}$  monitor reset. See Section "7. Electrical Characteristics" on page 39 for complete electrical characteristics of the  $V_{DD}$  monitor.

## SFR Definition 21.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|---------|--------|--------|--------|--------|--------|--------|

| Name  | VDMEN  | VDDSTAT |        |        |        |        |        |        |

| Туре  | R/W    | R       | R      | R      | R      | R      | R      | R      |

| Reset | Varies | Varies  | Varies | Varies | Varies | Varies | Varies | Varies |

#### SFR Address = 0xFF

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 21.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. After a power-on reset, the VDD monitor is enabled, and this bit will read 1. The state of this bit is sticky through any other reset source.  0: V <sub>DD</sub> Monitor Disabled.  1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |         | This bit indicates the current power supply status (V <sub>DD</sub> Monitor output).  0: V <sub>DD</sub> is at or below the V <sub>DD</sub> monitor threshold.  1: V <sub>DD</sub> is above the V <sub>DD</sub> monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5:0 | Unused  | Read = Varies; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 21.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. As<u>serting</u> an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Section "7. Electrical Characteristics" on page 39 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 21.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the MCD timeout, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

## **SFR Definition 22.4. OSCXCN: External Oscillator Control**

| Bit   | 7      | 6   | 5         | 4  | 3 | 2         | 1   | 0 |  |

|-------|--------|-----|-----------|----|---|-----------|-----|---|--|

| Name  | XTLVLD | X   | OSCMD[2:0 | )] |   | XFCN[2:0] |     |   |  |

| Туре  | R      | R/W |           |    | R |           | R/W |   |  |

| Reset | 0      | 0   | 0         | 0  | 0 | 0         | 0   | 0 |  |

### SFR Address = 0xB1

| Bit | Name        |         | Function                                                                            |                            |                 |  |  |  |  |  |

|-----|-------------|---------|-------------------------------------------------------------------------------------|----------------------------|-----------------|--|--|--|--|--|

| 7   | XTLVLD      | Crystal | Oscillator Valid Flag.                                                              |                            |                 |  |  |  |  |  |

|     |             | (Read o | (Read only when XOSCMD = 11x.)                                                      |                            |                 |  |  |  |  |  |

|     |             | _       | 0: Crystal Oscillator is unused or not yet stable.                                  |                            |                 |  |  |  |  |  |

|     |             | ,       | al Oscillator is running ar                                                         |                            |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa | I Oscillator Mode Selec                                                             | ct.                        |                 |  |  |  |  |  |

|     |             |         | ternal Oscillator circuit of                                                        |                            |                 |  |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                                                              |                            |                 |  |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                                                              | e with divide by 2 stage.  |                 |  |  |  |  |  |

|     |             |         | Oscillator Mode.                                                                    |                            |                 |  |  |  |  |  |

|     |             |         | pacitor Oscillator Mode. /stal Oscillator Mode.                                     |                            |                 |  |  |  |  |  |

|     |             | -       | rstal Oscillator Mode with                                                          | divide by 2 stage          |                 |  |  |  |  |  |

| 3   | Unused      | •       | 0; Write = Don't Care                                                               | - arriae by 2 stage.       |                 |  |  |  |  |  |

|     |             |         |                                                                                     | Control Dita               |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   |         | Il Oscillator Frequency                                                             |                            |                 |  |  |  |  |  |

|     |             |         | =                                                                                   | quency for Crystal or RC r | node.           |  |  |  |  |  |

|     |             |         | Set according to the desired K Factor for C mode.  KFCN Crystal Mode RC Mode C Mode |                            |                 |  |  |  |  |  |

|     |             | XFCN    | Crystal Mode                                                                        | C Mode                     |                 |  |  |  |  |  |

|     |             | 000     | f≤32 kHz                                                                            | f≤25 kHz                   | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001     | 32 kHz < f ≤ 84 kHz                                                                 | 25 kHz < f ≤ 50 kHz        | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010     | 10 84 kHz < f ≤ 225 kHz 50 kHz < f ≤ 100 kHz K Factor = 7.7                         |                            |                 |  |  |  |  |  |

|     |             | 011     | 011 225 kHz < f $\leq$ 590 kHz 100 kHz < f $\leq$ 200 kHz K Factor = 22             |                            |                 |  |  |  |  |  |

|     |             | 100     | 0 590 kHz < f ≤ 1.5 MHz 200 kHz < f ≤ 400 kHz K Factor = 65                         |                            |                 |  |  |  |  |  |

|     |             | 101     | 1.5 MHz < f ≤ 4 MHz                                                                 |                            |                 |  |  |  |  |  |

|     |             | 110     | 4 MHz < f ≤ 10 MHz                                                                  | 800 kHz < f ≤ 1.6 MHz      | K Factor = 664  |  |  |  |  |  |

|     |             | 111     | 10 MHz < f ≤ 30 MHz                                                                 | 1.6 MHz < f ≤ 3.2 MHz      | K Factor = 1590 |  |  |  |  |  |

#### 22.3.1. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 22.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 22.4 (OSCXCN register). For example, an 11.0592 MHz crystal requires an XFCN setting of 111b and a 32.768 kHz Watch Crystal requires an XFCN setting of 001b. After an external 32.768 kHz oscillator is stabilized, the XFCN setting can be switched to 000 to save power. It is recommended to enable the missing clock detector before switching the system clock to any external oscillator source.

When the crystal oscillator is first enabled, the oscillator amplitude detection circuit requires a settling time to achieve proper bias. Introducing a delay of 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is as follows:

- 1. Force XTAL1 and XTAL2 to a low state. This involves enabling the Crossbar and writing 0 to the port pins associated with XTAL1 and XTAL2.

- 2. Configure XTAL1 and XTAL2 as analog inputs.

- 3. Enable the external oscillator.

- 4. Wait at least 1 ms.

- 5. Poll for XTLVLD = 1.

- 6. If desired, enable the Missing Clock Detector.

- 7. Switch the system clock to the external oscillator.

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

**Note:** The desired load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 22.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 22.2.

#### 22.3.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 22.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation 22.2, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and  $V_{DD} = the$  MCU power supply in volts.

### **Equation 22.2. C Mode Oscillator Frequency**

$$f = (KF)/(R \times V_{DD})$$

For example: Assume  $V_{DD} = 3.0 \text{ V}$  and f = 150 kHz:

$f = KF / (C \times VDD)$ 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 22.4 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

Table 23.2. Port I/O Assignment for Digital Functions

| Digital Function                                                    | Potentially Assignable Port Pins                                                                                                                      | SFR(s) used for<br>Assignment |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| UART0, SPI0, SMBus,<br>SYSCLK, PCA0 (CEX0-2<br>and ECI), T0, or T1. | Any Port pin available for assignment by the Crossbar. This includes P0.0 - P1.7 <sup>2</sup> pins which have their PnSKIP bit set to 0. <sup>1</sup> | XBR0, XBR1                    |

| Any pin used for GPIO                                               | P0.0–P2.0 <sup>2</sup>                                                                                                                                | PnSKIP                        |

#### Notes:

- 1. The Crossbar will always assign UART0 pins to P0.4 and P0.5.

- 2. Port pins P1.4–P1.7 are not available on the 16-pin packages.

#### 23.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions

External digital event capture functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The digital event capture functions do not require dedicated pins and will function on both GPIO pins (PnSKIP = 1) and pins in use by the Crossbar (PnSKIP = 0). External digital event capture functions cannot be used on pins configured for analog I/O. Table 23.3 shows all available external digital event capture functions.

Table 23.3. Port I/O Assignment for External Digital Event Capture Functions

| Digital Function                                                    | Potentially Assignable Port Pins | SFR(s) used for<br>Assignment  |  |  |  |  |

|---------------------------------------------------------------------|----------------------------------|--------------------------------|--|--|--|--|

| External Interrupt 0                                                | P0.0–P0.7                        | IT01CF                         |  |  |  |  |

| External Interrupt 1                                                | P0.0–P0.7                        | IT01CF                         |  |  |  |  |

| Port Match                                                          | P0.0-P1.7*                       | P0MASK, P0MAT<br>P1MASK, P1MAT |  |  |  |  |

| Note: Port pins P1.4–P1.7 are not available on the 16-pin packages. |                                  |                                |  |  |  |  |

## SFR Definition 23.16. P2MDOUT: Port 2 Output Mode

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0          |

|-------|---|---|---|---|---|---|---|------------|

| Name  |   |   |   |   |   |   |   | P2MDOUT[0] |

| Туре  | R | R | R | R | R | R | R | R/W        |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0          |

### SFR Address = 0xA6

| Bit | Name       | Function                           |  |  |  |

|-----|------------|------------------------------------|--|--|--|

| 7:1 | Unused     | ead = 0000000b; Write = Don't Care |  |  |  |

| 0   | P2MDOUT[0] | utput Configuration Bits for P2.0. |  |  |  |

|     |            | P2.0 Output is open-drain.         |  |  |  |

|     |            | 1: P2.0 Output is push-pull.       |  |  |  |

## SFR Definition 24.1. CRC0CN: CRC0 Control

| Bit   | 7   | 6   | 5   | 4       | 3        | 2       | 1     | 0       |

|-------|-----|-----|-----|---------|----------|---------|-------|---------|

| Name  |     |     |     | CRC0SEL | CRC0INIT | CRC0VAL | CRC0P | NT[1:0] |

| Туре  | R/W | R/W | R/W | R/W     | R/W      | R/W     | R/    | W       |

| Reset | 0   | 0   | 0   | 0       | 0        | 0       | 0     | 0       |

### SFR Address = 0xCE

| Bit | Name         | Function                                                                                                                                                                                                                             |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused       | Read = 000b; Write = Don't Care.                                                                                                                                                                                                     |

| 4   | CRC0SEL      | CRC0 Polynomial Select Bit.                                                                                                                                                                                                          |

|     |              | This bit selects the CRC0 polynomial and result length (32-bit or 16-bit).  0: CRC0 uses the 32-bit polynomial 0x04C11DB7 for calculating the CRC result.  1: CRC0 uses the 16-bit polynomial 0x1021 for calculating the CRC result. |

| 3   | CRC0INIT     | CRC0 Result Initialization Bit.                                                                                                                                                                                                      |

|     |              | Writing a 1 to this bit initializes the entire CRC result based on CRC0VAL.                                                                                                                                                          |

| 2   | CRC0VAL      | CRC0 Set Value Initialization Bit.                                                                                                                                                                                                   |

|     |              | This bit selects the set value of the CRC result.                                                                                                                                                                                    |

|     |              | 0: CRC result is set to 0x00000000 on write of 1 to CRC0INIT.                                                                                                                                                                        |

|     |              | 1: CRC result is set to 0xFFFFFFFF on write of 1 to CRC0INIT.                                                                                                                                                                        |

| 1:0 | CRC0PNT[1:0] | CRC0 Result Pointer.                                                                                                                                                                                                                 |

|     |              | Specifies the byte of the CRC result to be read/written on the next access to CRC0DAT. The value of these bits will auto-increment upon each read or write. For CRC0SEL = 0:                                                         |

|     |              | 00: CRC0DAT accesses bits 7–0 of the 32-bit CRC result.                                                                                                                                                                              |

|     |              | 01: CRC0DAT accesses bits 15–8 of the 32-bit CRC result.                                                                                                                                                                             |

|     |              | 10: CRC0DAT accesses bits 23–16 of the 32-bit CRC result.                                                                                                                                                                            |

|     |              | 11: CRC0DAT accesses bits 31–24 of the 32-bit CRC result.                                                                                                                                                                            |

|     |              | For CRC0SEL = 1:  00: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.                                                                                                                                                            |

|     |              | 01: CRC0DAT accesses bits 15–8 of the 16-bit CRC result.                                                                                                                                                                             |

|     |              | 10: CRCODAT accesses bits 7–0 of the 16-bit CRC result.                                                                                                                                                                              |

|     |              | 11: CRC0DAT accesses bits 15–8 of the 16-bit CRC result.                                                                                                                                                                             |

## SFR Definition 25.1. SPI0CFG: SPI0 Configuration

| Bit   | 7      | 6     | 5     | 4     | 3      | 2     | 1    | 0     |

|-------|--------|-------|-------|-------|--------|-------|------|-------|

| Name  | SPIBSY | MSTEN | СКРНА | CKPOL | SLVSEL | NSSIN | SRMT | RXBMT |

| Туре  | R      | R/W   | R/W   | R/W   | R      | R     | R    | R     |

| Reset | 0      | 0     | 0     | 0     | 0      | 1     | 1    | 1     |

### SFR Address = 0xA1

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7   | SPIBSY | SPI Busy.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|     |        | This bit is set to logic 1 when a SPI transfer is in progress (master or slave mode).                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 6   | MSTEN  | Master Mode Enable.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|     |        | 0: Disable master mode. Operate in slave mode.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|     |        | 1: Enable master mode. Operate as a master.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 5   | СКРНА  | SPI0 Clock Phase.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|     |        | 0: Data centered on first edge of SCK period.*                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|     |        | 1: Data centered on second edge of SCK period.*                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 4   | CKPOL  | SPI0 Clock Polarity.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|     |        | 0: SCK line low in idle state.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|     |        | 1: SCK line high in idle state.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 3   | SLVSEL | Slave Selected Flag.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|     |        | This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected slave. It is cleared to logic 0 when NSS is high (slave not selected). This bit does not indicate the instantaneous value at the NSS pin, but rather a de-glitched version of the pin input.                                                                                       |  |  |  |  |  |  |

| 2   | NSSIN  | NSS Instantaneous Pin Input.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|     |        | This bit mimics the instantaneous value that is present on the NSS port pin at the time that the register is read. This input is not de-glitched.                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 1   | SRMT   | Shift Register Empty (valid in slave mode only).                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|     |        | This bit will be set to logic 1 when all data has been transferred in/out of the shift register, and there is no new information available to read from the transmit buffer or write to the receive buffer. It returns to logic 0 when a data byte is transferred to the shift register from the transmit buffer or by a transition on SCK. SRMT = 1 when in Master Mode. |  |  |  |  |  |  |

| 0   | RXBMT  | Receive Buffer Empty (valid in slave mode only).                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|     |        | This bit will be set to logic 1 when the receive buffer has been read and contains no new information. If there is new information available in the receive buffer that has not been read, this bit will return to logic 0. RXBMT = 1 when in Master Mode.                                                                                                                |  |  |  |  |  |  |

**Note:** In slave mode, data on MOSI is sampled in the center of each data bit. In master mode, data on MISO is sampled one SYSCLK before the end of each data bit, to provide maximum settling time for the slave device. See Table 25.1 for timing parameters.

### 28. Timers

Each MCU includes three counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and one is a 16-bit auto-reload timer for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 offers 16-bit and split 8-bit timer functionality with auto-reload. Additionally, Timer 2 offers the ability to be clocked from the external oscillator while the device is in Suspend mode, and can be used as a wake-up source. This allows for implementation of a very low-power system, including RTC capability.

| Timer 0 and Timer 1 Modes                  | Timer 2 Modes                     |  |  |

|--------------------------------------------|-----------------------------------|--|--|

| 13-bit counter/timer                       | 16-bit timer with auto-reload     |  |  |

| 16-bit counter/timer                       | 16-bit timer with auto-reioad     |  |  |

| 8-bit counter/timer with auto-reload       | Two 9 hit timore with outo relead |  |  |

| Two 8-bit counter/timers<br>(Timer 0 only) | Two 8-bit timers with auto-reload |  |  |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 28.1 for pre-scaled clock selection).

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

## SFR Definition 28.4. TL0: Timer 0 Low Byte

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---|---|---|---|---|---|---|

| Name  | TL0[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W      |   |   |   |   |   |   |   |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### SFR Address = 0x8A

| Bit | Name     | Function                                                |  |  |  |

|-----|----------|---------------------------------------------------------|--|--|--|

| 7:0 | TL0[7:0] | Timer 0 Low Byte.                                       |  |  |  |

|     |          | The TL0 register is the low byte of the 16-bit Timer 0. |  |  |  |

## SFR Definition 28.5. TL1: Timer 1 Low Byte

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---|---|---|---|---|---|---|

| Name  | TL1[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W      |   |   |   |   |   |   |   |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## SFR Address = 0x8B

| Bit | Name     | Function                                                |  |  |

|-----|----------|---------------------------------------------------------|--|--|

| 7:0 | TL1[7:0] | Fimer 1 Low Byte.                                       |  |  |

|     |          | The TL1 register is the low byte of the 16-bit Timer 1. |  |  |

## SFR Definition 28.9. TMR2RLL: Timer 2 Reload Register Low Byte

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | TMR2RLL[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### SFR Address = 0xCA

| Bit | Name         | Function                                                    |  |  |  |

|-----|--------------|-------------------------------------------------------------|--|--|--|

| 7:0 | TMR2RLL[7:0] | Timer 2 Reload Register Low Byte.                           |  |  |  |

|     |              | TMR2RLL holds the low byte of the reload value for Timer 2. |  |  |  |

## SFR Definition 28.10. TMR2RLH: Timer 2 Reload Register High Byte

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | TMR2RLH[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### SFR Address = 0xCB

| Bit | Name         | Function                                                     |  |  |

|-----|--------------|--------------------------------------------------------------|--|--|

| 7:0 | TMR2RLH[7:0] | Timer 2 Reload Register High Byte.                           |  |  |

|     |              | TMR2RLH holds the high byte of the reload value for Timer 2. |  |  |

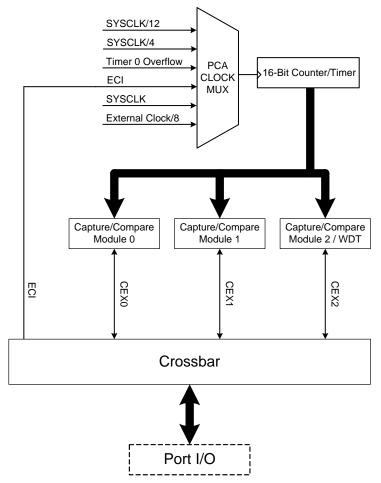

## 29. programmable Counter Array

The programmable counter array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled. The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 15-Bit PWM, or 16-Bit PWM (each mode is described in Section "29.3. Capture/Compare Modules" on page 228). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 29.1

**Important Note:** The PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. **Access to certain PCA registers is restricted while WDT mode is enabled**. See Section 29.4 for details.

Figure 29.1. PCA Block Diagram

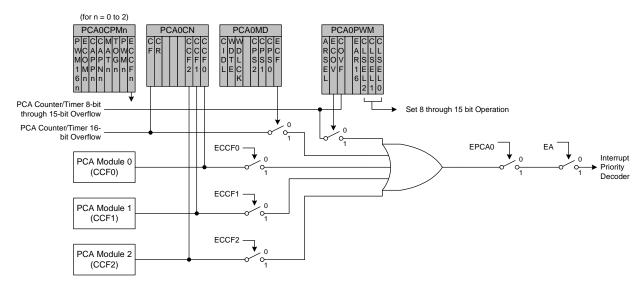

### 29.2. PCA0 Interrupt Sources

Figure 29.3 shows a diagram of the PCA interrupt tree. There are five independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th through 15th bit of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, and CCF2), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit in the IE register and the EPCA0 bit in the EIE1 register to logic 1.

Figure 29.3. PCA Interrupt Block Diagram