# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f826-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 21.2. RSTSRC: Reset Source                        | . 128 |

|------------------------------------------------------------------|-------|

| SFR Definition 22.1. CLKSEL: Clock Select                        | . 130 |

| SFR Definition 22.2. OSCICL: Internal H-F Oscillator Calibration | . 131 |

| SFR Definition 22.3. OSCICN: Internal H-F Oscillator Control     | . 132 |

| SFR Definition 22.4. OSCXCN: External Oscillator Control         | . 134 |

| SFR Definition 23.1. XBR0: Port I/O Crossbar Register 0          | . 148 |

| SFR Definition 23.2. XBR1: Port I/O Crossbar Register 1          | . 149 |

| SFR Definition 23.3. P0MASK: Port 0 Mask Register                | . 151 |

| SFR Definition 23.4. P0MAT: Port 0 Match Register                | . 151 |

| SFR Definition 23.5. P1MASK: Port 1 Mask Register                | . 152 |

| SFR Definition 23.6. P1MAT: Port 1 Match Register                |       |

| SFR Definition 23.7. P0: Port 0                                  | . 153 |

| SFR Definition 23.8. P0MDIN: Port 0 Input Mode                   | . 154 |

| SFR Definition 23.9. P0MDOUT: Port 0 Output Mode                 | . 154 |

| SFR Definition 23.10. P0SKIP: Port 0 Skip                        | . 155 |

| SFR Definition 23.11. P1: Port 1                                 |       |

| SFR Definition 23.12. P1MDIN: Port 1 Input Mode                  | . 156 |

| SFR Definition 23.13. P1MDOUT: Port 1 Output Mode                | . 156 |

| SFR Definition 23.14. P1SKIP: Port 1 Skip                        | . 157 |

| SFR Definition 23.15. P2: Port 2                                 |       |

| SFR Definition 23.16. P2MDOUT: Port 2 Output Mode                | . 158 |

| SFR Definition 24.1. CRC0CN: CRC0 Control                        |       |

| SFR Definition 24.2. CRC0IN: CRC Data Input                      | . 164 |

| SFR Definition 24.3. CRC0DATA: CRC Data Output                   | . 164 |

| SFR Definition 24.4. CRC0AUTO: CRC Automatic Control             | . 165 |

| SFR Definition 24.5. CRC0CNT: CRC Automatic Flash Sector Count   | . 165 |

| SFR Definition 24.6. CRC0FLIP: CRC Bit Flip                      | . 166 |

| SFR Definition 25.1. SPI0CFG: SPI0 Configuration                 |       |

| SFR Definition 25.2. SPI0CN: SPI0 Control                        |       |

| SFR Definition 25.3. SPI0CKR: SPI0 Clock Rate                    | . 176 |

| SFR Definition 25.4. SPI0DAT: SPI0 Data                          | . 176 |

| SFR Definition 26.1. SMB0CF: SMBus Clock/Configuration           | . 186 |

| SFR Definition 26.2. SMB0CN: SMBus Control                       |       |

| SFR Definition 26.3. SMB0ADR: SMBus Slave Address                | . 191 |

| SFR Definition 26.4. SMB0ADM: SMBus Slave Address Mask           | . 191 |

| SFR Definition 26.5. SMB0DAT: SMBus Data                         | . 192 |

| SFR Definition 27.1. SCON0: Serial Port 0 Control                | . 206 |

| SFR Definition 27.2. SBUF0: Serial (UART0) Port Data Buffer      | . 207 |

| SFR Definition 28.1. CKCON: Clock Control                        |       |

| SFR Definition 28.2. TCON: Timer Control                         | . 215 |

| SFR Definition 28.3. TMOD: Timer Mode                            | . 216 |

| SFR Definition 28.4. TL0: Timer 0 Low Byte                       |       |

| SFR Definition 28.5. TL1: Timer 1 Low Byte                       |       |

| SFR Definition 28.6. TH0: Timer 0 High Byte                      |       |

| SFR Definition 28.7. TH1: Timer 1 High Byte                      |       |

| <b>č</b> ,                                                       |       |

## 6. SOIC-16 Package Specifications

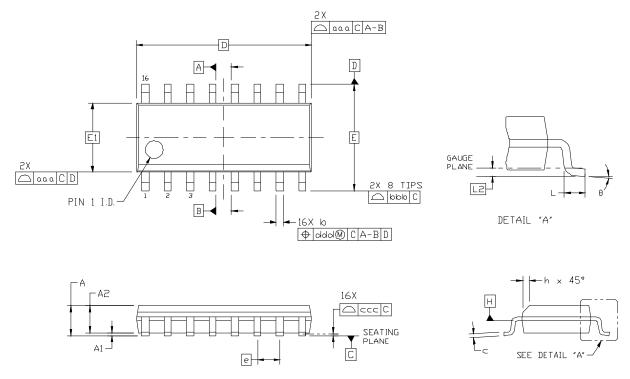

Figure 6.1. SOIC-16 Package Drawing

| Dimension | Min      | Nom      | Max  | Dimension | Min  | Nom      | Ма  |

|-----------|----------|----------|------|-----------|------|----------|-----|

| A         | _        |          | 1.75 | L         | 0.40 |          | 1.2 |

| A1        | 0.10     |          | 0.25 | L2        |      | 0.25 BSC |     |

| A2        | 1.25     |          | _    | h         | 0.25 |          | 0.5 |

| b         | 0.31     |          | 0.51 | θ         | 0°   |          | 80  |

| С         | 0.17     |          | 0.25 | aaa       |      | 0.10     |     |

| D         |          | 9.90 BSC |      | bbb       |      | 0.20     |     |

| E         | 6.00 BSC |          |      | CCC       |      | 0.10     |     |

| E1        |          | 3.90 BSC |      | ddd       |      | 0.25     |     |

| е         |          | 1.27 BSC |      | <b>L</b>  |      |          |     |

#### Table 6.1. SOIC-16 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MS-012, Variation AC.

Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 7. Electrical Characteristics

#### 7.1. Absolute Maximum Specifications

#### Table 7.1. Absolute Maximum Ratings

| Parameter                                                           | Conditions | Min  | Тур | Max                                                                                                                                                                                                                         | Units |  |  |  |  |  |  |

|---------------------------------------------------------------------|------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|

| Ambient temperature under bias                                      |            | -55  |     | 125                                                                                                                                                                                                                         | °C    |  |  |  |  |  |  |

| Storage Temperature                                                 |            | -65  | _   | 150                                                                                                                                                                                                                         | °C    |  |  |  |  |  |  |

| Voltage on $\overline{RST}$ or any Port I/O Pin with respect to GND |            | -0.3 | _   | 5.8                                                                                                                                                                                                                         | V     |  |  |  |  |  |  |

| Voltage on V <sub>DD</sub> with respect to GND                      |            | -0.3 |     | 4.2                                                                                                                                                                                                                         | V     |  |  |  |  |  |  |

| Maximum Total current through V <sub>DD</sub><br>and GND            |            |      | _   | 500                                                                                                                                                                                                                         | mA    |  |  |  |  |  |  |

| Maximum output current sunk by RST or any Port pin                  |            | —    | _   | 100                                                                                                                                                                                                                         | mA    |  |  |  |  |  |  |

|                                                                     | <b>.</b> . |      |     | Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.<br>This is a stress rating only and functional operation of the devices at those or any other conditions above |       |  |  |  |  |  |  |

This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### Table 7.13. Comparator Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise noted.

| Parameter                                         | Conditions              | Min   | Тур  | Max                    | Units |

|---------------------------------------------------|-------------------------|-------|------|------------------------|-------|

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 220  | —                      | ns    |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | —     | 225  | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 340  | —                      | ns    |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CP0+-CP0-=-100  mV      | —     | 380  | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 510  | —                      | ns    |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | —     | 945  | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | —     | 1500 | —                      | ns    |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100  mV  | —     | 5000 | —                      | ns    |

| Common-Mode Rejection Ratio                       |                         | —     | 1    | 4                      | mV/V  |

| Positive Hysteresis 1                             | Mode 2, CP0HYP1–0 = 00b | —     | 0    | 1                      | mV    |

| Positive Hysteresis 2                             | Mode 2, CP0HYP1–0 = 01b | 2     | 5    | 10                     | mV    |

| Positive Hysteresis 3                             | Mode 2, CP0HYP1–0 = 10b | 7     | 10   | 20                     | mV    |

| Positive Hysteresis 4                             | Mode 2, CP0HYP1–0 = 11b | 10    | 20   | 30                     | mV    |

| Negative Hysteresis 1                             | Mode 2, CP0HYN1–0 = 00b | —     | 0    | 1                      | mV    |

| Negative Hysteresis 2                             | Mode 2, CP0HYN1–0 = 01b | 2     | 5    | 10                     | mV    |

| Negative Hysteresis 3                             | Mode 2, CP0HYN1–0 = 10b | 7     | 10   | 20                     | mV    |

| Negative Hysteresis 4                             | Mode 2, CP0HYN1–0 = 11b | 10    | 20   | 30                     | mV    |

| Inverting or Non-Inverting Input<br>Voltage Range |                         | -0.25 | _    | V <sub>DD</sub> + 0.25 | V     |

| Input Offset Voltage                              |                         | -7.5  |      | 7.5                    | mV    |

| Power Specifications                              | •                       |       |      |                        |       |

| Power Supply Rejection                            |                         |       | 0.1  | —                      | mV/V  |

| Powerup Time                                      |                         | —     | 10   | —                      | μs    |

| Supply Current at DC                              | Mode 0                  | —     | 20   | —                      | μA    |

|                                                   | Mode 1                  | —     | 8    | —                      | μA    |

|                                                   | Mode 2                  | —     | 3    | —                      | μA    |

|                                                   | Mode 3                  | —     | 0.5  | —                      | μA    |

| Note: Vcm is the common-mode vo                   | Itage on CP0+ and CP0–. | ·     |      |                        |       |

#### 8.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 8.5. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit                | 7   | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|-----|-----------------|---|---|---|---|---|---|

| Name               |     | ADC0GTH[7:0]    |   |   |   |   |   |   |

| Туре               | R/W |                 |   |   |   |   |   |   |

| Reset              | 1   | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |

| SFR Address = 0xC4 |     |                 |   |   |   |   |   |   |

| Bit | Name         | Function                                     |

|-----|--------------|----------------------------------------------|

| 7:0 | ADC0GTH[7:0] | ADC0 Greater-Than Data Word High-Order Bits. |

#### SFR Definition 8.6. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit   | 7                  | 6                                              | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------------|------------------------------------------------|----------|---|---|---|---|---|--|--|

| Nam   | e                  | ADC0GTL[7:0]                                   |          |   |   |   |   |   |  |  |

| Туре  | 9                  | R/W                                            |          |   |   |   |   |   |  |  |

| Rese  | et 1               | 1                                              | 1        | 1 | 1 | 1 | 1 | 1 |  |  |

| SFR A | SFR Address = 0xC3 |                                                |          |   |   |   |   |   |  |  |

| Bit   | Name               |                                                | Function |   |   |   |   |   |  |  |

| 7:0   | ADC0GTL[7:0]       | 0] ADC0 Greater-Than Data Word Low-Order Bits. |          |   |   |   |   |   |  |  |

#### SFR Definition 13.2. CS0CF: Capacitive Sense Configuration

| Bit   | 7 | 6   | 5          | 4   | 3 | 2   | 1          | 0   |

|-------|---|-----|------------|-----|---|-----|------------|-----|

| Name  |   |     | CS0CM[2:0] |     |   | (   | CS0ACU[2:0 | ]   |

| Туре  | R | R/W | R/W        | R/W | R | R/W | R/W        | R/W |

| Reset | 0 | 0   | 0          | 0   | 0 | 0   | 0          | 0   |

SFR Address = 0x9E

| Bit | Name                                            | Description                                                                            |  |  |  |  |

|-----|-------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| 7   | Unused                                          | Read = 0b; Write = Don't care                                                          |  |  |  |  |

| 6:4 | CS0CM[2:0] CS0 Start of Conversion Mode Select. |                                                                                        |  |  |  |  |

|     |                                                 | 000: Conversion initiated on every write of 1 to CS0BUSY.                              |  |  |  |  |

|     |                                                 | 001: Conversion initiated on overflow of Timer 0.                                      |  |  |  |  |

|     |                                                 | 010: Conversion initiated on overflow of Timer 2.                                      |  |  |  |  |

|     |                                                 | 011: Conversion initiated on overflow of Timer 1.                                      |  |  |  |  |

|     |                                                 | 100: Reserved.                                                                         |  |  |  |  |

|     |                                                 | 101: Reserved.                                                                         |  |  |  |  |

|     |                                                 | 110: Conversion initiated continuously after writing 1 to CS0BUSY.                     |  |  |  |  |

|     |                                                 | 111: Auto-scan enabled, conversions initiated continuously after writing 1 to CS0BUSY. |  |  |  |  |

| 3   | Unused                                          | Read = 0b; Write = Don't care                                                          |  |  |  |  |

| 2:0 | CS0ACU[2:0]                                     | CS0 Accumulator Mode Select.                                                           |  |  |  |  |

|     |                                                 | 000: Accumulate 1 sample.                                                              |  |  |  |  |

|     |                                                 | 001: Accumulate 4 samples.                                                             |  |  |  |  |

|     |                                                 | 010: Accumulate 8 samples.                                                             |  |  |  |  |

|     |                                                 | 011: Accumulate 16 samples                                                             |  |  |  |  |

|     |                                                 | 100: Accumulate 32 samples.                                                            |  |  |  |  |

|     |                                                 | 101: Accumulate 64 samples.                                                            |  |  |  |  |

|     |                                                 | 11x: Reserved.                                                                         |  |  |  |  |

#### SFR Definition 13.3. CS0DH: Capacitive Sense Data High Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|------------|---|---|---|---|---|---|--|

| Name  |   | CS0DH[7:0] |   |   |   |   |   |   |  |

| Туре  | R | R          | R | R | R | R | R | R |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xAC

| Bit | Name  | Description                                                                    |

|-----|-------|--------------------------------------------------------------------------------|

| 7:0 | CS0DH | CS0 Data High Byte.                                                            |

|     |       | Stores the high byte of the last completed 16-bit Capacitive Sense conversion. |

#### SFR Definition 13.4. CS0DL: Capacitive Sense Data Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | CS0DL[7:0] |   |   |   |   |   |   |   |

| Туре  | R          | R | R | R | R | R | R | R |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xAB

| Bit | Name  | Description                                                                   |  |  |  |

|-----|-------|-------------------------------------------------------------------------------|--|--|--|

| 7:0 | CS0DL | CS0 Data Low Byte.                                                            |  |  |  |

|     |       | Stores the low byte of the last completed 16-bit Capacitive Sense conversion. |  |  |  |

# C8051F80x-83x

#### SFR Definition 14.3. SP: Stack Pointer

| Bit   | 7                  | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------------|--------------|---|---|---|---|---|---|--|

| Nam   | e                  | SP[7:0]      |   |   |   |   |   |   |  |

| Туре  | •                  | R/W          |   |   |   |   |   |   |  |

| Rese  | <b>t</b> 0         | 0            | 0 | 0 | 0 | 1 | 1 | 1 |  |

| SFR A | SFR Address = 0x81 |              |   |   |   |   |   |   |  |

| Bit   | Name               | Function     |   |   |   |   |   |   |  |

| 7:0   | SP[7:0]            | Stack Pointe | r |   |   |   |   |   |  |

The Stack Pointer holds the location of the top of the stack. The stack pointer is incremented before every PUSH operation. The SP register defaults to 0x07 after reset.

#### SFR Definition 14.4. ACC: Accumulator

| Bit                                 | 7    | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------------------------|------|----------|---|---|---|---|---|---|

| Name                                | e    | ACC[7:0] |   |   |   |   |   |   |

| Туре                                | •    | R/W      |   |   |   |   |   |   |

| Rese                                | t 0  | 0        | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0xE0; Bit-Addressable |      |          |   |   |   |   |   |   |

| Bit                                 | Name | Function |   |   |   |   |   |   |

| BIt | Name     | Function                                                    |  |

|-----|----------|-------------------------------------------------------------|--|

| 7:0 | ACC[7:0] | Accumulator.                                                |  |

|     |          | This register is the accumulator for arithmetic operations. |  |

#### SFR Definition 18.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7        | 6        | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|----------|----------|------|-------|-------|--------|------|-------|

| Name  | Reserved | Reserved | ECP0 | EADC0 | EPCA0 | EWADC0 | EMAT | ESMB0 |

| Туре  | W        | W        | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0        | 0        | 0    | 0     | 0     | 0      | 0    | 0     |

SFR Address = 0xE6

| Bit | Name     | Function                                                                                                                                                                                                                                                                          |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved | Must write 0.                                                                                                                                                                                                                                                                     |

| 6   | Reserved | Reserved.                                                                                                                                                                                                                                                                         |

|     |          | Must write 0.                                                                                                                                                                                                                                                                     |

| 5   | ECP0     | <ul> <li>Enable Comparator0 (CP0) Interrupt.</li> <li>This bit sets the masking of the CP0 rising edge or falling edge interrupt.</li> <li>0: Disable CP0 interrupts.</li> <li>1: Enable interrupt requests generated by the CP0RIF and CP0FIF flags.</li> </ul>                  |

| 4   | EADC0    | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 3   | EPCA0    | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 2   | EWADC0   | <ul> <li>Enable Window Comparison ADC0 interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 1   | EMAT     | Enable Port Match Interrupts.<br>This bit sets the masking of the Port Match event interrupt.<br>0: Disable all Port Match interrupts.<br>1: Enable interrupt requests generated by a Port Match.                                                                                 |

| 0   | ESMB0    | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

#### 18.3. INTO and INT1 External Interrupts

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "28.1. Timer 0 and Timer 1" on page 211) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 18.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see Section "23.3. Priority Crossbar Decoder" on page 143 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

#### 21.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

#### 21.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "29.4. Watchdog Timer Mode" on page 236; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to '1'. The state of the RST pin is unaffected by this reset.

#### 21.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above address 0x3DFF.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above address 0x3DFF.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0x3DFF.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "19.3. Security Options" on page 114).

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 21.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

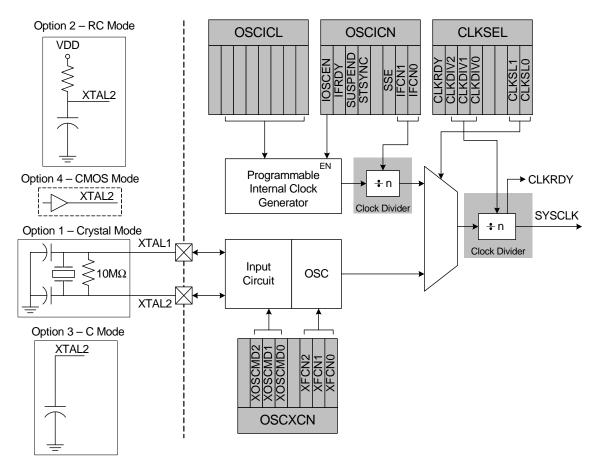

#### 22. Oscillators and Clock Selection

C8051F80x-83x devices include a programmable internal high-frequency oscillator and an external oscillator drive circuit. The internal high-frequency oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 22.1. The system clock can be sourced by the external oscillator circuit or the internal oscillator (default). The internal oscillator offers a selectable post-scaling feature, which is initially set to divide the clock by 8.

Figure 22.1. Oscillator Options

#### 22.1. System Clock Selection

The system clock source for the MCU can be selected using the CLKSEL register. The clock selected as the system clock can be divided by 1, 2, 4, 8, 16, 32, 64, or 128. When switching between two clock divide values, the transition may take up to 128 cycles of the undivided clock source. The CLKRDY flag can be polled to determine when the new clock divide value has been applied. The clock divider must be set to "divide by 1" when entering Suspend mode. The system clock source may also be switched on-the-fly. The switchover takes effect after one clock period of the slower oscillator.

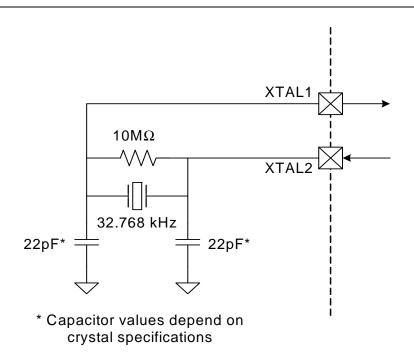

#### Figure 22.2. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram

#### 22.3.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 22.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation 22.1, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in k $\Omega$ .

#### Equation 22.1. RC Mode Oscillator Frequency

$f = 1.23 \times 10^3 / (R \times C)$

Rev. 1.0

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$f = 1.23(10^3) / RC = 1.23(10^3) / [246 \times 50] = 0.1 MHz = 100 kHz$

Referring to the table in SFR Definition 22.4, the required XFCN setting is 010b.

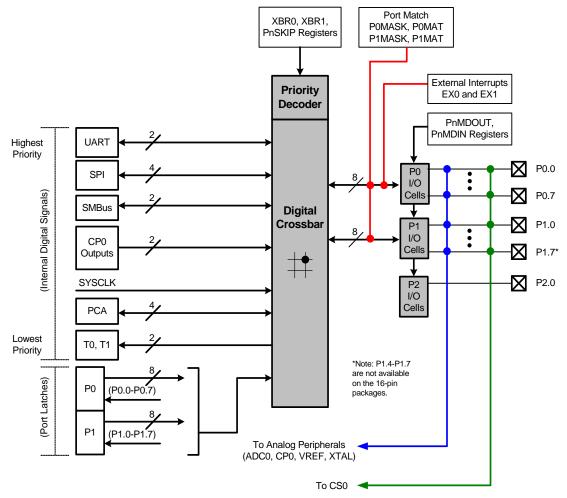

## 23. Port Input/Output

Digital and analog resources are available through 17 I/O pins (24-pin and 20-pin packages) or 13 I/O pins (16-pin packages). Port pins P0.0–P1.7 can be defined as general-purpose I/O (GPIO) or assigned to one of the internal digital resources as shown in Figure 23.4. Port pin P2.0 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 23.5). The registers XBR0 and XBR1, defined in SFR Definition 23.1 and SFR Definition 23.2, are used to select internal digital functions.

All Port I/Os are 5 V tolerant (refer to Figure 23.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Section "7. Electrical Characteristics" on page 39.

Figure 23.1. Port I/O Functional Block Diagram

#### SFR Definition 25.1. SPI0CFG: SPI0 Configuration

| Bit   | 7      | 6     | 5     | 4     | 3      | 2     | 1    | 0     |

|-------|--------|-------|-------|-------|--------|-------|------|-------|

| Name  | SPIBSY | MSTEN | СКРНА | CKPOL | SLVSEL | NSSIN | SRMT | RXBMT |

| Туре  | R      | R/W   | R/W   | R/W   | R      | R     | R    | R     |

| Reset | 0      | 0     | 0     | 0     | 0      | 1     | 1    | 1     |

SFR Address = 0xA1

| Bit   | Name           | Function                                                                                                     |  |  |  |  |

|-------|----------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7     | SPIBSY         | SPI Busy.                                                                                                    |  |  |  |  |

|       |                | This bit is set to logic 1 when a SPI transfer is in progress (master or slave mode).                        |  |  |  |  |

| 6     | MSTEN          | Master Mode Enable.                                                                                          |  |  |  |  |

|       |                | 0: Disable master mode. Operate in slave mode.                                                               |  |  |  |  |

|       |                | 1: Enable master mode. Operate as a master.                                                                  |  |  |  |  |

| 5     | CKPHA          | SPI0 Clock Phase.                                                                                            |  |  |  |  |

|       |                | 0: Data centered on first edge of SCK period.*                                                               |  |  |  |  |

|       |                | 1: Data centered on second edge of SCK period.*                                                              |  |  |  |  |

| 4     | CKPOL          | SPI0 Clock Polarity.                                                                                         |  |  |  |  |

|       |                | 0: SCK line low in idle state.                                                                               |  |  |  |  |

|       |                | 1: SCK line high in idle state.                                                                              |  |  |  |  |

| 3     | SLVSEL         | Slave Selected Flag.                                                                                         |  |  |  |  |

|       |                | This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected                       |  |  |  |  |

|       |                | slave. It is cleared to logic 0 when NSS is high (slave not selected). This bit does                         |  |  |  |  |

|       |                | not indicate the instantaneous value at the NSS pin, but rather a de-glitched ver-<br>sion of the pin input. |  |  |  |  |

| 2     | NSSIN          | NSS Instantaneous Pin Input.                                                                                 |  |  |  |  |

|       |                | This bit mimics the instantaneous value that is present on the NSS port pin at the                           |  |  |  |  |

|       |                | time that the register is read. This input is not de-glitched.                                               |  |  |  |  |

| 1     | SRMT           | Shift Register Empty (valid in slave mode only).                                                             |  |  |  |  |

|       |                | This bit will be set to logic 1 when all data has been transferred in/out of the shift                       |  |  |  |  |

|       |                | register, and there is no new information available to read from the transmit buffer                         |  |  |  |  |

|       |                | or write to the receive buffer. It returns to logic 0 when a data byte is transferred to                     |  |  |  |  |

|       |                | the shift register from the transmit buffer or by a transition on SCK. SRMT = 1 when in Master Mode.         |  |  |  |  |

| 0     | RXBMT          | Receive Buffer Empty (valid in slave mode only).                                                             |  |  |  |  |

|       |                | This bit will be set to logic 1 when the receive buffer has been read and contains no                        |  |  |  |  |

|       |                | new information. If there is new information available in the receive buffer that has                        |  |  |  |  |

|       |                | not been read, this bit will return to logic 0. RXBMT = 1 when in Master Mode.                               |  |  |  |  |

| Note: | In slave mode, | data on MOSI is sampled in the center of each data bit. In master mode, data on MISO is                      |  |  |  |  |

|       |                | YSCLK before the end of each data bit, to provide maximum settling time for the slave device.                |  |  |  |  |

|       | See Table 25.1 | for timing parameters.                                                                                       |  |  |  |  |

imum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                 | Minimum SDA Setup Time                                                                                                                                                                                                                                                                                                 | Minimum SDA Hold Time |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| 0                       | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay <sup>*</sup>                                                                                                                                                                                                                                    | 3 system clocks       |  |  |  |  |

| 1                       | 11 system clocks                                                                                                                                                                                                                                                                                                       | 12 system clocks      |  |  |  |  |

| software a<br>ACK is wi | <b>Note:</b> Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                       |  |  |  |  |

Table 26.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "26.3.4. SCL Low Timeout" on page 182). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 26.4).

#### SFR Definition 26.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1    | 0       |

|-------|-------|-----|------|---------|--------|--------|------|---------|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBC | :S[1:0] |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/W  |         |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0    | 0       |

SFR Address = 0xC1

| ENSMB      | <b>SMBus Enable.</b><br>This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INH        | constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                                                                                                                             |

| INH        |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |

| BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |

| EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |

|            | This bit controls the SDA setup and hold times according to Table 26.2.<br>0: SDA Extended Setup and Hold Times disabled.<br>1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                            |

| SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |

| SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | These two bits select the SMBus clock source, which is used to generate the SMBus<br>bit rate. The selected device should be configured according to Equation 26.1.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow                                                                                                                                                |

|            | EXTHOLD<br>SMBTOE<br>SMBFTE                                                                                                                                                                                                                                                                                                                                                                                                           |

#### SFR Definition 28.4. TL0: Timer 0 Low Byte

| Bit   | 7            | 6                                                                            | 5                 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|------------------------------------------------------------------------------|-------------------|---|---|---|---|---|

| Name  | • TL0[7:0]   |                                                                              |                   |   |   |   |   |   |

| Туре  | •            | R/W                                                                          |                   |   |   |   |   |   |

| Rese  | t 0          | 0                                                                            | 0                 | 0 | 0 | 0 | 0 | 0 |

| SFR A | ddress = 0x8 | A                                                                            |                   |   |   |   |   |   |

| Bit   | Name         | Function                                                                     |                   |   |   |   |   |   |

| 7:0   | TL0[7:0]     | Timer 0 Lov                                                                  | Timer 0 Low Byte. |   |   |   |   |   |

|       |              | Timer 0 Low Byte.<br>The TL0 register is the low byte of the 16-bit Timer 0. |                   |   |   |   |   |   |

#### SFR Definition 28.5. TL1: Timer 1 Low Byte

| Bit   | 7                  | 6              | 5     | 4   | 3        | 2 | 1 | 0        |  |  |

|-------|--------------------|----------------|-------|-----|----------|---|---|----------|--|--|

| Name  | 9                  |                |       | TL1 | [7:0]    |   |   | <u>I</u> |  |  |

| Туре  |                    | R/W            |       |     |          |   |   |          |  |  |

| Rese  | t 0                | 0              | 0     | 0   | 0        | 0 | 0 | 0        |  |  |

| SFR A | SFR Address = 0x8B |                |       |     |          |   |   |          |  |  |

| Bit   | Name               |                |       |     | Function |   |   | -        |  |  |

| 7.0   | TL 4[7.0]          | Time or 4 1 or | Durta |     |          |   |   | -        |  |  |

| 7:0 | TL1[7:0] | Timer 1 Low Byte.                                       |

|-----|----------|---------------------------------------------------------|

|     |          | The TL1 register is the low byte of the 16-bit Timer 1. |

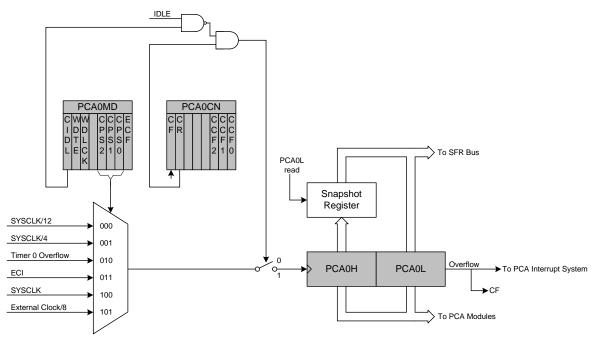

#### 29.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2–CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 29.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2      | CPS1                                                                                 | CPS0 | Timebase                                                              |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------|--|--|--|--|--|

| 0         | 0                                                                                    | 0    | System clock divided by 12                                            |  |  |  |  |  |

| 0         | 0                                                                                    | 1    | System clock divided by 4                                             |  |  |  |  |  |

| 0         | 1                                                                                    | 0    | Timer 0 overflow                                                      |  |  |  |  |  |

| 0         | 1                                                                                    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |  |  |  |  |  |

| 1         | 0                                                                                    | 0    | System clock                                                          |  |  |  |  |  |

| 1         | 0                                                                                    | 1    | External oscillator source divided by 8 (Note)                        |  |  |  |  |  |

| 1         | 1                                                                                    | Х    | Reserved                                                              |  |  |  |  |  |

| Note: Ext | Note: External oscillator source divided by 8 is synchronized with the system clock. |      |                                                                       |  |  |  |  |  |

Table 29.1. PCA Timebase Input Options

#### SFR Definition 29.7. PCA0CPLn: PCA0 Capture Module Low Byte

| Bit   | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0CPn[7:0] |     |     |     |     |     |     |     |

| Туре  | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Addresses: PCA0CPL0 = 0xFB, PCA0CPL1 = 0xE9, PCA0CPL2 = 0xEB

| Bit   | Name                                                                     | Function                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0   | PCA0CPn[7:0]                                                             | PCA Capture Module Low Byte.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|       |                                                                          | The PCA0CPLn register holds the low byte (LSB) of the 16-bit capture module n.<br>This register address also allows access to the low byte of the corresponding<br>PCA channel's auto-reload value for 9-bit through 15-bit PWM mode and 16-bit<br>PWM mode. The ARSEL bit in register PCA0PWM controls which register is<br>accessed. |  |  |  |  |  |  |

| Note: | Note: A write to this register will clear the module's ECOMn bit to a 0. |                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

#### SFR Definition 29.8. PCA0CPHn: PCA0 Capture Module High Byte

| Bit   | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0CPn[15:8] |     |     |     |     |     |     |     |

| Туре  | R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0             | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Addresses: PCA0CPH0 = 0xFC, PCA0CPH1 = 0xEA, PCA0CPH2 = 0xEC

| Bit  | Name                  | Function                                                                                                                                                                                                                                                                                                                                 |

|------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | PCA0CPn[15:8]         | PCA Capture Module High Byte.                                                                                                                                                                                                                                                                                                            |

|      |                       | The PCA0CPHn register holds the high byte (MSB) of the 16-bit capture module n.<br>This register address also allows access to the high byte of the corresponding<br>PCA channel's auto-reload value for 9-bit through 15-bit PWM mode and 16-bit<br>PWM mode. The ARSEL bit in register PCA0PWM controls which register is<br>accessed. |

| Note | : A write to this reg | ister will set the module's ECOMn bit to a 1.                                                                                                                                                                                                                                                                                            |