Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Not For New Designs                                            |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, WDT                                       |

| Number of I/O              | 13                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 16-SOIC                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f827-gs |

# **List of Figures**

| 1. System Overview                                                    | 4.0 |

|-----------------------------------------------------------------------|-----|

| Figure 1.1. C8051F800, C8051F806, C8051F812, C8051F818 Block Diagram  |     |

| Figure 1.2. C8051F801, C8051F807, C8051F813, C8051F819 Block Diagram  |     |

| Figure 1.3. C8051F802, C8051F808, C8051F814, C8051F820 Block Diagram  |     |

| Figure 1.4. C8051F803, C8051F809, C8051F815, C8051F821 Block Diagram  |     |

| Figure 1.5. C8051F804, C8051F810, C8051F816, C8051F822 Block Diagram  |     |

| Figure 1.6. C8051F805, C8051F811, C8051F817, C8051F823 Block Diagram  |     |

| Figure 1.7. C8051F824, C8051F827, C8051F830, C8051F833 Block Diagram  |     |

| Figure 1.8. C8051F825, C8051F828, C8051F831, C8051F834 Block Diagram  |     |

| Figure 1.9. C8051F826, C8051F829, C8051F832, C8051F835 Block Diagram  | 24  |

| 2. Ordering Information                                               |     |

| 3. Pin Definitions                                                    |     |

| Figure 3.1. QFN-20 Pinout Diagram (Top View)                          |     |

| Figure 3.2. QSOP-24 Pinout Diagram (Top View)                         |     |

| Figure 3.3. SOIC-16 Pinout Diagram (Top View)                         | 32  |

| 4. QFN-20 Package Specifications                                      | 00  |

| Figure 4.1. QFN-20 Package Drawing                                    |     |

| Figure 4.2. QFN-20 Recommended PCB Land Pattern                       | 34  |

| 5. QSOP-24 Package Specifications                                     | 0.5 |

| Figure 5.1. QSOP-24 Package Drawing                                   |     |

| Figure 5.2. QSOP-24 PCB Land Pattern                                  | 36  |

| 6. SOIC-16 Package Specifications                                     | 0.7 |

| Figure 6.1. SOIC-16 Package Drawing                                   |     |

| Figure 6.2. SOIC-16 PCB Land Pattern                                  | 38  |

| 7. Electrical Characteristics                                         |     |

| 8. 10-Bit ADC (ADC0)                                                  | 40  |

| Figure 8.1. ADC0 Functional Block Diagram                             |     |

| Figure 8.2. 10-Bit ADC Track and Conversion Example Timing            |     |

| Figure 8.3. ADC0 Equivalent Input Circuits                            |     |

| Figure 8.4. ADC Window Compare Example: Right-Justified Data          |     |

| Figure 8.5. ADC Window Compare Example: Left-Justified Data           |     |

| Figure 8.6. ADC0 Multiplexer Block Diagram                            | 56  |

| 9. Temperature Sensor                                                 | ΕO  |

| Figure 9.1. Temperature Sensor Transfer Function                      |     |

| Figure 9.2. Temperature Sensor Error with 1-Point Calibration at 0 °C | 59  |

| 10. Voltage and Ground Reference Options                              | 00  |

| Figure 10.1. Voltage Reference Functional Block Diagram               | 60  |

| 11. Voltage Regulator (REG0)                                          |     |

| 12. Comparator0                                                       | 0.5 |

| Figure 12.1. Comparator United Block Diagram                          |     |

| Figure 12.2. Comparator Hysteresis Plot                               |     |

| Figure 12.3. Comparator Input Multiplexer Block Diagram               | 69  |

| 13. Capacitive Sense (CS0)                                            |     |

| SFR Definition 21.2. RSTSRC: Reset Source                        | 128 |

|------------------------------------------------------------------|-----|

| SFR Definition 22.1. CLKSEL: Clock Select                        | 130 |

| SFR Definition 22.2. OSCICL: Internal H-F Oscillator Calibration | 131 |

| SFR Definition 22.3. OSCICN: Internal H-F Oscillator Control     | 132 |

| SFR Definition 22.4. OSCXCN: External Oscillator Control         | 134 |

| SFR Definition 23.1. XBR0: Port I/O Crossbar Register 0          |     |

| SFR Definition 23.2. XBR1: Port I/O Crossbar Register 1          | 149 |

| SFR Definition 23.3. P0MASK: Port 0 Mask Register                |     |

| SFR Definition 23.4. P0MAT: Port 0 Match Register                | 151 |

| SFR Definition 23.5. P1MASK: Port 1 Mask Register                |     |

| SFR Definition 23.6. P1MAT: Port 1 Match Register                | 152 |

| SFR Definition 23.7. P0: Port 0                                  |     |

| SFR Definition 23.8. P0MDIN: Port 0 Input Mode                   | 154 |

| SFR Definition 23.9. P0MDOUT: Port 0 Output Mode                 | 154 |

| SFR Definition 23.10. P0SKIP: Port 0 Skip                        | 155 |

| SFR Definition 23.11. P1: Port 1                                 |     |

| SFR Definition 23.12. P1MDIN: Port 1 Input Mode                  | 156 |

| SFR Definition 23.13. P1MDOUT: Port 1 Output Mode                |     |

| SFR Definition 23.14. P1SKIP: Port 1 Skip                        | 157 |

| SFR Definition 23.15. P2: Port 2                                 | 157 |

| SFR Definition 23.16. P2MDOUT: Port 2 Output Mode                | 158 |

| SFR Definition 24.1. CRC0CN: CRC0 Control                        | 163 |

| SFR Definition 24.2. CRC0IN: CRC Data Input                      | 164 |

| SFR Definition 24.3. CRC0DATA: CRC Data Output                   | 164 |

| SFR Definition 24.4. CRC0AUTO: CRC Automatic Control             |     |

| SFR Definition 24.5. CRC0CNT: CRC Automatic Flash Sector Count   | 165 |

| SFR Definition 24.6. CRC0FLIP: CRC Bit Flip                      | 166 |

| SFR Definition 25.1. SPI0CFG: SPI0 Configuration                 | 174 |

| SFR Definition 25.2. SPI0CN: SPI0 Control                        | 175 |

| SFR Definition 25.3. SPI0CKR: SPI0 Clock Rate                    | 176 |

| SFR Definition 25.4. SPI0DAT: SPI0 Data                          |     |

| SFR Definition 26.1. SMB0CF: SMBus Clock/Configuration           | 186 |

| SFR Definition 26.2. SMB0CN: SMBus Control                       |     |

| SFR Definition 26.3. SMB0ADR: SMBus Slave Address                |     |

| SFR Definition 26.4. SMB0ADM: SMBus Slave Address Mask           | 191 |

| SFR Definition 26.5. SMB0DAT: SMBus Data                         |     |

| SFR Definition 27.1. SCON0: Serial Port 0 Control                |     |

| SFR Definition 27.2. SBUF0: Serial (UART0) Port Data Buffer      | 207 |

| SFR Definition 28.1. CKCON: Clock Control                        |     |

| SFR Definition 28.2. TCON: Timer Control                         | 215 |

| SFR Definition 28.3. TMOD: Timer Mode                            | 216 |

| SFR Definition 28.4. TL0: Timer 0 Low Byte                       |     |

| SFR Definition 28.5. TL1: Timer 1 Low Byte                       | 217 |

| SFR Definition 28.6. TH0: Timer 0 High Byte                      | 218 |

| SFR Definition 28.7. TH1: Timer 1 High Byte                      | 218 |

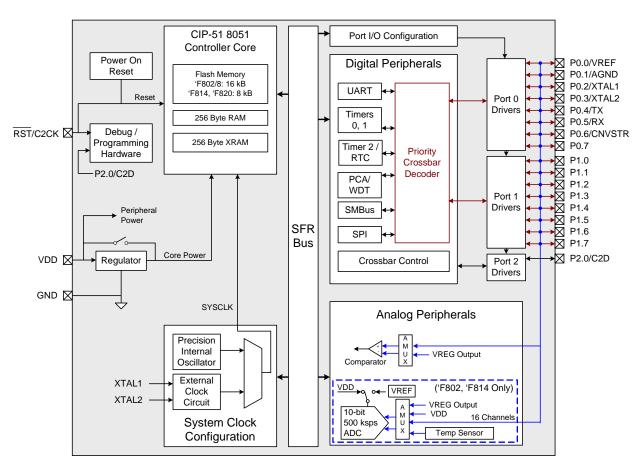

### 1. System Overview

C8051F80x-83x devices are fully integrated, mixed-signal, system-on-a-chip capacitive sensing MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Capacitive sense interface with 16 input channels

- 10-bit 500 ksps single-ended ADC with 16-channel analog multiplexer and integrated temperature sensor

- Precision calibrated 24.5 MHz internal oscillator

- 16 kb of on-chip Flash memory

- 512 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Three general-purpose 16-bit timers

- Programmable counter/timer array (PCA) with three capture/compare modules

- On-chip internal voltage reference

- · On-chip Watchdog timer

- · On-chip power-on reset and supply monitor

- On-chip voltage comparator

- 17 general purpose I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F80x-83x devices are truly stand-alone, system-on-a-chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The C8051F80x-83x processors include Silicon Laboratories' 2-Wire C2 Debug and Programming interface, which allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection of memory, viewing and modification of special function registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 1.8-3.6 V operation over the industrial temperature range (-45 to +85 °C). An internal LDO regulator is used to supply the processor core voltage at 1.8 V. The Port I/O and RST pins are tolerant of input signals up to 5 V. See Table 2.1 for ordering information. Block diagrams of the devices in the C8051F80x-83x family are shown in Figure 1.1 through Figure 1.9.

Figure 1.3. C8051F802, C8051F808, C8051F814, C8051F820 Block Diagram

### **Table 7.9. ADC0 Electrical Characteristics**

$V_{DD}$  = 3.0 V, VREF = 2.40 V (REFSL=0), -40 to +85 °C unless otherwise specified.

| Parameter                       | Conditions                    | Min     | Тур        | Max      | Units  |  |  |  |

|---------------------------------|-------------------------------|---------|------------|----------|--------|--|--|--|

| DC Accuracy                     |                               |         |            |          |        |  |  |  |

| Resolution                      |                               |         | 10         |          | bits   |  |  |  |

| Integral Nonlinearity           |                               | _       | ±0.5       | ±1       | LSB    |  |  |  |

| Differential Nonlinearity       | Guaranteed Monotonic          | _       | ±0.5       | ±1       | LSB    |  |  |  |

| Offset Error                    |                               | -2      | 0          | 2        | LSB    |  |  |  |

| Full Scale Error                |                               | -2      | 0          | 2        | LSB    |  |  |  |

| Offset Temperature Coefficient  |                               |         | 45         | _        | ppm/°C |  |  |  |

| Dynamic performance (10 kHz s   | sine-wave single-ended input, | dB belo | ow Full So | ale, 200 | ksps)  |  |  |  |

| Signal-to-Noise Plus Distortion |                               | 54      | 60         | _        | dB     |  |  |  |

| Total Harmonic Distortion       | Up to the 5th harmonic        | _       | 75         | _        | dB     |  |  |  |

| Spurious-Free Dynamic Range     |                               | _       | -90        | _        | dB     |  |  |  |

| Conversion Rate                 | _                             |         | •          |          |        |  |  |  |

| SAR Conversion Clock            |                               | _       | _          | 8.33     | MHz    |  |  |  |

| Conversion Time in SAR Clocks   | 10-bit Mode                   | 13      | _          | _        | clocks |  |  |  |

|                                 | 8-bit Mode                    | 11      | _          | _        | clocks |  |  |  |

| Track/Hold Acquisition Time     | V <sub>DD</sub> >= 2.0 V      | 300     | _          | _        | ns     |  |  |  |

|                                 | V <sub>DD</sub> < 2.0 V       | 2.0     | _          | _        | μs     |  |  |  |

| Throughput Rate                 |                               | _       | _          | 500      | ksps   |  |  |  |

| Analog Inputs                   |                               | •       |            |          |        |  |  |  |

| ADC Input Voltage Range         |                               | 0       | _          | VREF     | V      |  |  |  |

| Sampling Capacitance            | 1x Gain                       | _       | 5          | _        | pF     |  |  |  |

|                                 | 0.5x Gain                     |         | 3          | _        | pF     |  |  |  |

| Input Multiplexer Impedance     |                               | _       | 5          | _        | kΩ     |  |  |  |

| Power Specifications            |                               |         |            |          |        |  |  |  |

| Power Supply Current            | Operating Mode, 500 ksps      | _       | 630        | 1000     | μΑ     |  |  |  |

| Power Supply Rejection          |                               | _       | -70        | —        | dB     |  |  |  |

## SFR Definition 8.7. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|---|---|---|---|---|---|---|--|

| Name  | ADC0LTH[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

### SFR Address = 0xC6

| Bit | Name         | Function                                  |

|-----|--------------|-------------------------------------------|

| 7:0 | ADC0LTH[7:0] | ADC0 Less-Than Data Word High-Order Bits. |

### SFR Definition 8.8. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|---|---|---|---|---|---|---|--|

| Name  | ADC0LTL[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

### SFR Address = 0xC5

| Bit | Name         | Function                                 |

|-----|--------------|------------------------------------------|

| 7:0 | ADC0LTL[7:0] | ADC0 Less-Than Data Word Low-Order Bits. |

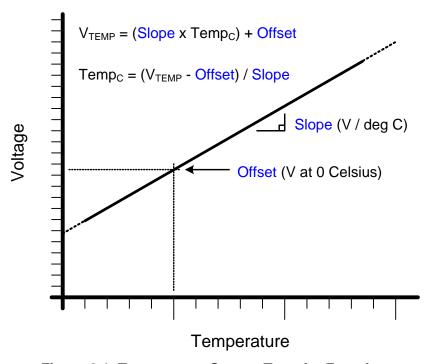

### 9. Temperature Sensor

An on-chip temperature sensor is included on the C8051F800/1/2/3/4/5, C8051F812/3/4/5/6/7, C8051F824/5/6, and C8051F830/1/2 which can be directly accessed via the ADC multiplexer in single-ended configuration. To use the ADC to measure the temperature sensor, the ADC mux channel should be configured to connect to the temperature sensor. The temperature sensor transfer function is shown in Figure 9.1. The output voltage (V<sub>TEMP</sub>) is the positive ADC input when the ADC multiplexer is set correctly. The TEMPE bit in register REF0CN enables/disables the temperature sensor, as described in SFR Definition 10.1. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 7.11 for the slope and offset parameters of the temperature sensor.

Figure 9.1. Temperature Sensor Transfer Function

#### 9.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 5.1 for linearity specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. Typically a 1-point (offset) calibration includes the following steps:

- 1. Control/measure the ambient temperature (this temperature must be known).

- 2. Power the device, and delay for a few seconds to allow for self-heating.

- 3. Perform an ADC conversion with the temperature sensor selected as the ADC's input.

- 4. Calculate the offset characteristics, and store this value in non-volatile memory for use with subsequent temperature sensor measurements.

Figure 5.3 shows the typical temperature sensor error assuming a 1-point calibration at 0 °C.

Parameters that affect ADC measurement, in particular the voltage reference value, will also affect temperature measurement.

### SFR Definition 10.1. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4   | 3   | 2     | 1     | 0 |

|-------|---|---|--------|-----|-----|-------|-------|---|

| Name  |   |   | REFGND | REI | FSL | TEMPE | BIASE |   |

| Туре  | R | R | R/W    | R/W | R/W | R/W   | R/W   | R |

| Reset | 0 | 0 | 0      | 1   | 0   | 0     | 0     | 0 |

### SFR Address = 0xD1

| Bit | Name   | Function                                                                            |

|-----|--------|-------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                     |

| 5   | REFGND | Analog Ground Reference.                                                            |

|     |        | Selects the ADC0 ground reference.                                                  |

|     |        | 0: The ADC0 ground reference is the GND pin.                                        |

|     |        | 1: The ADC0 ground reference is the P0.1/AGND pin.                                  |

| 4:3 | REFSL  | Voltage Reference Select.                                                           |

|     |        | Selects the ADC0 voltage reference.                                                 |

|     |        | 00: The ADC0 voltage reference is the P0.0/VREF pin.                                |

|     |        | 01: The ADC0 voltage reference is the VDD pin.                                      |

|     |        | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.        |

|     |        | 11: The ADC0 voltage reference is the internal 1.65 V high speed voltage reference. |

| 2   | TEMPE  | Temperature Sensor Enable.                                                          |

|     |        | Enables/Disables the internal temperature sensor.                                   |

|     |        | 0: Temperature Sensor Disabled.                                                     |

|     |        | 1: Temperature Sensor Enabled.                                                      |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                          |

|     |        | 0: Internal Bias Generator off.                                                     |

|     |        | 1: Internal Bias Generator on.                                                      |

| 0   | Unused | Read = 0b; Write = Don't Care.                                                      |

### **Table 17.2. Special Function Registers (Continued)**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register          | Address | Description                 | Page |

|-------------------|---------|-----------------------------|------|

| SBUF0             | 0x99    | UART0 Data Buffer           | 207  |

| SCON0             | 0x98    | UART0 Control               | 206  |

| SMB0ADM           | 0xD6    | SMBus Slave Address mask    | 191  |

| SMB0ADR           | 0xD7    | SMBus Slave Address         | 191  |

| SMB0CF            | 0xC1    | SMBus Configuration         | 186  |

| SMB0CN            | 0xC0    | SMBus Control               | 188  |

| SMB0DAT           | 0xC2    | SMBus Data                  | 192  |

| SP                | 0x81    | Stack Pointer               | 89   |

| SPI0CFG           | 0xA1    | SPI0 Configuration          | 174  |

| SPI0CKR           | 0xA2    | SPI0 Clock Rate Control     | 176  |

| SPI0CN            | 0xF8    | SPI0 Control                | 175  |

| SPI0DAT           | 0xA3    | SPI0 Data                   | 176  |

| TCON              | 0x88    | Timer/Counter Control       | 215  |

| TH0               | 0x8C    | Timer/Counter 0 High        | 218  |

| TH1               | 0x8D    | Timer/Counter 1 High        | 218  |

| TL0               | 0x8A    | Timer/Counter 0 Low         | 217  |

| TL1               | 0x8B    | Timer/Counter 1 Low         | 217  |

| TMOD              | 0x89    | Timer/Counter Mode          | 216  |

| TMR2CN            | 0xC8    | Timer/Counter 2 Control     | 222  |

| TMR2H             | 0xCD    | Timer/Counter 2 High        | 224  |

| TMR2L             | 0xCC    | Timer/Counter 2 Low         | 224  |

| TMR2RLH           | 0xCB    | Timer/Counter 2 Reload High | 223  |

| TMR2RLL           | 0xCA    | Timer/Counter 2 Reload Low  | 223  |

| VDM0CN            | 0xFF    | VDD Monitor Control         | 126  |

| XBR0              | 0xE1    | Port I/O Crossbar Control 0 | 148  |

| XBR1              | 0xE2    | Port I/O Crossbar Control 1 | 149  |

| All other SFR Loc | ations  | Reserved                    |      |

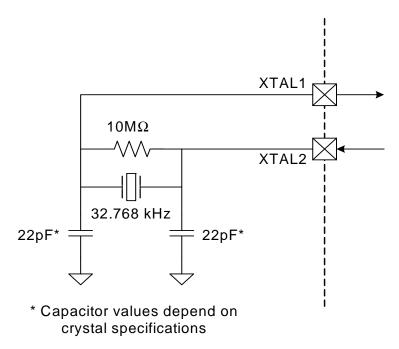

### **SFR Definition 22.4. OSCXCN: External Oscillator Control**

| Bit   | 7      | 6   | 5         | 4  | 3 | 2 | 1         | 0 |

|-------|--------|-----|-----------|----|---|---|-----------|---|

| Name  | XTLVLD | X   | OSCMD[2:0 | )] |   |   | XFCN[2:0] |   |

| Туре  | R      | R/W |           |    | R |   | R/W       |   |

| Reset | 0      | 0   | 0         | 0  | 0 | 0 | 0         | 0 |

### SFR Address = 0xB1

| Bit | Name        |         |                                                               | Function                   |                 |  |  |  |  |  |

|-----|-------------|---------|---------------------------------------------------------------|----------------------------|-----------------|--|--|--|--|--|

| 7   | XTLVLD      | Crystal | Crystal Oscillator Valid Flag.                                |                            |                 |  |  |  |  |  |

|     |             | (Read o | Read only when XOSCMD = 11x.)                                 |                            |                 |  |  |  |  |  |

|     |             | _       | al Oscillator is unused or                                    | •                          |                 |  |  |  |  |  |

|     |             | ,       | al Oscillator is running ar                                   |                            |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa | I Oscillator Mode Selec                                       | ct.                        |                 |  |  |  |  |  |

|     |             |         | ternal Oscillator circuit of                                  |                            |                 |  |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                                        |                            |                 |  |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                                        | e with divide by 2 stage.  |                 |  |  |  |  |  |

|     |             |         | Oscillator Mode.                                              |                            |                 |  |  |  |  |  |

|     |             |         | pacitor Oscillator Mode. /stal Oscillator Mode.               |                            |                 |  |  |  |  |  |

|     |             | -       | rstal Oscillator Mode with                                    | divide by 2 stage          |                 |  |  |  |  |  |

| 3   | Unused      | •       | 0; Write = Don't Care                                         | - arriae by 2 stage.       |                 |  |  |  |  |  |

|     |             |         |                                                               | Control Dita               |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   |         | Il Oscillator Frequency                                       |                            |                 |  |  |  |  |  |

|     |             |         | ording to the desired fred<br>ording to the desired K F       | quency for Crystal or RC r | node.           |  |  |  |  |  |

|     |             |         |                                                               |                            | C Mada          |  |  |  |  |  |

|     |             | XFCN    | Crystal Mode                                                  | RC Mode                    | C Mode          |  |  |  |  |  |

|     |             | 000     | f≤32 kHz                                                      | f≤25 kHz                   | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001     | 32 kHz < f ≤ 84 kHz                                           | 25 kHz < f ≤ 50 kHz        | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010     | 84 kHz < f ≤ 225 kHz                                          | 50 kHz < f ≤ 100 kHz       | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011     | 011 225 kHz < f ≤ 590 kHz 100 kHz < f ≤ 200 kHz K Factor = 22 |                            |                 |  |  |  |  |  |

|     |             | 100     | 590 kHz < f ≤ 1.5 MHz   200 kHz < f ≤ 400 kHz   K Factor = 65 |                            |                 |  |  |  |  |  |

|     |             | 101     | 1.5 MHz < f ≤ 4 MHz  400 kHz < f ≤ 800 kHz  K Factor = 180    |                            |                 |  |  |  |  |  |

|     |             | 110     | 4 MHz < f ≤ 10 MHz                                            | 800 kHz < f ≤ 1.6 MHz      | K Factor = 664  |  |  |  |  |  |

|     |             | 111     | 10 MHz < f ≤ 30 MHz                                           | 1.6 MHz < f ≤ 3.2 MHz      | K Factor = 1590 |  |  |  |  |  |

Figure 22.2. External 32.768 kHz Quartz Crystal Oscillator Connection Diagram

#### 22.3.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 22.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation 22.1, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in  $k\Omega$ .

#### **Equation 22.1. RC Mode Oscillator Frequency**

$$f = 1.23 \times 10^3 / (R \times C)$$

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$$f = 1.23(10^3) / RC = 1.23(10^3) / [246 \times 50] = 0.1 MHz = 100 kHz$$

Referring to the table in SFR Definition 22.4, the required XFCN setting is 010b.

#### 23.5. Port Match

Port match functionality allows system events to be triggered by a logic value change on P0 or P1. A software controlled value stored in the PnMATCH registers specifies the expected or normal logic values of P0 and P1. A Port mismatch event occurs if the logic levels of the Port's input pins no longer match the software controlled value. This allows Software to be notified if a certain change or pattern occurs on P0 or P1 input pins regardless of the XBRn settings.

The PnMASK registers can be used to individually select which P0 and P1 pins should be compared against the PnMATCH registers. A Port mismatch event is generated if (P0 & P0MASK) does not equal (P0MATCH & P0MASK) or if (P1 & P1MASK) does not equal (P1MATCH & P1MASK).

A Port mismatch event may be used to generate an interrupt or wake the device from a low power mode, such as IDLE or SUSPEND. See the Interrupts and Power Options chapters for more details on interrupt and wake-up sources.

### SFR Definition 25.3. SPI0CKR: SPI0 Clock Rate

| Bit   | 7 | 6 | 5 | 4   | 3     | 2 | 1 | 0 |

|-------|---|---|---|-----|-------|---|---|---|

| Name  |   |   |   | SCR | [7:0] |   |   |   |

| Туре  |   |   |   | R/  | W     |   |   |   |

| Reset | 0 | 0 | 0 | 0   | 0     | 0 | 0 | 0 |

### SFR Address = 0xA2

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                             |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SCR[7:0] | SPI0 Clock Rate.                                                                                                                                                                                                                                                                                                                     |

|     |          | These bits determine the frequency of the SCK output when the SPI0 module is configured for master mode operation. The SCK clock frequency is a divided version of the system clock, and is given in the following equation, where SYSCLK is the system clock frequency and SPI0CKR is the 8-bit value held in the SPI0CKR register. |

|     |          | $f_{SCK} = \frac{SYSCLK}{2 \times (SPI0CKR[7:0] + 1)}$                                                                                                                                                                                                                                                                               |

|     |          | for 0 <= SPI0CKR <= 255                                                                                                                                                                                                                                                                                                              |

|     |          | Example: If SYSCLK = 2 MHz and SPI0CKR = 0x04,                                                                                                                                                                                                                                                                                       |

|     |          | $f_{SCK} = \frac{2000000}{2 \times (4+1)}$                                                                                                                                                                                                                                                                                           |

|     |          | $f_{SCK} = 200kHz$                                                                                                                                                                                                                                                                                                                   |

### SFR Definition 25.4. SPI0DAT: SPI0 Data

| Bit   | 7 | 6 | 5 | 4      | 3       | 2 | 1 | 0 |

|-------|---|---|---|--------|---------|---|---|---|

| Name  |   |   |   | SPI0D. | AT[7:0] |   |   |   |

| Туре  |   |   |   | R/     | W       |   |   |   |

| Reset | 0 | 0 | 0 | 0      | 0       | 0 | 0 | 0 |

#### SFR Address = 0xA3

| Bit | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

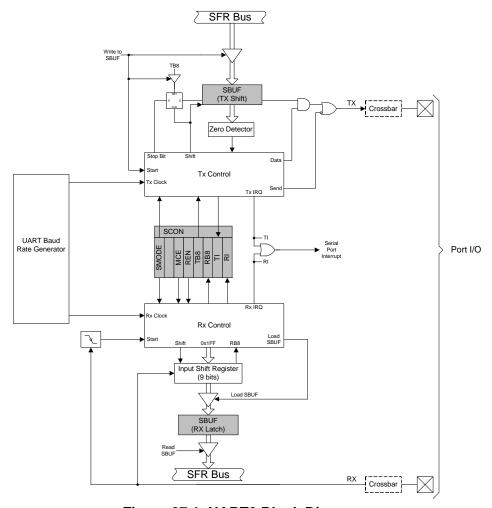

#### 27. UARTO

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "27.1. Enhanced Baud Rate Generation" on page 202). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. **Writes to SBUF0** always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

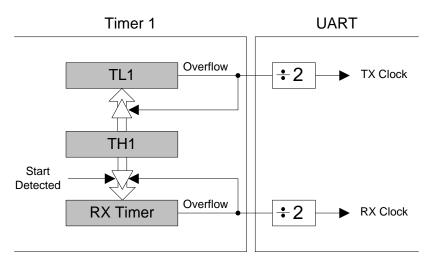

Figure 27.1. UARTO Block Diagram

#### 27.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 27.2), which is not user-accessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 27.2. UARTO Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "28.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 212). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK/4, SYSCLK/12, SYSCLK/48, the external oscillator clock/8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 27.1-A and Equation 27.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =

$$\frac{\text{T1}_{\text{CLK}}}{256 - \text{TH1}}$$

#### **Equation 27.1. UARTO Baud Rate**

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "28. Timers" on page 209. A quick reference for typical baud rates and system clock frequencies is given in Table 27.1 through Table 27.2. The internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

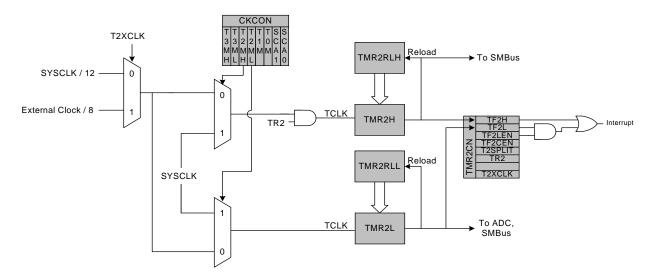

#### 28.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 28.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode. Timer 2 can also be used in capture mode to capture rising edges of the Comparator 0 output.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | X      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | X      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 28.5. Timer 2 8-Bit Mode Block Diagram

#### 29.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high-speed output, frequency output, 8-bit through 15-bit pulse width modulator, or 16-bit pulse width modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 29.2 summarizes the bit settings in the PCA0CPMn and PCA0PWM registers used to select the PCA capture/compare module's operating mode. Note that all modules set to use 8-bit through 15-bit PWM mode must use the same cycle length (8–15 bits). Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

Table 29.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules 1,2,3,4,5,6

| Operational Mode                              |   |   | PC | Α0 | СР | Mn |   |   |   | F | PC/ | \0P | WI | N   |

|-----------------------------------------------|---|---|----|----|----|----|---|---|---|---|-----|-----|----|-----|

| Bit Number                                    | 7 | 6 | 5  | 4  | 3  | 2  | 1 | 0 | 7 | 6 | 5   | 4   | 3  | 2-0 |

| Capture triggered by positive edge on CEXn    | Χ | Χ | 1  | 0  | 0  | 0  | 0 | Α | 0 | Χ | В   | Χ   | Χ  | XXX |

| Capture triggered by negative edge on CEXn    | Χ | Х | 0  | 1  | 0  | 0  | 0 | Α | 0 | Х | В   | Χ   | Χ  | XXX |

| Capture triggered by any transition on CEXn   | Χ | Х | 1  | 1  | 0  | 0  | 0 | Α | 0 | Х | В   | Χ   | Χ  | XXX |

| Software Timer                                | Χ | С | 0  | 0  | 1  | 0  | 0 | Α | 0 | Χ | В   | Χ   | Χ  | XXX |

| High Speed Output                             | Χ | С | 0  | 0  | 1  | 1  | 0 | Α | 0 | Χ | В   | Χ   | Χ  | XXX |

| Frequency Output                              | Χ | С | 0  | 0  | 0  | 1  | 1 | Α | 0 | Χ | В   | Χ   | Χ  | XXX |

| 8-Bit Pulse Width Modulator <sup>7</sup>      | 0 | С | 0  | 0  | Е  | 0  | 1 | Α | 0 | Χ | В   | Χ   | Χ  | 000 |

| 9-Bit Pulse Width Modulator <sup>7</sup>      | 0 | С | 0  | 0  | Е  | 0  | 1 | Α | D | Х | В   | Χ   | Χ  | 001 |

| 10-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0  | 0  | Е  | 0  | 1 | Α | D | Х | В   | Χ   | Χ  | 010 |

| 11-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0  | 0  | Е  | 0  | 1 | Α | D | Х | В   | Χ   | Χ  | 011 |

| 12-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0  | 0  | Е  | 0  | 1 | Α | D | Х | В   | Χ   | Χ  | 100 |

| 13-Bit Pulse Width Modulator <sup>7</sup>     |   |   |    | 0  | Е  | 0  | 1 | Α | D | Х | В   | Χ   | Χ  | 101 |

| 14-Bit Pulse Width Modulator <sup>7</sup>     |   |   |    | 0  | Е  | 0  | 1 | Α | D | Х | В   | Χ   | Χ  | 110 |

| 15-Bit Pulse Width Modulator <sup>7</sup>     | 0 | С | 0  | 0  | Е  | 0  | 1 | Α | D | Χ | В   | Χ   | Χ  | 111 |

| 16-Bit Pulse Width Modulator                  | 1 | С | 0  | 0  | Е  | 0  | 1 | Α | 0 | Χ | В   | Χ   | 0  | XXX |

| 16-Bit Pulse Width Modulator with Auto-Reload | 1 | С | 0  | 0  | Е  | 0  | 1 | Α | D | Χ | В   | Χ   | 1  | XXX |

#### Notes:

228

- **1.** X = Don't Care (no functional difference for individual module if 1 or 0).

- **2.** A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

- 3. B = Enable 8th through 15th bit overflow interrupt (Depends on setting of CLSEL[2:0]).

- **4.** C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

- **5.** D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- 6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

- 7. All modules set to 8-bit through 15-bit PWM mode use the same cycle length setting.

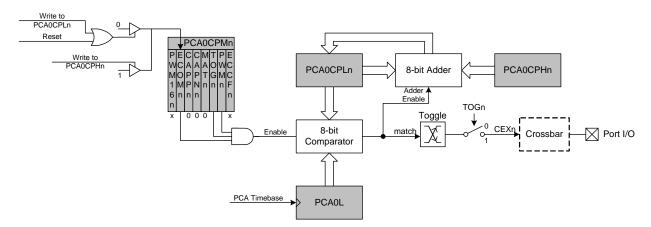

#### 29.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 29.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### **Equation 29.1. Square Wave Frequency Output**

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. The MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

Figure 29.7. PCA Frequency Output Mode

#### 29.3.5. 8-bit through 15-bit Pulse Width Modulator Modes

232

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer, and the setting of the PWM cycle length (8, 9, 10, 11, 12, 13, 14, or 15-bits). For backwards-compatibility with the 8-bit PWM mode available on other devices, the 8-bit PWM mode operates slightly different than 9, 10, 11, 12, 13, 14, and 15-bit PWM modes. It is important to note that all channels configured for 8-bit through 15-bit PWM mode will use the same cycle length. For example, it is not possible to configure one channel for 8-bit PWM mode and another for 11-bit mode. However, other PCA channels can be configured to Pin Capture, High-Speed Output, Software Timer, Frequency Output, or 16-bit PWM mode independently.

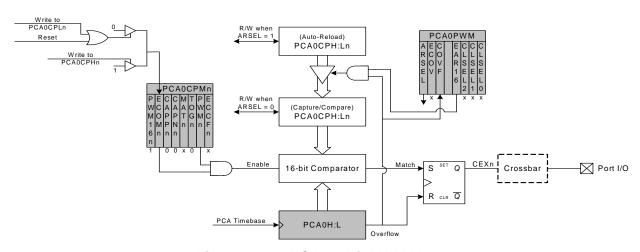

#### 29.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8-bit through 15-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register.

The duty cycle of the PWM output signal can be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0. This synchronous update feature allows software to asynchronously write a new PWM high time, which will then take effect on the following PWM period.

For backwards-compatibility with the 16-bit PWM mode available on other devices, the PWM duty cycle can also be changed without using the "Auto-Reload" register. To output a varying duty cycle without using the "Auto-Reload" register, new value writes should be synchronized with PCA CCFn match interrupts. Match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 29.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(65536 - PCA0CPn)}{65536}$$

### Equation 29.4. 16-Bit PWM Duty Cycle

Using Equation 29.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 29.10. PCA 16-Bit PWM Mode

### SFR Definition 29.5. PCA0L: PCA0 Counter/Timer Low Byte

| Bit   | 7   | 6   | 5   | 4   | 3      | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|--------|-----|-----|-----|

| Name  |     |     |     | PCA | 0[7:0] |     |     |     |

| Туре  | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0   | 0      | 0   | 0   | 0   |

### SFR Address = 0xF9

| Bit   | Name         | Function                                                                                                    |  |  |  |  |  |  |  |  |

|-------|--------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7:0   | PCA0[7:0]    | PCA Counter/Timer Low Byte.                                                                                 |  |  |  |  |  |  |  |  |

|       |              | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer.                                |  |  |  |  |  |  |  |  |

| Note: | When the WD  | When the WDTE bit is set to 1, the PCA0L register cannot be modified by software. To change the contents of |  |  |  |  |  |  |  |  |

|       | the PCA0L re | he PCA0L register, the Watchdog Timer must first be disabled.                                               |  |  |  |  |  |  |  |  |

### SFR Definition 29.6. PCA0H: PCA0 Counter/Timer High Byte

| Bit   | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|-------|-----|-----|-----|------|--------|-----|-----|-----|

| Name  |     |     |     | PCA0 | [15:8] |     |     |     |

| Туре  | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

### SFR Address = 0xFA

242

| Bit   | Name                                                                                                                                                                          | Function                                                                                                                                                                                                                                      |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0   | PCA0[15:8]                                                                                                                                                                    | PCA Counter/Timer High Byte.                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                               | The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer. Reads of this register will read the contents of a "snapshot" register, whose contents are updated only when the contents of PCA0L are read (see Section 29.1). |  |  |  |  |

| Note: | Note: When the WDTE bit is set to 1, the PCA0H register cannot be modified by software. To change the contents the PCA0H register, the Watchdog Timer must first be disabled. |                                                                                                                                                                                                                                               |  |  |  |  |