# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | · ·                                                             |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            |                                                                 |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f827-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

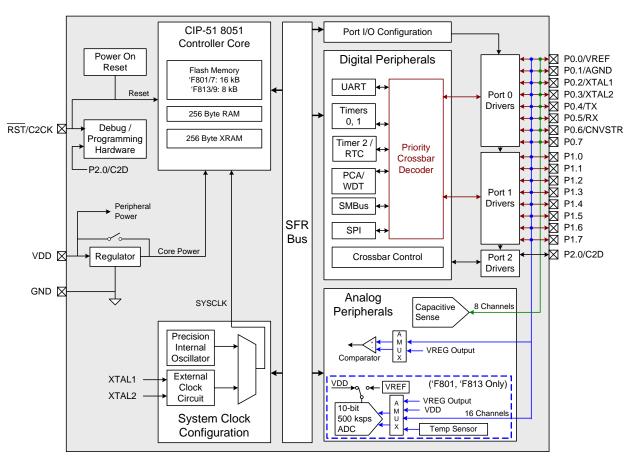

Figure 1.2. C8051F801, C8051F807, C8051F813, C8051F819 Block Diagram

| Part<br>Number | Digital<br>Port I/Os | Capacitive Sense<br>Channels | Flash<br>Memory<br>(kB) | RAM<br>(Bytes) | 10-bit<br>500 ksps<br>ADC | ADC<br>Channels | Temperature<br>Sensor | Package (RoHS) |

|----------------|----------------------|------------------------------|-------------------------|----------------|---------------------------|-----------------|-----------------------|----------------|

| C8051F800-GU   | 17                   | 16                           | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F801-GU   | 17                   | 8                            | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F802-GU   | 17                   |                              | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F800-GM   | 17                   | 16                           | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F801-GM   | 17                   | 8                            | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F802-GM   | 17                   | _                            | 16                      | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F803-GS   | 13                   | 12                           | 16                      | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F804-GS   | 13                   | 8                            | 16                      | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F805-GS   | 13                   | _                            | 16                      | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F806-GU   | 17                   | 16                           | 16                      | 512            | —                         |                 |                       | QSOP-24        |

| C8051F807-GU   | 17                   | 8                            | 16                      | 512            | —                         |                 |                       | QSOP-24        |

| C8051F808-GU   | 17                   | _                            | 16                      | 512            | —                         | —               | —                     | QSOP-24        |

| C8051F806-GM   | 17                   | 16                           | 16                      | 512            |                           |                 | —                     | QFN-20         |

| C8051F807-GM   | 17                   | 8                            | 16                      | 512            | —                         |                 | —                     | QFN-20         |

| C8051F808-GM   | 17                   | _                            | 16                      | 512            | —                         |                 | —                     | QFN-20         |

| C8051F809-GS   | 13                   | 12                           | 16                      | 512            | —                         |                 |                       | SOIC-16        |

| C8051F810-GS   | 13                   | 8                            | 16                      | 512            | —                         |                 |                       | SOIC-16        |

| C8051F811-GS   | 13                   | _                            | 16                      | 512            | —                         |                 |                       | SOIC-16        |

| C8051F812-GU   | 17                   | 16                           | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F813-GU   | 17                   | 8                            | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F814-GU   | 17                   | _                            | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QSOP-24        |

| C8051F812-GM   | 17                   | 16                           | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F813-GM   | 17                   | 8                            | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F814-GM   | 17                   | _                            | 8                       | 512            | $\checkmark$              | 16              | $\checkmark$          | QFN-20         |

| C8051F815-GS   | 13                   | 12                           | 8                       | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F816-GS   | 13                   | 8                            | 8                       | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F817-GS   | 13                   | —                            | 8                       | 512            | $\checkmark$              | 12              | $\checkmark$          | SOIC-16        |

| C8051F818-GU   | 17                   | 16                           | 8                       | 512            | —                         | —               | —                     | QSOP-24        |

| C8051F819-GU   | 17                   | 8                            | 8                       | 512            | —                         | —               | —                     | QSOP-24        |

| C8051F820-GU   | 17                   | —                            | 8                       | 512            | —                         | —               | —                     | QSOP-24        |

| C8051F818-GM   | 17                   | 16                           | 8                       | 512            | —                         |                 |                       | QFN-20         |

| C8051F819-GM   | 17                   | 8                            | 8                       | 512            | _                         |                 |                       | QFN-20         |

| C8051F820-GM   | 17                   |                              | 8                       | 512            |                           | _               |                       | QFN-20         |

Table 2.1. Product Selection Guide

#### Table 7.10. Power Management Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                 | Conditions | Min | Тур | Мах | Units   |

|---------------------------|------------|-----|-----|-----|---------|

| Idle Mode Wake-Up Time    |            | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time |            | _   | 500 | _   | ns      |

#### Table 7.11. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter                | Conditions                                             | Min | Тур  | Max | Units |  |  |  |  |  |  |

|--------------------------|--------------------------------------------------------|-----|------|-----|-------|--|--|--|--|--|--|

| Linearity                |                                                        | -   | 1    | —   | °C    |  |  |  |  |  |  |

| Slope                    |                                                        | —   | 2.43 | _   | mV/°C |  |  |  |  |  |  |

| Slope Error*             |                                                        |     | ±45  | —   | µV/°C |  |  |  |  |  |  |

| Offset                   | Temp = 0 °C                                            | —   | 873  | —   | mV    |  |  |  |  |  |  |

| Offset Error*            | Temp = 0 °C                                            |     | 14.5 | —   | mV    |  |  |  |  |  |  |

| *Note: Represents one st | Note: Represents one standard deviation from the mean. |     |      |     |       |  |  |  |  |  |  |

#### Table 7.12. Voltage Reference Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V; -40 to +85 °C unless otherwise specified.

| Parameter                                       | Conditions                           | Min  | Тур  | Max      | Units |  |  |  |  |  |

|-------------------------------------------------|--------------------------------------|------|------|----------|-------|--|--|--|--|--|

| Internal High Speed Reference (REFSL[1:0] = 11) |                                      |      |      |          |       |  |  |  |  |  |

| Output Voltage                                  | 25 °C ambient                        | 1.55 | 1.65 | 1.75     | V     |  |  |  |  |  |

| Turn-on Time                                    |                                      | —    | —    | 1.7      | μs    |  |  |  |  |  |

| Supply Current                                  |                                      |      | 180  |          | μA    |  |  |  |  |  |

| External Reference (REF0E = 0)                  |                                      |      |      |          |       |  |  |  |  |  |

| Input Voltage Range                             |                                      | 0    | —    | $V_{DD}$ |       |  |  |  |  |  |

| Input Current                                   | Sample Rate = 500 ksps; VREF = 3.0 V |      | 7    | _        | μA    |  |  |  |  |  |

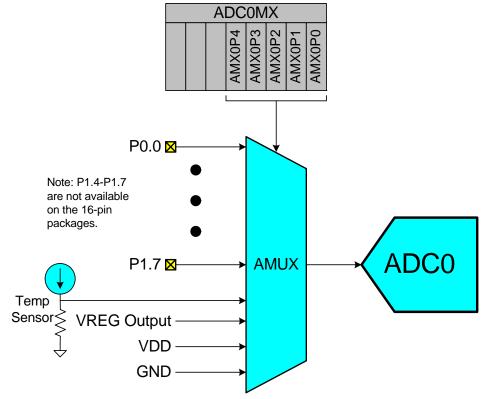

#### 8.5. ADC0 Analog Multiplexer

ADC0 on the C8051F800/1/2/3/4/5, C8051F812/3/4/5/6/7, C8051F824/5/6, and C8051F830/1/2 uses an analog input multiplexer to select the positive input to the ADC. Any of the following may be selected as the positive input: Port 0 or Port 1 I/O pins, the on-chip temperature sensor, or the positive power supply ( $V_{DD}$ ). The ADC0 input channel is selected in the ADC0MX register described in SFR Definition 8.9.

Figure 8.6. ADC0 Multiplexer Block Diagram

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set the corresponding bit in register PnMDIN to 0. To force the Crossbar to skip a Port pin, set the corresponding bit in register PnSKIP to 1. See Section "23. Port Input/Output" on page 138 for more Port I/O configuration details.

#### SFR Definition 13.1. CS0CN: Capacitive Sense Control

| Bit   | 7     | 6 | 5      | 4       | 3        | 2 | 1 | 0       |

|-------|-------|---|--------|---------|----------|---|---|---------|

| Name  | CS0EN |   | CS0INT | CS0BUSY | CS0CMPEN |   |   | CS0CMPF |

| Туре  | R/W   | R | R/W    | R/W     | R/W      | R | R | R       |

| Reset | 0     | 0 | 0      | 0       | 0        | 0 | 0 | 0       |

#### SFR Address = 0xB0; Bit-Addressable

| Bit   | Name      | Description                                                                                                                                                   |

|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | CS0EN     | CS0 Enable.                                                                                                                                                   |

|       |           | 0: CS0 disabled and in low-power mode.                                                                                                                        |

|       |           | 1: CS0 enabled and ready to convert.                                                                                                                          |

| 6     | Unused    | Read = 0b; Write = Don't care                                                                                                                                 |

| 5     | CS0INT    | CS0 Interrupt Flag.                                                                                                                                           |

|       |           | 0: CS0 has not completed a data conversion since the last time CS0INT was cleared.                                                                            |

|       |           | 1: CS0 has completed a data conversion.                                                                                                                       |

|       | 00051101/ | This bit is not automatically cleared by hardware.                                                                                                            |

| 4     | CS0BUSY   | CS0 Busy.                                                                                                                                                     |

|       |           | Read:                                                                                                                                                         |

|       |           | <ul><li>0: CS0 conversion is complete or a conversion is not currently in progress.</li><li>1: CS0 conversion is in progress.</li></ul>                       |

|       |           | Write:                                                                                                                                                        |

|       |           | 0: No effect.                                                                                                                                                 |

|       |           | 1: Initiates CS0 conversion if CS0CM[2:0] = 000b, 110b, or 111b.                                                                                              |

| 3     | CS0CMPEN  | CS0 Digital Comparator Enable Bit.                                                                                                                            |

|       |           | Enables the digital comparator, which compares accumulated CS0 conversion output to the value stored in CS0THH:CS0THL.<br>0: CS0 digital comparator disabled. |

|       |           | 1: CS0 digital comparator enabled.                                                                                                                            |

| 2:1   | Unused    | Read = 00b; Write = Don't care                                                                                                                                |

| 0     | CS0CMPF   | CS0 Digital Comparator Interrupt Flag.                                                                                                                        |

|       |           | 0: CS0 result is smaller than the value set by CS0THH and CS0THL since the last time CS0CMPF was cleared.                                                     |

|       |           | 1: CS0 result is greater than the value set by CS0THH and CS0THL since the last time CS0CMPF was cleared.                                                     |

| Note: |           | suspend mode due to a CS0 greater-than comparator event, the CS0CN register sed only after at least two system clock cycles have elapsed.                     |

| Table | 18.1. | Interrupt | Summary |

|-------|-------|-----------|---------|

|-------|-------|-----------|---------|

| Interrupt Source               | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|--------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                          | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0) | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow               | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1) | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow               | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                          | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

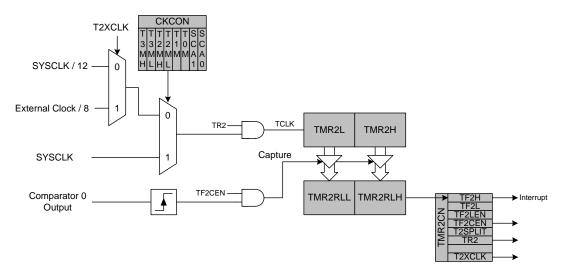

| Timer 2 Overflow               | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                           | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                |                | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                           | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| Port Match                     | 0x0043              | 8                 | None                                                                       | N/A              | N/A            | EMAT<br>(EIE1.1)   | PMAT<br>(EIP1.1)    |

| ADC0<br>Window Compare         | 0x004B              | 9                 | ADOWINT (ADC0CN.3)                                                         | Y                | N              | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0<br>Conversion Complete    | 0x0053              | 10                | AD0INT (ADC0CN.5)                                                          | Y                | N              | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

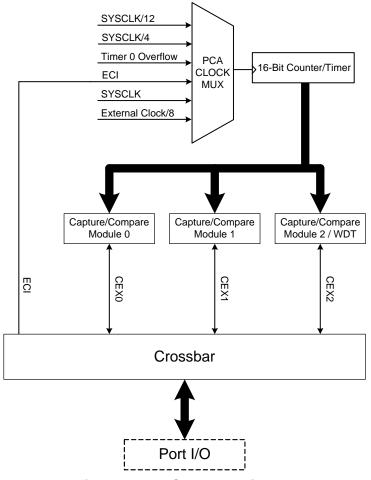

| Programmable<br>Counter Array  | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                           | Y                | N              | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                    | 0x0063              | 12                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N                | N              | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| RESERVED                       |                     |                   |                                                                            |                  |                |                    |                     |

| RESERVED                       |                     |                   |                                                                            | 1                |                |                    |                     |

| CS0 Conversion Com-<br>plete   | 0x007B              | 15                | CS0INT (CS0CN.5)                                                           | N                | N              | ECSCPT<br>(EIE2.0) | PSCCPT<br>(EIP2.0)  |

| CS0 Greater Than               | 0x0083              | 16                | CS0CMPF (CS0CN.0)                                                          | N                | N              | ECSGRT<br>(EIE2.1) | PSCGRT<br>(EIP2.1)  |

#### **18.2.** Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

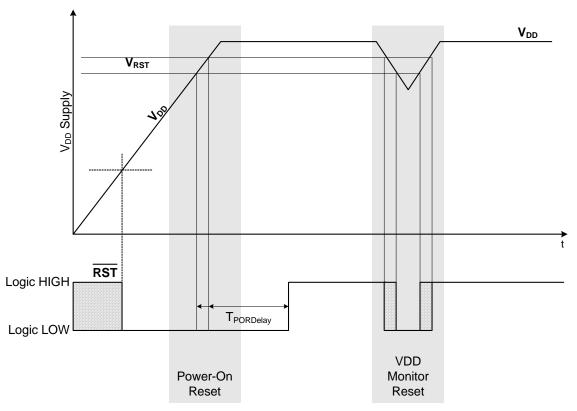

#### 21.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. A delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 21.2. plots the power-on and V<sub>DD</sub> monitor reset timing. The maximum V<sub>DD</sub> ramp time is 1 ms; slower ramp times may cause the device to be released from reset before V<sub>DD</sub> reaches the V<sub>RST</sub> level. For ramp times less than 1 ms, the power-on reset delay (T<sub>PORDelay</sub>) is typically less than 10 ms.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is enabled and selected as a reset source following a power-on reset.

Figure 21.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

### SFR Definition 21.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF

| Bit   | Name       | Description                                                                                    | Write                                                                                                                                                                | Read                                                                                                                                           |

|-------|------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                        | Don't care.                                                                                                                                                          | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                        | N/A                                                                                                                                                                  | Set to 1 if Flash<br>read/write/erase error<br>caused the last reset.                                                                          |

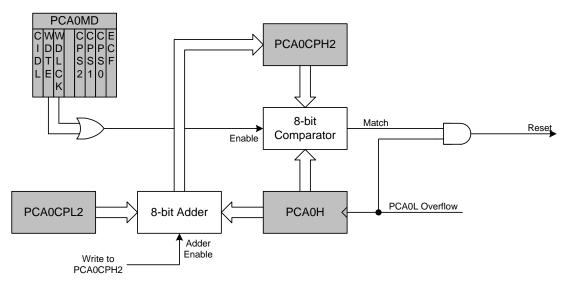

| 5     | CORSEF     | Comparator0 Reset Enable and Flag.                                                             | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                                 | Writing a 1 forces a sys-<br>tem reset.                                                                                                                              | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                   |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                     | N/A                                                                                                                                                                  | Set to 1 if Watchdog Timer<br>overflow caused the last<br>reset.                                                                               |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                     | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                       | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor as a reset source.<br>Writing 1 to this bit before the $V_{DD}$ monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                             | N/A                                                                                                                                                                  | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                           | s register                                                                                                                                                           | 1                                                                                                                                              |

#### 22.3.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 22.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation 22.2, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and V<sub>DD</sub> = the MCU power supply in volts.

#### Equation 22.2. C Mode Oscillator Frequency

$f = (KF)/(R \times V_{DD})$

For example: Assume  $V_{DD} = 3.0$  V and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 22.4 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

| Special<br>Function<br>Signals<br>(Control<br>Signals)<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK)<br>(Control<br>SCK) | P0.0 Skipped                                                              | AGND AGND                                        | P0.2 Skipped XTAL1 N                                | P0.3 Skipped                                         |                      | 5                           | CNVSTR 9                    | 7                            |                               |             | 2                            | 3                             | 4 <sup>1</sup>             | 5 <sup>1</sup>       | 6 <sup>1</sup>        | <b>7</b> <sup>1</sup> | Signal Unavailable to Crossbar |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|----------------------|-----------------------------|-----------------------------|------------------------------|-------------------------------|-------------|------------------------------|-------------------------------|----------------------------|----------------------|-----------------------|-----------------------|--------------------------------|--|

| Function<br>SignalsTX0RX0RX0SCKMISOMOSINSS2SDASCLCP0ASYSCLKCEX0CEX1CEX2ECIT1Pin Skip<br>SettingsIn this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Skipped                                                                   | AGND                                             |                                                     | Skipped                                              |                      |                             | CNVSTR                      |                              |                               |             |                              |                               |                            |                      |                       |                       | Crossbar                       |  |

| RX0<br>SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0 Skipped                                                              |                                                  | P0.2 Skipped                                        | P0.3 Skipped                                         |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | Crossbar                       |  |

| SCK<br>MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P0.0 Skipped                                                              |                                                  | P0.2 Skipped                                        | P0.3 Skipped                                         |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | Crossbar                       |  |

| MISO<br>MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped                                                              |                                                  | P0.2 Skipped                                        | P0.3 Skipped                                         |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | Crossbar                       |  |

| MOSI<br>NSS <sup>2</sup><br>SDA<br>SCL<br>CP0<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skipped                                                              |                                                  | P0.2 Skipped                                        | P0.3 Skipped                                         |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | Crossbar                       |  |

| NSS <sup>2</sup><br>SDA<br>SCL<br>CP00<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 Skipped                                                              |                                                  | P0.2 Skipped                                        | P0.3 Skipped                                         |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | Crossl                         |  |

| SDA<br>SCL<br>CP00<br>SYSCLK<br>CEX0<br>CEX1<br>CEX1<br>CEX2<br>ECI<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P0.0 Skipped                                                              |                                                  | P0.2 Skipped                                        | P0.3 Skipped                                         |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | ō                              |  |

| SCL<br>CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P0.0 Skipped                                                              |                                                  | P0.2 Skipped                                        | P0.3 Skipped                                         |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       |                                |  |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Skippe                                                               |                                                  | P0.2 Skippe                                         | P0.3 Skippe                                          |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | e to                           |  |

| CP0A<br>SYSCLK<br>CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P0.0 Ski                                                                  |                                                  | P0.2 Ski                                            | P0.3 Ski                                             |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | able                           |  |

| CEX0<br>CEX1<br>CEX2<br>ECI<br>T0<br>T1<br>Pin Skip<br>Settings<br>In this example<br>RX0 signals, th<br>signals are ass<br>P0.3 are config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P0.0                                                                      |                                                  | P0.2                                                | P0.3                                                 |                      |                             |                             |                              |                               |             |                              |                               |                            |                      |                       |                       | vail                           |  |