# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 13                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 16-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f832-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | Table 18.1. Interrupt Summary                                                | 104 |

|----|------------------------------------------------------------------------------|-----|

| 19 | . Flash Memory                                                               |     |

|    | Table 19.1. Flash Security Summary                                           | 115 |

| 20 | . Power Management Modes                                                     |     |

| 21 | . Reset Sources                                                              |     |

| 22 | . Oscillators and Clock Selection                                            |     |

| 23 | . Port Input/Output                                                          |     |

|    | Table 23.1. Port I/O Assignment for Analog Functions                         | 141 |

|    | Table 23.2. Port I/O Assignment for Digital Functions                        | 142 |

|    | Table 23.3. Port I/O Assignment for External Digital Event Capture Functions | 142 |

| 24 | . Cyclic Redundancy Check Unit (CRC0)                                        |     |

|    | Table 24.1. Example 16-bit CRC Outputs                                       | 160 |

|    | Table 24.2. Example 32-bit CRC Outputs                                       |     |

| 25 | . Enhanced Serial Peripheral Interface (SPI0)                                |     |

|    | Table 25.1. SPI Slave Timing Parameters                                      | 179 |

| 26 | . SMBus                                                                      |     |

|    | Table 26.1. SMBus Clock Source Selection                                     | 184 |

|    | Table 26.2. Minimum SDA Setup and Hold Times                                 |     |

|    | Table 26.3. Sources for Hardware Changes to SMB0CN                           |     |

|    | Table 26.4. Hardware Address Recognition Examples (EHACK = 1)                |     |

|    | Table 26.5. SMBus Status Decoding With Hardware ACK Generation Disabled      |     |

|    | (EHACK = 0)                                                                  | 197 |

|    | Table 26.6. SMBus Status Decoding With Hardware ACK Generation Enabled       |     |

|    | (EHACK = 1)                                                                  | 199 |

| 27 | . UARTO                                                                      |     |

|    | Table 27.1. Timer Settings for Standard Baud Rates                           |     |

|    | Using The Internal 24.5 MHz Oscillator                                       | 208 |

|    | Table 27.2. Timer Settings for Standard Baud Rates                           | 200 |

|    | Using an External 22.1184 MHz Oscillator                                     | 208 |

| 28 | . Timers                                                                     | 200 |

| -  | . Programmable Counter Array                                                 |     |

| 20 | Table 29.1. PCA Timebase Input Options                                       | 226 |

|    | Table 29.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare M       |     |

|    | ules <sup>1,2,3,4,5,6</sup>                                                  | 228 |

|    | Table 29.3. Watchdog Timer Timeout Intervals1                                | 227 |

| 30 | . C2 Interface                                                               | 201 |

| 00 |                                                                              |     |

| SFR Definition 28.8. TMR2CN: Timer 2 Control                     | 222 |

|------------------------------------------------------------------|-----|

| SFR Definition 28.9. TMR2RLL: Timer 2 Reload Register Low Byte   | 223 |

| SFR Definition 28.10. TMR2RLH: Timer 2 Reload Register High Byte | 223 |

| SFR Definition 28.11. TMR2L: Timer 2 Low Byte                    | 224 |

| SFR Definition 28.12. TMR2H Timer 2 High Byte                    | 224 |

| SFR Definition 29.1. PCA0CN: PCA0 Control                        | 238 |

| SFR Definition 29.2. PCA0MD: PCA0 Mode                           | 239 |

| SFR Definition 29.3. PCA0PWM: PCA0 PWM Configuration             | 240 |

| SFR Definition 29.4. PCA0CPMn: PCA0 Capture/Compare Mode         | 241 |

| SFR Definition 29.5. PCA0L: PCA0 Counter/Timer Low Byte          | 242 |

| SFR Definition 29.6. PCA0H: PCA0 Counter/Timer High Byte         | 242 |

| SFR Definition 29.7. PCA0CPLn: PCA0 Capture Module Low Byte      | 243 |

| SFR Definition 29.8. PCA0CPHn: PCA0 Capture Module High Byte     | 243 |

| C2 Register Definition 30.1. C2ADD: C2 Address                   | 244 |

| C2 Register Definition 30.3. REVID: C2 Revision ID               | 245 |

| C2 Register Definition 30.2. DEVICEID: C2 Device ID              | 245 |

| C2 Register Definition 30.4. FPCTL: C2 Flash Programming Control | 246 |

| C2 Register Definition 30.5. FPDAT: C2 Flash Programming Data    | 246 |

### 1. System Overview

C8051F80x-83x devices are fully integrated, mixed-signal, system-on-a-chip capacitive sensing MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Capacitive sense interface with 16 input channels

- 10-bit 500 ksps single-ended ADC with 16-channel analog multiplexer and integrated temperature sensor

- Precision calibrated 24.5 MHz internal oscillator

- 16 kb of on-chip Flash memory

- 512 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Three general-purpose 16-bit timers

- Programmable counter/timer array (PCA) with three capture/compare modules

- On-chip internal voltage reference

- On-chip Watchdog timer

- On-chip power-on reset and supply monitor

- On-chip voltage comparator

- 17 general purpose I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F80x-83x devices are truly stand-alone, system-on-a-chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The C8051F80x-83x processors include Silicon Laboratories' 2-Wire C2 Debug and Programming interface, which allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection of memory, viewing and modification of special function registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 1.8-3.6 V operation over the industrial temperature range (-45 to +85 °C). An internal LDO regulator is used to supply the processor core voltage at 1.8 V. The Port I/O and RST pins are tolerant of input signals up to 5 V. See Table 2.1 for ordering information. Block diagrams of the devices in the C8051F80x-83x family are shown in Figure 1.1 through Figure 1.9.

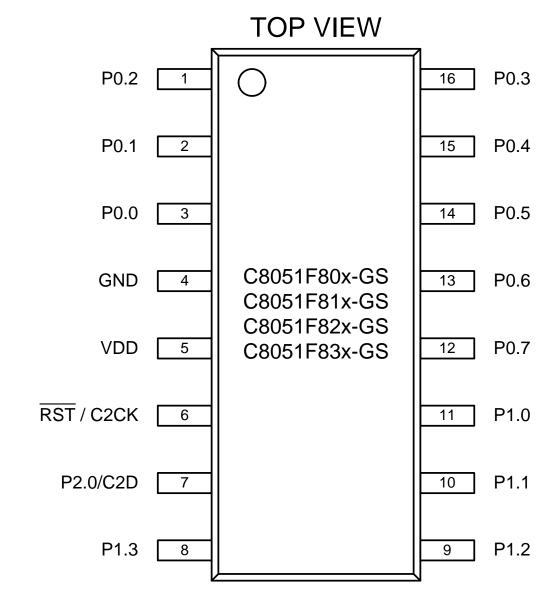

Figure 3.3. SOIC-16 Pinout Diagram (Top View)

### 9. Temperature Sensor

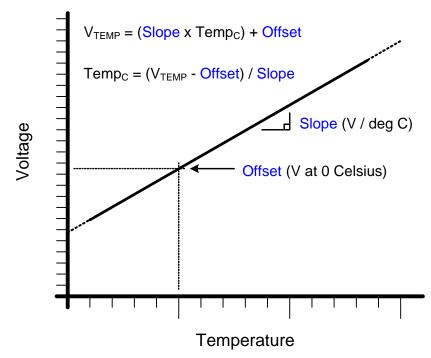

An on-chip temperature sensor is included on the C8051F800/1/2/3/4/5, C8051F812/3/4/5/6/7, C8051F824/5/6, and C8051F830/1/2 which can be directly accessed via the ADC multiplexer in singleended configuration. To use the ADC to measure the temperature sensor, the ADC mux channel should be configured to connect to the temperature sensor. The temperature sensor transfer function is shown in Figure 9.1. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the ADC multiplexer is set correctly. The TEMPE bit in register REF0CN enables/disables the temperature sensor, as described in SFR Definition 10.1. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 7.11 for the slope and offset parameters of the temperature sensor.

Figure 9.1. Temperature Sensor Transfer Function

#### 9.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 5.1 for linearity specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. Typically a 1-point (offset) calibration includes the following steps:

- 1. Control/measure the ambient temperature (this temperature must be known).

- 2. Power the device, and delay for a few seconds to allow for self-heating.

- 3. Perform an ADC conversion with the temperature sensor selected as the ADC's input.

- 4. Calculate the offset characteristics, and store this value in non-volatile memory for use with subsequent temperature sensor measurements.

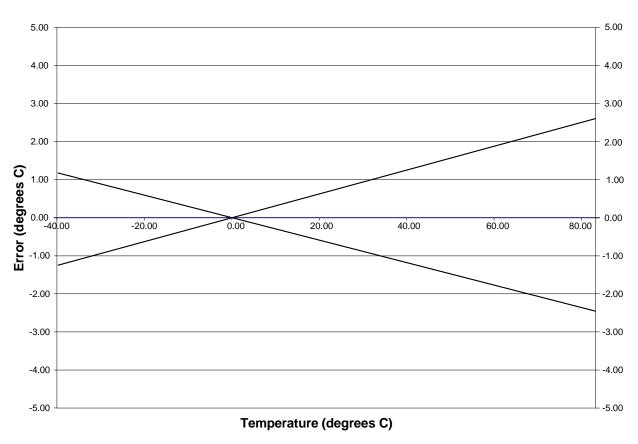

Figure 5.3 shows the typical temperature sensor error assuming a 1-point calibration at 0 °C.

Parameters that affect ADC measurement, in particular the voltage reference value, will also affect temperature measurement.

Figure 9.2. Temperature Sensor Error with 1-Point Calibration at 0 °C

## SFR Definition 12.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

SFR Address = 0x9B

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0–.                                                    |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## SFR Definition 12.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|---|---|--------|--------|---|---|------------|---|

| Name  |   |   | CP0RIE | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

#### SFR Address = 0x9D

| Bit | Name       | Function                                                                   |  |  |  |  |  |  |

|-----|------------|----------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:6 | Unused     | Read = 00b, Write = Don't Care.                                            |  |  |  |  |  |  |

| 5   | CP0RIE     | Comparator0 Rising-Edge Interrupt Enable.                                  |  |  |  |  |  |  |

|     |            | Comparator0 Rising-edge interrupt disabled.                                |  |  |  |  |  |  |

|     |            | 1: Comparator0 Rising-edge interrupt enabled.                              |  |  |  |  |  |  |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.                                 |  |  |  |  |  |  |

|     |            | 0: Comparator0 Falling-edge interrupt disabled.                            |  |  |  |  |  |  |

|     |            | 1: Comparator0 Falling-edge interrupt enabled.                             |  |  |  |  |  |  |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                            |  |  |  |  |  |  |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.                                                   |  |  |  |  |  |  |

|     |            | These bits affect the response time and power consumption for Comparator0. |  |  |  |  |  |  |

|     |            | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)              |  |  |  |  |  |  |

|     |            | 01: Mode 1                                                                 |  |  |  |  |  |  |

|     |            | 10: Mode 2                                                                 |  |  |  |  |  |  |

|     |            | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)               |  |  |  |  |  |  |

#### SFR Definition 18.4. EIE2: Extended Interrupt Enable 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|-------|---|---|---|---|---|---|--------|--------|

| Name  |   |   |   |   |   |   | ECSGRT | ECSCPT |

| Туре  | R | R | R | R | R | R | R/W    | R/W    |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

SFR Address = 0xE7

| Bit | Name   | Function                                                                                                                                                                           |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b; Write = don't care.                                                                                                                                                |

| 1   | ECSGRT | Enable Capacitive Sense Greater Than Comparator Interrupt.<br>0: Disable Capacitive Sense Greater Than Comparator interrupt.<br>1: Enable interrupt requests generated by CS0CMPF. |

| 0   | ECSCPT | Enable Capacitive Sense Conversion Complete Interrupt.<br>0: Disable Capacitive Sense Conversion Complete interrupt.<br>1: Enable interrupt requests generated by CS0INT.          |

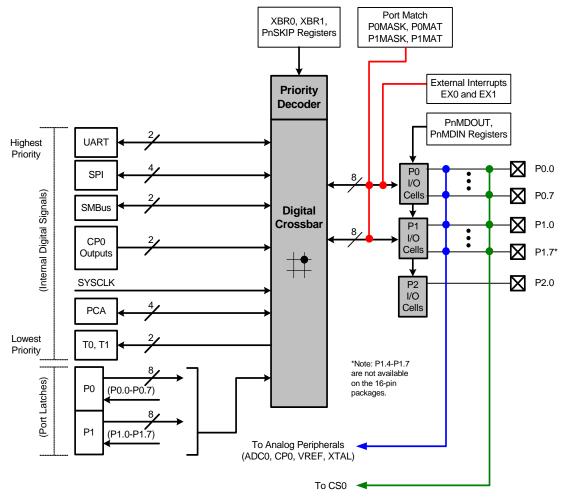

## 23. Port Input/Output

Digital and analog resources are available through 17 I/O pins (24-pin and 20-pin packages) or 13 I/O pins (16-pin packages). Port pins P0.0–P1.7 can be defined as general-purpose I/O (GPIO) or assigned to one of the internal digital resources as shown in Figure 23.4. Port pin P2.0 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 23.5). The registers XBR0 and XBR1, defined in SFR Definition 23.1 and SFR Definition 23.2, are used to select internal digital functions.

All Port I/Os are 5 V tolerant (refer to Figure 23.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Section "7. Electrical Characteristics" on page 39.

Figure 23.1. Port I/O Functional Block Diagram

## SFR Definition 23.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7 | 6 | 5     | 4    | 3      | 2     | 1     | 0     |

|-------|---|---|-------|------|--------|-------|-------|-------|

| Name  |   |   | CP0AE | CP0E | SYSCKE | SMB0E | SPI0E | URT0E |

| Туре  | R | R | R/W   | R/W  | R/W    | R/W   | R/W   | R/W   |

| Reset | 0 | 0 | 0     | 0    | 0      | 0     | 0     | 0     |

SFR Address = 0xE1

| Bit | Name   | Function                                                                             |

|-----|--------|--------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b. Write = don't care.                                                      |

| 5   | CP0AE  | Comparator0 Asynchronous Output Enable.                                              |

|     |        | 0: Asynchronous CP0 unavailable at Port pin.                                         |

|     |        | 1: Asynchronous CP0 routed to Port pin.                                              |

| 4   | CP0E   | Comparator0 Output Enable.                                                           |

|     |        | 0: CP0 unavailable at Port pin.                                                      |

|     |        | 1: CP0 routed to Port pin.                                                           |

| 3   | SYSCKE | SYSCLK Output Enable.                                                                |

|     |        | 0: <u>SYSCLK</u> unavailable at Port pin.                                            |

|     |        | 1: SYSCLK output routed to Port pin.                                                 |

| 2   | SMB0E  | SMBus I/O Enable.                                                                    |

|     |        | 0: SMBus I/O unavailable at Port pins.                                               |

|     |        | 1: SMBus I/O routed to Port pins.                                                    |

| 1   | SPI0E  | SPI I/O Enable.                                                                      |

|     |        | 0: SPI I/O unavailable at Port pins.                                                 |

|     |        | 1: SPI I/O routed to Port pins. Note that the SPI can be assigned either 3 or 4 GPIO |

|     |        | pins.                                                                                |

| 0   | URT0E  | UART I/O Output Enable.                                                              |

|     |        | 0: UART I/O unavailable at Port pin.                                                 |

|     |        | 1: UART TX0, RX0 routed to Port pins P0.4 and P0.5.                                  |

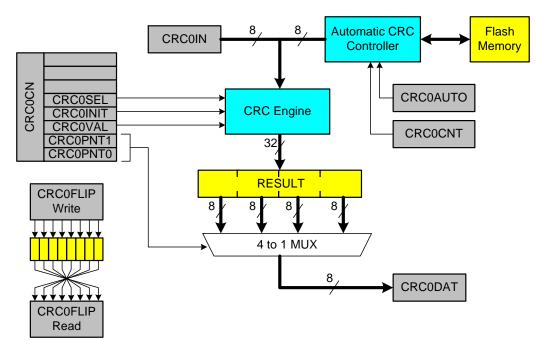

## 24. Cyclic Redundancy Check Unit (CRC0)

C8051F80x-83x devices include a cyclic redundancy check unit (CRC0) that can perform a CRC using a 16-bit or 32-bit polynomial. CRC0 accepts a stream of 8-bit data written to the CRC0IN register. CRC0 posts the 16-bit or 32-bit result to an internal register. The internal result register may be accessed indirectly using the CRC0PNT bits and CRC0DAT register, as shown in Figure 24.1. CRC0 also has a bit reverse register for quick data manipulation.

Figure 24.1. CRC0 Block Diagram

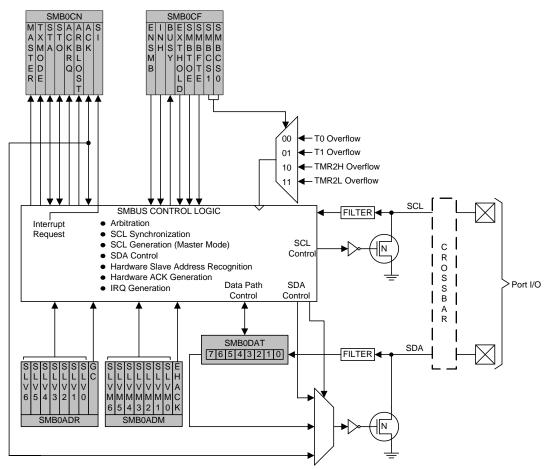

### 26. SMBus

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock as a master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The SMBus interface may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. The SMBus peripheral can be fully driven by software (i.e., software accepts/rejects slave addresses, and generates ACKs), or hardware slave address recognition and automatic ACK generation can be enabled to minimize software overhead. A block diagram of the SMBus peripheral and the associated SFRs is shown in Figure 26.1.

Figure 26.1. SMBus Block Diagram

#### 26.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 26.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER indicates whether a device is the master or slave during the current transfer. TXMODE indicates whether the device is transmitting or receiving data for the current byte.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a 1 to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a 1 to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 26.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

#### 26.4.2.1. Software ACK Generation

When the EHACK bit in register SMB0ADM is cleared to 0, the firmware on the device must detect incoming slave addresses and ACK or NACK the slave address and incoming data bytes. As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received during the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

#### 26.4.2.2. Hardware ACK Generation

When the EHACK bit in register SMB0ADM is set to 1, automatic slave address recognition and ACK generation is enabled. More detail about automatic slave address recognition can be found in Section 26.4.3. As a receiver, the value currently specified by the ACK bit will be automatically sent on the bus during the ACK cycle of an incoming data byte. As a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. The ACKRQ bit is not used when hardware ACK generation is enabled. If a received slave address is NACKed by hardware, further slave events will be ignored until the next START is detected, and no interrupt will be generated.

Table 26.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 26.5 for SMBus status decoding using the SMB0CN register.

### SFR Definition 26.3. SMB0ADR: SMBus Slave Address

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|----------|---|---|---|---|---|---|---|--|

| Name  | SLV[6:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W      |   |   |   |   |   |   |   |  |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xD7

| Bit | Name     | Function                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV[6:0] | SMBus Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |          | Defines the SMBus Slave Address(es) for automatic hardware acknowledgement.<br>Only address bits which have a 1 in the corresponding bit position in SLVM[6:0]<br>are checked against the incoming address. This allows multiple addresses to be<br>recognized.            |

| 0   | GC       | General Call Address Enable.                                                                                                                                                                                                                                               |

|     |          | <ul> <li>When hardware address recognition is enabled (EHACK = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

#### SFR Definition 26.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|-------|-----------|---|---|---|---|---|---|-------|

| Name  | SLVM[6:0] |   |   |   |   |   |   | EHACK |

| Туре  | R/W       |   |   |   |   |   |   | R/W   |

| Reset | 1         | 1 | 1 | 1 | 1 | 1 | 1 | 0     |

#### SFR Address = 0xD6

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |

|     |           | <ul><li>Enables hardware acknowledgement of slave address and received data bytes.</li><li>0: Firmware must manually acknowledge all incoming address and data bytes.</li><li>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.</li></ul>                |

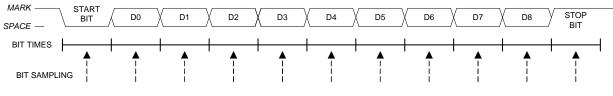

#### 27.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to 1. If the above conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set to 1. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to 1.

### SFR Definition 27.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7                  | 6           | 5                                      | 4 | 3 | 2 | 1 | 0 |

|-------|--------------------|-------------|----------------------------------------|---|---|---|---|---|

| Nam   | е                  | SBUF0[7:0]  |                                        |   |   |   |   |   |

| Туре  | ype R/W            |             |                                        |   |   |   |   |   |

| Rese  | et O               | 0           | 0                                      | 0 | 0 | 0 | 0 | 0 |

| SFR A | SFR Address = 0x99 |             |                                        |   |   |   |   |   |

| Bit   | Name               | Function    |                                        |   |   |   |   |   |

| 7:0   | SBUF0[7:0]         | Serial Data | Serial Data Buffer Bits 7–0 (MSB–LSB). |   |   |   |   |   |

|       |                    |             |                                        | • |   |   |   |   |

This SFR accesses two registers; a transmit shift register and a receive latch register. When data is written to SBUF0, it goes to the transmit shift register and is held for serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of SBUF0 returns the contents of the receive latch.

### SFR Definition 28.1. CKCON: Clock Control

| Bit   | 7 | 6 | 5    | 4    | 3   | 2   | 1   | 0     |

|-------|---|---|------|------|-----|-----|-----|-------|

| Name  |   |   | T2MH | T2ML | T1M | ТОМ | SCA | [1:0] |

| Туре  | R | R | R/W  | R/W  | R/W | R/W | R/  | W     |

| Reset | 0 | 0 | 0    | 0    | 0   | 0   | 0   | 0     |

#### SFR Address = 0x8E

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused   | Read = 0b; Write = Don't care                                                                                                                                                                                                                                                                                                                             |

| 5   | T2MH     | Timer 2 High Byte Clock Select.Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.1: Timer 2 high byte uses the system clock.                                                                                                                      |

| 4   | T2ML     | <ul> <li>Timer 2 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |

| 3   | T1       | <b>Timer 1 Clock Select.</b><br>Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                                     |

| 2   | T0       | Timer 0 Clock Select.Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].1: Counter/Timer 0 uses the system clock.                                                                                                                                        |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.These bits control the Timer 0/1 Clock Prescaler:00: System clock divided by 1201: System clock divided by 410: System clock divided by 4811: External clock divided by 8 (synchronized with the system clock)                                                                                                                    |

### SFR Definition 28.4. TL0: Timer 0 Low Byte

| Bit           | 7            | 6            | 5                                                       | 4 | 3 | 2 | 1 | 0 |  |

|---------------|--------------|--------------|---------------------------------------------------------|---|---|---|---|---|--|

| Name TL0[7:0] |              |              |                                                         |   |   |   |   |   |  |

| Туре          | •            | R/W          |                                                         |   |   |   |   |   |  |

| Rese          | t 0          | 0            | 0                                                       | 0 | 0 | 0 | 0 | 0 |  |

| SFR A         | ddress = 0x8 | A            |                                                         |   |   |   |   |   |  |

| Bit           | Name         | Function     |                                                         |   |   |   |   |   |  |

| 7:0           | TL0[7:0]     | Timer 0 Lov  | Timer 0 Low Byte.                                       |   |   |   |   |   |  |

|               |              | The TI O rec | The TL0 register is the low byte of the 16-bit Timer 0. |   |   |   |   |   |  |

## SFR Definition 28.5. TL1: Timer 1 Low Byte

| Bit                | 7         | 6              | 5        | 4   | 3     | 2 | 1 | 0        |

|--------------------|-----------|----------------|----------|-----|-------|---|---|----------|

| Name               | 9         |                |          | TL1 | [7:0] |   |   | <u>I</u> |

| Туре               |           | R/W            |          |     |       |   |   |          |

| Rese               | t 0       | 0              | 0        | 0   | 0     | 0 | 0 | 0        |

| SFR Address = 0x8B |           |                |          |     |       |   |   |          |

| Bit                | Name      |                | Function |     |       |   |   |          |

| 7.0                | TL 4[7.0] | Time or 4 1 or | Durta    |     |       |   |   | -        |

| 7:0 | TL1[7:0] | Timer 1 Low Byte.                                       |

|-----|----------|---------------------------------------------------------|

|     |          | The TL1 register is the low byte of the 16-bit Timer 1. |

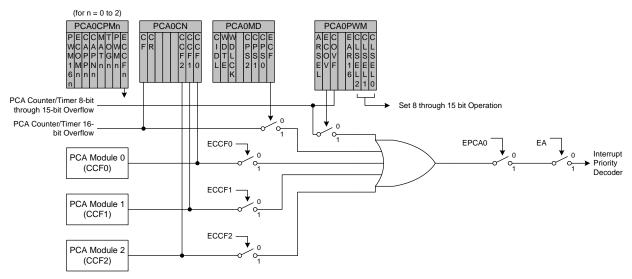

#### 29.2. PCA0 Interrupt Sources

Figure 29.3 shows a diagram of the PCA interrupt tree. There are five independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, an intermediate overflow flag (COVF), which can be set on an overflow from the 8th through 15th bit of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, and CCF2), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, ECOV for COVF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit in the IE register and the EPCA0 bit in the EIE1 register to logic 1.

Figure 29.3. PCA Interrupt Block Diagram