# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M4F                                                        |

| Core Size                  | 32-Bit Dual-Core                                                           |

| Speed                      | 120MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                            |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 1MB (1M x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 6x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-LQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4cmp16ca-au |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Examples

| SMLSD   | R0, | R4, | R5, | R6 |   | Multiplies bottom halfword of R4 with bottom halfword of R5, multiplies top halfword of R4 |

|---------|-----|-----|-----|----|---|--------------------------------------------------------------------------------------------|

|         |     |     |     |    | ; | with top halfword of R5, subtracts second from                                             |

|         |     |     |     |    | ; | first, adds R6, writes to R0                                                               |

| SMLSDX  | R1, | R3, | R2, | R0 | ; | Multiplies bottom halfword of R3 with top                                                  |

|         |     |     |     |    | ; | halfword of R2, multiplies top halfword of R3                                              |

|         |     |     |     |    | ; | with bottom halfword of R2, subtracts second from                                          |

|         |     |     |     |    | ; | first, adds R0, writes to R1                                                               |

| SMLSLD  | R3, | R6, | R2, | R7 | ; | Multiplies bottom halfword of R6 with bottom                                               |

|         |     |     |     |    | ; | halfword of R2, multiplies top halfword of R6                                              |

|         |     |     |     |    | ; | with top halfword of R2, subtracts second from                                             |

|         |     |     |     |    | ; | first, adds R6:R3, writes to R6:R3                                                         |

| SMLSLDX | R3, | R6, | R2, | R7 | ; | Multiplies bottom halfword of R6 with top                                                  |

|         |     |     |     |    | ; | halfword of R2, multiplies top halfword of R6                                              |

|         |     |     |     |    | ; | with bottom halfword of R2, subtracts second from                                          |

|         |     |     |     |    | ; | first, adds R6:R3, writes to R6:R3.                                                        |

#### 12.6.7.7 UQADD and UQSUB

Saturating Add and Saturating Subtract Unsigned.

Syntax

op{cond} {Rd}, Rn, Rm

op{cond} {Rd}, Rn, Rm

where:

| ор     | is one of:                                                   |

|--------|--------------------------------------------------------------|

|        | UQADD8 Saturating four unsigned 8-bit integer additions.     |

|        | UQADD16 Saturating two unsigned 16-bit integer additions.    |

|        | UDSUB8 Saturating four unsigned 8-bit integer subtractions.  |

|        | UQSUB16 Saturating two unsigned 16-bit integer subtractions. |

| cond   | is an optional condition code, see "Conditional Execution".  |

| Rd     | is the destination register.                                 |

| Rn, Rm | are registers holding the first and second operands.         |

#### Operation

These instructions add or subtract two or four values and then writes an unsigned saturated value in the destination register.

The UQADD16 instruction:

- Adds the respective top and bottom halfwords of the first and second operands.

- Saturates the result of the additions for each halfword in the destination register to the unsigned range  $0 \le x \le 2^{16}$ -1, where x is 16.

The UQADD8 instruction:

- Adds each respective byte of the first and second operands.

- Saturates the result of the addition for each byte in the destination register to the unsigned range  $0 \le x \le 2^{8}$ -1, where x is 8.

The UQSUB16 instruction:

- Subtracts both halfwords of the second operand from the respective halfwords of the first operand.

- Saturates the result of the differences in the destination register to the unsigned range  $0 \le x \le 2^{16}$ -1, where x is 16.

The UQSUB8 instructions:

- Subtracts the respective bytes of the second operand from the respective bytes of the first operand.

- Saturates the results of the differences for each byte in the destination register to the unsigned range  $0 \le x \le 2^8$ -1, where x is 8.

Restrictions

Do not use SP and do not use PC.

## 12.9.1.7 Configuration and Control Register

| Name:   | SCB_CCR    |    |           |             |    |              |                    |

|---------|------------|----|-----------|-------------|----|--------------|--------------------|

| Access: | Read/Write |    |           |             |    |              |                    |

| 31      | 30         | 29 | 28        | 27          | 26 | 25           | 24                 |

| _       | -          | -  | -         | -           | _  | —            | -                  |

| 23      | 22         | 21 | 20        | 19          | 18 | 17           | 16                 |

| -       | -          | -  | -         | -           | _  | _            | -                  |

| 15      | 14         | 13 | 12        | 11          | 10 | 9            | 8                  |

| -       | -          | -  | -         | -           | —  | STKALIGN     | BFHFNMIGN          |

| 7       | 6          | 5  | 4         | 3           | 2  | 1            | 0                  |

| -       | -          | -  | DIV_0_TRP | UNALIGN_TRP | _  | USERSETMPEND | NONBASETHRDE<br>NA |

The SCB\_CCR controls the entry to the Thread mode and enables the handlers for NMI, hard fault and faults escalated by FAULTMASK to ignore BusFaults. It also enables the division by zero and unaligned access trapping, and the access to the NVIC\_STIR by unprivileged software (see "Software Trigger Interrupt Register").

#### • STKALIGN: Stack Alignment

Indicates the stack alignment on exception entry:

0: 4-byte aligned.

1: 8-byte aligned.

On exception entry, the processor uses bit [9] of the stacked PSR to indicate the stack alignment. On return from the exception, it uses this stacked bit to restore the correct stack alignment.

#### • BFHFNMIGN: Bus Faults Ignored

Enables handlers with priority -1 or -2 to ignore data bus faults caused by load and store instructions. This applies to the hard fault and FAULTMASK escalated handlers:

0: Data bus faults caused by load and store instructions cause a lock-up.

1: Handlers running at priority -1 and -2 ignore data bus faults caused by load and store instructions.

Set this bit to 1 only when the handler and its data are in absolutely safe memory. The normal use of this bit is to probe system devices and bridges to detect control path problems and fix them.

#### • DIV\_0\_TRP: Division by Zero Trap

Enables faulting or halting when the processor executes an SDIV or UDIV instruction with a divisor of 0:

0: Do not trap divide by 0.

1: Trap divide by 0.

When this bit is set to 0, a divide by zero returns a quotient of 0.

# • SIZE: Size of the MPU Protection Region

The minimum permitted value is 3 (b00010).

The SIZE field defines the size of the MPU memory region specified by the MPU\_RNR. as follows:

(Region size in bytes) =  $2^{(SIZE+1)}$

The smallest permitted region size is 32B, corresponding to a SIZE value of 4. The table below gives an example of SIZE values, with the corresponding region size and value of N in the MPU\_RBAR.

| SIZE Value  | Region Size | Value of N <sup>(1)</sup> | Note                   |

|-------------|-------------|---------------------------|------------------------|

| b00100 (4)  | 32 B        | 5                         | Minimum permitted size |

| b01001 (9)  | 1 KB        | 10                        | _                      |

| b10011 (19) | 1 MB        | 20                        | -                      |

| b11101 (29) | 1 GB        | 30                        | _                      |

| b11111 (31) | 4 GB        | b01100                    | Maximum possible size  |

Note: 1. In the MPU\_RBAR; see "MPU Region Base Address Register"

#### • ENABLE: Region Enable

Note: For information about access permission, see "MPU Access Permission Attributes".

# 12.13 Glossary

This glossary describes some of the terms used in technical documents from ARM.

| Abort             | A mechanism that indicates to a processor that the value associated with a memory access is invalid.<br>An abort can be caused by the external or internal memory system as a result of attempting to access<br>invalid instruction or data memory.                                                                                                                                                                                                                                                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aligned           | A data item stored at an address that is divisible by the number of bytes that defines the data size is said to be aligned. Aligned words and halfwords have addresses that are divisible by four and two respectively. The terms word-aligned and halfword-aligned therefore stipulate addresses that are divisible by four and two respectively.                                                                                                                                                     |

| Banked register   | A register that has multiple physical copies, where the state of the processor determines which copy is used. The Stack Pointer, SP (R13) is a banked register.                                                                                                                                                                                                                                                                                                                                        |

| Base register     | In instruction descriptions, a register specified by a load or store instruction that is used to hold the base value for the instruction's address calculation. Depending on the instruction and its addressing mode, an offset can be added to or subtracted from the base register value to form the address that is sent to memory.                                                                                                                                                                 |

|                   | See also "Index register".                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Big-endian (BE)   | Byte ordering scheme in which bytes of decreasing significance in a data word are stored at increasing addresses in memory.                                                                                                                                                                                                                                                                                                                                                                            |

|                   | See also "Byte-invariant", "Endianness", "Little-endian (LE)".                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Big-endian memory | Memory in which:<br>a byte or halfword at a word-aligned address is the most significant byte or halfword within the word at<br>that address,<br>a byte at a halfword-aligned address is the most significant byte within the halfword at that address.                                                                                                                                                                                                                                                |

|                   | See also "Little-endian memory".                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Breakpoint        | A breakpoint is a mechanism provided by debuggers to identify an instruction at which program execution is to be halted. Breakpoints are inserted by the programmer to enable inspection of register contents, memory locations, variable values at fixed points in the program execution to test that the program is operating correctly. Breakpoints are removed after the program is successfully tested.                                                                                           |

| Byte-invariant    | In a byte-invariant system, the address of each byte of memory remains unchanged when switching between little-endian and big-endian operation. When a data item larger than a byte is loaded from or stored to memory, the bytes making up that data item are arranged into the correct order depending on the endianness of the memory access.<br>An ARM byte-invariant implementation also supports unaligned halfword and word memory accesses. It expects multi-word accesses to be word-aligned. |

| Condition field   | A four-bit field in an instruction that specifies a condition under which the instruction can execute.                                                                                                                                                                                                                                                                                                                                                                                                 |

# 13.7.8 ID Code Register

Access: Read-only

| 31 | 30                    | 29    | 28     | 27    | 26        | 25           | 24 |

|----|-----------------------|-------|--------|-------|-----------|--------------|----|

|    | VER                   | SION  |        |       | PART N    | UMBER        |    |

| 23 | 22                    | 21    | 20     | 19    | 18        | 17           | 16 |

|    |                       |       | PART N | UMBER |           |              |    |

| 15 | 14                    | 13    | 12     | 11    | 10        | 9            | 8  |

|    | PART N                | UMBER |        |       | MANUFACTU | RER IDENTITY |    |

| 7  | 6                     | 5     | 4      | 3     | 2         | 1            | 0  |

|    | MANUFACTURER IDENTITY |       |        |       |           |              |    |

## • VERSION[31:28]: Product Version Number

Set to 0x0.

#### • PART NUMBER[27:12]: Product Part Number

| Chip Name | Chip ID |

|-----------|---------|

| SAM4CM    | 0x05B34 |

# • MANUFACTURER IDENTITY[11:1]

Set to 0x01F.

# • Bit[0] Required by IEEE Std. 1149.1

Set to 0x1.

| Chip Name | JTAG ID Code |

|-----------|--------------|

| SAM4CM    | 0x05B3_403F  |

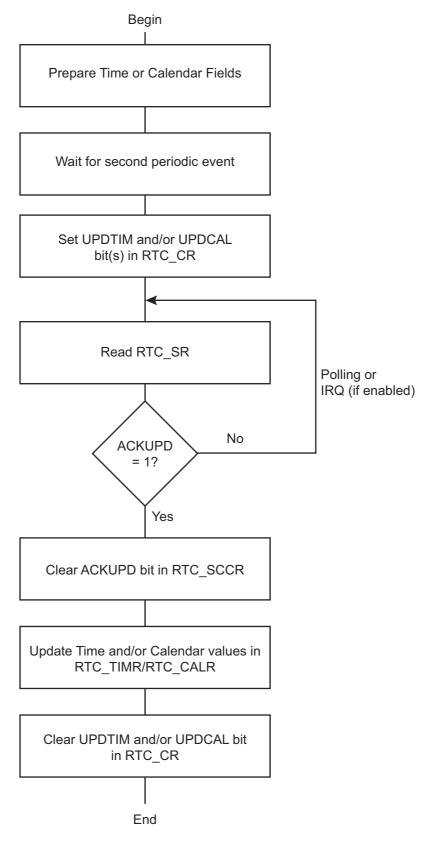

Figure 17-3. Gregorian and Persian Modes Update Sequence

To ease the comparison of the inherent crystal accuracy with the reference clock/signal during manufacturing, an internal prescaled 32.768 kHz clock derivative signal can be assigned to drive RTC output. To accommodate the measure, several clock frequencies can be selected among 1 Hz, 32 Hz, 64 Hz, 512 Hz.

The clock calibration correction drives the internal RTC counters but can also be observed in the RTC output when one of the following three frequencies 1 Hz, 32 Hz or 64 Hz is configured. The correction is not visible in the RTC output if 512 Hz frequency is configured.

In any event, this adjustment does not take into account the temperature variation.

The frequency drift (up to -200 ppm) due to temperature variation can be compensated using a reference time if the application can access such a reference. If a reference time cannot be used, a temperature sensor can be placed close to the crystal oscillator in order to get the operating temperature of the crystal oscillator. Once obtained, the temperature may be converted using a lookup table (describing the accuracy/temperature curve of the crystal oscillator used) and RTC\_MR configured accordingly. The calibration can be performed on-the-fly. This adjustment method is not based on a measurement of the crystal frequency/drift and therefore can be improved by means of the networking capability of the target application.

If no crystal frequency adjustment has been done during manufacturing, it is still possible to do it. In the case where a reference time of the day can be obtained through LAN/WAN network, it is possible to calculate the drift of the application crystal oscillator by comparing the values read on RTC Time Register (RTC\_TIMR) and programming the HIGHPPM and CORRECTION fields on RTC\_MR according to the difference measured between the reference time and those of RTC\_TIMR.

#### 17.5.8 Waveform Generation

Waveforms can be generated by the RTC in order to take advantage of the RTC inherent prescalers while the RTC is the only powered circuitry (Low-power mode of operation, Backup mode) or in any active mode. Going into Backup or Low-power operating modes does not affect the waveform generation outputs.

The RTC output (RTCOUT0) has a source driver selected among seven possibilities.

The first selection choice sticks the associated output at 0 (This is the reset value and it can be used at any time to disable the waveform generation).

Selection choices 1 to 4 respectively select 1 Hz, 32 Hz, 64 Hz and 512 Hz.

32 Hz or 64 Hz can drive, for example, a TN LCD backplane signal while 1 Hz can be used to drive a blinking character like ":" for basic time display (hour, minute) on TN LCDs.

Selection choice 5 provides a toggling signal when the RTC alarm is reached.

Selection choice 6 provides a copy of the alarm flag, so the associated output is set high (logical 1) when an alarm occurs and immediately cleared when software clears the alarm interrupt source.

Selection choice 7 provides a 1 Hz periodic high pulse of 15 µs duration that can be used to drive external devices for power consumption reduction or any other purpose.

PIO line associated to RTC output is automatically selecting these waveforms as soon as RTC\_MR corresponding fields OUT0 differ from 0.

# 22.5.2 EEFC Flash Command Register

| Name: El | EFC_FCR |

|----------|---------|

|----------|---------|

Address: 0x400E0A04 (0), 0x400E0C04 (1)

Access: Write-only

| 31 | 30 | 29 | 28  | 27 | 26 | 25 | 24 |

|----|----|----|-----|----|----|----|----|

|    |    |    | FKI | EY |    |    |    |

| 23 | 22 | 21 | 20  | 19 | 18 | 17 | 16 |

|    |    |    | FAF | RG |    |    |    |

| 15 | 14 | 13 | 12  | 11 | 10 | 9  | 8  |

|    |    |    | FAF | RG |    |    |    |

| 7  | 6  | 5  | 4   | 3  | 2  | 1  | 0  |

|    |    |    | FCI | MD |    |    |    |

# • FCMD: Flash Command

| Value | Name  | Description                         |

|-------|-------|-------------------------------------|

| 0x00  | GETD  | Get Flash descriptor                |

| 0x01  | WP    | Write page                          |

| 0x02  | WPL   | Write page and lock                 |

| 0x03  | EWP   | Erase page and write page           |

| 0x04  | EWPL  | Erase page and write page then lock |

| 0x05  | EA    | Erase all                           |

| 0x06  | EPL   | Erase plane                         |

| 0x07  | EPA   | Erase pages                         |

| 0x08  | SLB   | Set lock bit                        |

| 0x09  | CLB   | Clear lock bit                      |

| 0x0A  | GLB   | Get lock bit                        |

| 0x0B  | SGPB  | Set GPNVM bit                       |

| 0x0C  | CGPB  | Clear GPNVM bit                     |

| 0x0D  | GGPB  | Get GPNVM bit                       |

| 0x0E  | STUI  | Start read unique identifier        |

| 0x0F  | SPUI  | Stop read unique identifier         |

| 0x10  | GCALB | Get CALIB bit                       |

| 0x11  | ES    | Erase sector                        |

| 0x12  | WUS   | Write user signature                |

| 0x13  | EUS   | Erase user signature                |

| 0x14  | STUS  | Start read user signature           |

| 0x15  | SPUS  | Stop read user signature            |

## 28.5.2 Receive Counter Register

| Name:   | PERIPH_RCR |       |     |       |    |    |    |  |  |  |

|---------|------------|-------|-----|-------|----|----|----|--|--|--|

| Access: | Read/Write |       |     |       |    |    |    |  |  |  |

| 31      | 30         | 29    | 28  | 27    | 26 | 25 | 24 |  |  |  |

| -       | -          | _     |     |       | -  | -  | -  |  |  |  |

| 23      | 22         | 21    | 20  | 19    | 18 | 17 | 16 |  |  |  |

| -       | -          | _     | _   | -     | -  | _  | —  |  |  |  |

| 15      | 14         | 14 13 |     | 12 11 |    | 9  | 8  |  |  |  |

| RXCTR   |            |       |     |       |    |    |    |  |  |  |

| 7       | 6 5        |       | 4 3 |       | 2  | 1  | 0  |  |  |  |

|         | RXCTR      |       |     |       |    |    |    |  |  |  |

# • RXCTR: Receive Counter Register

RXCTR must be set to receive buffer size.

When a half-duplex peripheral is connected to the PDC, RXCTR = TXCTR.

0: Stops peripheral data transfer to the receiver.

1–65535: Starts peripheral data transfer if the corresponding channel is active.

# 29.4 Slow Clock

The Supply Controller embeds a slow clock generator that is supplied with the VDDBU power supply. As soon as VDDBU is supplied, both the 32.768 kHz crystal oscillator and the embedded 32 kHz (typical) RC oscillator are powered up, but only the RC oscillator is enabled. This allows the slow clock to be valid in a short time (about 100 µs).

The slow clock is generated either by the 32.768 kHz crystal oscillator or by the embedded 32 kHz (typical) RC oscillator.

The selection of the slow clock source is made via the XTALSEL bit in the Supply Controller Control Register (SUPC\_CR).

The OSCSEL bit of the Supply Controller Status Register (SUPC\_SR) and the OSCSEL bit of the PMC Status Register (PMC\_SR) report which oscillator is selected as the slow clock source. PMC\_SR.OSCSEL informs when the switch sequence initiated by a new value written in SUPC\_CR.XTALSEL is done.

#### 29.4.1 Embedded 32 kHz (typical) RC Oscillator

By default, the embedded 32 kHz (typical) RC oscillator is enabled and selected. The user has to take into account the possible drifts of this oscillator. More details are given in the section "DC Characteristics".

This oscillator is disabled by clearing the SUPC\_CR.XTALSEL.

#### 29.4.2 32.768 kHz Crystal Oscillator

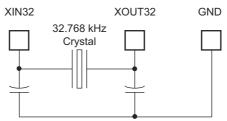

The Clock Generator integrates a low-power 32.768 kHz crystal oscillator. To use this oscillator, the XIN32 and XOUT32 pins must be connected to a 32.768 kHz crystal. Two external capacitors must be wired as shown in Figure 29-2. More details are given in the section "DC Characteristics".

Note that the user is not obliged to use the 32.768 kHz crystal oscillator and can use the 32 kHz (typical) RC oscillator instead.

#### Figure 29-2. Typical 32768 Crystal Oscillator Connection

The 32.768 kHz crystal oscillator provides a more accurate frequency than the 32 kHz (typical) RC oscillator.

To select the 32.768 kHz crystal oscillator as the source of the slow clock, the bit SUPC\_CR.XTALSEL must be set. This results in a sequence which enables the 32.768 kHz crystal oscillator and then disables the 32 kHz (typical) RC oscillator to save power. The switch of the slow clock source is glitch-free.

Reverting to the 32 kHz (typical) RC oscillator is only possible by shutting down the VDDBU power supply. If the user does not need the 32.768 kHz crystal oscillator, the XIN32 and XOUT32 pins can be left unconnected.

The user can also set the 32.768 kHz crystal oscillator in Bypass mode instead of connecting a crystal. In this case, the user must provide the external clock signal on XIN32. The input characteristics of the XIN32 pin are given in the section "Electrical Characteristics". To enter Bypass mode, the OSCBYPASS bit of the Supply Controller Mode Register (SUPC\_MR) must be set prior to setting SUPC\_CR.XTALSEL.

5. Check the main clock frequency:

This main clock frequency can be measured via CKGR\_MCFR.

Read CKGR\_MCFR until the MAINFRDY field is set, after which the user can read the MAINF field in CKGR\_MCFR by performing an additional read. This provides the number of main clock cycles that have been counted during a period of 16 slow clock cycles.

If MAINF = 0, switch the MAINCK to the 4/8/12 MHz RC Oscillator by clearing MOSCSEL in CKGR\_MOR. If MAINF  $\neq$  0, proceed to Step 6.

6. Set PLLx and Divider (if not required, proceed to Step 7.):

In the names PLLx, DIVx, MULx, LOCKx, PLLxCOUNT, and CKGR\_PLLxR, 'x' represents A or B.

All parameters needed to configure PLLx and the divider are located in CKGR\_PLLxR.

The DIVx field is used to control the divider itself. This parameter can be programmed between 0 and 127. Divider output is divider input divided by DIVx parameter. By default, DIVx field is cleared which means that the divider and PLLx are turned off.

The MULx field is the PLLx multiplier factor. This parameter can be programmed between 0 and 254. If MULx is cleared, PLLx will be turned off, otherwise the PLLx output frequency is PLLx input frequency multiplied by (MULx + 1).

The PLLxCOUNT field specifies the number of slow clock cycles before the LOCKx bit is set in the PMC\_SR after CKGR\_PLLxR has been written.

Once CKGR\_PLLxR has been written, the user must wait for the LOCKx bit to be set in the PMC\_SR. This can be done either by polling LOCKx in PMC\_SR or by waiting for the interrupt line to be raised if the associated interrupt source (LOCKx) has been enabled in PMC\_IER. All fields in CKGR\_PLLxR can be programmed in a single write operation. If at some stage one of the following parameters, MULx or DIVx is modified, the LOCKx bit goes low to indicate that PLLx is not yet ready. When PLLx is locked, LOCKx is set again. The user must wait for the LOCKx bit to be set before using the PLLx output clock.

7. Select the master clock and processor clock

The master clock and the processor clock are configurable via PMC\_MCKR.

The CSS field is used to select the clock source of the master clock and processor clock dividers. By default, the selected clock source is the main clock.

The PRES field is used to define the processor clock and master clock prescaler. The user can choose between different values (1, 2, 3, 4, 8, 16, 32, 64). Prescaler output is the selected clock source frequency divided by the PRES value.

Once the PMC\_MCKR has been written, the user must wait for the MCKRDY bit to be set in the PMC\_SR. This can be done either by polling MCKRDY in PMC\_SR or by waiting for the interrupt line to be raised if the associated interrupt source (MCKRDY) has been enabled in PMC\_IER. PMC\_MCKR must not be programmed in a single write operation. The programming sequence for PMC\_MCKR is as follows:

- If a new value for CSS field corresponds to PLL clock,

- Program the PRES field in PMC\_MCKR.

- Wait for the MCKRDY bit to be set in PMC\_SR.

- Program the CSS field in PMC\_MCKR.

- Wait for the MCKRDY bit to be set in PMC\_SR.

- If a new value for CSS field corresponds to main clock or slow clock,

- Program the CSS field in PMC\_MCKR.

- Wait for the MCKRDY bit to be set in the PMC\_SR.

- Program the PRES field in PMC\_MCKR.

# 30.18.8 PMC Clock Generator Main Clock Frequency Register

| Name:    | CKGR_MCFR  |    |        |       |    |    |          |  |  |  |

|----------|------------|----|--------|-------|----|----|----------|--|--|--|

| Address: | 0x400E0424 |    |        |       |    |    |          |  |  |  |

| Access:  | Read/Write |    |        |       |    |    |          |  |  |  |

| 31       | 30         | 29 | 28 27  |       | 26 | 25 | 24       |  |  |  |

| _        | _          | _  | _      | _     | _  | _  | _        |  |  |  |

|          |            |    | -      | -     | 18 |    |          |  |  |  |

| 23       | 22         | 21 | 20     | 20 19 |    | 17 | 16       |  |  |  |

| -        | -          | -  | RCMEAS | -     | -  | -  | MAINFRDY |  |  |  |

| 15       | 14         | 13 | 12     | 11    | 10 | 9  | 8        |  |  |  |

| MAINF    |            |    |        |       |    |    |          |  |  |  |

| 7        | 6          | 5  | 4      | 3     | 2  | 1  | 0        |  |  |  |

| MAINF    |            |    |        |       |    |    |          |  |  |  |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

#### • MAINF: Main Clock Frequency

Gives the number of main clock cycleswithin 16 slow clock periods. To calculate the frequency of the measured clock:  $f_{MAINCK} = (MAINF \times f_{SLCK}) / 16$

where frequency is in MHz.

#### • MAINFRDY: Main Clock Frequency Measure Ready

0: MAINF value is not valid or the measured oscillator is disabled or a measure has just been started by means of RCMEAS.

1: The measured oscillator has been enabled previously and MAINF value is available.

Note: To ensure that a correct value is read on the MAINF field, the MAINFRDY flag must be read at 1 then another read access must be performed on the register to get a stable value on the MAINF field.

#### • RCMEAS: Restart Main Clock Source Frequency Measure (write-only)

0: No effect.

1: Restarts measuring of the frequency of the main clock source. MAINF will carry the new frequency as soon as a low to high transition occurs on the MAINFRDY flag.

The measure is performed on the main frequency (i.e. not limited to RC oscillator only), but if the main clock frequency source is the 3 to 20 MHz crystal oscillator, the restart of measuring is not needed because of the well known stability of crystal oscillators.

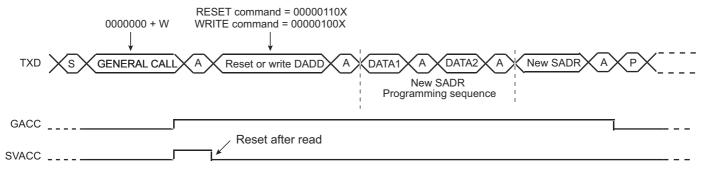

#### General Call

The general call is performed in order to change the address of the slave.

If a GENERAL CALL is detected, GACC is set.

After the detection of GENERAL CALL, it is up to the programmer to decode the commands which come afterwards.

In case of a WRITE command, the programmer has to decode the programming sequence and program a new SADR if the programming sequence matches.

Figure 34-27 describes the GENERAL CALL access.

#### Figure 34-27. Master Performs a General Call

Note: This method allows the user to create a personal programming sequence by choosing the programming bytes and the number of them. The programming sequence has to be provided to the master.

# 36. Universal Synchronous Asynchronous Receiver Transceiver (USART)

# 36.1 Description

The Universal Synchronous Asynchronous Receiver Transceiver (USART) provides one full duplex universal synchronous asynchronous serial link. Data frame format is widely programmable (data length, parity, number of stop bits) to support a maximum of standards. The receiver implements parity error, framing error and overrun error detection. The receiver time-out enables handling variable-length frames and the transmitter timeguard facilitates communications with slow remote devices. Multidrop communications are also supported through address bit handling in reception and transmission.

The USART features three test modes: Remote loopback, Local loopback and Automatic echo.

The USART supports specific operating modes providing interfaces on RS485, and SPI buses, with ISO7816 T = 0 or T = 1 smart card slots and infrared transceivers. The hardware handshaking feature enables an out-of-band flow control by automatic management of the pins RTS and CTS.

The USART supports the connection to the Peripheral DMA Controller, which enables data transfers to the transmitter and from the receiver. The PDC provides chained buffer management without any intervention of the processor.

# 36.2 Embedded Characteristics

- Programmable Baud Rate Generator

- 5- to 9-bit Full-duplex Synchronous or Asynchronous Serial Communications

- 1, 1.5 or 2 Stop Bits in Asynchronous Mode or 1 or 2 Stop Bits in Synchronous Mode

- Parity Generation and Error Detection

- Framing Error Detection, Overrun Error Detection

- Digital Filter on Receive Line

- MSB- or LSB-first

- Optional Break Generation and Detection

- By 8 or by 16 Over-sampling Receiver Frequency

- Optional Hardware Handshaking RTS-CTS

- Receiver Time-out and Transmitter Timeguard

- Optional Multidrop Mode with Address Generation and Detection

- RS485 with Driver Control Signal

- ISO7816, T = 0 or T = 1 Protocols for Interfacing with Smart Cards

- NACK Handling, Error Counter with Repetition and Iteration Limit

- IrDA Modulation and Demodulation

- Communication at up to 115.2 kbit/s

- SPI Mode

- Master or Slave

- Serial Clock Programmable Phase and Polarity

- SPI Serial Clock (SCK) Frequency up to f<sub>peripheral clock</sub>/6

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

- Supports Connection of:

- Two Peripheral DMA Controller Channels (PDC)

# 38.7.12 PWM Channel Counter Register

Name: PWM\_CCNT[0..3]

# Address: 0x4800820C [0], 0x4800822C [1], 0x4800824C [2], 0x4800826C [3]

Access: Read-only

| 31  | 30 | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |

|-----|----|----|----|----|----|----|----|--|--|--|

| CNT |    |    |    |    |    |    |    |  |  |  |

| 23  | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |

| CNT |    |    |    |    |    |    |    |  |  |  |

| 15  | 14 | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |

| CNT |    |    |    |    |    |    |    |  |  |  |

| 7   | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

| CNT |    |    |    |    |    |    |    |  |  |  |

#### CNT: Channel Counter Register

Internal counter value. This register is reset when:

- the channel is enabled (writing CHIDx in the PWM\_ENA register).

- the counter reaches CPRD value defined in the PWM\_CPRDx register if the waveform is left aligned.

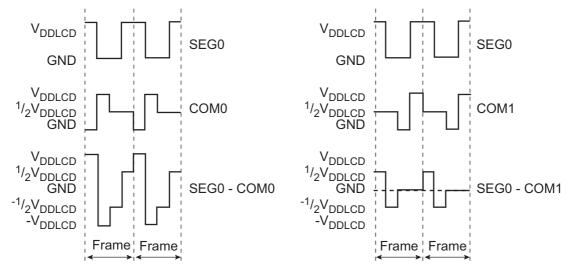

Figure 39-3. Driving an LCD with One Common Terminal

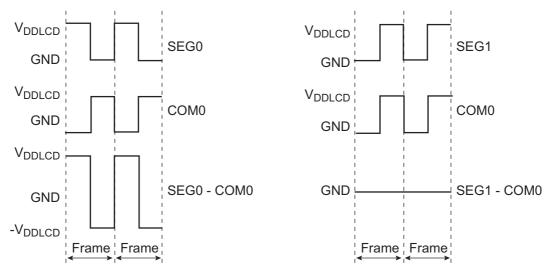

#### 39.6.2.2 1/2 Duty and 1/2 Bias

For an LCD with two common terminals (1/2 duty) a more complex waveform must be used to control segments individually. Although 1/3 bias can be selected, 1/2 bias is most common for these displays. In the waveform shown in Figure 39-4, SEG0 - COM0 is the voltage across a segment that is on, and SEG0 - COM1 is the voltage across a segment that is off.

#### 39.6.2.3 1/3 Duty and 1/3 Bias

1/3 bias is usually recommended for an LCD with three common terminals (1/3 duty). In the waveform shown in Figure 39-5, SEG0 - COM0 is the voltage across a segment that is on and SEG0 - COM1 is the voltage across a segment that is off.

# 43. Integrity Check Monitor (ICM)

# 43.1 Description

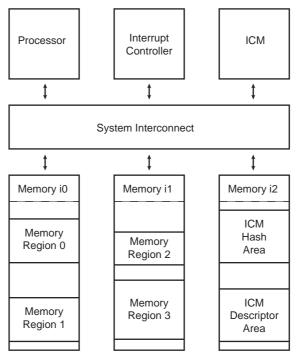

The Integrity Check Monitor (ICM) is a DMA controller that performs hash calculation over multiple memory regions through the use of transfer descriptors located in memory (ICM Descriptor Area). The Hash function is based on the Secure Hash Algorithm (SHA). The ICM controller integrates two modes of operation. The first one is used to hash a list of memory regions and save the digests to memory (ICM Hash Area). The second operation mode is an active monitoring of the memory. In that mode, the hash function is evaluated and compared to the digest located at a predefined memory address (ICM Hash Area). If a mismatch occurs, an interrupt is raised. See Figure 43-1 for an example of four-region monitoring. Hash and Descriptor areas are located in Memory instance i2, and the four regions are split in memory instances i0 and i1.

#### Figure 43-1. Four-region Monitoring Example

The ICM SHA engine is compliant with the American FIPS (Federal Information Processing Standard) Publication 180-2 specification.

The following terms are concise definitions of the ICM concepts used throughout this document:

- Region—a partition of instruction or data memory space

- Region Descriptor—a data structure stored in memory, defining region attributes

- Region Attributes—region start address, region size, region SHA engine processing mode, Write Back or Compare function mode

- Context Registers—a set of ICM non-memory-mapped, internal registers which are automatically loaded, containing the attributes of the region being processed

- Main List—a list of region descriptors. Each element associates the start address of a region with a set of attributes.

- Secondary List—a linked list defined on a per region basis that describes the memory layout of the region (when the region is non-contiguous)

- Hash Area—predefined memory space where the region hash results (digest) are stored

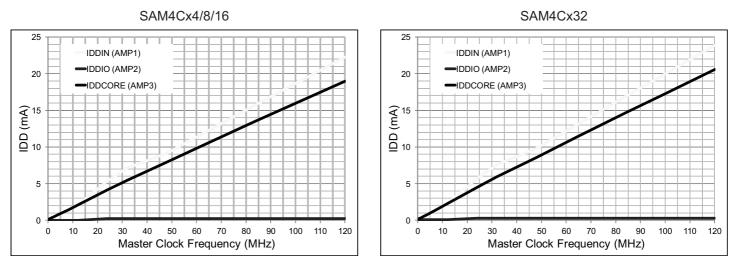

Figure 46-28. Typical Current Consumption in Active Mode (Test Setup 2)

#### 46.7.4.3 Test Setup 3: CoreMark

- CoreMark on Core 0 (CM4P0) running out of Flash in 128-bit or 64-bit Access mode with and without Cache Enabled. Cache is enabled above 0 WS.

- CoreMark on Core 1 (CM4P1) running out of SRAM1 (Code) / SRAM2 (Data)

|                | 128-bit Flash Access |                  |                    |                  |                  |                    | 64-bit Flash Access |                  |                    |                  |                  |                    |      |

|----------------|----------------------|------------------|--------------------|------------------|------------------|--------------------|---------------------|------------------|--------------------|------------------|------------------|--------------------|------|

|                | Cache Enabled        |                  |                    | Cache Disabled   |                  | Cache Enabled      |                     |                  | Cache Disabled     |                  |                  |                    |      |

| Clock<br>(MHz) | IDD_IN<br>(AMP1)     | IDD_I0<br>(AMP2) | IDD_CORE<br>(AMP3) | IDD_IN<br>(AMP1) | IDD_I0<br>(AMP2) | IDD_CORE<br>(AMP3) | IDD_IN<br>(AMP1)    | IDD_I0<br>(AMP2) | IDD_CORE<br>(AMP3) | IDD_IN<br>(AMP1) | IDD_I0<br>(AMP2) | IDD_CORE<br>(AMP3) | Unit |

| 120            | 31.3                 | 0.28             | 28.0               | 34.2             | 1.9              | 30.9               | 31.3                | 0.28             | 28.0               | 30.7             | 1.8              | 27.4               |      |

| 100            | 26.4                 | 0.28             | 23.6               | 29.8             | 1.8              | 27.1               | 26.4                | 0.28             | 23.6               | 27.0             | 1.8              | 24.3               |      |

| 84             | 22.4                 | 0.28             | 20.1               | 26.3             | 1.7              | 24.0               | 22.4                | 0.28             | 20.1               | 24.1             | 1.7              | 21.8               |      |

| 64             | 17.2                 | 0.28             | 15.6               | 21.0             | 1.5              | 19.3               | 17.2                | 0.28             | 15.6               | 19.6             | 1.6              | 18.0               |      |

| 48             | 13.1                 | 0.28             | 11.8               | 16.6             | 1.4              | 15.3               | 13.1                | 0.28             | 11.8               | 16.0             | 1.6              | 14.7               |      |

| 32             | 9.8                  | 0.28             | 8.1                | 12.6             | 1.2              | 10.9               | 9.8                 | 0.28             | 8.1                | 12.3             | 1.4              | 10.6               |      |

| 24             | 7.4                  | 0.28             | 6.2                | 9.5              | 1.1              | 8.3                | 7.4                 | 0.28             | 6.2                | 9.4              | 1.3              | 8.1                | mA   |

| 12             | 3.1                  | 0.11             | 3.1                | 4.2              | 0.88             | 4.2                | 3.1                 | 0.11             | 3.1                | 4.2              | 1.2              | 4.2                | ma   |

| 8              | 2.1                  | 0.11             | 2.1                | 2.8              | 0.78             | 2.8                | 2.1                 | 0.11             | 2.1                | 2.8              | 1.0              | 2.8                |      |

| 4              | 1.1                  | 0.11             | 1.1                | 1.5              | 0.58             | 1.5                | 1.1                 | 0.11             | 1.1                | 1.5              | 0.9              | 1.5                |      |

| 2              | 0.63                 | 0.11             | 0.61               | 0.82             | 0.40             | 0.81               | 0.63                | 0.11             | 0.61               | 0.82             | 0.66             | 0.81               |      |

| 1              | 0.38                 | 0.11             | 0.37               | 0.47             | 0.26             | 0.46               | 0.38                | 0.11             | 0.37               | 0.47             | 0.38             | 0.46               |      |

| 0.5            | 0.25                 | 0.11             | 0.24               | 0.30             | 0.18             | 0.29               | 0.25                | 0.11             | 0.24               | 0.30             | 0.23             | 0.29               |      |

| 0.25           | 0.14                 | 0.11             | 0.13               | 0.16             | 0.12             | 0.15               | 0.14                | 0.11             | 0.13               | 0.16             | 0.14             | 0.15               |      |

Table 46-66. SAM4CM4/8/16 Test Setup 3 Current Consumption