#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M4F                                                         |

| Core Size                  | 32-Bit Dual-Core                                                            |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                             |

| Number of I/O              | 52                                                                          |

| Program Memory Size        | 1MB (1M x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                |

| Data Converters            | A/D 6x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-LQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4cmp16cb-aur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Return

This occurs when the exception handler is completed, and:

- There is no pending exception with sufficient priority to be serviced

- The completed exception handler was not handling a late-arriving exception.

The processor pops the stack and restores the processor state to the state it had before the interrupt occurred. See "Exception Return" for more information.

#### Tail-chaining

This mechanism speeds up exception servicing. On completion of an exception handler, if there is a pending exception that meets the requirements for exception entry, the stack pop is skipped and control transfers to the new exception handler.

#### Late-arriving

This mechanism speeds up preemption. If a higher priority exception occurs during state saving for a previous exception, the processor switches to handle the higher priority exception and initiates the vector fetch for that exception. State saving is not affected by late arrival because the state saved is the same for both exceptions. Therefore the state saving continues uninterrupted. The processor can accept a late arriving exception until the first instruction of the exception handler of the original exception enters the execute stage of the processor. On return from the exception handler of the late-arriving exception, the normal tail-chaining rules apply.

#### **Exception Entry**

An Exception entry occurs when there is a pending exception with sufficient priority and either the processor is in Thread mode, or the new exception is of a higher priority than the exception being handled, in which case the new exception preempts the original exception.

When one exception preempts another, the exceptions are nested.

Sufficient priority means that the exception has more priority than any limits set by the mask registers, see "Exception Mask Registers". An exception with less priority than this is pending but is not handled by the processor.

When the processor takes an exception, unless the exception is a tail-chained or a late-arriving exception, the processor pushes information onto the current stack. This operation is referred as *stacking* and the structure of eight data words is referred to as *stack frame*.

When using floating-point routines, the Cortex-M4 processor automatically stacks the architected floating-point state on exception entry. Figure 12-7 shows the Cortex-M4 stack frame layout when floating-point state is preserved on the stack as the result of an interrupt or an exception.

Note: Where stack space for floating-point state is not allocated, the stack frame is the same as that of ARMv7-M implementations without an FPU. Figure 12-7 shows this stack frame also.

#### 12.6.9.1 BFC and BFI

Bit Field Clear and Bit Field Insert.

Syntax

BFC{cond} Rd, #lsb, #width

BFI{cond} Rd, Rn, #lsb, #width

where:

cond is an optional condition code, see "Conditional Execution".

Rd is the destination register.

Rn is the source register.

lsb is the position of the least significant bit of the bitfield. *Isb* must be in the range 0 to 31.

width is the width of the bitfield and must be in the range 1 to 32-*lsb*.

Operation

BFC clears a bitfield in a register. It clears *width* bits in *Rd*, starting at the low bit position *lsb*. Other bits in *Rd* are unchanged.

BFI copies a bitfield into one register from another register. It replaces *width* bits in *Rd* starting at the low bit position *lsb*, with *width* bits from *Rn* starting at bit[0]. Other bits in *Rd* are unchanged.

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not affect the flags.

#### Examples

| BFC | R4, #8, | #12     | ; | Clear bit 8 to bit 19 (12 bits) of R4 to 0   |

|-----|---------|---------|---|----------------------------------------------|

| BFI | R9, R2, | #8, #12 | ; | Replace bit 8 to bit 19 (12 bits) of R9 with |

|     |         |         | ; | bit 0 to bit 11 from R2.                     |

#### 12.11.2.5 MPU Region Attribute and Size Register

| Name:   | MPU_RASR   | L_RASR |     |      |    |    |        |  |  |

|---------|------------|--------|-----|------|----|----|--------|--|--|

| Access: | Read/Write |        |     |      |    |    |        |  |  |

| 31      | 30         | 29     | 28  | 27   | 26 | 25 | 24     |  |  |

| —       | —          | —      | XN  | —    |    | AP |        |  |  |

| 23      | 22         | 21     | 20  | 19   | 18 | 17 | 16     |  |  |

| _       | —          |        | TEX |      | S  | С  | В      |  |  |

| 15      | 14         | 13     | 12  | 11   | 10 | 9  | 8      |  |  |

|         |            |        | SI  | RD   |    |    |        |  |  |

| 7       | 6          | 5      | 4   | 3    | 2  | 1  | 0      |  |  |

| _       | -          |        |     | SIZE |    |    | ENABLE |  |  |

The MPU\_RASR defines the region size and memory attributes of the MPU region specified by the MPU\_RNR, and enables that region and any subregions.

MPU\_RASR is accessible using word or halfword accesses:

- The most significant halfword holds the region attributes.

- The least significant halfword holds the region size, and the region and subregion enable bits.

#### • XN: Instruction Access Disable

- 0: Instruction fetches enabled.

- 1: Instruction fetches disabled.

#### • AP: Access Permission

See Table 12-39.

## • TEX, C, B: Memory Access Attributes

See Table 12-37.

#### • S: Shareable

See Table 12-37.

## • SRD: Subregion Disable

For each bit in this field:

- 0: Corresponding subregion is enabled.

- 1: Corresponding subregion is disabled.

See "Subregions" for more information.

Region sizes of 128 bytes and less do not support subregions. When writing the attributes for such a region, write the SRD field as 0x00.

## 18.5.2 Watchdog Timer Mode Register

| Name:<br>Address: | WDT_MR<br>0x400E1454 |           |          |          |    |    |    |

|-------------------|----------------------|-----------|----------|----------|----|----|----|

| Access:           | Read/Write Onc       | e         |          |          |    |    |    |

| 31                | 30                   | 29        | 28       | 27       | 26 | 25 | 24 |

| _                 | -                    | WDIDLEHLT | WDDBGHLT |          | WI | DD |    |

| 23                | 22                   | 21        | 20<br>WE | 19<br>DD | 18 | 17 | 16 |

| 15                | 14                   | 13        | 12       | 11       | 10 | 9  | 8  |

| WDDIS             | WDRPROC              | WDRSTEN   | WDFIEN   |          | W  | DV |    |

| 7                 | 6                    | 5         | 4<br>WE  | 3        | 2  | 1  | 0  |

|                   |                      |           | VVL      | Jv       |    |    |    |

Note: The first write access prevents any further modification of the value of this register. Read accesses remain possible.

Note: The WDD and WDV values must not be modified within three slow clock periods following a restart of the watchdog performed by a write access in WDT\_CR. Any modification will cause the watchdog to trigger an end of period earlier than expected.

#### • WDV: Watchdog Counter Value

Defines the value loaded in the 12-bit watchdog counter.

#### • WDFIEN: Watchdog Fault Interrupt Enable

- 0: A watchdog fault (underflow or error) has no effect on interrupt.

- 1: A watchdog fault (underflow or error) asserts interrupt.

## • WDRSTEN: Watchdog Reset Enable

- 0: A watchdog fault (underflow or error) has no effect on the resets.

- 1: A watchdog fault (underflow or error) triggers a watchdog reset.

## • WDRPROC: Watchdog Reset Processor

- 0: If WDRSTEN is 1, a watchdog fault (underflow or error) activates all resets.

- 1: If WDRSTEN is 1, a watchdog fault (underflow or error) activates the processor reset.

## • WDDIS: Watchdog Disable

- 0: Enables the Watchdog Timer.

- 1: Disables the Watchdog Timer.

#### • WDD: Watchdog Delta Value

Defines the permitted range for reloading the Watchdog Timer.

If the Watchdog Timer value is less than or equal to WDD, setting bit WDT\_CR.WDRSTT restarts the timer.

If the Watchdog Timer value is greater than WDD, setting bit WDT\_CR.WDRSTT causes a watchdog error.

The following registers can be write-protected:

- "SMC Setup Register"

- "SMC Pulse Register"

- "SMC Cycle Register"

- "SMC MODE Register"

### 27.9.6 Coding Timing Parameters

All timing parameters are defined for one chip select and are grouped together in one SMC\_REGISTER according to their type.

The SMC\_SETUP register groups the definition of all setup parameters:

NRD\_SETUP, NCS\_RD\_SETUP, NWE\_SETUP, NCS\_WR\_SETUP

The SMC\_PULSE register groups the definition of all pulse parameters:

• NRD\_PULSE, NCS\_RD\_PULSE, NWE\_PULSE, NCS\_WR\_PULSE

The SMC\_CYCLE register groups the definition of all cycle parameters:

NRD\_CYCLE, NWE\_CYCLE

Table 27-4 shows how the timing parameters are coded and their permitted range.

|             |                |                               | nge         |                 |

|-------------|----------------|-------------------------------|-------------|-----------------|

| Coded Value | Number of Bits | Effective Value               | Coded Value | Effective Value |

| setup [5:0] | 6              | 128 x setup[5] + setup[4:0]   | 0 ≤ ≤ 31    | 0 ≤ ≤ 128+31    |

| pulse [6:0] | 7              | 256 x pulse[6] + pulse[5:0]   | 0 ≤ ≤ 63    | 0 ≤ ≤ 256+63    |

|             |                |                               |             | 0 ≤ ≤ 256+127   |

| cycle [8:0] | 9              | 256 x cycle[8:7] + cycle[6:0] | 0 ≤ ≤ 127   | 0 ≤ ≤ 512+127   |

|             |                |                               |             | 0 ≤ ≤ 768+127   |

#### Table 27-4. **Coding and Range of Timing Parameters**

#### 27.9.7 Reset Values of Timing Parameters

Table 27-5 gives the default value of timing parameters at reset.

|            |             | ,                                                                                    |

|------------|-------------|--------------------------------------------------------------------------------------|

| Register   | Reset Value | Definition                                                                           |

| SMC_SETUP  | 0x01010101  | All setup timings are set to 1.                                                      |

| SMC_PULSE  | 0x01010101  | All pulse timings are set to 1.                                                      |

| SMC_CYCLE  | 0x00030003  | The read and write operations last 3 Master Clock cycles and provide one hold cycle. |

| WRITE_MODE | 1           | Write is controlled with NWE.                                                        |

| READ_MODE  | 1           | Read is controlled with NRD.                                                         |

Table 27-5. **Reset Values of Timing Parameters**

#### 27.9.8 Usage Restriction

The SMC does not check the validity of the user-programmed parameters. If the sum of SETUP and PULSE parameters is larger than the corresponding CYCLE parameter, this leads to unpredictable behavior of the SMC.

## 30.18.17PMC Fast Startup Mode Register

| Name:<br>Address: | PMC_FSMR<br>0x400E0470 |        |        |        |        |       |       |

|-------------------|------------------------|--------|--------|--------|--------|-------|-------|

| Access:           | Read/Write             |        |        |        |        |       |       |

| 31                | 30                     | 29     | 28     | 27     | 26     | 25    | 24    |

| -                 | -                      | —      | —      | —      | —      | _     | —     |

| 23                | 22                     | 21     | 20     | 19     | 18     | 17    | 16    |

| _                 | FL                     | PM     | LPM    | -      | -      | RTCAL | RTTAL |

| 15                | 14                     | 13     | 12     | 11     | 10     | 9     | 8     |

| FSTT15            | FSTT14                 | FSTT13 | FSTT12 | FSTT11 | FSTT10 | FSTT9 | FSTT8 |

| 7                 | 6                      | 5      | 4      | 3      | 2      | 1     | 0     |

| FSTT7             | FSTT6                  | FSTT5  | FSTT4  | FSTT3  | FSTT2  | FSTT1 | FSTT0 |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

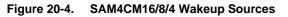

## • FSTT0–FSTT15: Fast Startup Input Enable 0 to 15

0: The corresponding wake-up input has no effect on the PMC.

1: The corresponding wake-up input enables a fast restart signal to the PMC.

#### • RTTAL: RTT Alarm Enable

0: The RTT alarm has no effect on the PMC.

1: The RTT alarm enables a fast restart signal to the PMC.

## • RTCAL: RTC Alarm Enable

0: The RTC alarm has no effect on the PMC.

1: The RTC alarm enables a fast restart signal to the PMC.

#### • LPM: Low-power Mode

0: The WaitForInterrupt (WFI) or the WaitForEvent (WFE) instruction of the processor makes the processor enter Sleep mode.

1: The WaitForEvent (WFE) instruction of the processor makes the system to enter Wait mode.

## • FLPM: Flash Low-power Mode

| Value | Name                 | Description                                                   |

|-------|----------------------|---------------------------------------------------------------|

| 0     | FLASH_STANDBY        | Flash is in Standby Mode when system enters Wait Mode         |

| 1     | FLASH_DEEP_POWERDOWN | Flash is in Deep-power-down mode when system enters Wait Mode |

| 2     | FLASH_IDLE           | Idle mode                                                     |

## 32.6.6 PIO Output Status Register

## Address: 0x400E0E18 (PIOA), 0x400E1018 (PIOB), 0x4800C018 (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Output Status

0: The I/O line is a pure input.

1: The I/O line is enabled in output.

## 33.8.4 SPI Transmit Data Register

| Name:    | SPI_TDR                        |    |    |    |    |    |          |  |  |  |

|----------|--------------------------------|----|----|----|----|----|----------|--|--|--|

| Address: | 0x4000800C (0), 0x4800000C (1) |    |    |    |    |    |          |  |  |  |

| Access:  | Write-only                     |    |    |    |    |    |          |  |  |  |

| 31       | 30                             | 29 | 28 | 27 | 26 | 25 | 24       |  |  |  |

| _        | _                              | —  | _  | _  | _  | _  | LASTXFER |  |  |  |

| 23       | 22                             | 21 | 20 | 19 | 18 | 17 | 16       |  |  |  |

| _        | -                              | —  | -  |    | PC | S  |          |  |  |  |

| 15       | 14                             | 13 | 12 | 11 | 10 | 9  | 8        |  |  |  |

|          |                                |    | Т  | D  |    |    |          |  |  |  |

| 7        | 6                              | 5  | 4  | 3  | 2  | 1  | 0        |  |  |  |

|          |                                |    | Т  | D  |    |    |          |  |  |  |

#### • TD: Transmit Data

Data to be transmitted by the SPI Interface is stored in this register. Information to be transmitted must be written to the transmit data register in a right-justified format.

## • PCS: Peripheral Chip Select

This field is only used if variable peripheral select is active (PS = 1).

If SPI\_MR.PCSDEC = 0:

PCS = xxx0 NPCS[3:0] = 1110

PCS = xx01 NPCS[3:0] = 1101

PCS = x011 NPCS[3:0] = 1011

PCS = 0111 NPCS[3:0] = 0111

PCS = 1111 forbidden (no peripheral is selected)

(x = don't care) If SPI

If SPI

MR.PCSDEC = 1:

NPCS[3:0] output signals = PCS.

#### • LASTXFER: Last Transfer

0: No effect

1: The current NPCS is de-asserted after the transfer of the character written in TD. When SPI\_CSRx.CSAAT is set, the communication with the current serial peripheral can be closed by raising the corresponding NPCS line as soon as TD transfer is completed.

This field is only used if variable peripheral select is active (SPI\_MR.PS = 1).

#### Figure 36-25. Break Transmission

| Baud Rate<br>Clock | Л | Л          | <b></b>    | IJ | $\Box$ |    |    |    |    | Л             |             | hunnun             | huuuuuuu     |   |

|--------------------|---|------------|------------|----|--------|----|----|----|----|---------------|-------------|--------------------|--------------|---|

| TXD                |   | ĺ          |            | Γ  |        |    |    |    |    |               |             |                    |              | - |

|                    |   | art<br>Bit | D0 D1      | D2 | D3     | D4 | D5 | D6 | D7 | Parity<br>Bit | Stop<br>Bit | Break Transmission | End of Break |   |

|                    |   |            | STTBRK = 1 |    |        |    |    |    |    |               |             | STPBRK = 1         |              |   |

| Write<br>US_CR     |   |            |            |    |        | Î  |    |    |    |               |             | Î                  |              | _ |

| _                  |   |            |            |    |        |    |    |    |    |               |             |                    |              |   |

| TXRDY              |   | Ì          |            |    |        | ]  |    |    |    |               |             |                    |              | _ |

|                    |   |            |            |    |        | _  |    |    |    |               |             |                    |              |   |

| TXEMPTY            |   |            |            |    |        |    |    |    |    |               |             |                    |              |   |

#### 36.6.3.14 Receive Break

The receiver detects a break condition when all data, parity and stop bits are low. This corresponds to detecting a framing error with data to 0x00, but FRAME remains low.

When the low stop bit is detected, the receiver asserts the RXBRK bit in US\_CSR. This bit may be cleared by writing a 1 to the RSTSTA bit in the US\_CR.

An end of receive break is detected by a high level for at least 2/16 of a bit period in Asynchronous operating mode or one sample at high level in Synchronous operating mode. The end of break detection also asserts the RXBRK bit.

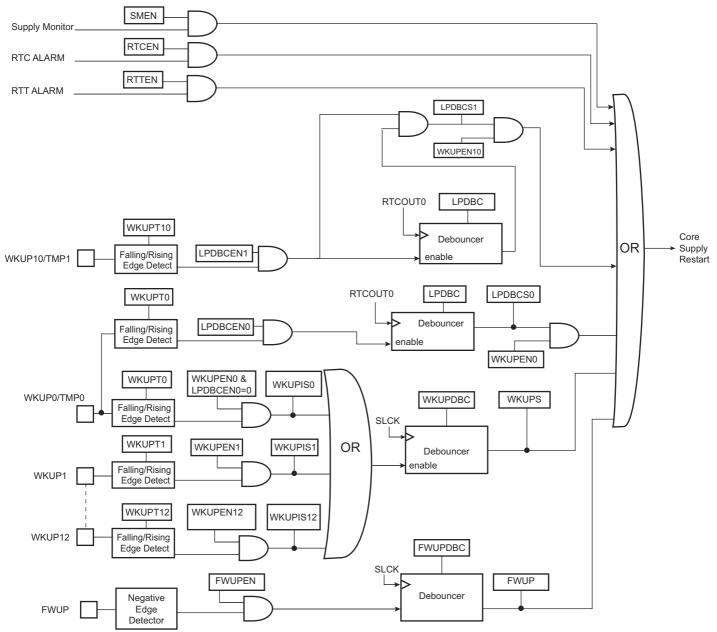

#### 36.6.3.15 Hardware Handshaking

The USART features a hardware handshaking out-of-band flow control. The RTS and CTS pins are used to connect with the remote device, as shown in Figure 36-26.

| USART |   | Remote<br>Device |

|-------|---|------------------|

| TXD   |   | RXD              |

| RXD   | • | TXD              |

| CTS   | • | RTS              |

| RTS   |   | CTS              |

Setting the USART to operate with hardware handshaking is performed by writing the USART\_MODE field in US\_MR to the value 0x2.

The USART behavior when hardware handshaking is enabled is the same as the behavior in standard Synchronous or Asynchronous mode, except that the receiver drives the RTS pin as described below and the level on the CTS pin modifies the behavior of the transmitter as described below. Using this mode requires using the PDC channel for reception. The transmitter can handle hardware handshaking in any case.

Figure 36-27 shows how the receiver operates if hardware handshaking is enabled. The RTS pin is driven high if the receiver is disabled or if the status RXBUFF (Receive Buffer Full) coming from the PDC channel is high. Normally, the remote device does not start transmitting while its CTS pin (driven by RTS) is high. As soon as the receiver is enabled, the RTS falls, indicating to the remote device that it can start transmitting. Defining a new buffer in the PDC clears the status bit RXBUFF and, as a result, asserts the pin RTS low.

- Serial Clock (SCK): This control line is driven by the master and regulates the flow of the data bits. The master may transmit data at a variety of baud rates. The SCK line cycles once for each bit that is transmitted.

- Slave Select (NSS): This control line allows the master to select or deselect the slave.

#### 36.6.7.1 Modes of Operation

The USART can operate in SPI Master mode or in SPI Slave mode.

Operation in SPI Master mode is programmed by writing 0xE to the USART\_MODE field in US\_MR. In this case the SPI lines must be connected as described below:

- The MOSI line is driven by the output pin TXD

- The MISO line drives the input pin RXD

- The SCK line is driven by the output pin SCK

- The NSS line is driven by the output pin RTS

Operation in SPI Slave mode is programmed by writing to 0xF the USART\_MODE field in US\_MR. In this case the SPI lines must be connected as described below:

- The MOSI line drives the input pin RXD

- The MISO line is driven by the output pin TXD

- The SCK line drives the input pin SCK

- The NSS line drives the input pin CTS

In order to avoid unpredictable behavior, any change of the SPI mode must be followed by a software reset of the transmitter and of the receiver (except the initial configuration after a hardware reset). (See Section 36.6.7.4 "Receiver and Transmitter Control").

#### 36.6.7.2 Baud Rate

In SPI mode, the baud rate generator operates in the same way as in USART Synchronous mode. See Section 36.6.1.3 "Baud Rate in Synchronous Mode or SPI Mode". However, there are some restrictions:

In SPI Master mode:

- The external clock SCK must not be selected (USCLKS ≠ 0x3), and the bit CLKO must be set to 1 in the US\_MR, in order to generate correctly the serial clock on the SCK pin.

- To obtain correct behavior of the receiver and the transmitter, the value programmed in CD must be superior or equal to 6.

- If the divided peripheral clock is selected, the value programmed in CD must be even to ensure a 50:50 mark/space ratio on the SCK pin, this value can be odd if the peripheral clock is selected.

In SPI Slave mode:

- The external clock (SCK) selection is forced regardless of the value of the USCLKS field in the US\_MR. Likewise, the value written in US\_BRGR has no effect, because the clock is provided directly by the signal on the USART SCK pin.

- To obtain correct behavior of the receiver and the transmitter, the external clock (SCK) frequency must be at least 6 times lower than the system clock.

## 36.6.7.3 Data Transfer

Up to nine data bits are successively shifted out on the TXD pin at each rising or falling edge (depending of CPOL and CPHA) of the programmed serial clock. There is no Start bit, no Parity bit and no Stop bit.

The number of data bits is selected by the CHRL field and the MODE 9 bit in the US\_MR. The nine bits are selected by setting the MODE 9 bit regardless of the CHRL field. The MSB data bit is always sent first in SPI mode (Master or Slave).

#### Table 37-4. I/O Lines (Continued)

| TC1 | TIOB3 | PB25         | ۸        |

|-----|-------|--------------|----------|

|     | ПОВЗ  | FD20         | A        |

| TC1 | TIOB4 | PA16         | В        |

| TO  | TIODE | <b>B</b> A00 | <b>D</b> |

| TC1 | TIOB5 | PA20         | В        |

#### 37.5.2 Power Management

The TC is clocked through the Power Management Controller (PMC), thus the programmer must first configure the PMC to enable the Timer Counter clock of each channel.

#### 37.5.3 Interrupt Sources

The TC has an interrupt line per channel connected to the interrupt controller. Handling the TC interrupt requires programming the interrupt controller before configuring the TC.

Table 37-5. Peripheral IDs

| Instance | ID |

|----------|----|

| TC0      | 23 |

| TC1      | 24 |

#### 37.6 Functional Description

#### 37.6.1 Description

All channels of the Timer Counter are independent and identical in operation except when the QDEC is enabled. The registers for channel programming are listed in Table 37-6 "Register Mapping".

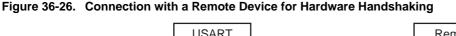

#### 37.6.2 16-bit Counter

Each 16-bit channel is organized around a 16-bit counter. The value of the counter is incremented at each positive edge of the selected clock. When the counter has reached the value 2<sup>16</sup>-1 and passes to zero, an overflow occurs and the COVFS bit in the TC Status Register (TC\_SR) is set.

The current value of the counter is accessible in real time by reading the TC Counter Value Register (TC\_CV). The counter can be reset by a trigger. In this case, the counter value passes to zero on the next valid edge of the selected clock.

#### 37.6.3 Clock Selection

At block level, input clock signals of each channel can either be connected to the external inputs TCLK0, TCLK1 or TCLK2, or be connected to the internal I/O signals TIOA0, TIOA1 or TIOA2 for chaining by programming the TC Block Mode Register (TC\_BMR). See Figure 37-2.

Each channel can independently select an internal or external clock source for its counter:

- External clock signals<sup>(1)</sup>: XC0, XC1 or XC2

- Internal clock signals: MCK/2, MCK/8, MCK/32, MCK/128, SLCK

This selection is made by the TCCLKS bits in the TC Channel Mode Register (TC\_CMR).

The selected clock can be inverted with the CLKI bit in the TC\_CMR. This allows counting on the opposite edges of the clock.

The burst function allows the clock to be validated when an external signal is high. The BURST parameter in the TC\_CMR defines this signal (none, XC0, XC1, XC2). See Figure 37-3.

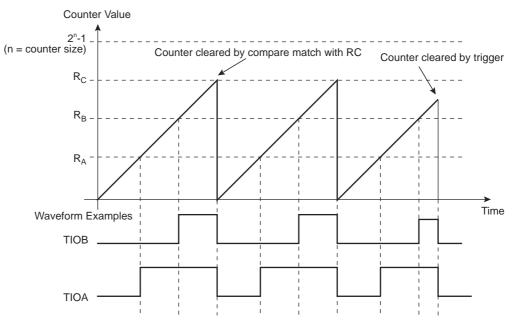

#### 37.6.11.2 WAVSEL = 10

When WAVSEL = 10, the value of TC\_CV is incremented from 0 to the value of RC, then automatically reset on a RC Compare. Once the value of TC\_CV has been reset, it is then incremented and so on. See Figure 37-9.

It is important to note that TC\_CV can be reset at any time by an external event or a software trigger if both are programmed correctly. See Figure 37-10.

In addition, RC Compare can stop the counter clock (CPCSTOP = 1 in TC\_CMR) and/or disable the counter clock (CPCDIS = 1 in TC\_CMR).

## • BEEVT: External Event Effect on TIOB

| Value | Name   | Description |

|-------|--------|-------------|

| 0     | NONE   | None        |

| 1     | SET    | Set         |

| 2     | CLEAR  | Clear       |

| 3     | TOGGLE | Toggle      |

## • BSWTRG: Software Trigger Effect on TIOB

| Value | Name   | Description |

|-------|--------|-------------|

| 0     | NONE   | None        |

| 1     | SET    | Set         |

| 2     | CLEAR  | Clear       |

| 3     | TOGGLE | Toggle      |

## • ETRGS: External Trigger Status (cleared on read)

0: External trigger has not occurred since the last read of the Status Register.

1: External trigger has occurred since the last read of the Status Register.

#### • CLKSTA: Clock Enabling Status

0: Clock is disabled.

1: Clock is enabled.

## • MTIOA: TIOA Mirror

0: TIOA is low. If TC\_CMRx.WAVE = 0, this means that TIOA pin is low. If TC\_CMRx.WAVE = 1, this means that TIOA is driven low.

1: TIOA is high. If TC\_CMRx.WAVE = 0, this means that TIOA pin is high. If TC\_CMRx.WAVE = 1, this means that TIOA is driven high.

#### • MTIOB: TIOB Mirror

0: TIOB is low. If TC\_CMRx.WAVE = 0, this means that TIOB pin is low. If TC\_CMRx.WAVE = 1, this means that TIOB is driven low.

1: TIOB is high. If TC\_CMRx.WAVE = 0, this means that TIOB pin is high. If TC\_CMRx.WAVE = 1, this means that TIOB is driven high.

## 37.7.13 TC Block Control Register

| Name:    | TC_BCR         |                                |    |    |    |    |      |  |

|----------|----------------|--------------------------------|----|----|----|----|------|--|

| Address: | 0x400100C0 (0) | 0x400100C0 (0), 0x400140C0 (1) |    |    |    |    |      |  |

| Access:  | Write-only     |                                |    |    |    |    |      |  |

| 31       | 30             | 29                             | 28 | 27 | 26 | 25 | 24   |  |

| _        | -              | -                              | -  | _  | -  | _  | -    |  |

| 23       | 22             | 21                             | 20 | 19 | 18 | 17 | 16   |  |

| -        | -              | -                              | -  | -  | -  | -  | -    |  |

| 15       | 14             | 13                             | 12 | 11 | 10 | 9  | 8    |  |

| -        | -              | -                              | -  | -  | -  | -  | -    |  |

| 7        | 6              | 5                              | 4  | 3  | 2  | 1  | 0    |  |

| _        | -              | _                              | _  | _  | -  | _  | SYNC |  |

## • SYNC: Synchro Command

0: No effect.

1: Asserts the SYNC signal which generates a software trigger simultaneously for each of the channels.

## 38.7.9 PWM Channel Mode Register

Name: PWM\_CMR[0..3]

## Address: 0x48008200 [0], 0x48008220 [1], 0x48008240 [2], 0x48008260 [3]

Access: Read/Write

| 31 | 30 | 29 | 28 | 27 | 26  | 25   | 24   |

|----|----|----|----|----|-----|------|------|

| _  | -  | —  | —  | —  | —   | _    | -    |

| 23 | 22 | 21 | 20 | 19 | 18  | 17   | 16   |

| _  | -  | -  | -  | —  | -   | -    | -    |

| 15 | 14 | 13 | 12 | 11 | 10  | 9    | 8    |

| -  | -  | —  | -  | -  | CPD | CPOL | CALG |

| 7  | 6  | 5  | 4  | 3  | 2   | 1    | 0    |

| _  | -  | —  | -  |    | CP  | RE   |      |

## • CPRE: Channel Pre-scaler

| Value | Name       | Description                  |

|-------|------------|------------------------------|

| 0000  | MCK        | Master Clock                 |

| 0001  | MCKDIV2    | Master Clock divided by 2    |

| 0010  | MCKDIV4    | Master Clock divided by 4    |

| 0011  | MCKDIV8    | Master Clock divided by 8    |

| 0100  | MCKDIV16   | Master Clock divided by 16   |

| 0101  | MCKDIV32   | Master Clock divided by 32   |

| 0110  | MCKDIV64   | Master Clock divided by 64   |

| 0111  | MCKDIV128  | Master Clock divided by 128  |

| 1000  | MCKDIV256  | Master Clock divided by 256  |

| 1001  | MCKDIV512  | Master Clock divided by 512  |

| 1010  | MCKDIV1024 | Master Clock divided by 1024 |

| 1011  | CLKA       | Clock A                      |

| 1100  | CLKB       | Clock B                      |

Values which are not listed in the table must be considered as "reserved".

## CALG: Channel Alignment

- 0 = The period is left aligned.

- 1 = The period is center aligned.

## • CPOL: Channel Polarity

- 0 = The output waveform starts at a low level.

- 1 = The output waveform starts at a high level.

# 39.6 Functional Description

The use of the SLCDC comprises three phases of functionality: initialization sequence, display phase, and disable sequence.

- Initialization Sequence:

- 1. Select the LCD supply source in the shutdown controller

- Internal: the On-chip LCD Power Supply is selected,

- External: the external supply source has to be between 2.5 to 3.6V

- 2. Select the clock division (SLCDC\_FRR) to use a proper frame rate

- 3. Enter the number of common and segments terminals (SLCDC\_MR)

- 4. Select the bias in compliance with the LCD manufacturer datasheet (SLCDC\_MR)

- 5. Enter buffer driving time (SLCDC\_MR)

- 6. Define the segments remapping pattern if required (SLCDC\_SMR0/1)

- During the Display Phase:

- 1. Data may be written at any time in the SLCDC memory, they are automatically latched and displayed at the next LCD frame

- 2. It is possible to:

- Adjust contrast

- Adjust the frame frequency

- Adjust buffer driving time

- Reduce the SLCDC consumption by entering in low-power waveform at any time

- Use the large set of display features such as blinking, inverted blink, etc.

- Disable Sequence: See Section 39.6.7 "Disabling the SLCDC"

## 40.7.20 ADC Write Protection Status Register

| Name:    | ADC_WPSR   |    |     |      |    |    |      |

|----------|------------|----|-----|------|----|----|------|

| Address: | 0x400380E8 |    |     |      |    |    |      |

| Access:  | Read-only  |    |     |      |    |    |      |

| 31       | 30         | 29 | 28  | 27   | 26 | 25 | 24   |

| -        | -          | -  | -   | -    | -  | -  | -    |

| 23       | 22         | 21 | 20  | 19   | 18 | 17 | 16   |

|          |            |    | WPV | /SRC |    |    |      |

| 15       | 14         | 13 | 12  | 11   | 10 | 9  | 8    |

|          |            |    | WPV | /SRC |    |    |      |

| 7        | 6          | 5  | 4   | 3    | 2  | 1  | 0    |

| -        | -          | -  | -   | _    | -  | _  | WPVS |

#### • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of the ADC\_WPSR register.

1: A write protection violation has occurred since the last read of the ADC\_WPSR register. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC.

#### • WPVSRC: Write Protection Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

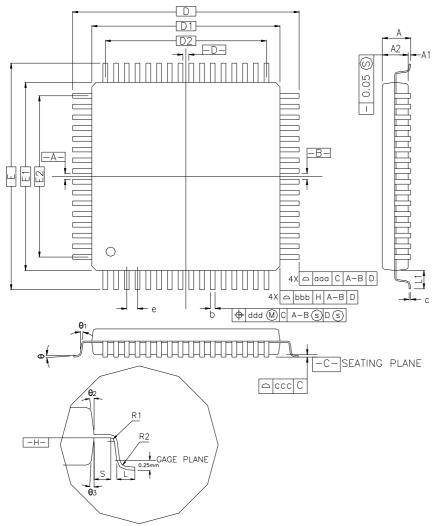

# 47. Mechanical Characteristics

# 47.1 100-lead LQFP Package

### Figure 47-1. 100-lead LQFP Package Drawing

| COTROL | DIMENSIONS   | ARF | IN   | MILLIMETERS.  |

|--------|--------------|-----|------|---------------|

| COINCE | DIVICINGIONS |     | 11.4 | WILLING ILKS. |

| SYMBOL | М     | ILLIMETI | ER    |        | INCH   |       |

|--------|-------|----------|-------|--------|--------|-------|

| STMBUL | MIN.  | NOM.     | MAX.  | MIN.   | NOM.   | MAX.  |

| A      | _     | —        | 1.60  | —      | _      | 0.063 |

| A1     | 0.05  |          | 0.15  | 0.002  |        | 0.006 |

| A2     | 1.35  | 1.40     | 1.45  | 0.053  | 0.055  | 0.057 |

| D      | 1     | 6.00 B   | SC.   | 0.     | 630 BS | SC.   |

| D1     | 1     | 4.00 B   | SC.   | 0.     | 551 BS | SC.   |

| E      | 1     | 6.00 B   | SC.   | 0.     | 630 BS | SC.   |

| E1     | 1.    | 4.00 B   | SC.   | 0.     | 551 BS | SC.   |

| R2     | 0.08  |          | 0.20  | 0.003  |        | 0.008 |

| R1     | 0.08  | —        | —     | 0.003  |        |       |

| θ      | 0°    | 3.5°     | 7*    | 0.     | 3.5°   | 7*    |

| θ1     | 0*    | —        |       | 0.     | _      | —     |

| θ2     | 11*   | 12*      | 1 3*  | 11.    | 12*    | 13*   |

| θ3     | 11°   | 12*      | 13*   | 11*    | 12°    | 13°   |

| с      | 0.09  | —        | 0.20  | 0.004  |        | 0.008 |

| L      | 0.45  | 0.60     | 0.75  | 0.018  | 0.024  | 0.030 |

| L 1    | 1     | .00 RE   | F     | 0.     | 039 RI | EF    |

| S      | 0.20  | —        |       | 0.008  | —      | —     |

| b      | 0.17  | 0.20     | 0.27  | 0.007  | 0.008  | 0.011 |

| е      |       | 0.50     | BSC.  | 0.0    | 20 BS0 | C.    |

| D2     |       | 12.00    | )     | 0      | .472   |       |

| E2     |       | 12.00    | )     | 0      | .472   |       |

|        | TOLER | ANCES    | OF FO | RM AND | POSI   | FION  |

| aaa    | 0.20  |          |       | 0      | .008   |       |

| bbb    | 0.20  |          |       |        | .008   |       |

| ccc    |       | 0.08     |       | (      | 0.003  |       |

| ddd    |       | 0.08     |       | (      | 0.003  |       |

| Table 47-1. | Device and LQFP Package Maximum \ | Neiaht |

|-------------|-----------------------------------|--------|

|             |                                   |        |

| SAM4CM                  |                        | 800    |  | mg |

|-------------------------|------------------------|--------|--|----|

| Table 47-2.             | LQFP Package Reference |        |  |    |

| JEDEC Drawing Reference |                        | MS-026 |  |    |

## Table 47-3. LQFP Package Characteristics

Moisture Sensitivity Level

**JESD97** Classification

3

e3

This package respects the recommendations of the NEMI User Group.