#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M4F                                                         |

| Core Size                  | 32-Bit Dual-Core                                                            |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I²C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                             |

| Number of I/O              | 57                                                                          |

| Program Memory Size        | 1MB (1M x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                |

| Data Converters            | A/D 6x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-LQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4cms16ca-aur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 12.6.6 Multiply and Divide Instructions

The table below shows the multiply and divide instructions.

| Mnemonic        | Description                                                                              |

|-----------------|------------------------------------------------------------------------------------------|

| MLA             | Multiply with Accumulate, 32-bit result                                                  |

| MLS             | Multiply and Subtract, 32-bit result                                                     |

| MUL             | Multiply, 32-bit result                                                                  |

| SDIV            | Signed Divide                                                                            |

| SMLA[B,T]       | Signed Multiply Accumulate (halfwords)                                                   |

| SMLAD, SMLADX   | Signed Multiply Accumulate Dual                                                          |

| SMLAL           | Signed Multiply with Accumulate ( $32 \times 32 + 64$ ), 64-bit result                   |

| SMLAL[B,T]      | Signed Multiply Accumulate Long (halfwords)                                              |

| SMLALD, SMLALDX | Signed Multiply Accumulate Long Dual                                                     |

| SMLAW[B T]      | Signed Multiply Accumulate (word by halfword)                                            |

| SMLSD           | Signed Multiply Subtract Dual                                                            |

| SMLSLD          | Signed Multiply Subtract Long Dual                                                       |

| SMMLA           | Signed Most Significant Word Multiply Accumulate                                         |

| SMMLS, SMMLSR   | Signed Most Significant Word Multiply Subtract                                           |

| SMUAD, SMUADX   | Signed Dual Multiply Add                                                                 |

| SMUL[B,T]       | Signed Multiply (word by halfword)                                                       |

| SMMUL, SMMULR   | Signed Most Significant Word Multiply                                                    |

| SMULL           | Signed Multiply (32x32), 64-bit result                                                   |

| SMULWB, SMULWT  | Signed Multiply (word by halfword)                                                       |

| SMUSD, SMUSDX   | Signed Dual Multiply Subtract                                                            |

| UDIV            | Unsigned Divide                                                                          |

| UMAAL           | Unsigned Multiply Accumulate Accumulate Long ( $32 \times 32 + 32 + 32$ ), 64-bit result |

| UMLAL           | Unsigned Multiply with Accumulate ( $32 \times 32 + 64$ ), 64-bit result                 |

| UMULL           | Unsigned Multiply ( $32 \times 32$ ), 64-bit result                                      |

Table 12-21. Multiply and Divide Instructions

## 17.6.17 RTC Write Protection Mode Register

| Name:    | RTC_WPMR   |    |    |     |    |    |      |

|----------|------------|----|----|-----|----|----|------|

| Address: | 0x400E1544 |    |    |     |    |    |      |

| Access:  | Read/Write |    |    |     |    |    |      |

| 31       | 30         | 29 | 28 | 27  | 26 | 25 | 24   |

|          |            |    | WP | KEY |    |    |      |

| 23       | 22         | 21 | 20 | 19  | 18 | 17 | 16   |

|          |            |    | WP | KEY |    |    |      |

| 15       | 14         | 13 | 12 | 11  | 10 | 9  | 8    |

|          |            |    | WP | KEY |    |    |      |

| 7        | 6          | 5  | 4  | 3   | 2  | 1  | 0    |

| -        | -          | -  | —  | —   | —  | _  | WPEN |

## • WPEN: Write Protection Enable

0: Disables the write protection if WPKEY corresponds to 0x525443 ("RTC" in ASCII).

1: Enables the write protection if WPKEY corresponds to 0x525443 ("RTC" in ASCII).

The following registers can be write-protected:

- RTC Mode Register

- RTC Time Alarm Register

- RTC Calendar Alarm Register

### • WPKEY: Write Protection Key

| Value    | Name   | Description                                                                       |

|----------|--------|-----------------------------------------------------------------------------------|

| 0x525443 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |

| 0x525443 |        | Always reads as 0.                                                                |

The erase sequence is the following:

- 1. Erase starts as soon as one of the erase commands and the FARG field are written in EEFC\_FCR.

- For the EPA command, the two lowest bits of the FARG field define the number of pages to be erased (FARG[1:0]):

| FARG[1:0] | Number of pages to be erased with EPA command |

|-----------|-----------------------------------------------|

| 0         | 4 pages (only valid for small 8 KB sectors)   |

| 1         | 8 pages                                       |

| 2         | 16 pages                                      |

| 3         | 32 pages (not valid for small 8 KB sectors)   |

### Table 22-4. EEFC\_FCR.FARG Field for EPA Command

2. When erasing is completed, the bit EEFC\_FSR.FRDY rises. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the interrupt line of the interrupt controller is activated.

Three errors can be detected in EEFC\_FSR after an erasing sequence:

- Command Error: A bad keyword has been written in EEFC\_FCR.

- Lock Error: At least one page to be erased belongs to a locked region. The erase command has been refused, no page has been erased. A command must be run previously to unlock the corresponding region.

- Flash Error: At the end of the erase period, the EraseVerify test of the Flash memory has failed.

### 22.4.3.4 Lock Bit Protection

Lock bits are associated with several pages in the embedded Flash memory plane. This defines lock regions in the embedded Flash memory plane. They prevent writing/erasing protected pages.

The lock sequence is the following:

- 1. Execute the 'Set Lock Bit' command by writing EEFC\_FCR.FCMD with the SLB command and EEFC\_FCR.FARG with a page number to be protected.

- 2. When the locking completes, the bit EEFC\_FSR.FRDY rises. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the interrupt line of the interrupt controller is activated.

- 3. The result of the SLB command can be checked running a 'Get Lock Bit' (GLB) command.

- Note: The value of the FARG argument passed together with SLB command must not exceed the higher lock bit index available in the product.

Two errors can be detected in EEFC\_FSR after a programming sequence:

- Command Error: A bad keyword has been written in EEFC\_FCR.

- Flash Error: At the end of the programming, the EraseVerify or WriteVerify test of the Flash memory has failed.

It is possible to clear lock bits previously set. After the lock bits are cleared, the locked region can be erased or programmed. The unlock sequence is the following:

- 1. Execute the 'Clear Lock Bit' command by writing EEFC\_FCR.FCMD with the CLB command and EEFC\_FCR.FARG with a page number to be unprotected.

- 2. When the unlock completes, the bit EEFC\_FSR.FRDY rises. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the interrupt line of the interrupt controller is activated.

- Note: The value of the FARG argument passed together with CLB command must not exceed the higher lock bit index available in the product.

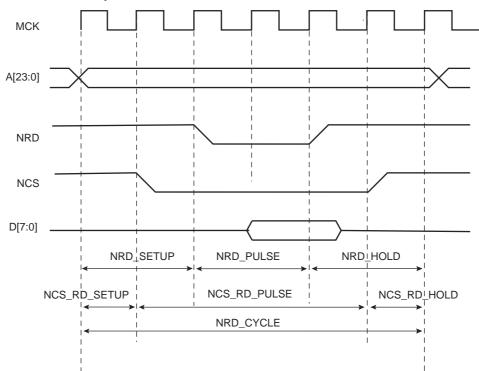

Figure 27-7. Standard Read Cycle

### 27.9.1.1 NRD Waveform

The NRD signal is characterized by a setup timing, a pulse width and a hold timing.

- NRD\_SETUP—the NRD setup time is defined as the setup of address before the NRD falling edge;

- NRD\_PULSE—the NRD pulse length is the time between NRD falling edge and NRD rising edge;

- NRD\_HOLD—the NRD hold time is defined as the hold time of address after the NRD rising edge.

### 27.9.1.2 NCS Waveform

The NCS signal can be divided into a setup time, pulse length and hold time:

- NCS\_RD\_SETUP—the NCS setup time is defined as the setup time of address before the NCS falling edge.

- NCS\_RD\_PULSE— the NCS pulse length is the time between NCS falling edge and NCS rising edge;

- NCS\_RD\_HOLD—the NCS hold time is defined as the hold time of address after the NCS rising edge.

### 27.9.1.3 Read Cycle

The NRD\_CYCLE time is defined as the total duration of the read cycle, i.e., from the time where address is set on the address bus to the point where address may change. The total read cycle time is equal to:

NRD\_CYCLE = NRD\_SETUP + NRD\_PULSE + NRD\_HOLD = NCS\_RD\_SETUP + NCS\_RD\_PULSE + NCS\_RD\_HOLD

All NRD and NCS timings are defined separately for each chip select as an integer number of Master Clock cycles. To ensure that the NRD and NCS timings are consistent, user must define the total read cycle instead of the hold timing. NRD\_CYCLE implicitly defines the NRD hold time and NCS hold time as:

NRD\_HOLD = NRD\_CYCLE - NRD SETUP - NRD PULSE

NCS\_RD\_HOLD = NRD\_CYCLE - NCS\_RD\_SETUP - NCS\_RD\_PULSE

### 27.9.1.4 Null Delay Setup and Hold

If null setup and hold parameters are programmed for NRD and/or NCS, NRD and NCS remain active continuously in case of consecutive read cycles in the same memory (see Figure 27-8).

# 29.4 Slow Clock

The Supply Controller embeds a slow clock generator that is supplied with the VDDBU power supply. As soon as VDDBU is supplied, both the 32.768 kHz crystal oscillator and the embedded 32 kHz (typical) RC oscillator are powered up, but only the RC oscillator is enabled. This allows the slow clock to be valid in a short time (about 100 µs).

The slow clock is generated either by the 32.768 kHz crystal oscillator or by the embedded 32 kHz (typical) RC oscillator.

The selection of the slow clock source is made via the XTALSEL bit in the Supply Controller Control Register (SUPC\_CR).

The OSCSEL bit of the Supply Controller Status Register (SUPC\_SR) and the OSCSEL bit of the PMC Status Register (PMC\_SR) report which oscillator is selected as the slow clock source. PMC\_SR.OSCSEL informs when the switch sequence initiated by a new value written in SUPC\_CR.XTALSEL is done.

### 29.4.1 Embedded 32 kHz (typical) RC Oscillator

By default, the embedded 32 kHz (typical) RC oscillator is enabled and selected. The user has to take into account the possible drifts of this oscillator. More details are given in the section "DC Characteristics".

This oscillator is disabled by clearing the SUPC\_CR.XTALSEL.

### 29.4.2 32.768 kHz Crystal Oscillator

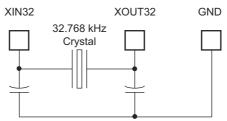

The Clock Generator integrates a low-power 32.768 kHz crystal oscillator. To use this oscillator, the XIN32 and XOUT32 pins must be connected to a 32.768 kHz crystal. Two external capacitors must be wired as shown in Figure 29-2. More details are given in the section "DC Characteristics".

Note that the user is not obliged to use the 32.768 kHz crystal oscillator and can use the 32 kHz (typical) RC oscillator instead.

### Figure 29-2. Typical 32768 Crystal Oscillator Connection

The 32.768 kHz crystal oscillator provides a more accurate frequency than the 32 kHz (typical) RC oscillator.

To select the 32.768 kHz crystal oscillator as the source of the slow clock, the bit SUPC\_CR.XTALSEL must be set. This results in a sequence which enables the 32.768 kHz crystal oscillator and then disables the 32 kHz (typical) RC oscillator to save power. The switch of the slow clock source is glitch-free.

Reverting to the 32 kHz (typical) RC oscillator is only possible by shutting down the VDDBU power supply. If the user does not need the 32.768 kHz crystal oscillator, the XIN32 and XOUT32 pins can be left unconnected.

The user can also set the 32.768 kHz crystal oscillator in Bypass mode instead of connecting a crystal. In this case, the user must provide the external clock signal on XIN32. The input characteristics of the XIN32 pin are given in the section "Electrical Characteristics". To enter Bypass mode, the OSCBYPASS bit of the Supply Controller Mode Register (SUPC\_MR) must be set prior to setting SUPC\_CR.XTALSEL.

# **30.17 Register Write Protection**

To prevent any single software error from corrupting PMC behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the PMC Write Protection Mode Register (PMC\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the PMC Write Protection Status Register (PMC\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the PMC\_WPSR.

The following registers can be write-protected:

- PMC System Clock Enable Register

- PMC System Clock Disable Register

- PMC Peripheral Clock Enable Register 0

- PMC Peripheral Clock Disable Register 0

- PMC Clock Generator Main Oscillator Register

- PMC Clock Generator PLLA Register

- PMC Clock Generator PLLB Register

- PMC Master Clock Register

- PMC Programmable Clock Register

- PMC Fast Startup Mode Register

- PMC Fast Startup Polarity Register

- PMC Coprocessor Fast Startup Mode Register

- PMC Peripheral Clock Enable Register 1

- PMC Peripheral Clock Disable Register 1

- PMC Oscillator Calibration Register

- Four input signals on I/O line 12 to 15 to read an external device status (polled, thus no input change interrupt), no pull-up resistor, no glitch filter

- I/O lines 16 to 19 assigned to peripheral A functions with pull-up resistor

- I/O lines 20 to 23 assigned to peripheral B functions with pull-down resistor

- I/O lines 24 to 27 assigned to peripheral C with input change interrupt, no pull-up resistor and no pull-down

resistor

- I/O lines 28 to 31 assigned to peripheral D, no pull-up resistor and no pull-down resistor

## Table 32-3.Programming Example

| Register    | Value to be Written |

|-------------|---------------------|

| PIO_PER     | 0x0000_FFFF         |

| PIO_PDR     | 0xFFFF_0000         |

| PIO_OER     | 0x0000_00FF         |

| PIO_ODR     | 0xFFFF_FF00         |

| PIO_IFER    | 0x0000_0F00         |

| PIO_IFDR    | 0xFFFF_F0FF         |

| PIO_SODR    | 0x0000_0000         |

| PIO_CODR    | 0x0FFF_FFFF         |

| PIO_IER     | 0x0F00_0F00         |

| PIO_IDR     | 0xF0FF_F0FF         |

| PIO_MDER    | 0x0000_000F         |

| PIO_MDDR    | 0xFFFF_FF0          |

| PIO_PUDR    | 0xFFF0_00F0         |

| PIO_PUER    | 0x000F_FF0F         |

| PIO_PPDDR   | 0xFF0F_FFFF         |

| PIO_PPDER   | 0x00F0_0000         |

| PIO_ABCDSR1 | 0xF0F0_0000         |

| PIO_ABCDSR2 | 0xFF00_0000         |

| PIO_OWER    | 0x0000_000F         |

| PIO_OWDR    | 0x0FFF_FFF0         |

## 32.6.15 PIO Interrupt Disable Register

| Name:    | PIO_IDR        |               |                 |              |     |     |     |

|----------|----------------|---------------|-----------------|--------------|-----|-----|-----|

| Address: | 0x400E0E44 (PI | OA), 0x400E10 | 044 (PIOB), 0x4 | 800C044 (PIO | C)  |     |     |

| Access:  | Write-only     |               |                 |              |     |     |     |

| 31       | 30             | 29            | 28              | 27           | 26  | 25  | 24  |

| P31      | P30            | P29           | P28             | P27          | P26 | P25 | P24 |

| 23       | 22             | 21            | 20              | 19           | 18  | 17  | 16  |

| P23      | P22            | P21           | P20             | P19          | P18 | P17 | P16 |

| 15       | 14             | 13            | 12              | 11           | 10  | 9   | 8   |

| P15      | P14            | P13           | P12             | P11          | P10 | P9  | P8  |

| 7        | 6              | 5             | 4               | 3            | 2   | 1   | 0   |

| P7       | P6             | P5            | P4              | P3           | P2  | P1  | P0  |

# • P0–P31: Input Change Interrupt Disable

0: No effect.

1: Disables the input change interrupt on the I/O line.

## 32.6.20 PIO Multi-driver Status Register

Name: PIO\_MDSR

Address: 0x400E0E58 (PIOA), 0x400E1058 (PIOB), 0x4800C058 (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Multi-drive Status

0: The multi-drive is disabled on the I/O line. The pin is driven at high- and low-level.

1: The multi-drive is enabled on the I/O line. The pin is driven at low-level only.

## 32.6.30 PIO Pad Pull-Down Disable Register

Name: PIO\_PPDDR

# Address: 0x400E0E90 (PIOA), 0x400E1090 (PIOB), 0x4800C090 (PIOC)

Access: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

## • P0-P31: Pull-Down Disable

0: No effect.

1: Disables the pull-down resistor on the I/O line.

## 32.6.46 PIO Write Protection Status Register

| Name:    | PIO_WPSR      |                |                 |               |    |    |      |

|----------|---------------|----------------|-----------------|---------------|----|----|------|

| Address: | 0x400E0EE8 (P | IOA), 0x400E10 | DE8 (PIOB), 0x4 | 4800C0E8 (PIO | C) |    |      |

| Access:  | Read-only     |                |                 |               |    |    |      |

| 31       | 30            | 29             | 28              | 27            | 26 | 25 | 24   |

| —        | -             | -              | -               | —             | -  | _  | —    |

| 23       | 22            | 21             | 20              | 19            | 18 | 17 | 16   |

|          |               |                | WPV             | /SRC          |    |    |      |

| 15       | 14            | 13             | 12              | 11            | 10 | 9  | 8    |

|          | WPVSRC        |                |                 |               |    |    |      |

| 7        | 6             | 5              | 4               | 3             | 2  | 1  | 0    |

| -        | -             | —              | -               | -             | -  | _  | WPVS |

## • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of the PIO\_WPSR.

1: A write protection violation has occurred since the last read of the PIO\_WPSR. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC.

## • WPVSRC: Write Protection Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

#### **Drift Compensation**

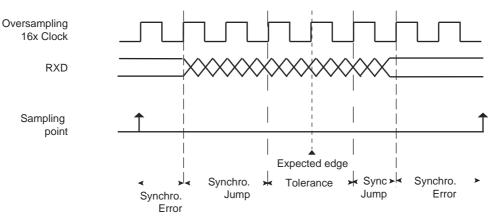

Drift compensation is available only in 16X oversampling mode. An hardware recovery system allows a larger clock drift. To enable the hardware system, the bit in the USART\_MAN register must be set. If the RXD edge is one 16X clock cycle from the expected edge, this is considered as normal jitter and no corrective actions is taken. If the RXD event is between 4 and 2 clock cycles before the expected edge, then the current period is shortened by one clock cycle. If the RXD event is between 2 and 3 clock cycles after the expected edge, then the current period is lengthened by one clock cycle. These intervals are considered to be drift and so corrective actions are automatically taken.

#### 36.6.3.3 Asynchronous Receiver

If the USART is programmed in Asynchronous operating mode (SYNC = 0), the receiver oversamples the RXD input line. The oversampling is either 16 or 8 times the baud rate clock, depending on the OVER bit in the US\_MR.

The receiver samples the RXD line. If the line is sampled during one half of a bit time to 0, a start bit is detected and data, parity and stop bits are successively sampled on the bit rate clock.

If the oversampling is 16 (OVER = 0), a start is detected at the eighth sample to 0. Data bits, parity bit and stop bit are assumed to have a duration corresponding to 16 oversampling clock cycles. If the oversampling is 8 (OVER = 1), a start bit is detected at the fourth sample to 0. Data bits, parity bit and stop bit are assumed to have a duration corresponding to 8 oversampling clock cycles.

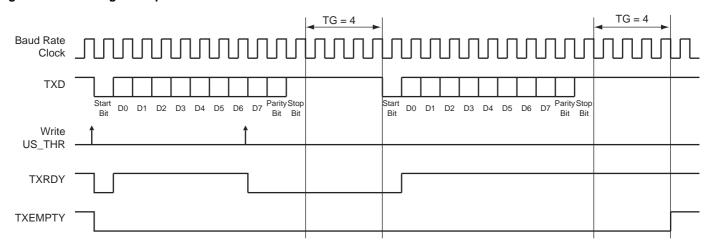

Figure 36-22. Timeguard Operations

Table 36-9 indicates the maximum length of a timeguard period that the transmitter can handle in relation to the function of the baud rate.

| Baud Rate (bit/s) | Bit Time (µs) | Timeguard (ms) |

|-------------------|---------------|----------------|

| 1,200             | 833           | 212.50         |

| 9,600             | 104           | 26.56          |

| 14,400            | 69.4          | 17.71          |

| 19,200            | 52.1          | 13.28          |

| 28,800            | 34.7          | 8.85           |

| 38,400            | 26            | 6.63           |

| 56,000            | 17.9          | 4.55           |

| 57,600            | 17.4          | 4.43           |

| 115,200           | 8.7           | 2.21           |

Table 36-9.

Maximum Timeguard Length Depending on Baud Rate

#### 36.6.3.11 Receiver Time-out

The Receiver Time-out provides support in handling variable-length frames. This feature detects an idle condition on the RXD line. When a time-out is detected, the bit TIMEOUT in the US\_CSR rises and can generate an interrupt, thus indicating to the driver an end of frame.

The time-out delay period (during which the receiver waits for a new character) is programmed in the TO field of the Receiver Time-out register (US\_RTOR). If the TO field is written to 0, the Receiver Time-out is disabled and no time-out is detected. The TIMEOUT bit in the US\_CSR remains at 0. Otherwise, the receiver loads a 16-bit counter with the value programmed in TO. This counter is decremented at each bit period and reloaded each time a new character is received. If the counter reaches 0, the TIMEOUT bit in US\_CSR rises. Then, the user can either:

- Stop the counter clock until a new character is received. This is performed by writing a 1 to the STTTO (Start Time-out) bit in the US\_CR. In this case, the idle state on RXD before a new character is received will not provide a time-out. This prevents having to handle an interrupt before a character is received and allows waiting for the next idle state on RXD after a frame is received.

- Obtain an interrupt while no character is received. This is performed by writing a 1 to the RETTO (Reload and Start Time-out) bit in the US\_CR. If RETTO is performed, the counter starts counting down immediately from the value TO. This enables generation of a periodic interrupt so that a user time-out can be handled, for example when no key is pressed on a keyboard.

# 36.7.19 USART Number of Errors Register

| Name:    | US_NER          |              |                |                |                 |         |    |

|----------|-----------------|--------------|----------------|----------------|-----------------|---------|----|

| Address: | 0x40024044 (0), | 0x40028044 ( | 1), 0x4002C044 | (2), 0x4003004 | 44 (3), 0x40034 | 044 (4) |    |

| Access:  | Read-only       |              |                |                |                 |         |    |

| 31       | 30              | 29           | 28             | 27             | 26              | 25      | 24 |

| _        | _               | _            | _              | _              | -               | _       | -  |

| 23       | 22              | 21           | 20             | 19             | 18              | 17      | 16 |

| -        | -               | —            | -              | —              | —               | _       | -  |

| 15       | 14              | 13           | 12             | 11             | 10              | 9       | 8  |

| _        | -               | _            | -              | -              | -               | _       | -  |

| 7        | 6               | 5            | 4              | 3              | 2               | 1       | 0  |

|          |                 |              | NB_EF          | RORS           |                 |         |    |

This register is relevant only if USART\_MODE = 0x4 or 0x6 in the USART Mode Register.

## • NB\_ERRORS: Number of Errors

Total number of errors that occurred during an ISO7816 transfer. This register automatically clears when read.

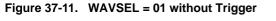

### 37.6.11.3 WAVSEL = 01

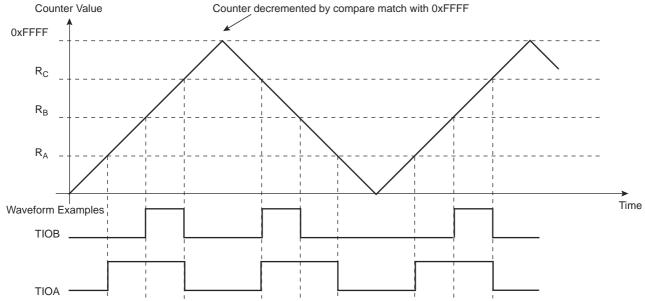

When WAVSEL = 01, the value of TC\_CV is incremented from 0 to  $2^{16}$ -1. Once  $2^{16}$ -1 is reached, the value of TC\_CV is decremented to 0, then re-incremented to  $2^{16}$ -1 and so on. See Figure 37-11.

A trigger such as an external event or a software trigger can modify TC\_CV at any time. If a trigger occurs while TC\_CV is incrementing, TC\_CV then decrements. If a trigger is received while TC\_CV is decrementing, TC\_CV then increments. See Figure 37-12.

RC Compare cannot be programmed to generate a trigger in this configuration.

At the same time, RC Compare can stop the counter clock (CPCSTOP = 1) and/or disable the counter clock (CPCDIS = 1).

#### Figure 37-12. WAVSEL = 01 with Trigger

## 37.7.10 TC Interrupt Enable Register

Name: TC\_IERx [x=0..2]

Address: 0x40010024 (0)[0], 0x40010064 (0)[1], 0x400100A4 (0)[2], 0x40014024 (1)[0], 0x40014064 (1)[1], 0x400140A4 (1)[2]

| Access: | Write-only |       |      |         |      |       |       |

|---------|------------|-------|------|---------|------|-------|-------|

| 31      | 30         | 29    | 28   | 27      | 26   | 25    | 24    |

| -       | _          | -     | _    | —       | —    | —     | -     |

| 23      | 22         | 21    | 20   | 19      | 18   | 17    | 16    |

| -       | -          | -     | -    | -       | -    | -     | -     |

| 15      | 14         | 13    | 12   | 11      | 10   | 9     | 8     |

| 15      | 1          | 13    | 12   | 11<br>i | 10   | 9     | °     |

|         | _          | _     | _    | _       | -    | _     | –     |

| 7       | 6          | 5     | 4    | 3       | 2    | 1     | 0     |

| ETRGS   | LDRBS      | LDRAS | CPCS | CPBS    | CPAS | LOVRS | COVFS |

## COVFS: Counter Overflow

0: No effect.

1: Enables the Counter Overflow Interrupt.

### • LOVRS: Load Overrun

0: No effect.

1: Enables the Load Overrun Interrupt.

### • CPAS: RA Compare

0: No effect.

1: Enables the RA Compare Interrupt.

## • CPBS: RB Compare

0: No effect.

1: Enables the RB Compare Interrupt.

## • CPCS: RC Compare

0: No effect.

1: Enables the RC Compare Interrupt.

## • LDRAS: RA Loading

0: No effect.

1: Enables the RA Load Interrupt.

## • LDRBS: RB Loading

0: No effect.

1: Enables the RB Load Interrupt.

| 43.5.2.1 ICI | M Region Start Add        | Iress Structure | e Member |     |    |    |    |  |  |

|--------------|---------------------------|-----------------|----------|-----|----|----|----|--|--|

| Name:        | ICM_RADDR                 |                 |          |     |    |    |    |  |  |

| Address:     | ICM_DSCR+0x000+RID*(0x10) |                 |          |     |    |    |    |  |  |

| Access:      | Read/Write                |                 |          |     |    |    |    |  |  |

| 31           | 30                        | 29              | 28       | 27  | 26 | 25 | 24 |  |  |

|              |                           |                 | RAI      | DDR |    |    |    |  |  |

| 23           | 22                        | 21              | 20       | 19  | 18 | 17 | 16 |  |  |

|              |                           |                 | RAI      | DDR |    |    |    |  |  |

| 15           | 14                        | 13              | 12       | 11  | 10 | 9  | 8  |  |  |

|              | RADDR                     |                 |          |     |    |    |    |  |  |

| 7            | 6                         | 5               | 4        | 3   | 2  | 1  | 0  |  |  |

|              |                           |                 | RAI      | DDR |    |    |    |  |  |

# • RADDR: Region Start Address

This field indicates the first byte address of the region.

| 43.5.2.4 ICM Region Next Address Structure Member |                           |    |    |    |    |    |    |  |  |

|---------------------------------------------------|---------------------------|----|----|----|----|----|----|--|--|

| Name:                                             | ICM_RNEXT                 |    |    |    |    |    |    |  |  |

| Address:                                          | ICM_DSCR+0x00C+RID*(0x10) |    |    |    |    |    |    |  |  |

| Access:                                           | : Read/Write              |    |    |    |    |    |    |  |  |

| 31                                                | 30                        | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|                                                   |                           |    | NE | XT |    |    |    |  |  |

| 23                                                | 22                        | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|                                                   | NEXT                      |    |    |    |    |    |    |  |  |

| 15                                                | 14                        | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

|                                                   | NEXT                      |    |    |    |    |    |    |  |  |

| 7                                                 | 6                         | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|                                                   |                           | NE | ХТ |    |    | _  | _  |  |  |

## • NEXT: Region Transfer Descriptor Next Address

When configured to 0, this field indicates that the current descriptor is the last descriptor of the Secondary List, otherwise it points at a new descriptor of the Secondary List.

# 43.6.2 ICM Control Register

| Name:<br>Address: | ICM_CTRL<br>0x40044004 |     |    |    |       |         |        |

|-------------------|------------------------|-----|----|----|-------|---------|--------|

| Access:           | Write-only             |     |    |    |       |         |        |

| 31                | 30                     | 29  | 28 | 27 | 26    | 25      | 24     |

| -                 | _                      | _   | -  | _  | _     | _       | _      |

| 23                | 22                     | 21  | 20 | 19 | 18    | 17      | 16     |

| -                 | -                      | _   | -  | _  | _     | _       | _      |

| 15                | 14                     | 13  | 12 | 11 | 10    | 9       | 8      |

|                   | RM                     | EN  |    |    | RM    | DIS     |        |

| 7                 | 6                      | 5   | 4  | 3  | 2     | 1       | 0      |

|                   | REH                    | ASH |    | —  | SWRST | DISABLE | ENABLE |

### • ENABLE: ICM Enable

### 0: No effect

1: When set to one, the ICM controller is activated.

## DISABLE: ICM Disable Register

0: No effect

1: The ICM controller is disabled. If a region is active, this region is terminated.

## • SWRST: Software Reset

0: No effect

1: Resets the ICM controller.

# • REHASH: Recompute Internal Hash

0: No effect

1: When REHASH[*i*] is set to one, Region *i* digest is re-computed. This bit is only available when region monitoring is disabled.

# • RMDIS: Region Monitoring Disable

0: No effect

1: When bit RMDIS[*i*] is set to one, the monitoring of region with identifier *i* is disabled.

# • RMEN: Region Monitoring Enable

0: No effect

1: When bit RMEN[*i*] is set to one, the monitoring of region with identifier *i* is activated.

Monitoring is activated by default.

### 46.5.15 Temperature Sensor Characteristics

The temperature sensor provides an output voltage ( $V_T$ ) that is proportional to absolute temperature (PTAT). This voltage can be measured through the channel number 7 of the 10-bit ADC. Improvement of the raw performance of the temperature sensor acquisition can be achieved by performing a single temperature point calibration to remove the initial inaccuracies ( $V_T$  and ADC offsets).

| Symbol              | Parameter                                 | Conditions                                                                                       | Min  | Тур  | Max  | Unit  |

|---------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>DDIN</sub>   | Supply voltage range (VDDIN)              | -                                                                                                | 2.4  | -    | 3.6  | V     |

| V <sub>T</sub>      | Output voltage                            | $T_J = 27^{\circ} C$                                                                             | 1.34 | 1.44 | 1.54 | V     |

| dV <sub>T</sub> /dT | Output voltage sensitivity to temperature | -                                                                                                | 4.2  | 4.7  | 5.2  | mV/°C |

| dV <sub>T</sub> /dV | $V_{T}$ variation with VDDIN              | VDDIN from 2.4V to 3.6V                                                                          | _    | -    | 1    | mV/V  |

| t <sub>S</sub>      | V <sub>T</sub> settling time              | When $V_T$ is sampled by the 10-bit ADC, the required track time to ensure 1°C accurate settling | -    | _    | 1    | μs    |

| T <sub>ACC</sub>    | Temperature accuracy <sup>(1)</sup>       | After offset calibration<br>Over T <sub>J</sub> range [-40°C to +85°C]                           | -    | ±5   | ±7   | °C    |

|                     | remperature accuracy."                    | After offset calibration<br>Over T <sub>J</sub> range [0°C to +80°C]                             | -    | ±4   | ±6   | °C    |

| t <sub>ON</sub>     | Start-up time                             | -                                                                                                | -    | 5    | 10   | μs    |

|                     | Current consumption                       | -                                                                                                | 50   | 70   | 80   | μA    |

Table 46-35. Temperature Sensor Characteristics

Note: 1. Does not include errors due to A/D conversion process.

### 46.5.16 Optical UART RX Transceiver Characteristics

Table 46-36 gives the description of the optical link transceiver for electrically isolated serial communication with hand-held equipment, such as calibrators compliant with standards ANSI-C12.18 or IEC62056-21 (only available on UART1).

Table 46-36. Transceiver Characteristics

| Symbol            | Parameter                    | Conditions                                                                                                          | Min | Тур | Max | Unit |

|-------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>DDIO</sub> | Supply voltage range (VDDIO) | -                                                                                                                   | 3   | 3.3 | 3.6 | V    |

| I <sub>DD</sub> C | Current concumption          | ON                                                                                                                  |     | 25  | 35  |      |

|                   | Current consumption          | OFF                                                                                                                 | _   |     | 0.1 | μA   |

| V <sub>TH</sub>   | Comparator threshold         | According to the programmed threshold. See the<br>OPT_CMPTH field in Section 35.6.2 "UART<br>Mode Register" (UART1) | -20 | -   | +20 | mV   |

| V <sub>HYST</sub> | Hysteresis                   | -                                                                                                                   | 10  | 20  | 40  | mV   |

| t <sub>PROP</sub> | Propagation time             | With 100 mVpp square wave input around threshold                                                                    | -   | -   | 5   | μs   |

| t <sub>ON</sub>   | Start-up time                | -                                                                                                                   | -   | _   | 100 | μs   |