# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M4F                                                        |

| Core Size                  | 32-Bit Dual-Core                                                           |

| Speed                      | 120MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                            |

| Number of I/O              | 57                                                                         |

| Program Memory Size        | 2MB (2M x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 6x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-LQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4cms32ca-au |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1. Configuration Summary

The SAM4CM devices differ in memory size, package and features. Table 1-1 summarizes the different device configurations.

| Feature                                   | SAM4CMP32C             | SAM4CMP16C         | SAM4CMP8C  | SAM4CMS32C                                 | SAM4CMS16C  | SAM4CMS8C  | SAM4CMS4C  |  |

|-------------------------------------------|------------------------|--------------------|------------|--------------------------------------------|-------------|------------|------------|--|

| Flash                                     | 2048 Kbytes            | 1024 Kbytes        | 512 Kbytes | 2048 Kbytes                                | 1024 Kbytes | 512 Kbytes | 256 Kbytes |  |

| SRAM                                      | 256 + 32 +16<br>Kbytes | 128 + 16 -         | + 8 Kbytes | 256 + 32 +16<br>Kbytes 128 + 16 + 8 Kbytes |             |            |            |  |

| Package                                   |                        |                    |            | LQFP 100                                   |             |            |            |  |

| Number of<br>PIOs                         |                        | 52                 |            |                                            | 5           | 7          |            |  |

| External Bus<br>Interface                 |                        |                    |            | 8-bit data                                 |             |            |            |  |

| 16-bit Timer                              |                        |                    |            | 6 channels                                 |             |            |            |  |

| 16-bit PWM                                |                        |                    |            | 3 channels                                 |             |            |            |  |

| UART /<br>USART                           |                        | 2/3                |            |                                            | 2           | /4         |            |  |

| SPI <sup>(1)</sup>                        |                        | 1/4 + 3            |            | 1/4 + 4                                    |             |            |            |  |

| тwi                                       |                        |                    |            | 2                                          |             |            |            |  |

| 10-bit ADC<br>Channels <sup>(2)</sup>     |                        |                    |            | 6                                          |             |            |            |  |

| Energy<br>Metering<br>Analog Front<br>End | 7 channe               | els (3 voltages, 4 | currents)  | 4 channels (2 voltages, 2 currents)        |             |            |            |  |

| Cryptography                              |                        |                    | AES, C     | PKCC, ICM (SHA                             | ), TRNG     |            |            |  |

| Segmented<br>LCD                          | 33 se                  | egments × 6 com    | mons       | 38 segments × 6 commons                    |             |            |            |  |

| Anti-<br>Tampering<br>Inputs              |                        | 1                  |            | 2                                          |             |            |            |  |

| Flash Page<br>Size                        | 512 bytes              |                    |            |                                            |             |            |            |  |

| Flash Pages                               | 2 × 2048               | 2048               | 1024       | 2 × 2048                                   | 2048        | 1024       | 512        |  |

| Flash Lock<br>Region Size                 |                        |                    |            | 8 Kbytes                                   |             |            |            |  |

| Flash Lock<br>Bits                        | 2 × 128                | 128                | 64         | 2 × 128                                    | 128         | 64         | 32         |  |

### Table 1-1. Configuration Summary

Notes: 1. 1/4 + 3 = Number of SPI Controllers / Number of Chip Selects + Number of USARTs with SPI mode.

2. One channel is reserved for internal temperature sensor and one channel for VDDBU measurement.

| Mnemonic | Description                                         |

|----------|-----------------------------------------------------|

| SHSUB16  | Signed Halving Subtract 16                          |

| SHSUB8   | Signed Halving Subtract 8                           |

| SSUB16   | Signed Subtract 16                                  |

| SSUB8    | Signed Subtract 8                                   |

| SUB      | Subtract                                            |

| SUBW     | Subtract                                            |

| TEQ      | Test Equivalence                                    |

| TST      | Test                                                |

| UADD16   | Unsigned Add 16                                     |

| UADD8    | Unsigned Add 8                                      |

| UASX     | Unsigned Add and Subtract with Exchange             |

| USAX     | Unsigned Subtract and Add with Exchange             |

| UHADD16  | Unsigned Halving Add 16                             |

| UHADD8   | Unsigned Halving Add 8                              |

| UHASX    | Unsigned Halving Add and Subtract with Exchange     |

| UHSAX    | Unsigned Halving Subtract and Add with Exchange     |

| UHSUB16  | Unsigned Halving Subtract 16                        |

| UHSUB8   | Unsigned Halving Subtract 8                         |

| USAD8    | Unsigned Sum of Absolute Differences                |

| USADA8   | Unsigned Sum of Absolute Differences and Accumulate |

| USUB16   | Unsigned Subtract 16                                |

| USUB8    | Unsigned Subtract 8                                 |

Table 12-20. Data Processing Instructions (Continued)

### 12.6.8.3 SXTA and UXTA

Signed and Unsigned Extend and Add

Syntax

op{cond} {Rd,} Rn, Rm {, ROR #n} op{cond} {Rd,} Rn, Rm {, ROR #n}

where:

| ор     | is one of:                                                          |

|--------|---------------------------------------------------------------------|

|        | SXTAB Sign extends an 8-bit value to a 32-bit value and add.        |

|        | SXTAH Sign extends a 16-bit value to a 32-bit value and add.        |

|        | SXTAB16 Sign extends two 8-bit values to two 16-bit values and add. |

|        | UXTAB Zero extends an 8-bit value to a 32-bit value and add.        |

|        | UXTAH Zero extends a 16-bit value to a 32-bit value and add.        |

|        | UXTAB16 Zero extends two 8-bit values to two 16-bit values and add. |

| cond   | is an optional condition code, see "Conditional Execution".         |

| Rd     | is the destination register.                                        |

| Rn     | is the first operand register.                                      |

| Rm     | is the register holding the value to rotate and extend.             |

| ROR #n | is one of:                                                          |

|        | ROR #8 Value from <i>Rm</i> is rotated right 8 bits.                |

|        | ROR #16 Value from Rm is rotated right 16 bits.                     |

|        |                                                                     |

### Operation

These instructions do the following:

- 1. Rotate the value from Rm right by 0, 8, 16 or 24 bits.

- 2. Extract bits from the resulting value:

- SXTAB extracts bits[7:0] from *Rm* and sign extends to 32 bits.

*ROR* #24 Value from *Rm* is rotated right 24 bits. If ROR #*n* is omitted, no rotation is performed.

- UXTAB extracts bits[7:0] from *Rm* and zero extends to 32 bits.

- SXTAH extracts bits[15:0] from *Rm* and sign extends to 32 bits.

- UXTAH extracts bits[15:0] from *Rm* and zero extends to 32 bits.

- SXTAB16 extracts bits[7:0] from *Rm* and sign extends to 16 bits, and extracts bits [23:16] from *Rm* and sign extends to 16 bits.

- UXTAB16 extracts bits[7:0] from *Rm* and zero extends to 16 bits, and extracts bits [23:16] from *Rm* and zero extends to 16 bits.

- 3. Adds the signed or zero extended value to the word or corresponding halfword of *Rn* and writes the result in *Rd*.

Restrictions

Do not use SP and do not use PC.

### 12.11.2.2 MPU Control Register

| Name:   | MPU_CTRL   |    |    |    |            |          |        |

|---------|------------|----|----|----|------------|----------|--------|

| Access: | Read/Write |    |    |    |            |          |        |

| 31      | 30         | 29 | 28 | 27 | 26         | 25       | 24     |

| _       | -          | -  | -  | _  | -          | _        | -      |

| 23      | 22         | 21 | 20 | 19 | 18         | 17       | 16     |

| -       | -          | -  | -  | -  | -          | _        | -      |

| 15      | 14         | 13 | 12 | 11 | 10         | 9        | 8      |

| _       | —          | -  | -  | —  | -          | _        | -      |

| 7       | 6          | 5  | 4  | 3  | 2          | 1        | 0      |

| -       | -          | _  | _  | _  | PRIVDEFENA | HFNMIENA | ENABLE |

The MPU CTRL register enables the MPU, enables the default memory map background region, and enables the use of the MPU when in the hard fault, Non-maskable Interrupt (NMI), and FAULTMASK escalated handlers.

### • PRIVDEFENA: Privileged Default Memory Map Enable

Enables privileged software access to the default memory map:

0: If the MPU is enabled, disables the use of the default memory map. Any memory access to a location not covered by any enabled region causes a fault.

1: If the MPU is enabled, enables the use of the default memory map as a background region for privileged software accesses.

When enabled, the background region acts as a region number -1. Any region that is defined and enabled has priority over this default map.

If the MPU is disabled, the processor ignores this bit.

### • HFNMIENA: Hard Fault and NMI Enable

Enables the operation of MPU during hard fault, NMI, and FAULTMASK handlers.

When the MPU is enabled:

0: MPU is disabled during hard fault, NMI, and FAULTMASK handlers, regardless of the value of the ENABLE bit.

1: The MPU is enabled during hard fault, NMI, and FAULTMASK handlers.

When the MPU is disabled, if this bit is set to 1, the behavior is unpredictable.

### • ENABLE: MPU Enable

Enables the MPU:

0: MPU disabled.

1: MPU enabled.

When ENABLE and PRIVDEFENA are both set to 1:

- For privileged accesses, the *default memory map* is as described in "Memory Model". Any access by privileged software that does not address an enabled memory region behaves as defined by the default memory map.

- Any access by unprivileged software that does not address an enabled memory region causes a memory management fault.

### • SIZE: Size of the MPU Protection Region

The minimum permitted value is 3 (b00010).

The SIZE field defines the size of the MPU memory region specified by the MPU\_RNR. as follows:

(Region size in bytes) =  $2^{(SIZE+1)}$

The smallest permitted region size is 32B, corresponding to a SIZE value of 4. The table below gives an example of SIZE values, with the corresponding region size and value of N in the MPU\_RBAR.

| SIZE Value  | Region Size | Value of N <sup>(1)</sup> | Note                   |

|-------------|-------------|---------------------------|------------------------|

| b00100 (4)  | 32 B        | 5                         | Minimum permitted size |

| b01001 (9)  | 1 KB        | 10                        | _                      |

| b10011 (19) | 1 MB        | 20                        | -                      |

| b11101 (29) | 1 GB        | 30                        | _                      |

| b11111 (31) | 4 GB        | b01100                    | Maximum possible size  |

Note: 1. In the MPU\_RBAR; see "MPU Region Base Address Register"

### • ENABLE: Region Enable

Note: For information about access permission, see "MPU Access Permission Attributes".

### 0b11: Round towards Zero (RZ) mode.

The specified rounding mode is used by almost all floating-point instructions.

### • IDC: Input Denormal Cumulative Exception

IDC is a cumulative exception bit for floating-point exception; see also bits [4:0]. This bit is set to 1 to indicate that the corresponding exception has occurred since 0 was last written to it.

### • IXC: Inexact Cumulative Exception

IXC is a cumulative exception bit for floating-point exception; see also bit [7]. This bit is set to 1 to indicate that the corresponding exception has occurred since 0 was last written to it.

### UFC: Underflow Cumulative Exception

UFC is a cumulative exception bit for floating-point exception; see also bit [7]. This bit is set to 1 to indicate that the corresponding exception has occurred since 0 was last written to it.

### OFC: Overflow Cumulative Exception

OFC is a cumulative exception bit for floating-point exception; see also bit [7]. This bit is set to 1 to indicate that the corresponding exception has occurred since 0 was last written to it.

### • DZC: Division by Zero Cumulative Exception

DZC is a cumulative exception bit for floating-point exception; see also bit [7].

This bit is set to 1 to indicate that the corresponding exception has occurred since 0 was last written to it.

### IOC: Invalid Operation Cumulative Exception

IOC is a cumulative exception bit for floating-point exception; see also bit [7].

This bit is set to 1 to indicate that the corresponding exception has occurred since 0 was last written to it.

### 20.4.8.2 Brownout Detector Reset

The brownout detector provides the core voltage status signal (BODCORE\_out) to the SUPC which indicates that the voltage regulation is operating as programmed. If this signal is lost for longer than one slow clock period while the voltage regulator is enabled, the SUPC can assert a system reset signal. This feature is enabled by setting BODRSTEN in SUPC\_MR.

If BODRSTEN is set and the voltage regulation is lost (output voltage of the regulator too low), the system reset signal is asserted for a minimum of one slow clock cycle and then released if the core voltage status has been reactivated. The BODRSTS bit is set in SUPC\_SR, indicating the source of the last reset.

The system reset signal remains active as long as the core voltage status signal (BODCORE\_out) indicates a powerfail condition.

### 20.4.8.3 Power-on-Reset on VDDBU\_SW

The power-on-reset monitors VDDBU\_SW. It is active by default and monitors voltage at startup but also during powerdown. It can be deactivated by clearing the BUPPOREN bit in SUPC\_MR. If VDDBU\_SW goes below the threshold voltage, the chip is reset. Note that due to the automatic power switch, VDDBU\_SW can be either VDDIO or VDDBU.

### 20.4.9 Wakeup Sources

The wakeup events allow the device to exit Backup mode. When a wakeup event is detected, the SUPC performs a sequence which automatically reenables the core power supply.

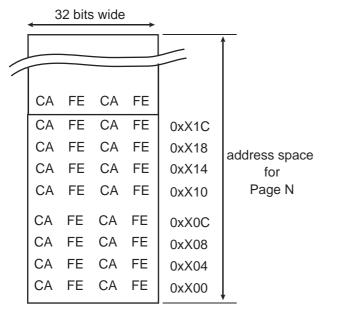

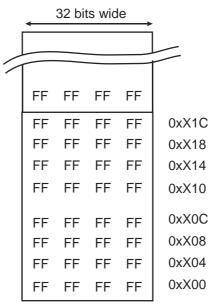

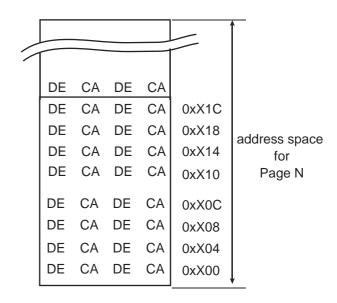

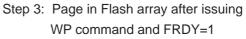

Figure 22-8. Full Page Programming

Before programming: Unerased page in Flash array

| DE | CA | DE | CA |       |               |

|----|----|----|----|-------|---------------|

| DE | CA | DE | CA | 0xX1C |               |

| DE | CA | DE | CA | 0xX18 | address space |

| DE | CA | DE | CA | 0xX14 | for           |

| DE | CA | DE | CA | 0xX10 | latch buffer  |

| DE | CA | DE | CA | 0xX0C |               |

| DE | CA | DE | CA | 0xX08 |               |

| DE | CA | DE | CA | 0xX04 |               |

| DE | CA | DE | CA | 0xX00 | ļ             |

Step 2: Writing a page in the latch buffer

Step 1: Flash array after page erase

| 24.5.9 Cache Controller Monitor Status Register |                |                |       |       |    |    |    |

|-------------------------------------------------|----------------|----------------|-------|-------|----|----|----|

| Name:                                           | CMCC_MSR       |                |       |       |    |    |    |

| Address:                                        | 0x4007C034 (0) | , 0x48018034 ( | 1)    |       |    |    |    |

| Access:                                         | Read-only      |                |       |       |    |    |    |

| 31                                              | 30             | 29             | 28    | 27    | 26 | 25 | 24 |

|                                                 |                |                | EVEN  | T_CNT |    |    |    |

| 23                                              | 22             | 21             | 20    | 19    | 18 | 17 | 16 |

|                                                 |                |                | EVEN. | T_CNT |    |    |    |

| 15                                              | 14             | 13             | 12    | 11    | 10 | 9  | 8  |

|                                                 | EVENT_CNT      |                |       |       |    |    |    |

| 7                                               | 6              | 5              | 4     | 3     | 2  | 1  | 0  |

|                                                 |                |                | EVEN  | T_CNT |    |    |    |

• EVENT\_CNT: Monitor Event Counter

### 27.11.3.2 Slow Clock Mode Transition

A Reload Configuration Wait State is also inserted when the Slow Clock mode is entered or exited, after the end of the current transfer (see Section 27.14 "Slow Clock Mode").

### 27.11.4 Read to Write Wait State

Due to an internal mechanism, a wait cycle is always inserted between consecutive read and write SMC accesses.

This wait cycle is referred to as a read to write wait state in this document.

This wait cycle is applied in addition to chip select and reload user configuration wait states when they are to be inserted. See Figure 27-15.

### 27.12 Data Float Wait States

Some memory devices are slow to release the external bus. For such devices, it is necessary to add wait states (data float wait states) after a read access:

- before starting a read access to a different external memory

- before starting a write access to the same device or to a different external one.

The Data Float Output Time ( $t_{DF}$ ) for each external memory device is programmed in the TDF\_CYCLES field of the SMC\_MODE register for the corresponding chip select. The value of TDF\_CYCLES indicates the number of data float wait cycles (between 0 and 15) before the external device releases the bus, and represents the time allowed for the data output to go to high impedance after the memory is disabled.

Data float wait states do not delay internal memory accesses. Hence, a single access to an external memory with long t<sub>DF</sub> will not slow down the execution of a program from internal memory.

The data float wait states management depends on the READ\_MODE and the TDF\_MODE fields of the SMC\_MODE register for the corresponding chip select.

### 27.12.1 READ\_MODE

Setting the READ\_MODE to 1 indicates to the SMC that the NRD signal is responsible for turning off the tri-state buffers of the external memory device. The Data Float Period then begins after the rising edge of the NRD signal and lasts TDF\_CYCLES MCK cycles.

When the read operation is controlled by the NCS signal (READ\_MODE = 0), the TDF field gives the number of MCK cycles during which the data bus remains busy after the rising edge of NCS.

Figure 27-19 illustrates the Data Float Period in NRD-controlled mode (READ\_MODE =1), assuming a data float period of 2 cycles (TDF\_CYCLES = 2). Figure 27-20 shows the read operation when controlled by NCS (READ\_MODE = 0) and the TDF\_CYCLES parameter equals 3.

### 28.5.3 Transmit Pointer Register

| Name:   | PERIPH_TPR |    |     |    |    |    |    |

|---------|------------|----|-----|----|----|----|----|

| Access: | Read/Write |    |     |    |    |    |    |

| 31      | 30         | 29 | 28  | 27 | 26 | 25 | 24 |

|         |            |    | TXF | ۲R |    |    |    |

| 23      | 22         | 21 | 20  | 19 | 18 | 17 | 16 |

|         |            |    | TXF | ۲R |    |    |    |

| 15      | 14         | 13 | 12  | 11 | 10 | 9  | 8  |

|         | TXPTR      |    |     |    |    |    |    |

| 7       | 6          | 5  | 4   | 3  | 2  | 1  | 0  |

|         | TXPTR      |    |     |    |    |    |    |

### • TXPTR: Transmit Counter Register

TXPTR must be set to transmit buffer address.

When a half-duplex peripheral is connected to the PDC, RXPTR = TXPTR.

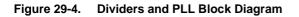

### 29.6.1 Divider and Phase Lock Loop Programming

The divider can be set between 1 and 255 in steps of 1. When a divider field (DIV) is cleared, the output of the corresponding divider and the PLL output is a continuous signal at level 0. On reset, each DIV field is cleared, thus the corresponding PLL input clock is stuck at 0.

The PLLs (PLLA, PLLB) allow multiplication of the SLCK clock source for PLLA or divided MAINCK or PLLA output clock for PLLB. The PLL clock signal has a frequency that depends on the respective source signal frequency and on the parameters DIV (, DIVB) and MUL (MULA, MULB) and PLLEN (PLLAEN). The factor applied to the source signal frequency is (MUL + 1)/DIV. When MUL is written to 0 or PLLEN = 0, the PLL is disabled and its power consumption is saved. Note that there is a delay of two SLCK clock cycles between the disable command and the real disable of the PLL. Re-enabling the PLL can be performed by writing a value higher than 0 in the MUL field and PLLA(B)EN higher than 0.

To change the frequency of the PLLA, the PLLA must be first disabled by writing 0 in the MULA field and 0 in PLLACOUNT field. Then, wait for two SLCK clock cycles before configuring the PLLA to generate the new frequency by programming a new multiplier in MULA and the PLLACOUNT field in the same register access. See Section 46. "Electrical Characteristics" to get the PLLACOUNT values covering the PLL transient time.

Whenever the PLL is re-enabled or one of its parameters is changed, the LOCK (LOCKA, LOCKB) bit in PMC\_SR is automatically cleared. The values written in the PLLCOUNT field (PLLACOUNT, PLLBCOUNT) in CKGR\_PLLR (CKGR\_PLLAR, CKGR\_PLLBR) are loaded in the PLL counter. The PLL counter then decrements at the speed of the slow clock until it reaches 0. At this time, the LOCK bit is set in PMC\_SR and can trigger an interrupt to the

# Atmel

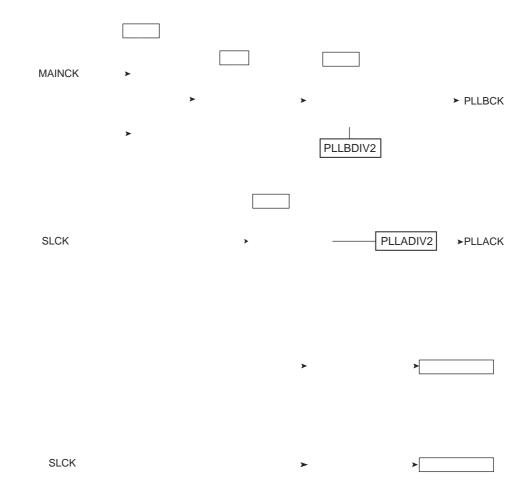

Figure 34-17. TWI Write Operation with Multiple Data Bytes with or without Internal Address

### 34.8.2 TWI Master Mode Register

| Name:    | TWI_MMR                        |    |       |    |    |     |     |  |

|----------|--------------------------------|----|-------|----|----|-----|-----|--|

| Address: | 0x40018004 (0), 0x4001C004 (1) |    |       |    |    |     |     |  |

| Access:  | Read/Write                     |    |       |    |    |     |     |  |

| 31       | 30                             | 29 | 28    | 27 | 26 | 25  | 24  |  |

| _        | -                              | -  | -     | _  | -  | -   | -   |  |

| 23       | 22                             | 21 | 20    | 19 | 18 | 17  | 16  |  |

| _        | DADR                           |    |       |    |    |     |     |  |

| 15       | 14                             | 13 | 12    | 11 | 10 | 9   | 8   |  |

| -        | -                              | —  | MREAD | -  | _  | IAD | RSZ |  |

| 7        | 6                              | 5  | 4     | 3  | 2  | 1   | 0   |  |

| _        | _                              | _  | _     | _  | _  | _   | _   |  |

### • IADRSZ: Internal Device Address Size

| Value | Name   | escription                         |  |

|-------|--------|------------------------------------|--|

| 0     | NONE   | o internal device address          |  |

| 1     | 1_BYTE | One-byte internal device address   |  |

| 2     | 2_BYTE | Two-byte internal device address   |  |

| 3     | 3_BYTE | Three-byte internal device address |  |

### • MREAD: Master Read Direction

0: Master write direction.

1: Master read direction.

### • DADR: Device Address

The device address is used to access slave devices in Read or Write mode. These bits are only used in Master mode.

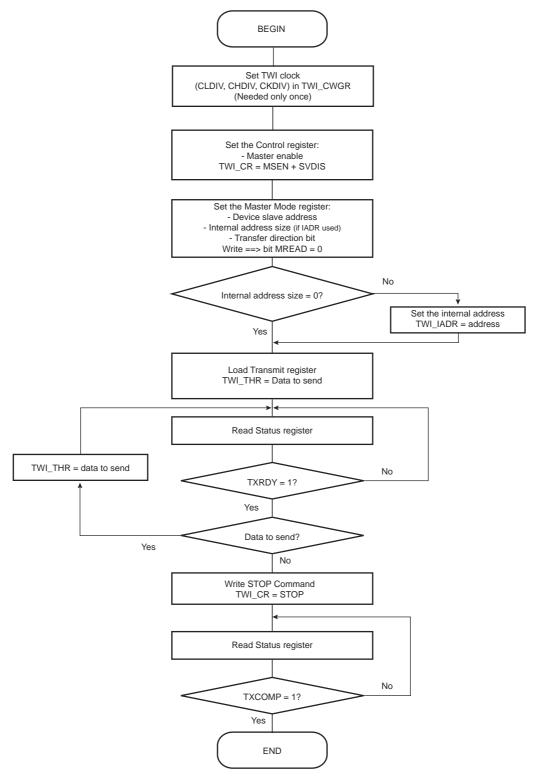

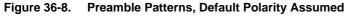

The Manchester encoded character can also be encapsulated by adding both a configurable preamble and a start frame delimiter pattern. Depending on the configuration, the preamble is a training sequence, composed of a predefined pattern with a programmable length from 1 to 15 bit times. If the preamble length is set to 0, the preamble waveform is not generated prior to any character. The preamble pattern is chosen among the following sequences: ALL\_ONE, ALL\_ZERO, ONE\_ZERO or ZERO\_ONE, writing the field TX\_PP in the US\_MAN register, the field TX\_PL is used to configure the preamble length. Figure 36-8 illustrates and defines the valid patterns. To improve flexibility, the encoding scheme can be configured using the TX\_MPOL field in the US\_MAN register. If the TX\_MPOL field is set to zero (default), a logic zero is encoded with a zero-to-one transition and a logic one is encoded with a one-to-zero transition. If the TX\_MPOL field is set to 1, a logic one is encoded with a one-to-zero transition.

8-bit width "ONE\_ZERO" Preamble

A start frame delimiter is to be configured using the ONEBIT bit in the US\_MR. It consists of a user-defined pattern that indicates the beginning of a valid data. Figure 36-9 illustrates these patterns. If the start frame delimiter, also known as the start bit, is one bit, (ONEBIT = 1), a logic zero is Manchester encoded and indicates that a new character is being sent serially on the line. If the start frame delimiter is a synchronization pattern also referred to as sync (ONE BIT to 0), a sequence of three bit times is sent serially on the line to indicate the start of a new character. The sync waveform is in itself an invalid Manchester waveform as the transition occurs at the middle of the second bit time. Two distinct sync patterns are used: the command sync and the data sync. The command sync has a logic one level for one and a half bit times, then a transition to logic zero for the second one and a half bit times. If the MODSYNC bit in the US\_MR is set to 1, the next character is a command. If it is set to 0, the next character is a data. When direct memory access is used, the MODSYNC field can be immediately updated with a modified character located in memory. To enable this mode, VAR\_SYNC bit in US\_MR must be set to 1. In this case, the MODSYNC bit in the US\_MR is bypassed and the sync configuration is held in the TXSYNH in the US\_THR. The USART character format is modified and includes sync information.

# Atmel

The USART cannot operate concurrently in both Receiver and Transmitter modes as the communication is unidirectional at a time. It has to be configured according to the required mode by enabling or disabling either the receiver or the transmitter as desired. Enabling both the receiver and the transmitter at the same time in ISO7816 mode may lead to unpredictable results.

The ISO7816 specification defines an inverse transmission format. Data bits of the character must be transmitted on the I/O line at their negative value.

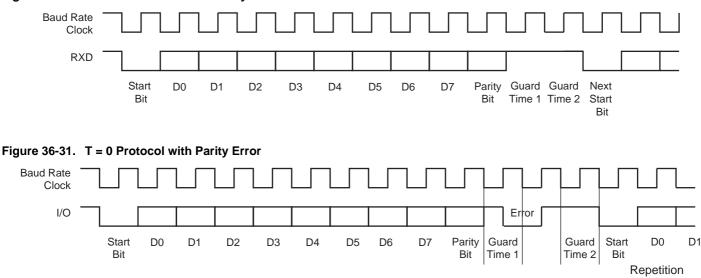

### 36.6.4.2 Protocol T = 0

In T = 0 protocol, a character is made up of one start bit, eight data bits, one parity bit and one guard time, which lasts two bit times. The transmitter shifts out the bits and does not drive the I/O line during the guard time.

If no parity error is detected, the I/O line remains at 1 during the guard time and the transmitter can continue with the transmission of the next character, as shown in Figure 36-30.

If a parity error is detected by the receiver, it drives the I/O line to 0 during the guard time, as shown in Figure 36-31. This error bit is also named NACK, for Non Acknowledge. In this case, the character lasts 1 bit time more, as the guard time length is the same and is added to the error bit time which lasts 1 bit time.

When the USART is the receiver and it detects an error, it does not load the erroneous character in the Receive Holding register (US\_RHR). It appropriately sets the PARE bit in the Status register (US\_SR) so that the software can handle the error.

### Figure 36-30. T = 0 Protocol without Parity Error

#### **Receive Error Counter**

The USART receiver also records the total number of errors. This can be read in the Number of Error (US\_NER) register. The NB\_ERRORS field can record up to 255 errors. Reading US\_NER automatically clears the NB\_ERRORS field.

### **Receive NACK Inhibit**

The USART can also be configured to inhibit an error. This can be achieved by setting the INACK bit in US\_MR. If INACK is to 1, no error signal is driven on the I/O line even if a parity bit is detected.

Moreover, if INACK is set, the erroneous received character is stored in the Receive Holding register, as if no error occurred and the RXRDY bit does rise.

To receive IrDA signals, the following needs to be done:

- Disable TX and Enable RX

- Configure the TXD pin as PIO and set it as an output to 0 (to avoid LED emission). Disable the internal pullup (better for power consumption).

- Receive data

### 36.6.5.1 IrDA Modulation

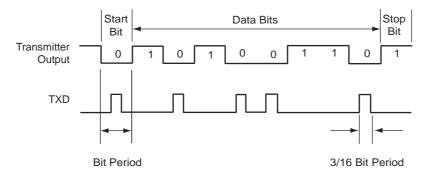

For baud rates up to and including 115.2 kbit/s, the RZI modulation scheme is used. "0" is represented by a light pulse of 3/16th of a bit time. Some examples of signal pulse duration are shown in Table 36-11.

| Baud Rate    | Pulse Duration (3/16) |

|--------------|-----------------------|

| 2.4 kbit/s   | 78.13 µs              |

| 9.6 kbit/s   | 19.53 µs              |

| 19.2 kbit/s  | 9.77 µs               |

| 38.4 kbit/s  | 4.88 µs               |

| 57.6 kbit/s  | 3.26 µs               |

| 115.2 kbit/s | 1.63 µs               |

### Table 36-11. IrDA Pulse Duration

Figure 36-33 shows an example of character transmission.

### Figure 36-33. IrDA Modulation

### 36.6.5.2 IrDA Baud Rate

Table 36-12 gives some examples of CD values, baud rate error and pulse duration. Note that the requirement on the maximum acceptable error of  $\pm 1.87\%$  must be met.

| Peripheral Clock | Baud Rate (bit/s) | CD | Baud Rate Error | Pulse Time (µs) |  |  |  |

|------------------|-------------------|----|-----------------|-----------------|--|--|--|

| 3,686,400        | 115,200           | 2  | 0.00%           | 1.63            |  |  |  |

| 20,000,000       | 115,200           | 11 | 1.38%           | 1.63            |  |  |  |

| 32,768,000       | 115,200           | 18 | 1.25%           | 1.63            |  |  |  |

| 40,000,000       | 115,200           | 22 | 1.38%           | 1.63            |  |  |  |

| 3,686,400        | 57,600            | 4  | 0.00%           | 3.26            |  |  |  |

| 20,000,000       | 57,600            | 22 | 1.38%           | 3.26            |  |  |  |

| 32,768,000       | 57,600            | 36 | 1.25%           | 3.26            |  |  |  |

| 40,000,000       | 57,600            | 43 | 0.93%           | 3.26            |  |  |  |

### Table 36-12. IrDA Baud Rate Error

### 37. Timer Counter (TC)

### 37.1 Description

A Timer Counter (TC) module includes three identical TC channels. The number of implemented TC modules is device-specific.

Each TC channel can be independently programmed to perform a wide range of functions including frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse width modulation.

Each channel has three external clock inputs, five internal clock inputs and two multi-purpose input/output signals which can be configured by the user. Each channel drives an internal interrupt signal which can be programmed to generate processor interrupts.

The TC embeds a quadrature decoder (QDEC) connected in front of the timers and driven by TIOA0, TIOB0 and TIOB1 inputs. When enabled, the QDEC performs the input lines filtering, decoding of quadrature signals and connects to the timers/counters in order to read the position and speed of the motor through the user interface.

The TC block has two global registers which act upon all TC channels:

- Block Control Register (TC\_BCR)—allows channels to be started simultaneously with the same instruction

- Block Mode Register (TC\_BMR)—defines the external clock inputs for each channel, allowing them to be chained

### 37.2 Embedded Characteristics

- Total number of TC channels: three

- TC channel size: 16-bit

- Wide range of functions including:

- Frequency measurement

- Event counting

- Interval measurement

- Pulse generation

- Delay timing

- Pulse Width Modulation

- Up/down capabilities

- Quadrature decoder

- 2-bit gray up/down count for stepper motor

- Each channel is user-configurable and contains:

- Three external clock inputs

- Five Internal clock inputs

- Two multi-purpose input/output signals acting as trigger event

- Internal interrupt signal

- Register Write Protection

### 37.7.10 TC Interrupt Enable Register

Name: TC\_IERx [x=0..2]

Address: 0x40010024 (0)[0], 0x40010064 (0)[1], 0x400100A4 (0)[2], 0x40014024 (1)[0], 0x40014064 (1)[1], 0x400140A4 (1)[2]

| Access: | Write-only |       |      |         |      |       |       |

|---------|------------|-------|------|---------|------|-------|-------|

| 31      | 30         | 29    | 28   | 27      | 26   | 25    | 24    |

| -       | _          | -     | _    | —       | —    | —     | -     |

| 23      | 22         | 21    | 20   | 19      | 18   | 17    | 16    |

| -       | -          | -     | -    | -       | -    | -     | -     |

| 15      | 14         | 13    | 12   | 11      | 10   | 9     | 8     |

| 15      | 1          | 13    | 12   | 11<br>i | 10   | 9     | °     |

|         | _          | _     | _    | _       | -    | _     | –     |

| 7       | 6          | 5     | 4    | 3       | 2    | 1     | 0     |

| ETRGS   | LDRBS      | LDRAS | CPCS | CPBS    | CPAS | LOVRS | COVFS |

### COVFS: Counter Overflow

0: No effect.

1: Enables the Counter Overflow Interrupt.

### • LOVRS: Load Overrun

0: No effect.

1: Enables the Load Overrun Interrupt.

### • CPAS: RA Compare

0: No effect.

1: Enables the RA Compare Interrupt.

### • CPBS: RB Compare

0: No effect.

1: Enables the RB Compare Interrupt.

### • CPCS: RC Compare

0: No effect.

1: Enables the RC Compare Interrupt.

### • LDRAS: RA Loading

0: No effect.

1: Enables the RA Load Interrupt.

### • LDRBS: RB Loading

0: No effect.

1: Enables the RB Load Interrupt.

### Table 55-2. SAM4CM Datasheet Rev. 11203D Revision History

| Doc. Rev.<br>11203D   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Section 35. "Universal Asynchronous Receiver Transmitter (UART)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | Modified Figure 35-2 "Baud Rate Generator"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | Section 35.6.9 "UART Baud Rate Generator Register": updated CD bit description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | Section 36. "Universal Synchronous Asynchronous Receiver Transceiver (USART)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       | Removed all references to bit RXIDLEV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       | Updated Section 36.5.1 "I/O Lines", Section 36.6.1 "Baud Rate Generator", Section 36.6.3.15 "Hardware Handshaking", Section 36.6.9 "Register Write Protection"                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | Section 36.7.1 "USART Control Register", Section 36.7.3 "USART Mode Register", Section 36.7.6 "USART Interrupt<br>Enable Register (SPI_MODE)", Section 36.7.8 "USART Interrupt Disable Register (SPI_MODE)", Section 36.7.10 "USART<br>Interrupt Mask Register (SPI_MODE)", Section 36.7.11 "USART Channel Status Register", Section 36.7.12 "USART<br>Channel Status Register (SPI_MODE)", Section 36.7.15 "USART Baud Rate Generator Register", Section 36.7.16<br>"USART Receiver Time-out Register", Section 36.7.17 "USART Transmitter Timeguard Register": updated bit descriptions |

|                       | Updated Table 36-14 "Register Mapping"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       | Section 37. "Timer Counter (TC)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | Updated Section 37.1 "Description", Section 37.5.2 "Power Management", Section 37.5.3 "Interrupt Sources", Section 37.6.14.4 "Position and Rotation Measurement", Section 37.6.14.5 "Speed Measurement" and Section 37.6.16 "Register Write Protection"                                                                                                                                                                                                                                                                                                                                   |

|                       | Section 37.6.14 "Quadrature Decoder": removed subsection "Missing Pulse Detection and Auto-correction"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 27-Mar-15<br>(cont'd) | Section 37.7.2 "TC Channel Mode Register: Capture Mode": in 'Name' line, replaced "(WAVE = 0)" with<br>"(CAPTURE_MODE)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                       | Section 37.7.3 "TC Channel Mode Register: Waveform Mode": in 'Name' line, replaced "(WAVE = 1)" with<br>"(WAVEFORM_MODE)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (,                    | Section 37.7.5 "TC Counter Value Register", Section 37.7.6 "TC Register A", Section 37.7.7 "TC Register B", Section 37.7.8 "TC Register C": added 'IMPORTANT' note                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | Section 37.7.9 "TC Status Register", Section 37.7.19 "TC Write Protection Mode Register": updated bit descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | Section 37.7.14 "TC Block Mode Register": removed AUTOC bit and MAXCMP field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | Section 37.7.18 "TC QDEC Interrupt Status Register": removed MPE bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | Section 42. "Advanced Encryption Standard (AES)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | Added Section 42.4.1 "AES Register Endianism"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       | Section 42.5.6 "AES Interrupt Status Register": updated bit descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       | Section 43. "Integrity Check Monitor (ICM)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Updated Section 43.5.1 "Overview", Section 43.5.4 "Using ICM as SHA Engine"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Section 43.5.2.2 "ICM Region Configuration Structure Member", Section 43.6.1 "ICM Configuration Register", Section 43.6.3 "ICM Status Register": updated bit descriptions                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | Section 45. "True Random Number Generator (TRNG)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                       | Updated Section 45.5 "Functional Description" and Table 45-2 "Register Mapping"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                       | Section 46. "Electrical Characteristics"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       | Updated Table 46-1 "Absolute Maximum Ratings*" and Table 46-3 "Recommended Operating Conditions on Input Pins"                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | Updated Figure 46-19 "Typical Current Consumption in Backup Mode for Configurations C and D"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | Added footnotes <sup>(4)</sup> and <sup>(5)</sup> in Table 46-5 "I/O DC Characteristics"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       | Updated VDDIN min. value in Table 46-41 "Programmable Voltage Reference Characteristics"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |