#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M4F                                                         |

| Core Size                  | 32-Bit Dual-Core                                                            |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                             |

| Number of I/O              | 57                                                                          |

| Program Memory Size        | 2MB (2M x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 256K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                |

| Data Converters            | A/D 6x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-LQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4cms32cb-aur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.3 System State at Power-up

## 5.3.1 Device Configuration after the First Power-up

At the first power-up, the SAM4CM boots from the ROM. The device configuration is defined by the SAM-BA boot program.

## 5.3.2 Device Configuration after a Power Cycle when Booting from Flash Memory

After a power cycle of all the power supply rails, the system peripherals, such as the Flash Controller, the Clock Generator, the Power Management Controller and the Supply Controller, are in the following states:

- Slow Clock (SLCK) source is the internal 32 kHz RC Oscillator (32 kHz crystal oscillator is disabled)

- Main Clock (MAINCK) source is set to the 4 MHz internal RC Oscillator

- 3–20 MHz crystal oscillator and PLLs are disabled

- Core Brownout Detector and Core Reset are enabled

- Backup Power-on-reset is enabled

- VDDIO Supply Monitor is disabled

- Flash Wait State (FWS) bit in the EEFC Flash Mode Register is set to 0

- Core 0 Cache Controller (CMCC0) is enabled (only used if the application link address for the Core 0 is 0x11000000)

- Sub-system 1 is in the reset state and not clocked

## 5.3.3 Device Configuration after a Reset

After a reset or a wake-up from Backup mode, the following system peripherals default to the same state as after a power cycle:

- Main Clock (MAINCK) source is set to the 4 MHz internal RC oscillator

- 3-20 MHz crystal oscillator and PLLs are disabled

- Flash Wait State (FWS) bit in the EEFC Flash Mode Register is set to 0

- Core 0 Cache Controller (CMCC0) is enabled (only used if the application link address for the Core 0 is 0x11000000)

- Sub-system 1 is in the reset state and not clocked

The states of the other peripherals are saved in the backup area managed by the Supply Controller as long as VDDBU is maintained during device reset:

- Slow Clock (SLCK) source selection is written in SUPC\_CR.XTALSEL.

- Core Brownout Detector enable/disable is written in SUPC\_MR.BODDIS.

- Backup Power-on-reset enable/disable is written in the SUPC\_MR.BUPPOREN.

- VDDIO Supply Monitor mode is written in the SUPC\_SMMR.

# 5.4 Active Mode

Active mode is the normal running mode, with the single core or the dual cores executing code. The system clock can be the fast RC oscillator, the main crystal oscillator or the PLLs. The Power Management Controller (PMC) can be used to adapt the frequency and to disable the peripheral clocks when unused.

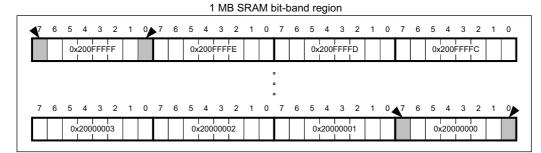

- The alias word at 0x22000000 maps to bit[0] of the bit-band byte at 0x20000000: 0x22000000 = 0x22000000 + (0\*32) + (0\*4).

- The alias word at 0x2200001C maps to bit[7] of the bit-band byte at 0x20000000: 0x2200001C = 0x2200000+ (0\*32) + (7\*4).

### Figure 12-4. Bit-band Mapping

|            |            |            | 32 MB                                 | alias region |                                       |            |            |

|------------|------------|------------|---------------------------------------|--------------|---------------------------------------|------------|------------|

|            |            | <u> </u>   | · · · · · · · · · · · · · · · · · · · |              | · · · · · · · · · · · · · · · · · · · |            |            |

| 0x23FFFFFC | 0x23FFFFF8 | 0x23FFFFF4 | 0x23FFFFF0                            | 0x23FFFFEC   | 0x23FFFFE8                            | 0x23FFFFE4 | 0x23FFFFE0 |

| ✓          |            |            |                                       |              |                                       |            | <          |

|            |            |            |                                       | 0            |                                       |            |            |

|            |            |            |                                       | 0            |                                       |            |            |

|            | -          |            |                                       |              |                                       |            |            |

| 0x2200001C | 0x22000018 | 0x22000014 | 0x22000010                            | 0x2200000C   | 0x22000008                            | 0x22000004 | 0x22000000 |

|            |            |            |                                       |              |                                       |            |            |

#### Directly Accessing an Alias Region

Writing to a word in the alias region updates a single bit in the bit-band region.

Bit[0] of the value written to a word in the alias region determines the value written to the targeted bit in the bitband region. Writing a value with bit[0] set to 1 writes a 1 to the bit-band bit, and writing a value with bit[0] set to 0 writes a 0 to the bit-band bit.

Bits[31:1] of the alias word have no effect on the bit-band bit. Writing 0x01 has the same effect as writing 0xFF. Writing 0x00 has the same effect as writing 0x0E.

Reading a word in the alias region:

- 0x00000000 indicates that the targeted bit in the bit-band region is set to 0

- 0x00000001 indicates that the targeted bit in the bit-band region is set to 1

#### Directly Accessing a Bit-band Region

"Behavior of Memory Accesses" describes the behavior of direct byte, halfword, or word accesses to the bit-band regions.

#### 12.4.2.6 Memory Endianness

The processor views memory as a linear collection of bytes numbered in ascending order from zero. For example, bytes 0–3 hold the first stored word, and bytes 4–7 hold the second stored word. "Little-endian Format" describes how words of data are stored in memory.

## Little-endian Format

In little-endian format, the processor stores the least significant byte of a word at the lowest-numbered byte, and the most significant byte at the highest-numbered byte. For example:

## 12.9.1.8 System Handler Priority Registers

The SCB\_SHPR1–SCB\_SHPR3 registers set the priority level, 0 to 15 of the exception handlers that have configurable priority. They are byte-accessible.

The system fault handlers and the priority field and register for each handler are:

## Table 12-34. System Fault Handler Priority Fields

| Handler                             | Field  | Register Description               |

|-------------------------------------|--------|------------------------------------|

| Memory management fault (MemManage) | PRI_4  |                                    |

| Bus fault (BusFault)                | PRI_5  | System Handler Priority Register 1 |

| Usage fault (UsageFault)            | PRI_6  |                                    |

| SVCall                              | PRI_11 | System Handler Priority Register 2 |

| PendSV                              | PRI_14 | System Handler Driggity Desigter 2 |

| SysTick                             | PRI_15 | System Handler Priority Register 3 |

Each PRI\_N field is 8 bits wide, but the processor implements only bits [7:4] of each field, and bits [3:0] read as zero and ignore writes.

## • SIZE: Size of the MPU Protection Region

The minimum permitted value is 3 (b00010).

The SIZE field defines the size of the MPU memory region specified by the MPU\_RNR. as follows:

(Region size in bytes) =  $2^{(SIZE+1)}$

The smallest permitted region size is 32B, corresponding to a SIZE value of 4. The table below gives an example of SIZE values, with the corresponding region size and value of N in the MPU\_RBAR.

| SIZE Value  | Region Size | Value of N <sup>(1)</sup> | Note                   |

|-------------|-------------|---------------------------|------------------------|

| b00100 (4)  | 32 B        | 5                         | Minimum permitted size |

| b01001 (9)  | 1 KB        | 10                        | _                      |

| b10011 (19) | 1 MB        | 20                        | -                      |

| b11101 (29) | 1 GB        | 30                        | _                      |

| b11111 (31) | 4 GB        | b01100                    | Maximum possible size  |

Note: 1. In the MPU\_RBAR; see "MPU Region Base Address Register"

## • ENABLE: Region Enable

Note: For information about access permission, see "MPU Access Permission Attributes".

# 20.6.4 Supply Controller Supply Monitor Mode Register

| Name:    | SUPC_SMMR  |       |         |    |    |        |    |

|----------|------------|-------|---------|----|----|--------|----|

| Address: | 0x400E1414 |       |         |    |    |        |    |

| Access:  | Read/Write |       |         |    |    |        |    |

| 31       | 30         | 29    | 28      | 27 | 26 | 25     | 24 |

| -        | -          | _     | -       | -  | -  | -      | -  |

|          | -          |       | -       |    | -  |        |    |

| 23       | 22         | 21    | 20      | 19 | 18 | 17     | 16 |

| -        | -          | _     | -       | -  | —  | -      | -  |

|          | -          |       | -       |    | -  |        |    |

| 15       | 14         | 13    | 12      | 11 | 10 | 9      | 8  |

| -        | -          | SMIEN | SMRSTEN | -  |    | SMSMPL |    |

|          |            |       |         |    |    |        |    |

| 7        | 6          | 5     | 4       | 3  | 2  | 1      | 0  |

| -        | -          | _     | _       |    | SM | ITH    |    |

This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC\_WPMR).

### • SMTH: Supply Monitor Threshold

Selects the threshold voltage of the supply monitor. Refer to the section "Electrical Characteristics" for voltage values.

### • SMSMPL: Supply Monitor Sampling Period

| Value | Name     | Description                                                     |

|-------|----------|-----------------------------------------------------------------|

| 0     | SMD      | Supply Monitor disabled                                         |

| 1     | CSM      | Continuous Supply Monitor                                       |

| 2     | 32SLCK   | Supply Monitor enabled one SLCK period every 32 SLCK periods    |

| 3     | 256SLCK  | Supply Monitor enabled one SLCK period every 256 SLCK periods   |

| 4     | 2048SLCK | Supply Monitor enabled one SLCK period every 2,048 SLCK periods |

#### • SMRSTEN: Supply Monitor Reset Enable

0 (NOT\_ENABLE): The system reset signal is not affected when a supply monitor detection occurs.

1 (ENABLE): The system reset signal is asserted when a supply monitor detection occurs.

#### SMIEN: Supply Monitor Interrupt Enable

0 (NOT\_ENABLE): The SUPC interrupt signal is not affected when a supply monitor detection occurs.

1 (ENABLE): The SUPC interrupt signal is asserted when a supply monitor detection occurs.

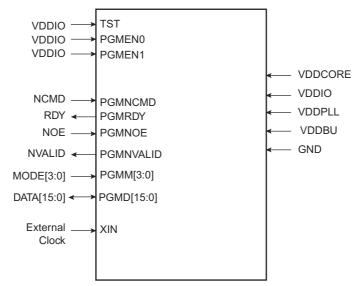

# 23. Fast Flash Programming Interface (FFPI)

# 23.1 Description

The Fast Flash Programming Interface (FFPI) provides parallel high-volume programming using a standard gang programmer. The parallel interface is fully handshaked and the device is considered to be a standard EEPROM. Additionally, the parallel protocol offers an optimized access to all the embedded Flash functionalities.

Although the Fast Flash Programming mode is a dedicated mode for high volume programming, this mode is not designed for in-situ programming.

## 23.2 Embedded Characteristics

- Programming Mode for High-volume Flash Programming Using Gang Programmer

- Offers Read and Write Access to the Flash Memory Plane

- Enables Control of Lock Bits and General-purpose NVM Bits

- Enables Security Bit Activation

- Disabled Once Security Bit is Set

- Parallel Fast Flash Programming Interface

- Provides an 16-bit Parallel Interface to Program the Embedded Flash

- Full Handshake Protocol

# 23.3 Parallel Fast Flash Programming

#### 23.3.1 Device Configuration

In Fast Flash Programming mode, the device is in a specific test mode. Only a certain set of pins is significant. The rest of the PIOs are used as inputs with a pull-up. The crystal oscillator is in bypass mode. Other pins must be left unconnected.

#### Figure 23-1. 16-bit Parallel Programming Interface

# 25.5.4 IPC Interrupt Enable Command Register

| Name:    | IPC_IECR       |              |       |       |       |       |       |

|----------|----------------|--------------|-------|-------|-------|-------|-------|

| Address: | 0x4004C00C (0) | , 0x4801400C | (1)   |       |       |       |       |

| Access:  | Write-only     |              |       |       |       |       |       |

| 31       | 30             | 29           | 28    | 27    | 26    | 25    | 24    |

| IRQ31    | IRQ30          | IRQ29        | IRQ28 | IRQ27 | IRQ26 | IRQ25 | IRQ24 |

| 23       | 22             | 21           | 20    | 19    | 18    | 17    | 16    |

| IRQ23    | IRQ22          | IRQ21        | IRQ20 | IRQ19 | IRQ18 | IRQ17 | IRQ16 |

| 15       | 14             | 13           | 12    | 11    | 10    | 9     | 8     |

| IRQ15    | IRQ14          | IRQ13        | IRQ12 | IRQ11 | IRQ10 | IRQ9  | IRQ8  |

| 7        | 6              | 5            | 4     | 3     | 2     | 1     | 0     |

| IRQ7     | IRQ6           | IRQ5         | IRQ4  | IRQ3  | IRQ2  | IRQ1  | IRQ0  |

## • IRQ0-IRQ31: Interrupt Enable

0: No effect.

1: Enables the corresponding interrupt.

## 30.18.5 PMC Peripheral Clock Disable Register 0

| Name:               | PMC_PCDR0                |             |             |             |             |             |             |

|---------------------|--------------------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Address:<br>Access: | 0x400E0414<br>Write-only |             |             |             |             |             |             |

| 31                  | 30                       | 29          | 28          | 27          | 26          | 25          | 24          |

| PID31               | _                        | PID29       | PID28       | PID27       | PID26       | PID25       | PID24       |

| 23<br>PID23         | 22<br>PID22              | 21<br>PID21 | 20<br>PID20 | 19<br>PID19 | 18<br>PID18 | 17<br>PID17 | 16<br>PID16 |

| 15<br>PID15         | 14<br>PID14              | 13<br>PID13 | 12<br>PID12 | 11<br>PID11 | 10<br>PID10 | 9<br>PID9   | 8<br>PID8   |

| 7                   | 6                        | 5           | 4           | 3           | 2           | 1           | 0           |

|                     | -                        | —           | _           | _           | _           | _           | —           |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

## • PIDx: Peripheral Clock x Disable

0: No effect.

1: Disables the corresponding peripheral clock.

Note: PIDx refers to identifiers defined in the section "Peripheral Identifiers". Other peripherals can be disabled in PMC\_PCDR1 (Section 30.18.24 "PMC Peripheral Clock Disable Register 1").

| 30.10.7 FIN | S CIUCK Generalu |         | lor Register |          |          |          |          |

|-------------|------------------|---------|--------------|----------|----------|----------|----------|

| Name:       | CKGR_MOR         |         |              |          |          |          |          |

| Address:    | 0x400E0420       |         |              |          |          |          |          |

| Access:     | Read/Write       |         |              |          |          |          |          |

| 31          | 30               | 29      | 28           | 27       | 26       | 25       | 24       |

| -           | -                | —       | —            | -        | XT32KFME | CFDEN    | MOSCSEL  |

| 23          | 22               | 21      | 20           | 19       | 18       | 17       | 16       |

|             |                  |         | К            | EY       |          |          |          |

| 15          | 14               | 13      | 12           | 11       | 10       | 9        | 8        |

|             |                  |         | MOS          | CXTST    |          |          |          |

| 7           | 6                | 5       | 4            | 3        | 2        | 1        | 0        |

| _           |                  | MOSCRCF |              | MOSCRCEN | WAITMODE | MOSCXTBY | MOSCXTEN |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

# MOSCXTEN: 3 to 20 MHz Crystal Oscillator Enable

30 18 7 PMC Clock Generator Main Oscillator Register

A crystal must be connected between XIN and XOUT.

0: The 3 to 20 MHz crystal oscillator is disabled.

1: The 3 to 20 MHz crystal oscillator is enabled. MOSCXTBY must be cleared.

When MOSCXTEN is set, the MOSCXTS flag is set once the crystal oscillator start-up time is achieved.

## • MOSCXTBY: 3 to 20 MHz Crystal Oscillator Bypass

0: No effect.

1: The 3 to 20 MHz crystal oscillator is bypassed. MOSCXTEN must be cleared. An external clock must be connected on XIN.

When MOSCXTBY is set, the MOSCXTS flag in PMC\_SR is automatically set.

Clearing MOSCXTEN and MOSCXTBY bits resets the MOSCXTS flag.

Note: When the crystal oscillator bypass is disabled (MOSCXTBY = 0), the MOSCXTS flag must be read at 0 in PMC\_SR before enabling the crystal oscillator (MOSCXTEN = 1).

## • WAITMODE: Wait Mode Command (Write-only)

0: No effect.

1: Puts the device in Wait mode.

## • MOSCRCEN: 4/8/12 MHz RC Oscillator Enable

0: The 4/8/12 MHz RC oscillator is disabled.

1: The 4/8/12 MHz RC oscillator is enabled.

When MOSCRCEN is set, the MOSCRCS flag is set once the RC oscillator start-up time is achieved.

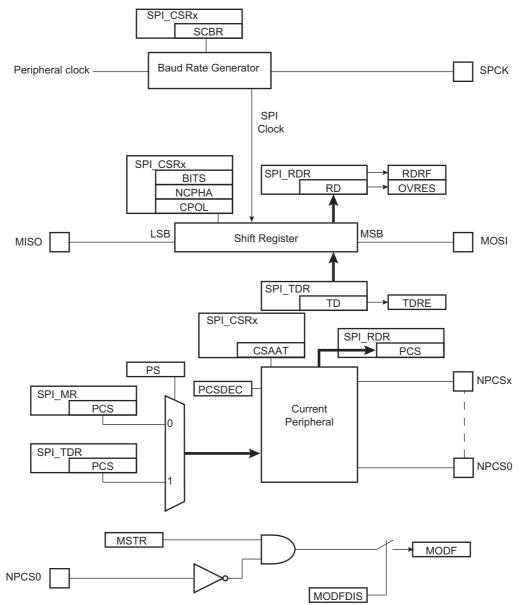

#### 33.7.3.1 Master Mode Block Diagram

#### 33.7.3.10 Mode Fault Detection

The SPI has the capability to operate in multi-master environment. Consequently, the NPCS0/NSS line must be monitored. If one of the masters on the SPI bus is currently transmitting, the NPCS0/NSS line is low and the SPI must not transmit any data. A mode fault is detected when the SPI is programmed in Master mode and a low level is driven by an external master on the NPCS0/NSS signal. In multi-master environment, NPCS0, MOSI, MISO and SPCK pins must be configured in open drain (through the PIO controller). When a mode fault is detected, the SPI\_SR.MODF bit is set until SPI\_SR is read and the SPI is automatically disabled until it is re-enabled by writing a 1 to the SPI\_CR.SPIEN bit.

By default, the mode fault detection is enabled. The user can disable it by setting the SPI\_MR.MODFDIS bit.

## 33.7.4 SPI Slave Mode

When operating in Slave mode, the SPI processes data bits on the clock provided on the SPI clock pin (SPCK).

The SPI waits until NSS goes active before receiving the serial clock from an external master. When NSS falls, the clock is validated and the data is loaded in the SPI\_RDR depending on the BITS field configured in the SPI\_CSR0. These bits are processed following a phase and a polarity defined respectively by the NCPHA and CPOL bits in the SPI\_CSR0. Note that BITS, CPOL and NCPHA of the other Chip Select registers have no effect when the SPI is programmed in Slave mode.

The bits are shifted out on the MISO line and sampled on the MOSI line.

Note: For more information on the BITS field, see also the note below the SPI\_CSRx register bitmap (Section 33.8.9 "SPI Chip Select Register").

When all bits are processed, the received data is transferred in the SPI\_RDR and the RDRF bit rises. If the SPI\_RDR has not been read before new data is received, the Overrun Error Status (OVRES) bit in the SPI\_SR is set. As long as this flag is set, data is loaded in the SPI\_RDR. The user must read SPI\_SR to clear the OVRES bit.

When a transfer starts, the data shifted out is the data present in the Shift register. If no data has been written in the SPI\_TDR, the last data received is transferred. If no data has been received since the last reset, all bits are transmitted low, as the Shift register resets to 0.

When a first data is written in the SPI\_TDR, it is transferred immediately in the Shift register and the TDRE flag rises. If new data is written, it remains in the SPI\_TDR until a transfer occurs, i.e., NSS falls and there is a valid clock on the SPCK pin. When the transfer occurs, the last data written in the SPI\_TDR is transferred in the Shift register and the TDRE flag rises. This enables frequent updates of critical variables with single transfers.

Then, new data is loaded in the Shift register from the SPI\_TDR. If no character is ready to be transmitted, i.e., no character has been written in the SPI\_TDR since the last load from the SPI\_TDR to the Shift register, the SPI\_TDR is retransmitted. In this case the Underrun Error Status Flag (UNDES) is set in the SPI\_SR.

Figure 33-13 shows a block diagram of the SPI when operating in Slave mode.

## 33.8.3 SPI Receive Data Register

| Name:    | SPI_RDR                        |    |    |    |    |    |    |  |  |

|----------|--------------------------------|----|----|----|----|----|----|--|--|

| Address: | 0x40008008 (0), 0x48000008 (1) |    |    |    |    |    |    |  |  |

| Access:  | Read-only                      |    |    |    |    |    |    |  |  |

| 31       | 30                             | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

| _        | _                              | _  | _  | _  | _  | _  | -  |  |  |

| 23       | 22                             | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

| _        | -                              | _  | _  |    | PC | S  |    |  |  |

| 15       | 14                             | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

|          |                                |    | R  | D  |    |    |    |  |  |

| 7        | 6                              | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|          |                                |    | R  | D  |    |    |    |  |  |

#### • RD: Receive Data

Data received by the SPI Interface is stored in this register in a right-justified format. Unused bits are read as zero.

## • PCS: Peripheral Chip Select

In Master mode only, these bits indicate the value on the NPCS pins at the end of a transfer. Otherwise, these bits are read as zero.

Note: When using Variable peripheral select mode (PS = 1 in SPI\_MR), it is mandatory to set the SPI\_MR.WDRBT bit to 1 if the PCS field must be processed in SPI\_RDR.

## 33.8.5 SPI Status Register

| Name:    | SPI_SR          |              |       |       |       |         |        |

|----------|-----------------|--------------|-------|-------|-------|---------|--------|

| Address: | 0x40008010 (0), | 0x48000010 ( | 1)    |       |       |         |        |

| Access:  | Read-only       |              |       |       |       |         |        |

| 31       | 30              | 29           | 28    | 27    | 26    | 25      | 24     |

| -        | -               | —            | _     | _     | _     | _       | —      |

| 23       | 22              | 21           | 20    | 19    | 18    | 17      | 16     |

| _        | -               | -            | _     | _     | -     | -       | SPIENS |

| 15       | 14              | 13           | 12    | 11    | 10    | 9       | 8      |

| _        | -               | -            | _     | _     | UNDES | TXEMPTY | NSSR   |

| 7        | 6               | 5            | 4     | 3     | 2     | 1       | 0      |

| TXBUFE   | RXBUFF          | ENDTX        | ENDRX | OVRES | MODF  | TDRE    | RDRF   |

|          |                 |              |       |       |       |         |        |

### RDRF: Receive Data Register Full (cleared by reading SPI\_RDR)

0: No data has been received since the last read of SPI\_RDR.

1: Data has been received and the received data has been transferred from the shift register to SPI\_RDR since the last read of SPI\_RDR.

## • TDRE: Transmit Data Register Empty (cleared by writing SPI\_TDR)

0: Data has been written to SPI\_TDR and not yet transferred to the shift register.

1: The last data written in the SPI\_TDR has been transferred to the shift register.

TDRE equals zero when the SPI is disabled or at reset. The SPI enable command sets this bit to 1.

#### MODF: Mode Fault Error (cleared on read)

0: No mode fault has been detected since the last read of SPI\_SR.

1: A mode fault occurred since the last read of SPI\_SR.

#### • OVRES: Overrun Error Status (cleared on read)

- 0: No overrun has been detected since the last read of SPI\_SR.

- 1: An overrun has occurred since the last read of SPI\_SR.

An overrun occurs when SPI\_RDR is loaded at least twice from the shift register since the last read of the SPI\_RDR.

## • ENDRX: End of RX Buffer (cleared by writing SPI\_RCR or SPI\_RNCR)

0: The Receive Counter register has not reached 0 since the last write in SPI\_RCR<sup>(1)</sup> or SPI\_RNCR<sup>(1)</sup>.

1: The Receive Counter register has reached 0 since the last write in SPI\_RCR<sup>(1)</sup> or SPI\_RNCR<sup>(1)</sup>.

## • ENDTX: End of TX Buffer (cleared by writing SPI\_TCR or SPI\_TNCR)

0: The Transmit Counter register has not reached 0 since the last write in SPI\_TCR<sup>(1)</sup> or SPI\_TNCR<sup>(1)</sup>.

1: The Transmit Counter register has reached 0 since the last write in SPI\_TCR<sup>(1)</sup> or SPI\_TNCR<sup>(1)</sup>.

## • RXBUFF: RX Buffer Full (cleared by writing SPI\_RCR or SPI\_RNCR)

0: SPI\_RCR<sup>(1)</sup> or SPI\_RNCR<sup>(1)</sup> has a value other than 0.

1: Both SPI\_RCR<sup>(1)</sup> and SPI\_RNCR<sup>(1)</sup> have a value of 0.

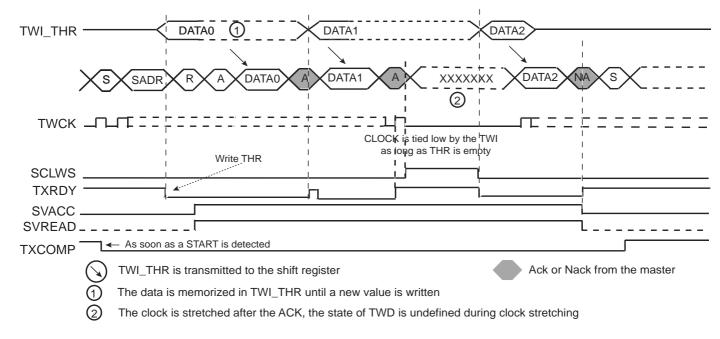

## Clock Synchronization/Stretching

In both Read and Write modes, it may occur that TWI\_THR/TWI\_RHR buffer is not filled /emptied before transmission/reception of a new character. In this case, to avoid sending/receiving undesired data, a clock stretching/synchronization mechanism is implemented.

#### **Clock Stretching in Read Mode**

The clock is tied low during the acknowledge phase if the internal shifter is empty and if a STOP or REPEATED START condition was not detected. It is tied low until the internal shifter is loaded.

Figure 34-28 describes clock stretching in Read mode.

#### Figure 34-28. Clock Stretching in Read Mode

- Notes: 1. TXRDY is reset when data has been written in the TWI\_THR to the internal shifter and set when this data has been acknowledged or non acknowledged.

- 2. At the end of the read sequence, TXCOMP is set after a STOP or after a REPEATED\_START + an address different from SADR.

- 3. SCLWS is automatically set when the clock stretching mechanism is started.

The following triggers are common to both modes:

- Software Trigger: Each channel has a software trigger, available by setting SWTRG in TC\_CCR.

- SYNC: Each channel has a synchronization signal SYNC. When asserted, this signal has the same effect as a software trigger. The SYNC signals of all channels are asserted simultaneously by writing TC\_BCR (Block Control) with SYNC set.

- Compare RC Trigger: RC is implemented in each channel and can provide a trigger when the counter value matches the RC value if CPCTRG is set in the TC\_CMR.

The channel can also be configured to have an external trigger. In Capture mode, the external trigger signal can be selected between TIOA and TIOB. In Waveform mode, an external event can be programmed on one of the following signals: TIOB, XC0, XC1 or XC2. This external event can then be programmed to perform a trigger by setting bit ENETRG in the TC\_CMR.

If an external trigger is used, the duration of the pulses must be longer than the peripheral clock period in order to be detected.

### 37.6.7 Capture Mode

Capture mode is entered by clearing the WAVE bit in the TC\_CMR.

Capture mode allows the TC channel to perform measurements such as pulse timing, frequency, period, duty cycle and phase on TIOA and TIOB signals which are considered as inputs.

Figure 37-5 shows the configuration of the TC channel when programmed in Capture mode.

### 37.6.8 Capture Registers A and B

Registers A and B (RA and RB) are used as capture registers. They can be loaded with the counter value when a programmable event occurs on the signal TIOA.

The LDRA field in the TC\_CMR defines the TIOA selected edge for the loading of register A, and the LDRB field defines the TIOA selected edge for the loading of Register B.

RA is loaded only if it has not been loaded since the last trigger or if RB has been loaded since the last loading of RA.

RB is loaded only if RA has been loaded since the last trigger or the last loading of RB.

Loading RA or RB before the read of the last value loaded sets the Overrun Error Flag (LOVRS bit) in the TC\_SR. In this case, the old value is overwritten.

#### 37.6.9 Trigger Conditions

In addition to the SYNC signal, the software trigger and the RC compare trigger, an external trigger can be defined.

The ABETRG bit in the TC\_CMR selects TIOA or TIOB input signal as an external trigger . The External Trigger Edge Selection parameter (ETRGEDG field in TC\_CMR) defines the edge (rising, falling, or both) detected to generate an external trigger. If ETRGEDG = 0 (none), the external trigger is disabled.

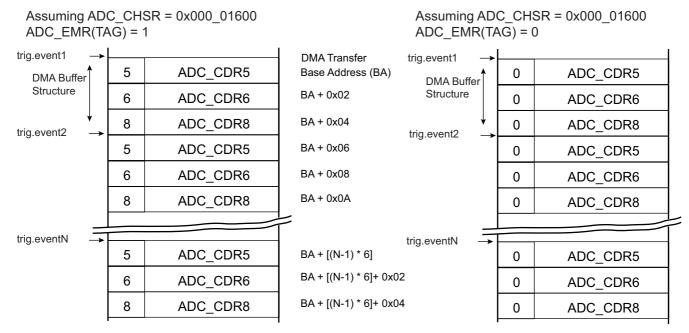

#### Figure 40-12. Buffer Structure

#### 40.6.13 Register Write Protection

To prevent any single software error from corrupting ADC behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the "ADC Write Protection Mode Register" (ADC\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the "ADC Write Protection Status Register" (ADC\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the ADC\_WPSR.

The following registers can be write-protected:

- "ADC Mode Register"

- "ADC Channel Sequence 1 Register"

- "ADC Channel Enable Register"

- "ADC Channel Disable Register"

- "ADC Temperature Sensor Mode Register"

- "ADC Temperature Compare Window Register"

- "ADC Extended Mode Register"

- "ADC Compare Window Register"

- "ADC Analog Control Register"

# Table 42-5. Register Mapping (Continued)

| Offset      | Register                               | Name       | Access     | Reset |

|-------------|----------------------------------------|------------|------------|-------|

| 0x90        | GCM Authentication Tag Word Register 2 | AES_TAGR2  | Read-only  | -     |

| 0x94        | GCM Authentication Tag Word Register 3 | AES_TAGR3  | Read-only  | _     |

| 0x98        | GCM Encryption Counter Value Register  | AES_CTRR   | Read-only  | _     |

| 0x9C        | GCM H Word Register 0                  | AES_GCMHR0 | Read/Write | _     |

| 0xA0        | GCM H Word Register 1                  | AES_GCMHR1 | Read/Write | _     |

| 0xA4        | GCM H Word Register 2                  | AES_GCMHR2 | Read/Write | -     |

| 0xA8        | GCM H Word Register 3                  | AES_GCMHR3 | Read/Write | -     |

| 0xAC        | Reserved                               | _          | -          | _     |

| 0xB0-0xFC   | Reserved                               | _          | -          | _     |

| 0x100-0x124 | Reserved for the PDC                   | _          | _          | _     |

| 42.5.11 AES | S Additional Authen | ticated Data | Length Regis | ter |    |    |    |  |  |

|-------------|---------------------|--------------|--------------|-----|----|----|----|--|--|

| Name:       | AES_AADLENR         |              |              |     |    |    |    |  |  |

| Address:    | 0x4000070           |              |              |     |    |    |    |  |  |

| Access:     | Read/Write          |              |              |     |    |    |    |  |  |

| 31          | 30                  | 29           | 28           | 27  | 26 | 25 | 24 |  |  |

| AADLEN      |                     |              |              |     |    |    |    |  |  |

| 23          | 22                  | 21           | 20           | 19  | 18 | 17 | 16 |  |  |

| AADLEN      |                     |              |              |     |    |    |    |  |  |

| 15          | 14                  | 13           | 12           | 11  | 10 | 9  | 8  |  |  |

| AADLEN      |                     |              |              |     |    |    |    |  |  |

| 7           | 6                   | 5            | 4            | 3   | 2  | 1  | 0  |  |  |

|             | AADLEN              |              |              |     |    |    |    |  |  |

# AADLEN: Additional Authenticated Data Length

Length in bytes of the Additional Authenticated Data (AAD) that is to be processed.

Note: The maximum byte length of the AAD portion of a message is limited to the 32-bit counter length.

#### 46.5.5 VDDCORE Power-On-Reset

| Symbol             | Parameter                                        | Conditions                                                             | Min  | Тур | Max  | Unit |

|--------------------|--------------------------------------------------|------------------------------------------------------------------------|------|-----|------|------|

| V <sub>IT-</sub>   | Negative-going input threshold voltage (VDDCORE) | -                                                                      | 0.71 | 0.9 | 1.02 | V    |

| V <sub>IT+</sub>   | Positive-going input threshold voltage (VDDCORE) | -                                                                      | 0.80 | 1.0 | 1.08 | V    |

| V <sub>HYS</sub>   | Hysteresis voltage                               | V <sub>IT+</sub> - V <sub>IT-</sub>                                    | _    | 60  | 110  | mV   |

| t <sub>d-</sub>    | V <sub>IT-</sub> detection propagation time      | VDDCORE = $V_{IT+}$ to ( $V_{IT-}$ - 100mV)                            | _    | _   | 15   | μs   |

| t <sub>START</sub> | Start-up time                                    | VDDCORE rising from 0 to final value.<br>Time to release reset signal. | _    | _   | 300  | μs   |

| IDDCORE            | Current consumption (VDDCORE)                    | _                                                                      | _    | _   | 6    | μA   |

| I <sub>DDIO</sub>  | Current consumption (VDDIO)                      | _                                                                      | _    | _   | 9    | μA   |

#### Table 46-22. Core Power Supply Power-On-Reset Characteristics

## 46.5.6 VDDIO Supply Monitor

#### Table 46-23. VDDIO Supply Monitor

| Symbol            | Parameter                                                                | Conditions                       | Min  | Тур | Max  | Unit |

|-------------------|--------------------------------------------------------------------------|----------------------------------|------|-----|------|------|

| V <sub>TH-</sub>  | Programmable range of negative-<br>going input threshold voltage (VDDIO) | 16 selectable steps              | 1.6  | _   | 3.4  | V    |

| ACC               | V <sub>TH-</sub> accuracy                                                | With respect to programmed value | -2.5 | _   | +2.5 | %    |

| V <sub>HYST</sub> | Hysteresis <sup>(2)</sup>                                                | _                                | _    | 30  | 40   | mV   |

| I <sub>DDON</sub> | Current consumption (VDDIO) <sup>(1)</sup>                               | On with a 100% duty cycle.       | _    | 20  | 40   | μA   |

| t <sub>ON</sub>   | Start-up time                                                            | From OFF to ON                   | _    | _   | 300  | μs   |

Notes: 1. The average current consumption can be reduced by using the supply monitor in Sampling mode. Refer to Section 20. "Supply Controller (SUPC)".

2.  $V_{HYST} = V_{TH+} - V_{TH-}$ .  $V_{TH+}$  is the positive-going input threshold voltage (VDDIO).

## Table 46-24. VDDIO Supply Monitor V<sub>TH-</sub> Threshold Selection

| Digital Code | Threshold<br>Typ (V) |

|--------------|----------------------|--------------|----------------------|--------------|----------------------|--------------|----------------------|

| 0000         | 1.60                 | 0100         | 2.08                 | 1000         | 2.56                 | 1100         | 3.04                 |

| 0001         | 1.72                 | 0101         | 2.20                 | 1001         | 2.68                 | 1101         | 3.16                 |

| 0010         | 1.84                 | 0110         | 2.32                 | 1010         | 2.80                 | 1110         | 3.28                 |

| 0011         | 1.96                 | 0111         | 2.44                 | 1011         | 2.92                 | 1111         | 3.40                 |

# Atmel Enabling Unlimited Possibilities

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200 | www.atmel.com

© 2016 Atmel Corporation. / Rev.: Atmel-11203E-ATARM-SAM4CM32-SAM4CM16-SAM4CM8-SAM4CM4-Datasheet\_24-Oct-16.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM<sup>®</sup>, ARM Connected<sup>®</sup> logo, and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR SAND PROPERTS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.