# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M4F                                                       |

| Core Size                  | 32-Bit Dual-Core                                                          |

| Speed                      | 120MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                           |

| Number of I/O              | 57                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 6x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4cms4cb-au |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

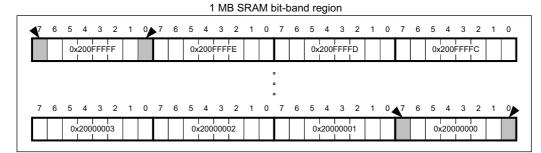

- The alias word at 0x22000000 maps to bit[0] of the bit-band byte at 0x20000000: 0x22000000 = 0x22000000 + (0\*32) + (0\*4).

- The alias word at 0x2200001C maps to bit[7] of the bit-band byte at 0x20000000: 0x2200001C = 0x2200000+ (0\*32) + (7\*4).

#### Figure 12-4. Bit-band Mapping

| 32 MB alias region |            |            |                                       |            |                                       |            |            |  |

|--------------------|------------|------------|---------------------------------------|------------|---------------------------------------|------------|------------|--|

|                    |            | <u> </u>   | · · · · · · · · · · · · · · · · · · · |            | · · · · · · · · · · · · · · · · · · · |            |            |  |

| 0x23FFFFFC         | 0x23FFFFF8 | 0x23FFFFF4 | 0x23FFFFF0                            | 0x23FFFFEC | 0x23FFFFE8                            | 0x23FFFFE4 | 0x23FFFFE0 |  |

| ✓                  |            |            |                                       |            |                                       |            | <          |  |

|                    |            |            |                                       | 0          |                                       |            |            |  |

|                    |            |            |                                       | 0          |                                       |            |            |  |

|                    | -          |            |                                       |            |                                       |            |            |  |

| 0x2200001C         | 0x22000018 | 0x22000014 | 0x22000010                            | 0x2200000C | 0x22000008                            | 0x22000004 | 0x22000000 |  |

|                    |            |            |                                       |            |                                       |            |            |  |

#### Directly Accessing an Alias Region

Writing to a word in the alias region updates a single bit in the bit-band region.

Bit[0] of the value written to a word in the alias region determines the value written to the targeted bit in the bitband region. Writing a value with bit[0] set to 1 writes a 1 to the bit-band bit, and writing a value with bit[0] set to 0 writes a 0 to the bit-band bit.

Bits[31:1] of the alias word have no effect on the bit-band bit. Writing 0x01 has the same effect as writing 0xFF. Writing 0x00 has the same effect as writing 0x0E.

Reading a word in the alias region:

- 0x00000000 indicates that the targeted bit in the bit-band region is set to 0

- 0x00000001 indicates that the targeted bit in the bit-band region is set to 1

#### Directly Accessing a Bit-band Region

"Behavior of Memory Accesses" describes the behavior of direct byte, halfword, or word accesses to the bit-band regions.

#### 12.4.2.6 Memory Endianness

The processor views memory as a linear collection of bytes numbered in ascending order from zero. For example, bytes 0–3 hold the first stored word, and bytes 4–7 hold the second stored word. "Little-endian Format" describes how words of data are stored in memory.

#### Little-endian Format

In little-endian format, the processor stores the least significant byte of a word at the lowest-numbered byte, and the most significant byte at the highest-numbered byte. For example:

#### 12.6.11.20 VMSR

Move to floating-point System Register from ARM Core register.

Syntax

VMSR{cond} FPSCR, Rt

where:

cond is an optional condition code, see "Conditional Execution".

Rt is the general-purpose register to be transferred to the FPSCR.

#### Operation

This instruction moves the value of a general-purpose register to the FPSCR. See "Floating-point Status Control Register" for more information.

#### Restrictions

The restrictions are:

• Rt cannot be PC or SP.

**Condition Flags**

This instruction updates the FPSCR.

#### 12.6.11.21 VMUL

Floating-point Multiply.

Syntax

$VMUL{cond}.F32 {Sd}, Sn, Sm$

where:

cond is an optional condition code, see "Conditional Execution".

Sd is the destination floating-point value.

Sn, Sm are the operand floating-point values.

Operation

This instruction:

- 1. Multiplies two floating-point values.

- 2. Places the results in the destination register.

Restrictions

There are no restrictions.

**Condition Flags**

These instructions do not change the flags.

#### 12.9.1.2 CPUID Base Register Name: SCB\_CPUID Access: Read/Write 31 30 29 28 27 26 25 24 Implementer 23 22 20 19 18 17 16 21 Variant Constant 14 12 10 9 8 15 13 11 PartNo 6 5 4 7 3 2 1 0 PartNo Revision

The SCB\_CPUID register contains the processor part number, version, and implementation information.

#### Implementer: Implementer Code

0x41: ARM.

#### • Variant: Variant Number

It is the r value in the rnpn product revision identifier: 0x0: Revision 0.

#### • Constant: Reads as 0xF

Reads as 0xF.

#### • PartNo: Part Number of the Processor

0xC24 = Cortex-M4.

#### • Revision: Revision Number

It is the p value in the rnpn product revision identifier: 0x0: Patch 0.

#### 12.11.2 Memory Protection Unit (MPU) User Interface

| Offset     | Register                                       | Name        | Access     | Reset      |

|------------|------------------------------------------------|-------------|------------|------------|

| 0xE000ED90 | MPU Type Register                              | MPU_TYPE    | Read-only  | 0x0000800  |

| 0xE000ED94 | MPU Control Register                           | MPU_CTRL    | Read/Write | 0x00000000 |

| 0xE000ED98 | MPU Region Number Register                     | MPU_RNR     | Read/Write | 0x00000000 |

| 0xE000ED9C | MPU Region Base Address Register               | MPU_RBAR    | Read/Write | 0x00000000 |

| 0xE000EDA0 | MPU Region Attribute and Size Register         | MPU_RASR    | Read/Write | 0x00000000 |

| 0xE000EDA4 | MPU Region Base Address Register Alias 1       | MPU_RBAR_A1 | Read/Write | 0x00000000 |

| 0xE000EDA8 | MPU Region Attribute and Size Register Alias 1 | MPU_RASR_A1 | Read/Write | 0x00000000 |

| 0xE000EDAC | MPU Region Base Address Register Alias 2       | MPU_RBAR_A2 | Read/Write | 0x00000000 |

| 0xE000EDB0 | MPU Region Attribute and Size Register Alias 2 | MPU_RASR_A2 | Read/Write | 0x00000000 |

| 0xE000EDB4 | MPU Region Base Address Register Alias 3       | MPU_RBAR_A3 | Read/Write | 0x00000000 |

| 0xE000EDB8 | MPU Region Attribute and Size Register Alias 3 | MPU_RASR_A3 | Read/Write | 0x00000000 |

#### Table 12-41. Memory Protection Unit (MPU) Register Mapping

### 15.5 Reset Controller (RSTC) User Interface

| Offset | Register                  | Name      | Access     | Reset                      |

|--------|---------------------------|-----------|------------|----------------------------|

| 0x00   | Control Register          | RSTC_CR   | Write-only | -                          |

| 0x04   | Status Register           | RSTC_SR   | Read-only  | 0x0000_0000 <sup>(1)</sup> |

| 0x08   | Mode Register             | RSTC_MR   | Read/Write | 0x0000 0001                |

| 0x0C   | Coprocessor Mode Register | RSTC_CPMR | Read/Write | 0x0000_0000                |

#### Table 15-1. Register Mapping

Note: 1. This value assumes that a general reset has been performed, subject to change if other types of reset are generated.

#### • SMOS: Supply Monitor Output Status

0 (HIGH): The supply monitor detected VDDIO higher than its threshold at its last measurement.

1 (LOW): The supply monitor detected VDDIO lower than its threshold at its last measurement.

#### OSCSEL: 32 kHz Oscillator Selection Status

0 (RC): The slow clock, SLCK, is generated by the embedded 32 kHz RC oscillator.

1 (CRYST): The slow clock, SLCK, is generated by the 32 kHz crystal oscillator.

#### LCDS: LCD Status

0 (DISABLED): LCD controller is disabled.

1 (ENABLED): LCD controller is enabled.

#### • FWUPIS: FWUP Input Status

0 (LOW): FWUP input is tied low.

1 (HIGH): FWUP input is tied high.

#### • LPDBCS0: Low Power Debouncer Wakeup Status on WKUP0/TMP0 (cleared on read)

0 (NO): No tamper detection or wakeup due to the assertion of the WKUP0/TMP0 pin has occurred since the last read of SUPC\_SR.

1 (PRESENT): At least one tamper detection and wakeup (if enabled by WKUPEN0) due to the assertion of the WKUP0/TMP0 pin has occurred since the last read of SUPC\_SR. The SUPC interrupt line is asserted while LPDBCS0 is 1.

#### • LPDBCS1: Low Power Debouncer Wakeup Status on WKUP10/TMP1 (cleared on read)

0 (NO): No tamper detection or wakeup due to the assertion of the WKUP10 pin has occurred since the last read of SUPC\_SR.

1 (PRESENT): At least one tamper detection and wakeup (if enabled by WKUPEN10) due to the assertion of the WKUP10/TMP1 pin has occurred since the last read of SUPC\_SR. The SUPC interrupt line is asserted while LPDBCS1 is 1.

### BUPPORS: Backup Area Power-On Reset Status

0 (BUPPOR\_DISABLED): Backup POR is disabled.

1 (BUPPOR\_ENABLED): Backup POR is enabled.

Note: The value written in BUPPOREN is effective when BUPPORENS has the same value in Supply Controller Status Register.

#### • WKUPISx: WKUPx Input Status (cleared on read)

0 (DIS): The corresponding wakeup input is disabled, or was inactive at the time the debouncer triggered a wakeup event.

1 (EN): The corresponding wakeup input was active at the time the debouncer triggered a wakeup event since the last read of SUPC\_SR.

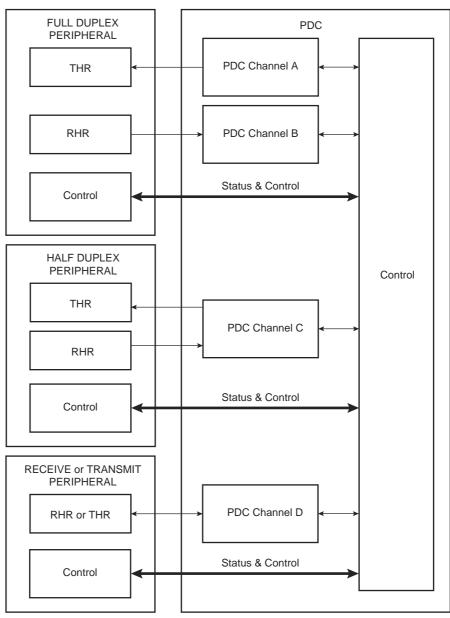

### 28.3 Block Diagram

Figure 28-1. Block Diagram

#### 32.6.22 PIO Pull-Up Enable Register

| Name:    | PIO_PUER       |                                                         |     |     |     |     |     |  |  |  |

|----------|----------------|---------------------------------------------------------|-----|-----|-----|-----|-----|--|--|--|

| Address: | 0x400E0E64 (PI | 0x400E0E64 (PIOA), 0x400E1064 (PIOB), 0x4800C064 (PIOC) |     |     |     |     |     |  |  |  |

| Access:  | Write-only     |                                                         |     |     |     |     |     |  |  |  |

| 31       | 30             | 29                                                      | 28  | 27  | 26  | 25  | 24  |  |  |  |

| P31      | P30            | P29                                                     | P28 | P27 | P26 | P25 | P24 |  |  |  |

| 23       | 22             | 21                                                      | 20  | 19  | 18  | 17  | 16  |  |  |  |

| P23      | P22            | P21                                                     | P20 | P19 | P18 | P17 | P16 |  |  |  |

| 15       | 14             | 13                                                      | 12  | 11  | 10  | 9   | 8   |  |  |  |

| P15      | P14            | P13                                                     | P12 | P11 | P10 | P9  | P8  |  |  |  |

| 7        | 6              | 5                                                       | 4   | 3   | 2   | 1   | 0   |  |  |  |

| P7       | P6             | P5                                                      | P4  | P3  | P2  | P1  | P0  |  |  |  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

#### • P0-P31: Pull-Up Enable

0: No effect.

1: Enables the pull-up resistor on the I/O line.

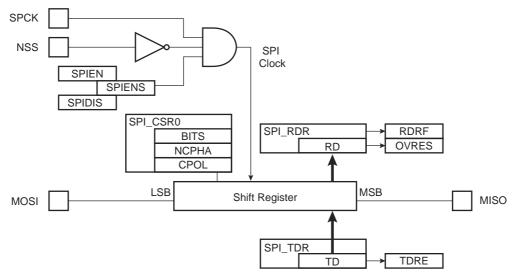

Figure 33-13. Slave Mode Functional Block Diagram

#### 33.7.5 Register Write Protection

To prevent any single software error from corrupting SPI behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the SPI Write Protection Mode Register (SPI\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the SPI Write Protection Status Register (SPI\_WPSR) is set and the WPVSRC field indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading SPI\_WPSR.

The following registers can be write-protected:

- SPI Mode Register

- SPI Chip Select Register

In SPI Slave mode, the transmitter does not require a falling edge of the slave select line (NSS) to initiate a character transmission but only a low level. However, this low level must be present on the slave select line (NSS) at least one  $t_{bit}$  before the first serial clock cycle corresponding to the MSB bit.

#### 36.6.7.6 Character Reception

When a character reception is completed, it is transferred to the Receive Holding register (US\_RHR) and the RXRDY bit in the Status register (US\_CSR) rises. If a character is completed while RXRDY is set, the OVRE (Overrun Error) bit is set. The last character is transferred into US\_RHR and overwrites the previous one. The OVRE bit is cleared by writing a 1 to the RSTSTA (Reset Status) bit in the US\_CR.

To ensure correct behavior of the receiver in SPI Slave mode, the master device sending the frame must ensure a minimum delay of one  $t_{bit}$  between each character transmission. The receiver does not require a falling edge of the slave select line (NSS) to initiate a character reception but only a low level. However, this low level must be present on the slave select line (NSS) at least one  $t_{bit}$  before the first serial clock cycle corresponding to the MSB bit.

#### 36.6.7.7 Receiver Timeout

Because the receiver baud rate clock is active only during data transfers in SPI mode, a receiver timeout is impossible in this mode, whatever the time-out value is (field TO) in the US\_RTOR.

#### 36.6.8 Test Modes

The USART can be programmed to operate in three different test modes. The internal loopback capability allows on-board diagnostics. In Loopback mode, the USART interface pins are disconnected or not and reconfigured for loopback internally or externally.

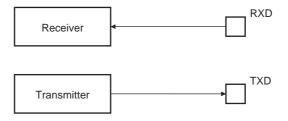

#### 36.6.8.1 Normal Mode

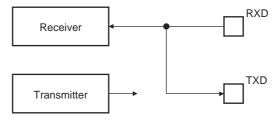

Normal mode connects the RXD pin on the receiver input and the transmitter output on the TXD pin.

#### Figure 36-39. Normal Mode Configuration

#### 36.6.8.2 Automatic Echo Mode

Automatic echo mode allows bit-by-bit retransmission. When a bit is received on the RXD pin, it is sent to the TXD pin, as shown in Figure 36-40. Programming the transmitter has no effect on the TXD pin. The RXD pin is still connected to the receiver input, thus the receiver remains active.

#### Figure 36-40. Automatic Echo Mode Configuration

#### • ETRGS: External Trigger Status (cleared on read)

0: External trigger has not occurred since the last read of the Status Register.

1: External trigger has occurred since the last read of the Status Register.

#### • CLKSTA: Clock Enabling Status

0: Clock is disabled.

1: Clock is enabled.

#### • MTIOA: TIOA Mirror

0: TIOA is low. If TC\_CMRx.WAVE = 0, this means that TIOA pin is low. If TC\_CMRx.WAVE = 1, this means that TIOA is driven low.

1: TIOA is high. If TC\_CMRx.WAVE = 0, this means that TIOA pin is high. If TC\_CMRx.WAVE = 1, this means that TIOA is driven high.

#### • MTIOB: TIOB Mirror

0: TIOB is low. If TC\_CMRx.WAVE = 0, this means that TIOB pin is low. If TC\_CMRx.WAVE = 1, this means that TIOB is driven low.

1: TIOB is high. If TC\_CMRx.WAVE = 0, this means that TIOB pin is high. If TC\_CMRx.WAVE = 1, this means that TIOB is driven high.

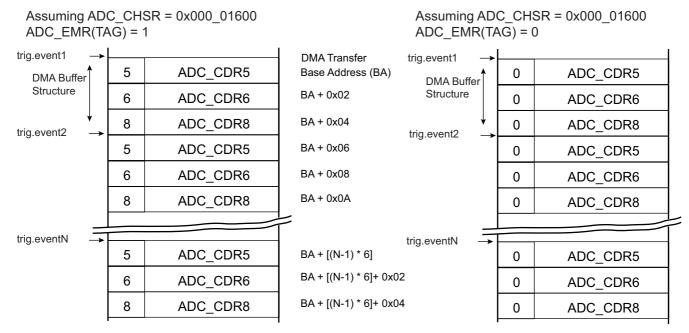

#### Figure 40-12. Buffer Structure

#### 40.6.13 Register Write Protection

To prevent any single software error from corrupting ADC behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the "ADC Write Protection Mode Register" (ADC\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the "ADC Write Protection Status Register" (ADC\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the ADC\_WPSR.

The following registers can be write-protected:

- "ADC Mode Register"

- "ADC Channel Sequence 1 Register"

- "ADC Channel Enable Register"

- "ADC Channel Disable Register"

- "ADC Temperature Sensor Mode Register"

- "ADC Temperature Compare Window Register"

- "ADC Extended Mode Register"

- "ADC Compare Window Register"

- "ADC Analog Control Register"

#### 40.7.20 ADC Write Protection Status Register

| Name:    | ADC_WPSR   |    |     |      |    |    |      |

|----------|------------|----|-----|------|----|----|------|

| Address: | 0x400380E8 |    |     |      |    |    |      |

| Access:  | Read-only  |    |     |      |    |    |      |

| 31       | 30         | 29 | 28  | 27   | 26 | 25 | 24   |

| -        | -          | -  | -   | -    | -  | -  | -    |

| 23       | 22         | 21 | 20  | 19   | 18 | 17 | 16   |

|          |            |    | WPV | /SRC |    |    |      |

| 15       | 14         | 13 | 12  | 11   | 10 | 9  | 8    |

|          |            |    | WPV | /SRC |    |    |      |

| 7        | 6          | 5  | 4   | 3    | 2  | 1  | 0    |

| -        | -          | -  | -   | _    | -  | _  | WPVS |

#### • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of the ADC\_WPSR register.

1: A write protection violation has occurred since the last read of the ADC\_WPSR register. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC.

#### • WPVSRC: Write Protection Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

#### • URAT: Unspecified Register Access (cleared by writing SWRST in AES\_CR)

| Value | Name              | Description                                                                    |

|-------|-------------------|--------------------------------------------------------------------------------|

| 0     | IDR_WR_PROCESSING | Input Data Register written during the data processing when $SMOD = 0x2$ mode. |

| 1     | ODR_RD_PROCESSING | Output Data Register read during the data processing.                          |

| 2     | MR_WR_PROCESSING  | Mode Register written during the data processing.                              |

| 3     | ODR_RD_SUBKGEN    | Output Data Register read during the sub-keys generation.                      |

| 4     | MR_WR_SUBKGEN     | Mode Register written during the sub-keys generation.                          |

| 5     | WOR_RD_ACCESS     | Write-only register read access.                                               |

Only the last Unspecified Register Access Type is available through the URAT field.

### • TAGRDY: GCM Tag Ready

0: GCM Tag is not valid.

1: GCM Tag generation is complete (cleared by reading GCM Tag, starting another processing or when writing a new key).

#### 43.6.5 ICM Interrupt Disable Register

| Name:<br>Address:<br>Access: | ICM_IDR<br>0x40044014<br>Write-only |    |    |     |    |    |      |  |

|------------------------------|-------------------------------------|----|----|-----|----|----|------|--|

| 31                           | 30                                  | 29 | 28 | 27  | 26 | 25 | 24   |  |

| _                            | _                                   | _  | -  | _   | _  | —  | URAD |  |

| 23                           | 22                                  | 21 | 20 | 19  | 18 | 17 | 16   |  |

|                              | RS                                  | U  |    | REC |    |    |      |  |

| 15                           | 14                                  | 13 | 12 | 11  | 10 | 9  | 8    |  |

|                              | RWC                                 |    |    | RBE |    |    |      |  |

| 7                            | 6                                   | 5  | 4  | 3   | 2  | 1  | 0    |  |

|                              | RDM                                 |    |    |     | RI | HC |      |  |

#### • RHC: Region Hash Completed Interrupt Disable

0: No effect

1: When RHC[*i*] is set to one, the Region *i* Hash Completed interrupt is disabled.

#### • RDM: Region Digest Mismatch Interrupt Disable

0: No effect

1: When RDM[*i*] is set to one, the Region *i* Digest Mismatch interrupt is disabled.

#### • RBE: Region Bus Error Interrupt Disable

0: No effect

1: When RBE[*i*] is set to one, the Region *i* Bus Error interrupt is disabled.

#### • RWC: Region Wrap Condition Detected Interrupt Disable

0: No effect

1: When RWC[*i*] is set to one, the Region *i* Wrap Condition interrupt is disabled.

#### • REC: Region End bit Condition detected Interrupt Disable

0: No effect

1: When REC[*i*] is set to one, the region *i* End bit Condition interrupt is disabled.

#### • RSU: Region Status Updated Interrupt Disable

0: No effect

1: When RSU[i] is set to one, the region i Status Updated interrupt is disabled.

#### • URAD: Undefined Register Access Detection Interrupt Disable

0: No effect

1: Undefined Register Access Detection interrupt is disabled.

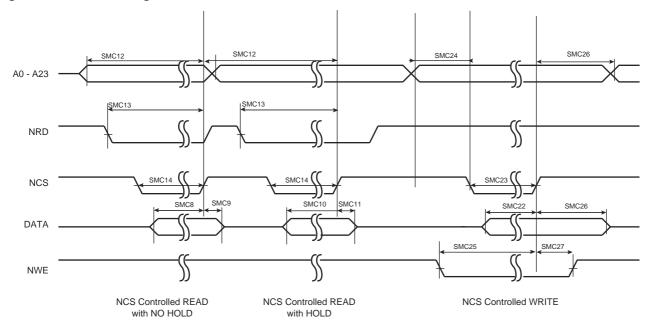

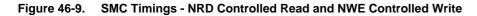

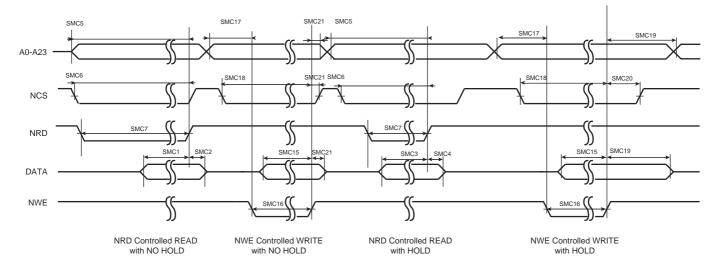

Figure 46-8. SMC Timings - NCS Controlled Read and Write

**Example:** Calculated track time is lower than actual ADC clock period

- Assuming:  $f_{CK ADC} = 1 \text{ MHz} (t_{CK ADC} = 1 \text{ } \mu\text{s}), R_{SOURCE} = 100\Omega \text{ and } V_{DDIN} = 3.3V$

- The minimum required track time is: t<sub>TRACK</sub> = 0.12 x 100 + 500 = 512 ns

- $t_{TRACK}$  being less than  $t_{CK_ADC}$ , TRACKTIM is set to 0. Actual track time is  $t_{CK_ADC} = 1 \ \mu s$

- The calculated sampling rate is: f<sub>S</sub> = 1 MHz / 24 = 41.7 kHz

- The maximum allowable source resistance is:  $R_{SOURCE MAX} = (1000 500) / 0.12 = 4.1 k\Omega$

**Example:** Calculated track time is greater than actual ADC clock period

- Assuming:  $f_{CK ADC} = 16$  MHz ( $t_{CK ADC} = 62.5$  ns),  $R_{SOURCE} = 600\Omega$  and  $V_{DDIN} = 2.8V$

- The minimum required track time is:  $t_{TRACK} = 0.12 \times 600 + 1000 = 1072 \text{ ns}$

- TRACKTIM = floor (1072 / 62.5) = 17. Actual track time is: (17 + 1) x  $t_{CK ADC}$  = 1.125 µs

- The calculated sampling rate is:  $f_s = 16 \text{ MHz} / (24 + 17) = 390.2 \text{ kHz}$

- The maximum allowable source resistance is:  $R_{SOURCE MAX} = (1125 1000) / 0.12 = 1.04 k\Omega$

#### 46.5.18 Programmable Voltage Reference Characteristics

SAM4CM embeds a programmable voltage reference designed to drive the 10-bit ADC ADVREF input. Table 46-43 shows the electrical characteristics of this internal voltage reference. If necessary, this voltage reference can be bypassed with some level of configurability: the user can either choose to feed the ADVREF input with an external voltage source or with the VDDIO internal power rail. Refer to programming details in Section 40.7.18 "ADC Analog Control Register".

| Symbol              | Parameter                                   | Conditions                                                                    | Min | Тур | Max | Unit   |

|---------------------|---------------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|--------|

| V <sub>DDIN</sub>   | Voltage reference supply range              | -                                                                             | 2   | _   | 3.6 | V      |

| V                   | Brogrommoble output ronge                   | Refer to Table 46-44.                                                         | 1.6 |     | 24  | V      |

| V <sub>ADVREF</sub> | Programmable output range                   | $V_{DDIN} > V_{ADVREF} + 100mV$                                               | 1.0 | _   | 3.4 | V      |

| ACC                 | Reference voltage accuracy                  | With respect to the programmed value. $V_{DDIN} = 3.3V$ ; $T_J = 25^{\circ}C$ | -3  | _   | 3   | %      |

| T <sub>C</sub>      | Temperature coefficient                     | Box method <sup>(1)</sup>                                                     | _   | -   | 250 | ppm/°C |

|                     |                                             | $V_{DDIN} = 2.4 V$                                                            |     |     | 100 |        |

| t <sub>ON</sub>     | Start-up time                               | $V_{DDIN} = 3V$                                                               | -   | -   | 70  | μs     |

|                     |                                             | $V_{DDIN} = 3.6V$                                                             |     |     | 40  |        |

| 7                   | Landimpedance                               | Resistive                                                                     | 4   | -   | -   | kΩ     |

| Z <sub>LOAD</sub>   | Load impedance                              | Capacitive                                                                    | 0.1 | -   | 1   | μF     |

| I <sub>VDDIN</sub>  | Current consumption on VDDIN <sup>(2)</sup> | ADC is OFF                                                                    | _   | 20  | 30  | μA     |

Table 46-43. Programmable Voltage Reference Characteristics

Notes: 1. TC =  $(\max(V_{ADVREF}) - \min(V_{ADVREF})) / ((T_{MAX} - T_{MIN}) * V_{ADVREF}(25^{\circ}C)).$

2. Does not include the current consumed by the ADC ADVREF input if ADC is ON

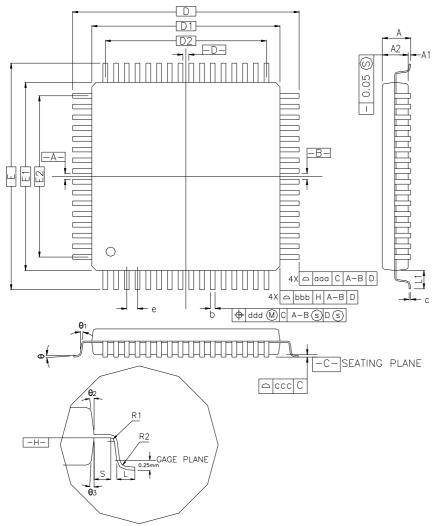

## 47. Mechanical Characteristics

### 47.1 100-lead LQFP Package

#### Figure 47-1. 100-lead LQFP Package Drawing

| COTROL | DIMENSIONS   | ARF | IN   | MILLIMETERS.  |

|--------|--------------|-----|------|---------------|

| CONCE  | DIVICINGIONS |     | 11.4 | WILLING ILKS. |

| SYMBOL | М     | ILLIMETI | ER    | INCH      |        |       |  |

|--------|-------|----------|-------|-----------|--------|-------|--|

| STMBUL | MIN.  | NOM.     | MAX.  | MIN.      | NOM.   | MAX.  |  |

| A      | _     | —        | 1.60  | —         | _      | 0.063 |  |

| A1     | 0.05  |          | 0.15  | 0.002     |        | 0.006 |  |

| A2     | 1.35  | 1.40     | 1.45  | 0.053     | 0.055  | 0.057 |  |

| D      | 1     | 6.00 B   | SC.   | 0.        | 630 BS | SC.   |  |

| D1     | 1     | 4.00 B   | SC.   | 0.        | 551 BS | SC.   |  |

| E      | 1     | 6.00 B   | SC.   | 0.        | 630 BS | SC.   |  |

| E1     | 1.    | 4.00 B   | SC.   | 0.        | 551 BS | SC.   |  |

| R2     | 0.08  |          | 0.20  | 0.003     |        | 0.008 |  |

| R1     | 0.08  | —        | —     | 0.003     |        |       |  |

| θ      | 0°    | 3.5°     | 7*    | 0.        | 3.5°   | 7*    |  |

| θ1     | 0*    | —        |       | 0.        | _      | —     |  |

| θ2     | 11*   | 12*      | 1 3*  | 11.       | 12*    | 13*   |  |

| θ3     | 11°   | 12*      | 13*   | 11*       | 12°    | 13°   |  |

| с      | 0.09  | —        | 0.20  | 0.004     |        | 0.008 |  |

| L      | 0.45  | 0.60     | 0.75  | 0.018     | 0.024  | 0.030 |  |

| L 1    | 1     | .00 RE   | F     | 0.039 REF |        |       |  |

| S      | 0.20  | —        |       | 0.008     | —      | —     |  |

| b      | 0.17  | 0.20     | 0.27  | 0.007     | 0.008  | 0.011 |  |

| е      |       | 0.50     | BSC.  | 0.0       | 20 BS0 | C.    |  |

| D2     |       | 12.00    | )     | 0         | .472   |       |  |

| E2     |       | 12.00    | )     | 0         | .472   |       |  |

|        | TOLER | ANCES    | OF FO | RM AND    | POSI   | FION  |  |

| aaa    | 0.20  |          |       | 0         | .008   |       |  |

| bbb    |       | 0.20     |       |           | .008   |       |  |

| ccc    |       | 0.08     |       | (         | 0.003  |       |  |

| ddd    |       | 0.08     |       | (         | 0.003  |       |  |

| Table 47-1. | Device and LQFP Package Maximum \ | Neiaht |

|-------------|-----------------------------------|--------|

|             |                                   |        |

| SAM4CM                  |                        | 800    |  | mg |

|-------------------------|------------------------|--------|--|----|

| Table 47-2.             | LQFP Package Reference |        |  |    |

| JEDEC Drawing Reference |                        | MS-026 |  |    |

#### Table 47-3. LQFP Package Characteristics

Moisture Sensitivity Level

**JESD97** Classification

3

e3

This package respects the recommendations of the NEMI User Group.

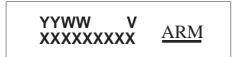

# 48. Marking

All devices are marked with the Atmel logo and the ordering code.

Additional marking is as follows:

where

- "YY": Manufactory year

- "WW": Manufactory week

- "V": Revision

- "XXXXXXXXX": Lot number