## Atmel - ATSAM4CMS8CA-AUR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | ARM® Cortex®-M4/M4F                                         |

| Core Size                  | 32-Bit Dual-Core                                            |

| Speed                      | 120MHz                                                      |

| Connectivity               | EBI/EMI, I²C, IrDA, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT             |

| Number of I/O              | 57                                                          |

| Program Memory Size        | 512KB (512K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 128K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                |

| Data Converters            | A/D 6x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 100-LQFP                                                    |

| Supplier Device Package    | 100-LQFP (14x14)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atsam4cms8ca-aur |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 12.6.5.2 AND, ORR, EOR, BIC, and ORN

Logical AND, OR, Exclusive OR, Bit Clear, and OR NOT.

Syntax

$op{S}{cond} {Rd}, Rn, Operand2$

where:

op

is one of:

AND logical AND. ORR logical OR, or bit set.

EOR logical Exclusive OR.

BIC logical AND NOT, or bit clear.

ORN logical OR NOT.

- S is an optional suffix. If S is specified, the condition code flags are updated on the result of the operation, see "Conditional Execution".

- cond is an optional condition code, see "Conditional Execution".

Rd is the destination register.

- Rn is the register holding the first operand.

- Operand2 is a flexible second operand. See "Flexible Second Operand" for details of the options.

## Operation

The AND, EOR, and ORR instructions perform bitwise AND, Exclusive OR, and OR operations on the values in *Rn* and *Operand2*.

The BIC instruction performs an AND operation on the bits in *Rn* with the complements of the corresponding bits in the value of *Operand*2.

The ORN instruction performs an OR operation on the bits in *Rn* with the complements of the corresponding bits in the value of *Operand2*.

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

If S is specified, these instructions:

- Update the N and Z flags according to the result

- Can update the C flag during the calculation of *Operand*2, see "Flexible Second Operand"

- Do not affect the V flag.

## 12.11.2.3 MPU Region Number Register

| Name:   | MPU_RNR    |    |     |      |    |    |    |

|---------|------------|----|-----|------|----|----|----|

| Access: | Read/Write |    |     |      |    |    |    |

| 31      | 30         | 29 | 28  | 27   | 26 | 25 | 24 |

| -       | -          | —  | —   | -    | -  | —  | -  |

| 23      | 22         | 21 | 20  | 19   | 18 | 17 | 16 |

| -       | -          | _  | _   | _    | _  | _  | -  |

| 15      | 14         | 13 | 12  | 11   | 10 | 9  | 8  |

| -       | -          | -  | -   | -    | -  | -  | -  |

| 7       | 6          | 5  | 4   | 3    | 2  | 1  | 0  |

|         |            |    | REG | SION |    |    |    |

The MPU\_RNR selects which memory region is referenced by the MPU\_RBAR and MPU\_RASRs.

## • REGION: MPU Region Referenced by the MPU\_RBAR and MPU\_RASRs

Indicates the MPU region referenced by the MPU\_RBAR and MPU\_RASRs.

The MPU supports 8 memory regions, so the permitted values of this field are 0–7.

Normally, the required region number is written to this register before accessing the MPU\_RBAR or MPU\_RASR. However, the region number can be changed by writing to the MPU\_RBAR with the VALID bit set to 1; see "MPU Region Base Address Register". This write updates the value of the REGION field.

12.11.2.8 MPU Region Base Address Register Alias 2

| Name:   | MPU_RBAR_A2 |    |       |    |     |      |    |

|---------|-------------|----|-------|----|-----|------|----|

| Access: | Read/Write  |    |       |    |     |      |    |

| 31      | 30          | 29 | 28    | 27 | 26  | 25   | 24 |

|         |             |    | ADI   | OR |     |      |    |

| 23      | 22          | 21 | 20    | 19 | 18  | 17   | 16 |

|         |             |    | ADI   | DR |     |      |    |

| 15      | 14          | 13 | 12    | 11 | 10  | 9    | 8  |

|         |             |    | ADI   | DR |     |      |    |

| 7       | 6           | 5  | 4     | 3  | 2   | 1    | 0  |

|         | ADDR        |    | VALID |    | REG | SION |    |

The MPU\_RBAR defines the base address of the MPU region selected by the MPU\_RNR, and can update the value of the MPU\_RNR.

Write MPU\_RBAR with the VALID bit set to 1 to change the current region number and update the MPU\_RNR.

## • ADDR: Region Base Address

Software must ensure that the value written to the ADDR field aligns with the size of the selected region.

The value of N depends on the region size. The ADDR field is bits[31:N] of the MPU\_RBAR. The region size, as specified by the SIZE field in the MPU\_RASR, defines the value of N:

N = Log2(Region size in bytes),

If the region size is configured to 4 GB, in the MPU\_RASR, there is no valid ADDR field. In this case, the region occupies the complete memory map, and the base address is 0x00000000.

The base address is aligned to the size of the region. For example, a 64 KB region must be aligned on a multiple of 64 KB, for example, at 0x00010000 or 0x00020000.

## • VALID: MPU Region Number Valid

Write:

0: MPU\_RNR not changed, and the processor updates the base address for the region specified in the MPU\_RNR, and ignores the value of the REGION field.

1: The processor updates the value of the MPU\_RNR to the value of the REGION field, and updates the base address for the region specified in the REGION field.

Always reads as zero.

## • REGION: MPU Region

For the behavior on writes, see the description of the VALID field.

On reads, returns the current region number, as specified by the MPU\_RNR.

## 12.12.2 Floating Point Unit (FPU) User Interface

| Offset     | Register                                       | Name   | Access     | Reset      |

|------------|------------------------------------------------|--------|------------|------------|

| 0xE000ED88 | ED88 Coprocessor Access Control Register       |        | Read/Write | 0x00000000 |

| 0xE000EF34 | Floating-point Context Control Register        | FPCCR  | Read/Write | 0xC0000000 |

| 0xE000EF38 | 00EF38 Floating-point Context Address Register |        | Read/Write | -          |

| _          | Floating-point Status Control Register         | FPSCR  | Read/Write | -          |

| 0xE000E01C | Floating-point Default Status Control Register | FPDSCR | Read/Write | 0x0000000  |

## Table 12-42. Floating Point Unit (FPU) Register Mapping

| Region            | A partition of memory space.                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved          | A field in a control register or instruction format is reserved if the field is to be defined by the implementation, or produces Unpredictable results if the contents of the field are not zero. These fields are reserved for use in future extensions of the architecture or are implementation-specific. All reserved bits not used by the implementation must be written as 0 and read as 0. |

| Thread-safe       | In a multi-tasking environment, thread-safe functions use safeguard mechanisms when accessing shared resources, to ensure correct operation without the risk of shared access conflicts.                                                                                                                                                                                                          |

| Thumb instruction | One or two halfwords that specify an operation for a processor to perform. Thumb instructions must be halfword-aligned.                                                                                                                                                                                                                                                                           |

| Unaligned         | A data item stored at an address that is not divisible by the number of bytes that defines the data size is said to be unaligned. For example, a word stored at an address that is not divisible by four.                                                                                                                                                                                         |

| Undefined         | Indicates an instruction that generates an Undefined instruction exception.                                                                                                                                                                                                                                                                                                                       |

| Unpredictable     | One cannot rely on the behavior. Unpredictable behavior must not represent security holes.<br>Unpredictable behavior must not halt or hang the processor, or any parts of the system.                                                                                                                                                                                                             |

| Warm reset        | Also known as a core reset. Initializes the majority of the processor excluding the debug controller and debug logic. This type of reset is useful if debugging features of a processor.                                                                                                                                                                                                          |

| Word              | A 32-bit data item.                                                                                                                                                                                                                                                                                                                                                                               |

| Write             | Writes are defined as operations that have the semantics of a store. Writes include the Thumb instructions STM, STR, STRH, STRB, and PUSH.                                                                                                                                                                                                                                                        |

## 17.6.7 RTC Status Register

| Name:<br>Address: | RTC_SR<br>0x400E1478 |       |       |       |     |       |        |

|-------------------|----------------------|-------|-------|-------|-----|-------|--------|

| Access:           | Read-only            |       |       |       |     |       |        |

| 31                | 30                   | 29    | 28    | 27    | 26  | 25    | 24     |

| _                 | -                    | _     | _     | _     | _   | _     | _      |

| 23                | 22                   | 21    | 20    | 19    | 18  | 17    | 16     |

| _                 | -                    | _     | -     | -     | -   | _     | -      |

| 15                | 14                   | 13    | 12    | 11    | 10  | 9     | 8      |

| _                 | -                    | _     | _     | _     | _   | _     | -      |

| 7                 | 6                    | 5     | 4     | 3     | 2   | 1     | 0      |

| _                 | _                    | TDERR | CALEV | TIMEV | SEC | ALARM | ACKUPD |

#### • ACKUPD: Acknowledge for Update

| Value | Name                                                 | Description                                    |  |

|-------|------------------------------------------------------|------------------------------------------------|--|

| 0     | FREERUN                                              | Time and calendar registers cannot be updated. |  |

| 1     | 1 UPDATE Time and calendar registers can be updated. |                                                |  |

#### • ALARM: Alarm Flag

| Value | Name          | Description                               |

|-------|---------------|-------------------------------------------|

| 0     | NO_ALARMEVENT | No alarm matching condition occurred.     |

| 1     | ALARMEVENT    | An alarm matching condition has occurred. |

#### • SEC: Second Event

| Value | Name        | Description                                                  |

|-------|-------------|--------------------------------------------------------------|

| 0     | NO_SECEVENT | No second event has occurred since the last clear.           |

| 1     | SECEVENT    | At least one second event has occurred since the last clear. |

## • TIMEV: Time Event

| Value      | Name Description |                                                            |

|------------|------------------|------------------------------------------------------------|

| 0          | NO_TIMEVENT      | No time event has occurred since the last clear.           |

| 1 TIMEVENT |                  | At least one time event has occurred since the last clear. |

Note: The time event is selected in the TIMEVSEL field in the Control Register (RTC\_CR) and can be any one of the following events: minute change, hour change, noon, midnight (day change).

## • CALEV: Calendar Event

| Value | Name        | Description                                                    |

|-------|-------------|----------------------------------------------------------------|

| 0     | NO_CALEVENT | No calendar event has occurred since the last clear.           |

| 1     | CALEVENT    | At least one calendar event has occurred since the last clear. |

Note: The calendar event is selected in the CALEVSEL field in the Control Register (RTC\_CR) and can be any one of the following events: week change, month change and year change.

## 26.9.8 Write Protection Status Register

| Name:    | MATRIX_WPSR                    |    |     |      |    |    |      |  |

|----------|--------------------------------|----|-----|------|----|----|------|--|

| Address: | 0x400E03E8 (0), 0x480101E8 (1) |    |     |      |    |    |      |  |

| Access:  | Read-only                      |    |     |      |    |    |      |  |

| 31       | 30                             | 29 | 28  | 27   | 26 | 25 | 24   |  |

| _        | -                              | -  | -   | -    | —  | -  | -    |  |

| 23       | 22                             | 21 | 20  | 19   | 18 | 17 | 16   |  |

|          |                                |    | WP\ | /SRC |    |    |      |  |

| 15       | 14                             | 13 | 12  | 11   | 10 | 9  | 8    |  |

|          |                                |    | WP\ | /SRC |    |    |      |  |

| 7        | 6                              | 5  | 4   | 3    | 2  | 1  | 0    |  |

| -        | -                              | -  | _   | -    | _  | _  | WPVS |  |

For more information on Write Protection registers, refer to Section 26.8 "Register Write Protection".

## • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of the MATRIX\_WPMR register.

1: A write protection violation has occurred since the last write of the MATRIX\_WPMR register. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC.

## • WPVSRC: Write Protection Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

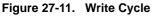

#### 27.9.3 Write Waveforms

The write protocol is similar to the read protocol. It is depicted in Figure 27-11. The write cycle starts with the address setting on the memory address bus.

## 27.9.3.1 NWE Waveforms

The NWE signal is characterized by a setup timing, a pulse width and a hold timing.

- NWE\_SETUP—the NWE setup time is defined as the setup of address and data before the NWE falling edge;

- NWE\_PULSE—the NWE pulse length is the time between NWE falling edge and NWE rising edge;

- NWE\_HOLD—the NWE hold time is defined as the hold time of address and data after the NWE rising edge.

## 27.9.3.2 NCS Waveforms

The NCS signal waveforms in write operation are not the same that those applied in read operations, but are separately defined:

- NCS\_WR\_SETUP—the NCS setup time is defined as the setup time of address before the NCS falling edge.

- NCS\_WR\_PULSE—the NCS pulse length is the time between NCS falling edge and NCS rising edge;

- NCS\_WR\_HOLD—the NCS hold time is defined as the hold time of address after the NCS rising edge.

## 27.9.3.3 Write Cycle

The write\_cycle time is defined as the total duration of the write cycle, that is, from the time where address is set on the address bus to the point where address may change. The total write cycle time is equal to:

NWE\_CYCLE=NWE\_SETUP + NWE\_PULSE + NWE\_HOLD=NCS\_WR\_SETUP + NCS\_WR\_PULSE + NCS\_WR\_HOLD

## 27.16.1 SMC Setup Register

Name: SMC\_SETUP[0..3]

Address: 0x400E0000 (0)[0], 0x400E0010 (0)[1], 0x400E0020 (0)[2], 0x400E0030 (0)[3], 0x4801C000 (1)[0], 0x4801C010 (1)[1], 0x4801C020 (1)[2], 0x4801C030 (1)[3]

| Access: | Read/Write |    |    |        |         |    |    |

|---------|------------|----|----|--------|---------|----|----|

| 31      | 30         | 29 | 28 | 27     | 26      | 25 | 24 |

| -       | -          |    |    | NCS_RE | D_SETUP |    |    |

| 23      | 22         | 21 | 20 | 19     | 18      | 17 | 16 |

| -       | _          |    |    | NRD_   | SETUP   |    |    |

| 15      | 14         | 13 | 12 | 11     | 10      | 9  | 8  |

| -       | -          |    |    | NCS_WF | R_SETUP |    |    |

| 7       | 6          | 5  | 4  | 3      | 2       | 1  | 0  |

| -       | -          |    |    | NWE_   | SETUP   |    |    |

This register can only be written if the WPEN bit is cleared in the "SMC Write Protection Mode Register" .

## • NWE\_SETUP: NWE Setup Length

The NWE signal setup length is defined as:

NWE setup length = (128\* NWE\_SETUP[5] + NWE\_SETUP[4:0]) clock cycles

## • NCS\_WR\_SETUP: NCS Setup Length in WRITE Access

In write access, the NCS signal setup length is defined as:

NCS setup length = (128\* NCS\_WR\_SETUP[5] + NCS\_WR\_SETUP[4:0]) clock cycles

## • NRD\_SETUP: NRD Setup Length

The NRD signal setup length is defined in clock cycles as: NRD setup length = (128\* NRD\_SETUP[5] + NRD\_SETUP[4:0]) clock cycles

## NCS\_RD\_SETUP: NCS Setup Length in READ Access

In read access, the NCS signal setup length is defined as: NCS setup length = (128\* NCS\_RD\_SETUP[5] + NCS\_RD\_SETUP[4:0]) clock cycles

## 28.5.7 Transmit Next Pointer Register

| Name:   | PERIPH_TNPR |    |     |     |    |    |    |

|---------|-------------|----|-----|-----|----|----|----|

| Access: | Read/Write  |    |     |     |    |    |    |

| 31      | 30          | 29 | 28  | 27  | 26 | 25 | 24 |

|         |             |    | TXN | PTR |    |    |    |

| 23      | 22          | 21 | 20  | 19  | 18 | 17 | 16 |

|         |             |    | TXN | PTR |    |    |    |

| 15      | 14          | 13 | 12  | 11  | 10 | 9  | 8  |

|         |             |    | TXN | PTR |    |    |    |

| 7       | 6           | 5  | 4   | 3   | 2  | 1  | 0  |

|         |             |    | TXN | PTR |    |    |    |

## • TXNPTR: Transmit Next Pointer

TXNPTR contains the next transmit buffer address.

When a half-duplex peripheral is connected to the PDC, RXNPTR = TXNPTR.

## 30.18.14PMC Interrupt Disable Register

| Name:<br>Address: | PMC_IDR<br>0x400E0464 |                |    |         |             |               |                |

|-------------------|-----------------------|----------------|----|---------|-------------|---------------|----------------|

| Access:           | Write-only            |                |    |         |             |               |                |

| 31                | 30                    | 29             | 28 | 27      | 26          | 25            | 24             |

| _                 | _                     | _              | —  | _       | _           | —             | —              |

| 23                | 22                    | 21<br>XT32KERR | 20 | 19<br>— | 18<br>CFDEV | 17<br>MOSCRCS | 16<br>MOSCSELS |

| 15                | 14                    | 13             | 12 | 11      | 10          | 9             | 8              |

| —                 | -                     | -              | -  | -       | PCKRDY2     | PCKRDY1       | PCKRDY0        |

| 7                 | 6                     | 5              | 4  | 3       | 2           | 1             | 0              |

| -                 | -                     | _              | —  | MCKRDY  | LOCKB       | LOCKA         | MOSCXTS        |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

- 1: Disables the corresponding interrupt.

- MOSCXTS: 3 to 20 MHz Crystal Oscillator Status Interrupt Disable

- LOCKA: PLLA Lock Interrupt Disable

- LOCKB: PLLB Lock Interrupt Disable

- MCKRDY: Master Clock Ready Interrupt Disable

- PCKRDYx: Programmable Clock Ready x Interrupt Disable

- MOSCSELS: Main Clock Source Oscillator Selection Status Interrupt Disable

- MOSCRCS: 4/8/12 MHz RC Oscillator Status Interrupt Disable

- CFDEV: Clock Failure Detector Event Interrupt Disable

- XT32KERR: 32.768 kHz Oscillator Error Interrupt Disable

## 32.6.20 PIO Multi-driver Status Register

Name: PIO\_MDSR

Address: 0x400E0E58 (PIOA), 0x400E1058 (PIOB), 0x4800C058 (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Multi-drive Status

0: The multi-drive is disabled on the I/O line. The pin is driven at high- and low-level.

1: The multi-drive is enabled on the I/O line. The pin is driven at low-level only.

#### 33.7.3.10 Mode Fault Detection

The SPI has the capability to operate in multi-master environment. Consequently, the NPCS0/NSS line must be monitored. If one of the masters on the SPI bus is currently transmitting, the NPCS0/NSS line is low and the SPI must not transmit any data. A mode fault is detected when the SPI is programmed in Master mode and a low level is driven by an external master on the NPCS0/NSS signal. In multi-master environment, NPCS0, MOSI, MISO and SPCK pins must be configured in open drain (through the PIO controller). When a mode fault is detected, the SPI\_SR.MODF bit is set until SPI\_SR is read and the SPI is automatically disabled until it is re-enabled by writing a 1 to the SPI\_CR.SPIEN bit.

By default, the mode fault detection is enabled. The user can disable it by setting the SPI\_MR.MODFDIS bit.

## 33.7.4 SPI Slave Mode

When operating in Slave mode, the SPI processes data bits on the clock provided on the SPI clock pin (SPCK).

The SPI waits until NSS goes active before receiving the serial clock from an external master. When NSS falls, the clock is validated and the data is loaded in the SPI\_RDR depending on the BITS field configured in the SPI\_CSR0. These bits are processed following a phase and a polarity defined respectively by the NCPHA and CPOL bits in the SPI\_CSR0. Note that BITS, CPOL and NCPHA of the other Chip Select registers have no effect when the SPI is programmed in Slave mode.

The bits are shifted out on the MISO line and sampled on the MOSI line.

Note: For more information on the BITS field, see also the note below the SPI\_CSRx register bitmap (Section 33.8.9 "SPI Chip Select Register").

When all bits are processed, the received data is transferred in the SPI\_RDR and the RDRF bit rises. If the SPI\_RDR has not been read before new data is received, the Overrun Error Status (OVRES) bit in the SPI\_SR is set. As long as this flag is set, data is loaded in the SPI\_RDR. The user must read SPI\_SR to clear the OVRES bit.

When a transfer starts, the data shifted out is the data present in the Shift register. If no data has been written in the SPI\_TDR, the last data received is transferred. If no data has been received since the last reset, all bits are transmitted low, as the Shift register resets to 0.

When a first data is written in the SPI\_TDR, it is transferred immediately in the Shift register and the TDRE flag rises. If new data is written, it remains in the SPI\_TDR until a transfer occurs, i.e., NSS falls and there is a valid clock on the SPCK pin. When the transfer occurs, the last data written in the SPI\_TDR is transferred in the Shift register and the TDRE flag rises. This enables frequent updates of critical variables with single transfers.

Then, new data is loaded in the Shift register from the SPI\_TDR. If no character is ready to be transmitted, i.e., no character has been written in the SPI\_TDR since the last load from the SPI\_TDR to the Shift register, the SPI\_TDR is retransmitted. In this case the Underrun Error Status Flag (UNDES) is set in the SPI\_SR.

Figure 33-13 shows a block diagram of the SPI when operating in Slave mode.

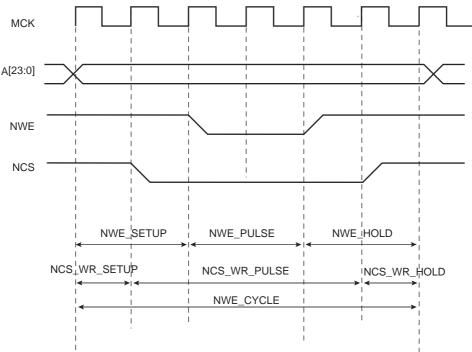

Figure 34-20. TWI Read Operation with Multiple Data Bytes with or without Internal Address

## 36. Universal Synchronous Asynchronous Receiver Transceiver (USART)

## 36.1 Description

The Universal Synchronous Asynchronous Receiver Transceiver (USART) provides one full duplex universal synchronous asynchronous serial link. Data frame format is widely programmable (data length, parity, number of stop bits) to support a maximum of standards. The receiver implements parity error, framing error and overrun error detection. The receiver time-out enables handling variable-length frames and the transmitter timeguard facilitates communications with slow remote devices. Multidrop communications are also supported through address bit handling in reception and transmission.

The USART features three test modes: Remote loopback, Local loopback and Automatic echo.

The USART supports specific operating modes providing interfaces on RS485, and SPI buses, with ISO7816 T = 0 or T = 1 smart card slots and infrared transceivers. The hardware handshaking feature enables an out-of-band flow control by automatic management of the pins RTS and CTS.

The USART supports the connection to the Peripheral DMA Controller, which enables data transfers to the transmitter and from the receiver. The PDC provides chained buffer management without any intervention of the processor.

## 36.2 Embedded Characteristics

- Programmable Baud Rate Generator

- 5- to 9-bit Full-duplex Synchronous or Asynchronous Serial Communications

- 1, 1.5 or 2 Stop Bits in Asynchronous Mode or 1 or 2 Stop Bits in Synchronous Mode

- Parity Generation and Error Detection

- Framing Error Detection, Overrun Error Detection

- Digital Filter on Receive Line

- MSB- or LSB-first

- Optional Break Generation and Detection

- By 8 or by 16 Over-sampling Receiver Frequency

- Optional Hardware Handshaking RTS-CTS

- Receiver Time-out and Transmitter Timeguard

- Optional Multidrop Mode with Address Generation and Detection

- RS485 with Driver Control Signal

- ISO7816, T = 0 or T = 1 Protocols for Interfacing with Smart Cards

- NACK Handling, Error Counter with Repetition and Iteration Limit

- IrDA Modulation and Demodulation

- Communication at up to 115.2 kbit/s

- SPI Mode

- Master or Slave

- Serial Clock Programmable Phase and Polarity

- SPI Serial Clock (SCK) Frequency up to f<sub>peripheral clock</sub>/6

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

- Supports Connection of:

- Two Peripheral DMA Controller Channels (PDC)

The baud rate error is calculated with the following formula. It is not recommended to work with an error higher than 5%.

$$Error = 1 - \left(\frac{ExpectedBaudRate}{ActualBaudRate}\right)$$

#### 36.6.1.2 Fractional Baud Rate in Asynchronous Mode

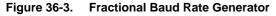

The baud rate generator is subject to the following limitation: the output frequency changes only by integer multiples of the reference frequency. An approach to this problem is to integrate a fractional N clock generator that has a high resolution. The generator architecture is modified to obtain baud rate changes by a fraction of the reference source clock. This fractional part is programmed with the FP field in the US\_BRGR. If FP is not 0, the fractional part is activated. The resolution is one eighth of the clock divider. This feature is only available when using USART normal mode. The fractional baud rate is calculated using the following formula:

$$Baudrate = \frac{SelectedClock}{\left(8(2 - Over)\left(CD + \frac{FP}{8}\right)\right)}$$

The modified architecture is presented in the following Figure 36-3.

#### 36.6.1.3 Baud Rate in Synchronous Mode or SPI Mode

If the USART is programmed to operate in Synchronous mode, the selected clock is simply divided by the field CD in the US\_BRGR.

$$BaudRate = \frac{SelectedClock}{CD}$$

In Synchronous mode, if the external clock is selected (USCLKS = 3), the clock is provided directly by the signal on the USART SCK pin. No division is active. The value written in US\_BRGR has no effect. The external clock frequency must be at least 3 times lower than the system clock. In Synchronous mode master (USCLKS = 0 or 1, CLKO set to 1), the receive part limits the SCK maximum frequency to  $f_{peripheral clock}/3$  in USART mode, or  $f_{peripheral clock}/6$  in SPI mode.

# Atmel

#### Figure 36-25. Break Transmission

| JU |   | Л            | IJ          | [                     |                          |                             |                               |                                   | Л                                    |                                                    | mmmm                                                       | hunnunund                                                                                  |                       |

|----|---|--------------|-------------|-----------------------|--------------------------|-----------------------------|-------------------------------|-----------------------------------|--------------------------------------|----------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|

|    | Γ |              |             |                       |                          |                             |                               |                                   |                                      |                                                    |                                                            |                                                                                            | -                     |

|    |   | D0 D1        | D2          | D3                    | D4                       | D5                          | D6                            | D7                                | Parity<br>Bit                        | Stop<br>Bit                                        | Break Transmission                                         | End of Break                                                                               |                       |

|    |   |              | S           | ттв                   | RK =                     | = 1                         |                               |                                   |                                      |                                                    | STPBRK = 1                                                 |                                                                                            |                       |

|    |   |              |             |                       | <u>Î</u>                 |                             |                               |                                   |                                      |                                                    | Î                                                          |                                                                                            |                       |

|    |   |              |             |                       |                          |                             |                               |                                   |                                      |                                                    |                                                            |                                                                                            |                       |

|    | Γ |              |             |                       | ٦                        |                             |                               |                                   |                                      |                                                    |                                                            |                                                                                            | -                     |

|    | 1 |              |             |                       | _                        |                             |                               |                                   |                                      |                                                    |                                                            |                                                                                            |                       |

|    |   |              |             |                       |                          |                             |                               |                                   |                                      |                                                    |                                                            |                                                                                            |                       |

|    |   | Start<br>Bit | Start po p1 | Start<br>Bit D0 D1 D2 | Start<br>Bit D0 D1 D2 D3 | Start<br>Bit D0 D1 D2 D3 D4 | Start pp. pt. pt. pt. pt. pt. | Start<br>Bit D0 D1 D2 D3 D4 D5 D6 | Start<br>Bit D0 D1 D2 D3 D4 D5 D6 D7 | Start<br>Bit D0 D1 D2 D3 D4 D5 D6 D7 Parity<br>Bit | Start<br>Bit D0 D1 D2 D3 D4 D5 D6 D7 ParityStop<br>Bit Bit | Start<br>Bit D0 D1 D2 D3 D4 D5 D6 D7 ParityStop<br>Bit Bit Bit Bit Bit Bit Bit Bit Bit Bit | Bit Bit Bit Bit Bit A |

#### 36.6.3.14 Receive Break

The receiver detects a break condition when all data, parity and stop bits are low. This corresponds to detecting a framing error with data to 0x00, but FRAME remains low.

When the low stop bit is detected, the receiver asserts the RXBRK bit in US\_CSR. This bit may be cleared by writing a 1 to the RSTSTA bit in the US\_CR.

An end of receive break is detected by a high level for at least 2/16 of a bit period in Asynchronous operating mode or one sample at high level in Synchronous operating mode. The end of break detection also asserts the RXBRK bit.

#### 36.6.3.15 Hardware Handshaking

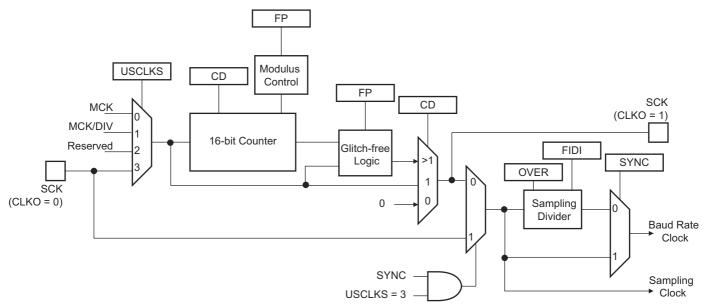

The USART features a hardware handshaking out-of-band flow control. The RTS and CTS pins are used to connect with the remote device, as shown in Figure 36-26.

| USART |   | Remote<br>Device |

|-------|---|------------------|

| TXD   |   | RXD              |

| RXD   | • | TXD              |

| CTS   | • | RTS              |

| RTS   |   | CTS              |

Setting the USART to operate with hardware handshaking is performed by writing the USART\_MODE field in US\_MR to the value 0x2.

The USART behavior when hardware handshaking is enabled is the same as the behavior in standard Synchronous or Asynchronous mode, except that the receiver drives the RTS pin as described below and the level on the CTS pin modifies the behavior of the transmitter as described below. Using this mode requires using the PDC channel for reception. The transmitter can handle hardware handshaking in any case.

Figure 36-27 shows how the receiver operates if hardware handshaking is enabled. The RTS pin is driven high if the receiver is disabled or if the status RXBUFF (Receive Buffer Full) coming from the PDC channel is high. Normally, the remote device does not start transmitting while its CTS pin (driven by RTS) is high. As soon as the receiver is enabled, the RTS falls, indicating to the remote device that it can start transmitting. Defining a new buffer in the PDC clears the status bit RXBUFF and, as a result, asserts the pin RTS low.

## 36.7.12 USART Channel Status Register (SPI\_MODE)

US\_CSR (SPL\_MODE)

Namo

| Name.    |                                                                                |      |        |        |      |         |       |  |

|----------|--------------------------------------------------------------------------------|------|--------|--------|------|---------|-------|--|

| Address: | 0x40024014 (0), 0x40028014 (1), 0x4002C014 (2), 0x40030014 (3), 0x40034014 (4) |      |        |        |      |         |       |  |

| Access:  | Read-only                                                                      |      |        |        |      |         |       |  |

| 31       | 30                                                                             | 29   | 28     | 27     | 26   | 25      | 24    |  |

| _        | -                                                                              | -    | -      | -      | -    | -       | -     |  |

| 23       | 22                                                                             | 21   | 20     | 19     | 18   | 17      | 16    |  |

| _        | -                                                                              | -    | _      | _      | -    | -       | -     |  |

| 15       | 14                                                                             | 13   | 12     | 11     | 10   | 9       | 8     |  |

| -        | -                                                                              | -    | RXBUFF | TXBUFE | UNRE | TXEMPTY | -     |  |

| 7        | -                                                                              |      |        | -      |      |         | 2     |  |

| /        | 6                                                                              | 5    | 4      | 3      | 2    | 1       | 0     |  |

| _        | -                                                                              | OVRE | ENDTX  | ENDRX  | —    | TXRDY   | RXRDY |  |

This configuration is relevant only if USART\_MODE = 0xE or 0xF in the USART Mode Register.

## • RXRDY: Receiver Ready (cleared by reading US\_RHR)

0: No complete character has been received since the last read of US\_RHR or the receiver is disabled. If characters were being received when the receiver was disabled, RXRDY changes to 1 when the receiver is enabled.

1: At least one complete character has been received and US\_RHR has not yet been read.

## • TXRDY: Transmitter Ready (cleared by writing US\_THR)

0: A character is in the US\_THR waiting to be transferred to the Transmit Shift Register or the transmitter is disabled. As soon as the transmitter is enabled, TXRDY becomes 1.

1: There is no character in the US\_THR.

## • ENDRX: End of RX Buffer (cleared by writing US\_RCR or US\_RNCR)

0: The Receive Counter Register has not reached 0 since the last write in US\_RCR or US\_RNCR<sup>(1)</sup>.

1: The Receive Counter Register has reached 0 since the last write in US\_RCR or US\_RNCR<sup>(1)</sup>.

## • ENDTX: End of TX Buffer (cleared by writing US\_TCR or US\_TNCR)

0: The Transmit Counter Register has not reached 0 since the last write in US\_TCR or US\_TNCR<sup>(1)</sup>.

1: The Transmit Counter Register has reached 0 since the last write in US\_TCR or US\_TNCR<sup>(1)</sup>.

## OVRE: Overrun Error (cleared by writing a one to bit US\_CR.RSTSTA)

0: No overrun error has occurred since the last RSTSTA.

1: At least one overrun error has occurred since the last RSTSTA.

## • TXEMPTY: Transmitter Empty (cleared by writing US\_THR)

0: There are characters in either US\_THR or the Transmit Shift Register, or the transmitter is disabled.

1: There are no characters in US\_THR, nor in the Transmit Shift Register.

| 43.5.2.3 ICN | 43.5.2.3 ICM Region Control Structure Member |                |     |      |    |    |    |  |

|--------------|----------------------------------------------|----------------|-----|------|----|----|----|--|

| Name:        | ICM_RCTRL                                    |                |     |      |    |    |    |  |

| Address:     | ICM_DSCR+0x0                                 | )08+RID*(0x10) | )   |      |    |    |    |  |

| Access:      | Read/Write                                   |                |     |      |    |    |    |  |

| 31           | 30                                           | 29             | 28  | 27   | 26 | 25 | 24 |  |

| _            | —                                            | -              | -   | _    | —  | -  | —  |  |

| 23           | 22                                           | 21             | 20  | 19   | 18 | 17 | 16 |  |

| _            | -                                            | _              | _   | _    | _  | _  | -  |  |

| 15           | 14                                           | 13             | 12  | 11   | 10 | 9  | 8  |  |

|              | TRSIZE                                       |                |     |      |    |    |    |  |

| 7            | 7 6 5 4 3 2 1 0                              |                |     |      |    |    |    |  |

|              |                                              |                | TRS | SIZE |    |    |    |  |

|              |                                              |                |     |      |    |    |    |  |

## • TRSIZE: Transfer Size for the Current Chunk of Data

ICM performs a transfer of (TRSIZE + 1) blocks of 512 bits.

## 43.6.8 ICM Undefined Access Status Register

| Name:    | ICM_UASR   |    |    |    |    |      |    |

|----------|------------|----|----|----|----|------|----|

| Address: | 0x40044020 |    |    |    |    |      |    |

| Access:  | Read-only  |    |    |    |    |      |    |

| 31       | 30         | 29 | 28 | 27 | 26 | 25   | 24 |

| _        | -          | _  | _  | _  | _  | _    | _  |

| 23       | 22         | 21 | 20 | 19 | 18 | 17   | 16 |

| _        | _          | _  | _  | -  | -  | _    | _  |

| 15       | 14         | 13 | 12 | 11 | 10 | 9    | 8  |

| _        | -          | _  | _  | _  | -  | _    | _  |

| 7        | 6          | 5  | 4  | 3  | 2  | 1    | 0  |

| _        | -          | _  | _  | _  |    | URAT |    |

## • URAT: Undefined Register Access Trace

| Value | Name                 | Description                                                                     |

|-------|----------------------|---------------------------------------------------------------------------------|

| 0     | UNSPEC_STRUCT_MEMBER | Unspecified structure member set to one detected when the descriptor is loaded. |

| 1     | ICM_CFG_MODIFIED     | ICM_CFG modified during active monitoring.                                      |

| 2     | ICM_DSCR_MODIFIED    | ICM_DSCR modified during active monitoring.                                     |

| 3     | ICM_HASH_MODIFIED    | ICM_HASH modified during active monitoring                                      |

| 4     | READ_ACCESS          | Write-only register read access                                                 |

Only the first Undefined Register Access Trace is available through the URAT field.

The URAT field is only reset by the SWRST bit in the ICM\_CTRL register.