# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4/M4F                                                        |

| Core Size                  | 32-Bit Dual-Core                                                           |

| Speed                      | 120MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                            |

| Number of I/O              | 57                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 6x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-LQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4cms8cb-aur |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The SAM-BA Boot provides an interface with SAM-BA Graphic User Interface (GUI).

The SAM-BA Boot is in ROM and is mapped in Flash at address 0x0 when GPNVM bit 1 is set to 0.

## 8.1.4.10 GPNVM Bits

The SAM4CM features two (SAM4CM16/SAM4CM8/SAM4CM4) or three (SAM4CM32) GPNVM bits. These bits can be cleared or set respectively through the commands "Clear GPNVM Bit" and "Set GPNVM Bit" of the EEFC User Interface (refer to Section 22. "Enhanced Embedded Flash Controller (EEFC)").

| Table 8-3. | General-purpose Nonvolatile Memory Bits |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

| GPNVM Bit | Function                                                         |

|-----------|------------------------------------------------------------------|

| 0         | Security bit                                                     |

| 1         | Boot mode selection                                              |

| 2         | Memory Plane Boot Selection (Plane 0 or Plane 1) (SAM4CM32 only) |

## 8.1.5 Boot Strategy

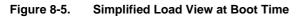

Figure 8-5 below shows a load view of the memory at boot time.

Note: Matrices, AHB and APB Bridges are not represented.

## 8.1.5.1 Application Core (Core 0) Boot Process

The application processor (CM4P0) always boots at the address 0x0. To ensure maximum boot possibilities, the memory layout can be changed using a General-purpose NVM (GPNVM) bit. A GPNVM bit is used to boot either on the ROM (default) or from the Flash. The GPNVM bit can be cleared or set through the commands "Clear General-purpose NVM Bit" and "Set General-purpose NVM Bit" of the EEFC User Interface. Setting GPNVM Bit 1 selects the boot from Flash whereas clearing this bit selects the boot from ROM. Asserting ERASE clears the GPNVM Bit 1 and thus selects the boot from the ROM by default.

| 12.4.1.15 B | 12.4.1.15 Base Priority Mask Register |    |    |      |    |    |    |  |

|-------------|---------------------------------------|----|----|------|----|----|----|--|

| Name:       | BASEPRI                               |    |    |      |    |    |    |  |

| Access:     | Read/Write                            |    |    |      |    |    |    |  |

| Reset:      | 0x00000000                            |    |    |      |    |    |    |  |

| 31          | 30                                    | 29 | 28 | 27   | 26 | 25 | 24 |  |

|             |                                       |    | -  | -    |    |    |    |  |

| 23          | 22                                    | 21 | 20 | 19   | 18 | 17 | 16 |  |

|             |                                       |    | -  | -    |    |    |    |  |

| 15          | 14                                    | 13 | 12 | - 11 | 10 | 9  | 8  |  |

|             |                                       |    | -  | _    |    |    |    |  |

| 7           | 6                                     | 5  | 4  | 3    | 2  | 1  | 0  |  |

|             | BASEPRI                               |    |    |      |    |    |    |  |

The BASEPRI register defines the minimum priority for exception processing. When BASEPRI is set to a nonzero value, it prevents the activation of all exceptions with same or lower priority level as the BASEPRI value.

## BASEPRI

Priority mask bits:

0x0000: No effect

Nonzero: Defines the base priority for exception processing

The processor does not process any exception with a priority value greater than or equal to BASEPRI.

This field is similar to the priority fields in the interrupt priority registers. The processor implements only bits[7:4] of this field, bits[3:0] read as zero and ignore writes. See "Interrupt Priority Registers" for more information. Remember that higher priority field values correspond to lower exception priorities.

For more information about hard faults, memory management faults, bus faults, and usage faults, see "Fault Handling".

## 12.4.3.3 Exception Handlers

The processor handles exceptions using:

- Interrupt Service Routines (ISRs) Interrupts IRQ0 to IRQ40 are the exceptions handled by ISRs.

- Fault Handlers Hard fault, memory management fault, usage fault, bus fault are fault exceptions handled by the fault handlers.

- System Handlers NMI, PendSV, SVCall SysTick, and the fault exceptions are all system exceptions that are handled by system handlers.

## 12.4.3.4 Vector Table

The vector table contains the reset value of the stack pointer, and the start addresses, also called exception vectors, for all exception handlers. Figure 12-6 shows the order of the exception vectors in the vector table. The least-significant bit of each vector must be 1, indicating that the exception handler is Thumb code.

| Exception number | IRQ number | Offset           | Vector                  |

|------------------|------------|------------------|-------------------------|

| 255              | 239        | 0x03FC           | IRQ239                  |

|                  |            |                  |                         |

|                  |            | •                |                         |

| 18               | 2          | 0x004C           | IRQ2                    |

| 17               | 1          | 0x0048<br>0x0044 | IRQ1                    |

| 16               | 0          | 0x0044<br>0x0040 | IRQ0                    |

| 15               | -1         | 0x003C           | SysTick                 |

| 14               | -2         | 0x0038           | PendSV                  |

| 13               |            |                  | Reserved                |

| 12               |            |                  | Reserved for Debug      |

| 11               | -5         | 0x002C           | SVCall                  |

| 10               |            | 0.0020           |                         |

| 9                |            |                  | Reserved                |

| 8                |            |                  | 1 COOLLOG               |

| 7                |            |                  |                         |

| 6                | -10        | 0x0018           | Usage fault             |

| 5                | -11        |                  | Bus fault               |

| 4                | -12        | 0x0014           | Memory management fault |

| 3                | -13        | 0x0010           | Hard fault              |

| 2                | -14        | 0x000C           | NMI                     |

| 1                |            | 0x0008           | Reset                   |

|                  |            |                  | Initial SP value        |

|                  |            | 0x0004<br>0x0000 |                         |

#### Figure 12-6. Vector Table

On system reset, the vector table is fixed at address 0x00000000. Privileged software can write to the SCB\_VTOR to relocate the vector table start address to a different memory location, in the range 0x00000080 to 0x3FFFF80, see "Vector Table Offset Register".

| Mnemonic                         | Operands               | Description                                       | Flags   |

|----------------------------------|------------------------|---------------------------------------------------|---------|

| SMULBB, SMULBT<br>SMULTB, SMULTT | {Rd,} Rn, Rm           | Signed Multiply (halfwords)                       | -       |

| SMULL                            | RdLo, RdHi, Rn, Rm     | Signed Multiply ( $32 \times 32$ ), 64-bit result | -       |

| SMULWB, SMULWT                   | {Rd,} Rn, Rm           | Signed Multiply word by halfword                  | _       |

| SMUSD, SMUSDX                    | {Rd,} Rn, Rm           | Signed dual Multiply Subtract                     | -       |

| SSAT                             | Rd, #n, Rm {,shift #s} | Signed Saturate                                   | Q       |

| SSAT16                           | Rd, #n, Rm             | Signed Saturate 16                                | Q       |

| SSAX                             | {Rd,} Rn, Rm           | Signed Subtract and Add with Exchange             | GE      |

| SSUB16                           | {Rd,} Rn, Rm           | Signed Subtract 16                                | _       |

| SSUB8                            | {Rd,} Rn, Rm           | Signed Subtract 8                                 | _       |

| STM                              | Rn{!}, reglist         | Store Multiple registers, increment after         | _       |

| STMDB, STMEA                     | Rn{!}, reglist         | Store Multiple registers, decrement before        | -       |

| STMFD, STMIA                     | Rn{!}, reglist         | Store Multiple registers, increment after         | -       |

| STR                              | Rt, [Rn, #offset]      | Store Register word                               | -       |

| STRB, STRBT                      | Rt, [Rn, #offset]      | Store Register byte                               | -       |

| STRD                             | Rt, Rt2, [Rn, #offset] | Store Register two words                          | -       |

| STREX                            | Rd, Rt, [Rn, #offset]  | Store Register Exclusive                          | -       |

| STREXB                           | Rd, Rt, [Rn]           | Store Register Exclusive byte                     | -       |

| STREXH                           | Rd, Rt, [Rn]           | Store Register Exclusive halfword                 | -       |

| STRH, STRHT                      | Rt, [Rn, #offset]      | Store Register halfword                           | _       |

| STRT                             | Rt, [Rn, #offset]      | Store Register word                               | _       |

| SUB, SUBS                        | {Rd,} Rn, Op2          | Subtract                                          | N,Z,C,V |

| SUB, SUBW                        | {Rd,} Rn, #imm12       | Subtract                                          | N,Z,C,V |

| SVC                              | #imm                   | Supervisor Call                                   | _       |

| SXTAB                            | {Rd,} Rn, Rm,{,ROR #}  | Extend 8 bits to 32 and add                       | _       |

| SXTAB16                          | {Rd,} Rn, Rm,{,ROR #}  | Dual extend 8 bits to 16 and add                  | _       |

| SXTAH                            | {Rd,} Rn, Rm,{,ROR #}  | Extend 16 bits to 32 and add                      | _       |

| SXTB16                           | {Rd,} Rm {,ROR #n}     | Signed Extend Byte 16                             | _       |

| SXTB                             | {Rd,} Rm {,ROR #n}     | Sign extend a byte                                | _       |

| SXTH                             | {Rd,} Rm {,ROR #n}     | Sign extend a halfword                            | -       |

| ТВВ                              | [Rn, Rm]               | Table Branch Byte                                 | -       |

| ТВН                              | [Rn, Rm, LSL #1]       | Table Branch Halfword                             | -       |

| TEQ                              | Rn, Op2                | Test Equivalence                                  | N,Z,C   |

| TST                              | Rn, Op2                | Test                                              | N,Z,C   |

| UADD16                           | {Rd,} Rn, Rm           | Unsigned Add 16                                   | GE      |

| UADD8                            | {Rd,} Rn, Rm           | Unsigned Add 8                                    | GE      |

| USAX                             | {Rd,} Rn, Rm           | Unsigned Subtract and Add with Exchange           | GE      |

| JSAX                             | {Ka,} Kn, Km           | Unsigned Subtract and Add with Exchange           | GE      |

## Table 12-13. Cortex-M4 Instructions (Continued)

## 12.9.1.17 Bus Fault Address Register

| Name:   | SCB_BFAR   |    |      |      |    |    |    |

|---------|------------|----|------|------|----|----|----|

| Access: | Read/Write |    |      |      |    |    |    |

| 31      | 30         | 29 | 28   | 27   | 26 | 25 | 24 |

|         |            |    | ADDF | RESS |    |    |    |

| 23      | 22         | 21 | 20   | 19   | 18 | 17 | 16 |

|         |            |    | ADDF | RESS |    |    |    |

| 15      | 14         | 13 | 12   | 11   | 10 | 9  | 8  |

|         |            |    | ADDF | RESS |    |    |    |

| 7       | 6          | 5  | 4    | 3    | 2  | 1  | 0  |

|         |            |    | ADDF | RESS |    |    |    |

The SCB\_BFAR contains the address of the location that generated a bus fault.

## • ADDRESS: Bus Fault Generation Location Address

When the BFARVALID bit of the BFSR subregister is set to 1, this field holds the address of the location that generated the bus fault.

Notes: 1. When an unaligned access faults, the address in the SCB\_BFAR is the one requested by the instruction, even if it is not the address of the fault.

2. Flags in the BFSR indicate the cause of the fault, and whether the value in the SCB\_BFAR is valid. See "BFSR: Bus Fault Status Subregister".

## 12.11.2.3 MPU Region Number Register

| Name:   | MPU_RNR    |    |     |      |    |    |    |

|---------|------------|----|-----|------|----|----|----|

| Access: | Read/Write |    |     |      |    |    |    |

| 31      | 30         | 29 | 28  | 27   | 26 | 25 | 24 |

| -       | -          | —  | —   | -    | -  | —  | -  |

| 23      | 22         | 21 | 20  | 19   | 18 | 17 | 16 |

| -       | -          | _  | _   | _    | _  | _  | -  |

| 15      | 14         | 13 | 12  | 11   | 10 | 9  | 8  |

| -       | -          | -  | -   | -    | -  | -  | -  |

| 7       | 6          | 5  | 4   | 3    | 2  | 1  | 0  |

|         |            |    | REG | SION |    |    |    |

The MPU\_RNR selects which memory region is referenced by the MPU\_RBAR and MPU\_RASRs.

## • REGION: MPU Region Referenced by the MPU\_RBAR and MPU\_RASRs

Indicates the MPU region referenced by the MPU\_RBAR and MPU\_RASRs.

The MPU supports 8 memory regions, so the permitted values of this field are 0–7.

Normally, the required region number is written to this register before accessing the MPU\_RBAR or MPU\_RASR. However, the region number can be changed by writing to the MPU\_RBAR with the VALID bit set to 1; see "MPU Region Base Address Register". This write updates the value of the REGION field.

## 12.12.2.1 Coprocessor Access Control Register

| Name:   | CPACR      |    |     |    |    |    |    |

|---------|------------|----|-----|----|----|----|----|

| Access: | Read/Write |    |     |    |    |    |    |

| 31      | 30         | 29 | 28  | 27 | 26 | 25 | 24 |

| _       | -          | _  | -   | -  | -  | -  | -  |

| 23      | 22         | 21 | 20  | 19 | 18 | 17 | 16 |

|         | CP11       | CI | P10 | -  | -  | -  | -  |

| 15      | 14         | 13 | 12  | 11 | 10 | 9  | 8  |

| _       | -          | _  | -   | -  | -  | -  | -  |

| 7       | 6          | 5  | 4   | 3  | 2  | 1  | 0  |

| _       | -          | _  | _   | _  | _  | _  | _  |

The CPACR specifies the access privileges for coprocessors.

## • CP10: Access Privileges for Coprocessor 10

The possible values of each field are:

0: Access denied. Any attempted access generates a NOCP UsageFault.

1: Privileged access only. An unprivileged access generates a NOCP fault.

2: Reserved. The result of any access is unpredictable.

3: Full access.

## • CP11: Access Privileges for Coprocessor 11

The possible values of each field are:

0: Access denied. Any attempted access generates a NOCP UsageFault.

1: Privileged access only. An unprivileged access generates a NOCP fault.

2: Reserved. The result of any access is unpredictable.

3: Full access.

## 20.4.5 Using Backup Battery/Automatic Power Switch

The power switch automatically selects either VDDBU or VDDIO as a power source.

As soon as VDDIO is present (higher than 1.9V), it supplies the backup area of the device (VDDBU\_SW = VDDIO) even if the voltage of VDDBU is higher than VDDIO. If not, the backup area is supplied by the VDDBU voltage source (VDDBU\_SW = VDDBU). For more information on power supply schematics, refer to the section "Power Supplies".

## 20.4.6 Supply Monitor

The SUPC embeds a supply monitor located in the VDDBU\_SW power domain and which monitors VDDIO power supply.

The supply monitor can be used to prevent the processor from falling into an unpredictable state if the main power supply drops below a certain level.

The threshold of the supply monitor is programmable. It can be selected from 1.9V to 3.4V by steps of 100 mV. This threshold is configured in the SMTH field of the Supply Controller Supply Monitor Mode register (SUPC\_SMMR).

The supply monitor can also be enabled during one slow clock period on every one of either 32, 256 or 2048 slow clock periods, depending on the user selection. This is configured in the SMSMPL field in SUPC\_SMMR.

Enabling the supply monitor for such reduced times divides the typical supply monitor power consumption by factors of 2, 16 or 128, respectively, if continuous monitoring of the VDDIO power supply is not required.

A supply monitor detection can either generate a system reset (vddcore\_nreset signal is asserted) or a system wakeup. Generating a system reset when a supply monitor detection occurs is enabled by setting the SMRSTEN bit in SUPC\_SMMR.

Waking up the system when a supply monitor detection occurs is enabled by setting the SMEN bit in the Supply Controller Wakeup Mode register (SUPC\_WUMR).

The SUPC provides two status bits for the supply monitor in the SUPC\_SR. These bits determine whether the last wakeup was due to the supply monitor:

- The SMOS bit provides real-time information, updated at each measurement cycle or updated at each Slow Clock cycle, if the measurement is continuous.

- The SMS bit provides saved information and shows a supply monitor detection has occurred since the last read of SUPC\_SR.

The SMS bit generates an interrupt if the SMIEN bit is set in SUPC\_SMMR.

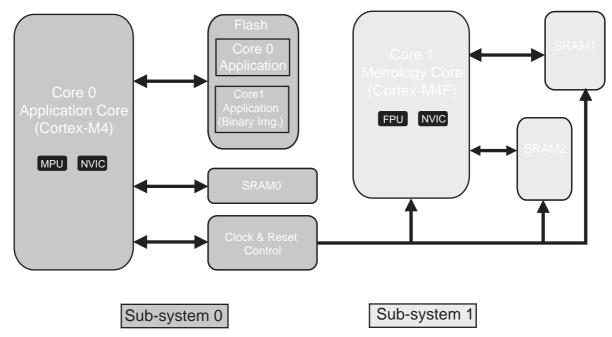

#### Figure 20-3. Raising the VDDBU\_SW Power Supply

Note: After processor reset rising, the core starts fetching instructions from Flash at 4 MHz.

#### 20.4.7.2 SHDN Output Pin

The SHDN pin is designed to drive the enable pin of an external voltage regulator. This pin is controlled by the VROFF bit in SUPC\_CR. When the device goes into Backup mode (bit VROFF set), the SHDN pin is asserted low. Upon a wakeup event, the SHDN pin is released (VDDBU level).

## 20.4.8 System Reset

The SUPC manages the system reset signal (vddcore\_nreset) to the Reset Controller, as described in Section 20.4.7 "Backup Power Supply Reset". The system reset signal is normally asserted before shutting down the core power supply and released as soon as the core power supply is correctly regulated.

There are two additional sources which can be programmed to activate the system reset signal:

- a supply monitor detection

- a brownout detection

#### 20.4.8.1 Supply Monitor Reset

The supply monitor can generate a reset of the system. This can be enabled by setting the SMRSTEN bit in SUPC\_SMMR.

The output of the supply monitor is synchronized on SLCK. If SMRSTEN is set and if a supply monitor detection occurs, the system reset is asserted one or two slow clock cycles after the detection.

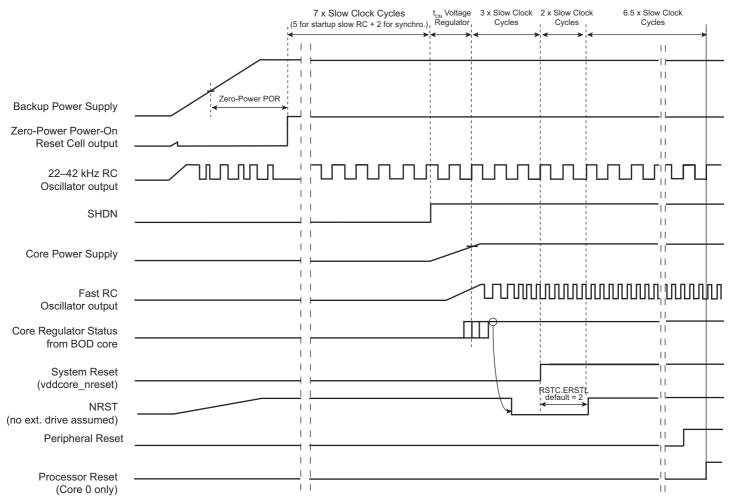

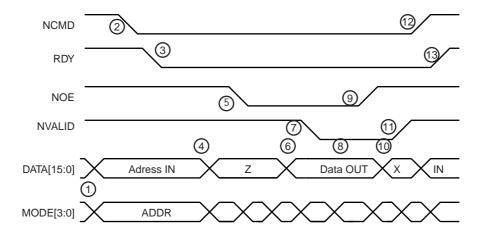

## Figure 23-2. Parallel Programming Timing, Write Sequence

## Table 23-4. Write Handshake

| Step | Programmer Action              | Device Action                        | Data I/O |

|------|--------------------------------|--------------------------------------|----------|

| 1    | Sets MODE and DATA signals     | Waits for NCMD low                   | Input    |

| 2    | Clears NCMD signal             | Latches MODE and DATA                | Input    |

| 3    | Waits for RDY low              | Clears RDY signal                    | Input    |

| 4    | Releases MODE and DATA signals | Executes command and polls NCMD high | Input    |

| 5    | Sets NCMD signal               | Executes command and polls NCMD high | Input    |

| 6    | Waits for RDY high             | Sets RDY                             | Input    |

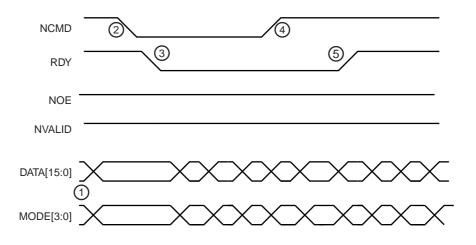

#### 23.3.4.2 Read Handshaking

For details on the read handshaking sequence, refer to Figure 23-3 and Table 23-5.

#### Figure 23-3. Parallel Programming Timing, Read Sequence

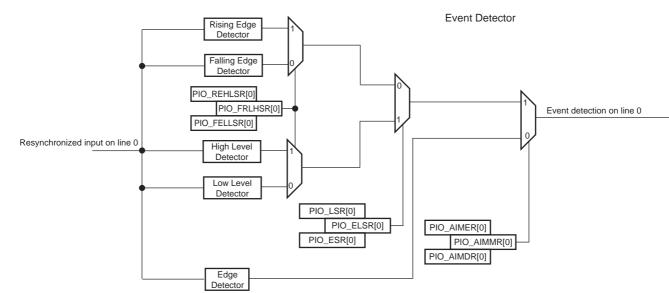

These additional modes are:

- Rising edge detection

- Falling edge detection

- Low-level detection

- High-level detection

In order to select an additional interrupt mode:

- The type of event detection (edge or level) must be selected by writing in the Edge Select Register (PIO\_ESR) and Level Select Register (PIO\_LSR) which select, respectively, the edge and level detection. The current status of this selection is accessible through the Edge/Level Status Register (PIO\_ELSR).

- The polarity of the event detection (rising/falling edge or high/low-level) must be selected by writing in the Falling Edge/Low-Level Select Register (PIO\_FELLSR) and Rising Edge/High-Level Select Register (PIO\_REHLSR) which allow to select falling or rising edge (if edge is selected in PIO\_ELSR) edge or highor low-level detection (if level is selected in PIO\_ELSR). The current status of this selection is accessible through the Fall/Rise - Low/High Status Register (PIO\_FRLHSR).

When an input edge or level is detected on an I/O line, the corresponding bit in the Interrupt Status Register (PIO\_ISR) is set. If the corresponding bit in PIO\_IMR is set, the PIO Controller interrupt line is asserted. The interrupt signals of the 32 channels are ORed-wired together to generate a single interrupt signal to the interrupt controller.

When the software reads PIO\_ISR, all the interrupts are automatically cleared. This signifies that all the interrupts that are pending when PIO\_ISR is read must be handled. When an Interrupt is enabled on a "level", the interrupt is generated as long as the interrupt source is not cleared, even if some read accesses in PIO\_ISR are performed.

## Figure 32-6. Event Detector on Input Lines (Figure Represents Line 0)

Example of interrupt generation on following lines:

- Rising edge on PIO line 0

- Falling edge on PIO line 1

- Rising edge on PIO line 2

- Low-level on PIO line 3

- High-level on PIO line 4

- High-level on PIO line 5

## Atmel

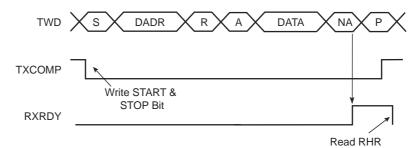

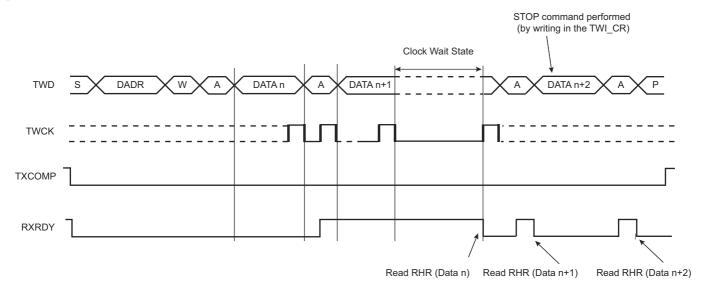

#### Figure 34-8. Master Read with One Data Byte

#### Figure 34-9. Master Read with Multiple Data Bytes

#### Figure 34-10. Master Read Wait State with Multiple Data Bytes

## 34.7.3.6 Internal Address

The TWI can perform transfers with 7-bit slave address devices and 10-bit slave address devices.

#### 7-bit Slave Addressing

When addressing 7-bit slave devices, the internal address bytes are used to perform random address (read or write) accesses to reach one or more data bytes, e.g. within a memory page location in a serial memory. When performing read operations with an internal address, the TWI performs a write operation to set the internal address into the slave device, and then switch to Master receiver mode. Note that the second START condition (after

## Atmel

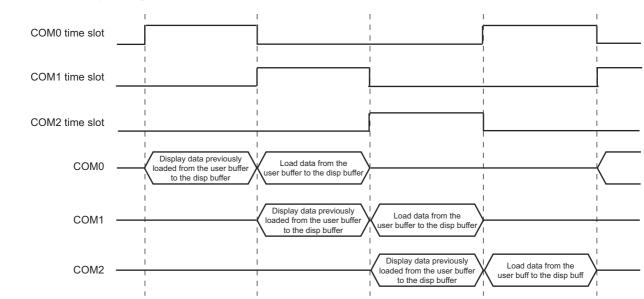

#### 39.6.4 SLCDC memory

Figure 39-9. Memory Management

When a bit in the display memory (SLCDC\_LMEMRx and SLCDC\_MMEMRx registers) is written to one, the corresponding segment is energized (on), and non-energized when a bit in the display memory is written to zero.

At the beginning of each common, the display buffer is updated. The value of the previous common is latched in the display memory (its value is transferred from the user buffer to the frame buffer).

The advantages of this solution are:

- Ability to access the user buffer at any time in the frame, in any display mode and even in low power waveform

- Ability to change only one pixel without reloading the picture

#### 39.6.5 Display Features

In order to improve the flexibility of SLCDC the following set of display modes are embedded:

- Force mode off: all pixels are turned off and the memory content is kept.

- Force mode on: all pixels are turned on and the memory content is kept.

- Inverted Mode: all pixels are set in the inverted state as defined in SLCDC memory and the memory content is kept.

- Two blinking modes:

- Standard Blinking mode: all pixels are alternately turned off to the predefined state in SLCDC memory at LCDBLKFREQ frequency.

- Inverted Blinking mode: all pixels are alternately turned off to the predefined opposite state in SLCDC memory at LCDBLKFREQ frequency.

- Buffer Swap mode: all pixels are alternatively assigned to the state defined in the user buffer then to the state defined in the display buffer.

## 39.8.8 SLCDC Interrupt Mask Register

| Name:    | SLCDC_IMR  |    |    |    |     |    |          |

|----------|------------|----|----|----|-----|----|----------|

| Address: | 0x4003C028 |    |    |    |     |    |          |

| Access:  | Read-only  |    |    |    |     |    |          |

| 31       | 30         | 29 | 28 | 27 | 26  | 25 | 24       |

| _        | -          | -  | _  | _  | _   | —  | -        |

| 23       | 22         | 21 | 20 | 19 | 18  | 17 | 16       |

| -        | -          | -  | _  | _  | -   | —  | -        |

| 15       | 14         | 13 | 12 | 11 | 10  | 9  | 8        |

| -        | -          | -  | _  | _  | -   | _  | -        |

| 7        | 6          | 5  | 4  | 3  | 2   | 1  | 0        |

| _        | -          | _  | _  | _  | DIS | _  | ENDFRAME |

## • ENDFRAME: End of Frame Interrupt Mask

- 0: The corresponding interrupt is not enabled.

- 1: The corresponding interrupt is enabled.

## • DIS: SLCDC Disable Completion Interrupt Mask

- 0: The corresponding interrupt is not enabled.

- 1: The corresponding interrupt is enabled.

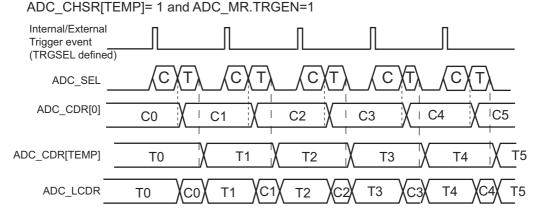

#### Figure 40-6. Non-optimized Temperature Conversion

Notes: ADC\_SEL: Command to the ADC cell C: Classic ADC Conversion Sequence

н

T: Temperature Sensor Channel

Assuming ADC\_CHSR[0] = 1 and ADC\_CHSR[TEMP] = 1 where TEMP is the index of the temperature sensor channel

| trig.event1 ->               |   |               | DMA Transfer      |

|------------------------------|---|---------------|-------------------|

| DMA Buffer                   | 0 | ADC_CDR[0]    | Base Address (BA) |

| Structure                    | 0 | ADC_CDR[TEMP] | BA + 0x02         |

| trig.event2→<br>trig.event3→ | 0 | ADC_CDR[0]    | BA + 0x04         |

|                              | 0 | ADC_CDR[TEMP] | BA + 0x06         |

|                              | 0 | ADC_CDR[0]    | BA + 0x08         |

|                              | 0 | ADC_CDR[TEMP] | BA + 0x0A         |

|                              |   |               |                   |

The temperature factor has a slow variation rate and is potentially different from other conversion channels. As a result, the ADC Controller triggers the measurement differently when TEMPON is set in ADC\_TEMPMR but CH7 is not set in the ADC\_CHSR.

ı

Under these conditions, the measurement is triggered every second by means of an internal trigger generated by the RTC, always enabled and totally independent of the internal/external triggers. The RTC event will be processed on the next internal/external trigger event as described in Figure 40-7, "Optimized Temperature Conversion Combined With Classical Conversions". The internal/external trigger is selected through the TRGSEL field of ADC\_MR.

In this mode of operation, the temperature sensor is only powered for a period of time covering the startup time and conversion time (refer to Figure 40-8, "Temperature Conversion Only").

Every second, a conversion is scheduled for channel 7 but the result of the conversion is only uploaded in ADC\_CDR7 and not in ADC\_LCDR. Therefore there is no change in the structure of the Peripheral DMA Controller buffer due to the conversion of the temperature channel; only the enabled channels are kept in the buffer. The end of conversion of the temperature channel is reported by means of EOC7 flag in ADC\_ISR.

## 43.6.6 ICM Interrupt Mask Register

| Name:<br>Address: | ICM_IMR<br>0x40044018 |    |    |     |    |    |      |

|-------------------|-----------------------|----|----|-----|----|----|------|

| Access:           | Read-only             |    |    |     |    |    |      |

| 31                | 30                    | 29 | 28 | 27  | 26 | 25 | 24   |

| _                 | -                     | _  | -  | _   | _  | -  | URAD |

| 23                | 22                    | 21 | 20 | 19  | 18 | 17 | 16   |

|                   | RS                    | U  |    | REC |    |    |      |

| 15                | 14                    | 13 | 12 | 11  | 10 | 9  | 8    |

|                   | RW                    | 'C |    | RBE |    |    |      |

| 7                 | 6                     | 5  | 4  | 3   | 2  | 1  | 0    |

|                   | RD                    | Μ  |    | RHC |    |    |      |

## RHC: Region Hash Completed Interrupt Mask

0: When RHC[/] is set to zero, the interrupt is disabled for region i.

1: When RHC[*i*] is set to one, the interrupt is enabled for region i.

## RDM: Region Digest Mismatch Interrupt Mask

0: When RDM[*i*] is set to zero, the interrupt is disabled for region i.1: When RDM[*i*] is set to one, the interrupt is enabled for region i.

## • RBE: Region Bus Error Interrupt Mask

0: When RBE[*i*] is set to zero, the interrupt is disabled for region i.1: When RBE[*i*] is set to one, the interrupt is enabled for region i.

## • RWC: Region Wrap Condition Detected Interrupt Mask

0: When RWC[*i*] is set to zero, the interrupt is disabled for region i.1: When RWC[*i*] is set to one, the interrupt is enabled for region i.

## • REC: Region End bit Condition Detected Interrupt Mask

0: When REC[*i*] is set to zero, the interrupt is disabled for region i.

1: When REC[*i*] is set to one, the interrupt is enabled for region i.

## • RSU: Region Status Updated Interrupt Mask

0: When RSU[*i*] is set to zero, the interrupt is disabled for region i.

1: When RSU[*i*] is set to one, the interrupt is enabled for region i.

## URAD: Undefined Register Access Detection Interrupt Mask

- 0: Interrupt is disabled

- 1: Interrupt is enabled.

## 43.6.7 ICM Interrupt Status Register

| Name:    | ICM_ISR    |    |    |     |    |    |      |

|----------|------------|----|----|-----|----|----|------|

| Address: | 0x4004401C |    |    |     |    |    |      |

| Access:  | Read-only  |    |    |     |    |    |      |

| 31       | 30         | 29 | 28 | 27  | 26 | 25 | 24   |

| _        | _          | _  | -  | _   | _  | -  | URAD |

| 23       | 22         | 21 | 20 | 19  | 18 | 17 | 16   |

|          | RS         | SU |    | REC |    |    |      |

| 15       | 14         | 13 | 12 | 11  | 10 | 9  | 8    |

|          | RV         | VC |    | RBE |    |    |      |

| 7        | 6          | 5  | 4  | 3   | 2  | 1  | 0    |

|          | RE         | DM |    |     | R  | HC |      |

## • RHC: Region Hash Completed

When RHC[*i*] is set, it indicates that the ICM has completed the region with identifier *i*.

## • RDM: Region Digest Mismatch

When RDM[*i*] is set, it indicates that there is a digest comparison mismatch between the hash value of the region with identifier *i* and the reference value located in the Hash Area.

## • RBE: Region Bus Error

When RBE[i] is set, it indicates that a bus error has been detected while hashing memory region i.

## • RWC: Region Wrap Condition Detected

When RWC[*i*] is set, it indicates that a wrap condition has been detected.

## • REC: Region End bit Condition Detected

When REC[*i*] is set, it indicates that an end bit condition has been detected.

## • RSU: Region Status Updated Detected

When RSU[*i*] is set, it indicates that a region status updated condition has been detected.

## • URAD: Undefined Register Access Detection Status

0: No undefined register access has been detected since the last SWRST.

1: At least one undefined register access has been detected since the last SWRST.

The URAD bit is only reset by the SWRST bit in the ICM\_CTRL register.

The URAT field in the ICM\_UASR indicates the unspecified access type.

Master Read Mode

$$f_{SPCK}Max = \frac{1}{SPI_0(orSPI_3) + t_{valid}}$$

$t_{valid}$  is the slave time response to output data after detecting an SPCK edge.

For a non-volatile memory with  $t_{valid}$  (or  $t_v$ ) = 5 ns,  $f_{SPCK}max$  = 40 MHz at  $V_{DDIO}$  = 3.3 V.

#### Slave Read Mode

In Slave mode, SPCK is the input clock for the SPI. The max SPCK frequency is given by setup and hold timings  $SPI_7/SPI_8$  (or  $SPI_{10}/SPI_{11}$ ). Since this gives a frequency well above the pad limit, the limit in Slave Read mode is given by the SPCK pad.

Slave Write Mode

$$f_{SPCK}Max = \frac{1}{2x(SPI_{6max}(orSPI_{9max}) + t_{setup})}$$

$\ensuremath{t_{\text{setup}}}$  is the setup time from the master before sampling data.

Notes: 1. Current consumption per measurement channel.

- V<sub>IND</sub> may be limited by the recommended input voltage on analog input pins (+/-0.25V, refer to Table 46-5 "Recommended Operating Conditions on Input Pins").

- 3. Corresponds to the maximum signal on the voltage channel(s).

- 4. Includes the input impedance drift with temperature.

| Symbol                | Parameter                                                        | Comments                                       | Min   | Тур   | Max   | Unit    |  |

|-----------------------|------------------------------------------------------------------|------------------------------------------------|-------|-------|-------|---------|--|

| V <sub>VDDA</sub>     | Operating supply voltage                                         | _                                              | 2.7   | 2.8   | 2.9   | V       |  |

| I <sub>VDDA</sub>     | Cumply summert                                                   | OFF                                            | _     | _     | 0.1   | μA      |  |

|                       | Supply current                                                   | ON                                             | _     | 70    | 100   |         |  |

| $V_{REF}_{AFE0}$      | Output voltage initial accuracy                                  | At $T_{J0} = 23^{\circ}C$                      | 1.142 | 1.144 | 1.146 | V       |  |

| $TC_{VREF_U}$         |                                                                  | Uncompensated (SAM4CMS4 devices)               | _     | 50    | _     |         |  |

| $TC_{VREF_C}$         | V <sub>REF</sub> drift with temperature <sup>(1)</sup>           | Using factory-programmed calibration registers | _     | 10    | 30    | ppm /°C |  |

| R <sub>OUT</sub>      | V <sub>REF_AFE</sub> output resistance                           | _                                              | 200   | 500   | 800   | kΩ      |  |

| D <sub>TEMP_Lin</sub> | Die temperature sensor,<br>digital reading linearity             | _                                              | _     | ±2    | _     | °C      |  |

| I <sub>VREF_OFF</sub> | Current in VREF pin when<br>internal voltage reference is<br>OFF | _                                              | -100  | _     | 100   | nA      |  |

Table 46-48. EMAFE Precision Voltage Reference and Die Temperature Sensor Characteristics

Note: 1. TC is defined using the box method: TC = ( $V_{REF\_AFE\_MAX} - V_{REF\_AFE\_MIN}$ ) / ( $V_{REF\_AFE0}$  x ( $T_{MAX} - T_{MIN}$ )).

## Table 46-49. EMAFE VDDA LDO Regulator

| Symbol                                       | Parameter                     | Comments                                                      | Min  | Тур  | Max  | Unit  |  |

|----------------------------------------------|-------------------------------|---------------------------------------------------------------|------|------|------|-------|--|

| V <sub>VDDIN</sub>                           | Operating supply voltage      | -                                                             | 3.0  | 3.3  | 3.6  | V     |  |

|                                              | Cumply current                | OFF                                                           | _    | _    | 0.1  |       |  |

|                                              | Supply current                | ON                                                            | _    | _    | 250  | μA    |  |

| I <sub>O</sub>                               | Output current                | -                                                             | -    | -    | 15   | mA    |  |

| Vo                                           | DC output voltage             | I <sub>O</sub> = 0 mA.                                        | 2.75 | 2.8V | 2.85 | V     |  |

| $\Delta V_{O} / \Delta I_{O}$                | Static load regulation        | I <sub>O</sub> : 0 to I <sub>OMAX</sub>                       | -5   | _    | _    | mV/mA |  |

| $\Delta V_{O}^{\prime}$<br>$\Delta V_{DDIN}$ | Static line regulation        | V <sub>DDIN</sub> : 3.0 to 3.6V                               | -5   | _    | 5    | mV/V  |  |

| PSRR Power                                   |                               | f = DC to 2000 Hz                                             | _    | 40   | _    |       |  |

|                                              | Power supply rejection ratio  | f = 1 MHz                                                     | _    | 40   | _    | - dB  |  |

| t <sub>ON</sub>                              | Start-up time                 | $V_0$ from 0 to 95% of final value.<br>I <sub>0</sub> = 0 mA. | _    | -    | 1    | ms    |  |

| Co                                           |                               | Capacitive                                                    | 0.5  | 1    | 4.7  | μF    |  |

|                                              | Stable output capacitor range | Resistive                                                     | 5    | 10   | 300  | mΩ    |  |

## 49. Ordering Information

| Ordering Code     | MRL | Flash<br>(Kbytes) | Package   | Conditioning | Temperature<br>Operating Range |

|-------------------|-----|-------------------|-----------|--------------|--------------------------------|

| ATSAM4CMP32CB-AU  | P   | - 2 x 1024        |           | Tray         |                                |

| ATSAM4CMP32CB-AUR | B   |                   |           | Reel         |                                |

| ATSAM4CMP32CA-AU  | •   |                   |           | Tray         |                                |

| ATSAM4CMP32CA-AUR | — A |                   |           | Reel         |                                |

| ATSAM4CMP16CC-AU  | C   |                   |           | Tray         |                                |

| ATSAM4CMP16CC-AUR |     |                   |           | Reel         |                                |

| ATSAM4CMP16CB-AU  | P   | 4004              |           | Tray         |                                |

| ATSAM4CMP16CB-AUR | — В | 1024              |           | Reel         |                                |

| ATSAM4CMP16CA-AU  | •   |                   |           | Tray         |                                |

| ATSAM4CMP16CA-AUR | — A |                   |           | Reel         |                                |

| ATSAM4CMP8CC-AU   | 0   |                   |           | Tray         |                                |

| ATSAM4CMP8CC-AUR  | C   | 512               |           | Reel         |                                |

| ATSAM4CMP8CB-AU   | P   |                   |           | Tray         |                                |

| ATSAM4CMP8CB-AUR  | В   |                   |           | Reel         |                                |

| ATSAM4CMP8CA-AU   |     |                   |           | Tray         |                                |

| ATSAM4CMP8CA-AUR  | — A |                   | – LQFP100 | Reel         | Industrial                     |

| ATSAM4CMS32CB-AU  | 5   |                   |           | Tray         | (-40°C to +85°C)               |

| ATSAM4CMS32CB-AUR | В   |                   |           | Reel         |                                |

| ATSAM4CMS32CA-AU  |     | 2 x 1024          |           | Tray         |                                |

| ATSAM4CMS32CA-AUR | Α   |                   |           | Reel         |                                |

| ATSAM4CMS16CC-AU  |     |                   |           | Tray         |                                |

| ATSAM4CMS16CC-AUR | C   | 1024              |           | Reel         |                                |

| ATSAM4CMS16CB-AU  |     |                   |           | Tray         |                                |

| ATSAM4CMS16CB-AUR | — В |                   |           | Reel         | -                              |

| ATSAM4CMS16CA-AU  |     |                   |           | Tray         |                                |

| ATSAM4CMS16CA-AUR | Α   |                   | -         | Reel         |                                |

| ATSAM4CMS8CC-AU   |     |                   | Tray      | -            |                                |

| ATSAM4CMS8CC-AUR  | - C |                   |           | Reel         |                                |

| ATSAM4CMS8CB-AU   |     |                   |           | Tray         |                                |

| ATSAM4CMS8CB-AUR  | — В |                   |           | Reel         | 1                              |

| ATSAM4CMS8CA-AU   |     | 1                 |           | Tray         |                                |

| ATSAM4CMS8CA-AUR  | A   |                   |           | Reel         |                                |

Table 49-1.

Ordering Codes for SAM4CM Devices