Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 38                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 10x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af5268tcy |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |       | 5.7.4    | Advanced control and general purpose timers                            | 0 |

|----|-------|----------|------------------------------------------------------------------------|---|

|    |       | 5.7.5    | Basic timer                                                            | 1 |

|    | 5.8   | Analog   | to digital converter (ADC) 22                                          | 2 |

|    | 5.9   | Commu    | inication interfaces 22                                                | 2 |

|    |       | 5.9.1    | Universal synchronous/asynchronous receiver transmitter (USART) 22     | 2 |

|    |       | 5.9.2    | Universal asynchronous receiver/transmitter with LIN support (LINUART) | 4 |

|    |       | 5.9.3    | Serial peripheral interface (SPI) 25                                   | 5 |

|    |       | 5.9.4    | Inter integrated circuit (I <sup>2</sup> C) interface                  | 5 |

|    |       | 5.9.5    | Controller area network interface (beCAN)                              | 6 |

|    | 5.10  | Input/o  | utput specifications                                                   | 7 |

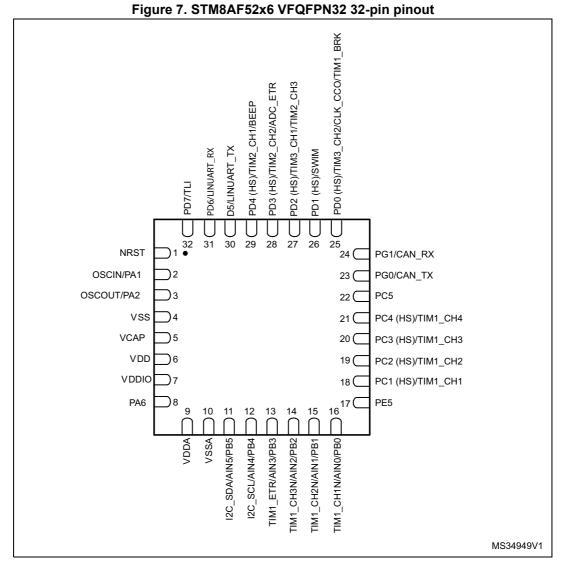

| 6  | Pino  | uts and  | pin description 28                                                     | 8 |

|    | 6.1   | Packag   | e pinouts                                                              | 8 |

|    | 6.2   | Alterna  | te function remapping                                                  | Э |

| 7  | Mem   | ory and  | register map 40                                                        | D |

|    | 7.1   | Memor    | y map                                                                  | D |

|    | 7.2   | Registe  | r map                                                                  | 1 |

| 8  | Inter | rupt tab | le                                                                     | 3 |

| 9  | Optic | on bytes | 5                                                                      | 4 |

| 10 | Elect | rical ch | aracteristics                                                          | 9 |

|    | 10.1  | Parame   | eter conditions                                                        | 9 |

|    |       | 10.1.1   | Minimum and maximum values                                             | 9 |

|    |       | 10.1.2   | Typical values                                                         | 9 |

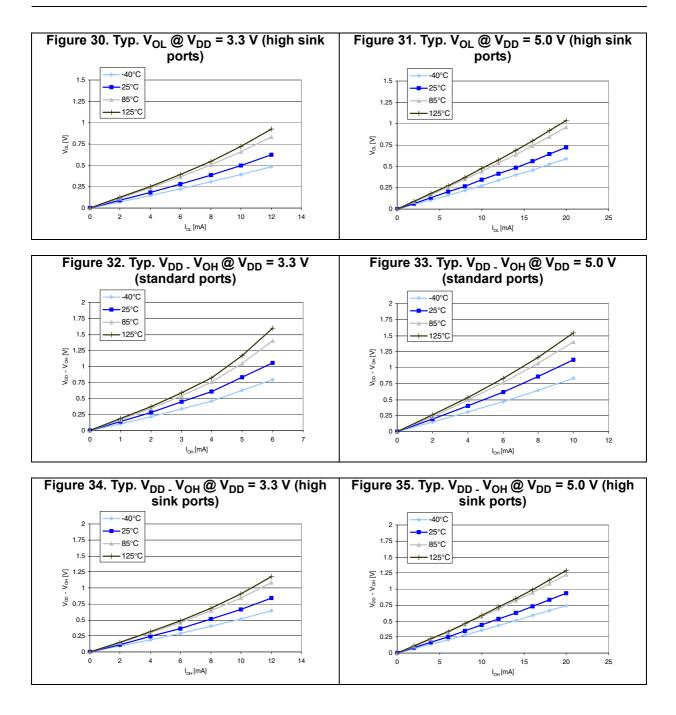

|    |       | 10.1.3   | Typical curves                                                         | Э |

|    |       | 10.1.4   | Loading capacitor                                                      | Э |

|    |       | 10.1.5   | Pin input voltage60                                                    | С |

|    | 10.2  | Absolut  | e maximum ratings 60                                                   | C |

|    | 10.3  | Operati  | ng conditions                                                          | 2 |

|    |       | 10.3.1   | VCAP external capacitor                                                | 3 |

|    |       | 10.3.2   | Supply current characteristics63                                       | 3 |

|    |       | 10.3.3   | External clock sources and timing characteristics                      | 8 |

|    |       | 10.3.4   | Internal clock sources and timing characteristics                      | D |

| Table 47.<br>Table 48.<br>Table 49. | ESD absolute maximum ratings                                                |

|-------------------------------------|-----------------------------------------------------------------------------|

|                                     | mechanical data                                                             |

| Table 50.                           | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                           |

|                                     | package mechanical data                                                     |

| Table 51.                           | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                     |

|                                     | mechanical data                                                             |

| Table 52.                           | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                     |

|                                     | mechanical data                                                             |

| Table 53.                           | VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad |

|                                     | flat package mechanical data                                                |

| Table 54.                           | Thermal characteristics                                                     |

| Table 55.                           | Document revision history                                                   |

# 2 Description

The STM8AF526x/8x/Ax and STM8AF6269/8x/Ax automotive 8-bit microcontrollers described in this datasheet offer from 32 Kbyte to 128 Kbyte of non volatile memory and integrated true data EEPROM. They are referred to as high density STM8A devices in STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

The STM8AF52 series features a CAN interface.

All devices of the STM8A product line provide the following benefits: reduced system cost, performance and robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, wtachdog, and brown-out reset.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map, and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8A family thanks to their advanced core which is made in a state-of-the art technology for automotive applications with 3.3 V to 5.5 V operating supply.

All STM8A and ST7 microcontrollers are supported by the same tools including STVD/STVP development environment, the STice emulator and a low-cost, third party incircuit debugging tool.

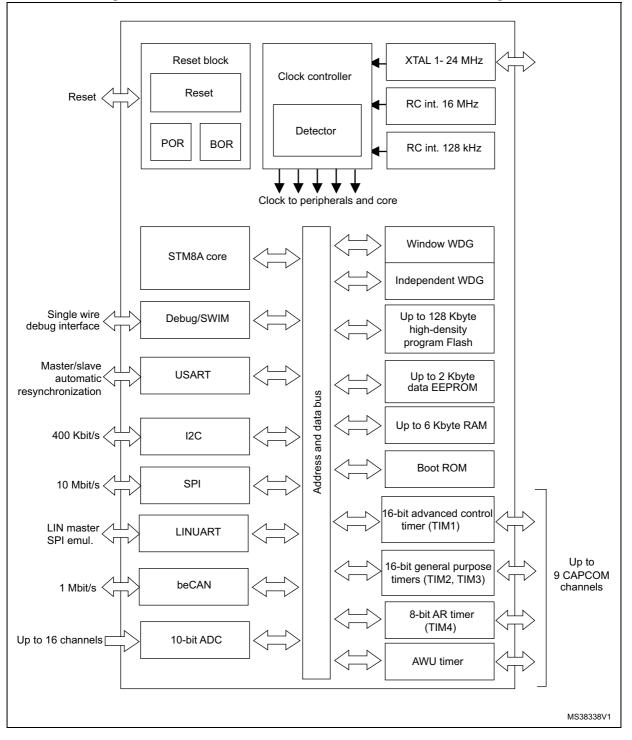

# 4 Block diagram

Figure 1. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax block diagram

DocID14395 Rev 15

## 5.2 Single wire interface module (SWIM) and debug module (DM)

#### 5.2.1 SWIM

The single wire interface module, SWIM, together with an integrated debug module, permits non-intrusive, real-time in-circuit debugging and fast memory programming. The interface can be activated in all device operation modes and can be connected to a running device (hot plugging). The maximum data transmission speed is 145 bytes/ms.

#### 5.2.2 Debug module

The non-intrusive debugging module features a performance close to a full-flavored emulator. Besides memory and peripheral operation, CPU operation can also be monitored in real-time by means of shadow registers.

- R/W of RAM and peripheral registers in real-time

- R/W for all resources when the application is stopped

- Breakpoints on all program-memory instructions (software breakpoints), except the interrupt vector table

- Two advanced breakpoints and 23 predefined breakpoint configurations

## 5.3 Interrupt controller

- Nested interrupts with three software priority levels

- 24 interrupt vectors with hardware priority

- Five vectors for external interrupts (up to 37 depending on the package)

- Trap and reset interrupts

## 5.4 Flash program and data EEPROM

- 32 Kbytes to 128 Kbytes of high density single voltage Flash program memory

- Up to 2 Kbytes true (not emulated) data EEPROM

- Read while write: writing in the data memory is possible while executing code in the Flash program memory.

The whole Flash program memory and data EEPROM are factory programmed with 0x00.

#### 5.4.1 Architecture

- The memory is organized in blocks of 128 bytes each

- Read granularity: 1 word = 4 bytes

- Write/erase granularity: 1 word (4 bytes) or 1 block (128 bytes) in parallel

- Writing, erasing, word and block management is handled automatically by the memory interface.

The ROP circuit may provide a temporary access for debugging or failure analysis. The temporary read access is protected by a user defined, 8-byte keyword stored in the option byte area. This keyword must be entered via the SWIM interface to temporarily unlock the device.

If desired, the temporary unlock mechanism can be permanently disabled by the user through OPT6/NOPT6 option bytes.

### 5.5 Clock controller

The clock controller distributes the system clock coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness.

#### 5.5.1 Features

- Clock sources

- 16 MHz high-speed internal RC oscillator (HSI)

- 128 kHz low-speed internal RC (LSI)

- 1-24 MHz high-speed external crystal (HSE)

- Up to 24 MHz high-speed user-external clock (HSE user-ext)

- **Reset**: After reset the microcontroller restarts by default with an internal 2-MHz clock (16 MHz/8). The clock source and speed can be changed by the application program as soon as the code execution starts.

- **Safe clock switching**: Clock sources can be changed safely on the fly in Run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

- **Clock management**: To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Wakeup**: In case the device wakes up from low-power modes, the internal RC oscillator (16 MHz/8) is used for quick startup. After a stabilization time, the device switches to the clock source that was selected before Halt mode was entered.

- **Clock security system (CSS)**: The CSS permits monitoring of external clock sources and automatic switching to the internal RC (16 MHz/8) in case of a clock failure.

- **Configurable main clock output (CCO)**: This feature permits to output a clock signal for use by the application.

#### 5.5.2 16 MHz high-speed internal RC oscillator (HSI)

- Default clock after reset 2 MHz (16 MHz/8)

- Fast wakeup time

#### **User trimming**

The register CLK\_HSITRIMR with two trimming bits plus one additional bit for the sign permits frequency tuning by the application program. The adjustment range covers all possible frequency variations versus supply voltage and temperature. This trimming does not change the initial production setting.

DocID14395 Rev 15

| Control bit | Peripheral |  |  |  |

|-------------|------------|--|--|--|

| PCKEN27     | CAN        |  |  |  |

| PCKEN26     | Reserved   |  |  |  |

| PCKEN25     | Reserved   |  |  |  |

| PCKEN24     | Reserved   |  |  |  |

| PCKEN23     | ADC        |  |  |  |

| PCKEN22     | AWU        |  |  |  |

| PCKEN21     | Reserved   |  |  |  |

| PCKEN20     | Reserved   |  |  |  |

|             |            |  |  |  |

#### Table 5. Peripheral clock gating bits (CLK PCKENR2)

## 5.6 Low-power operating modes

For efficient power management, the application can be put in one of four different lowpower modes. Users can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- Wait mode

In this mode, the CPU is stopped but peripherals are kept running. The wakeup is

performed by an internal or external interrupt or reset.

- Active-halt mode with regulator on

In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in Active-halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

• Active-halt mode with regulator off

This mode is the same as Active-halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

Halt mode

CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

In all modes the CPU and peripherals remain permanently powered on, the system clock is applied only to selected modules. The RAM content is preserved and the brown-out reset circuit remains activated.

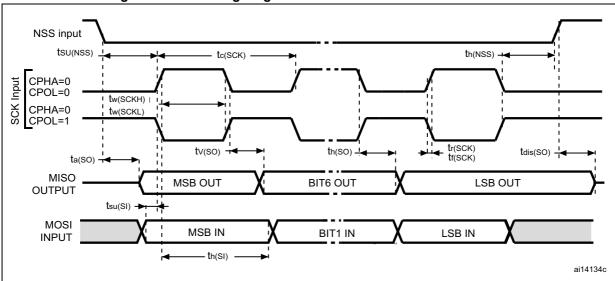

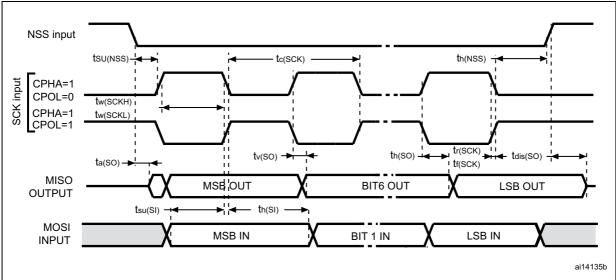

#### 5.9.3 Serial peripheral interface (SPI)

The devices covered by this datasheet contain one SPI. The SPI is available on all the supported packages.

- Maximum speed: 10 Mbit/s or f<sub>MASTER</sub>/2 for master, 8 Mbit/s or f<sub>MASTER</sub> /2 for slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave mode/master mode management by hardware or software for both master and slave

- Programmable clock polarity and phase

- Programmable data order with MSB-first or LSB-first shifting

- Dedicated transmission and reception flags with interrupt capability

- SPI bus busy status flag

- Hardware CRC feature for reliable communication:

- CRC value can be transmitted as last byte in Tx mode

- CRC error checking for last received byte

#### 5.9.4 Inter integrated circuit (I<sup>2</sup>C) interface

The devices covered by this datasheet contain one  $I^2C$  interface. The interface is available on all the supported packages.

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

- Status flags:

- Transmitter/receiver mode flag

- End-of-byte transmission flag

- I<sup>2</sup>C busy flag

- Error flags:

- Arbitration lost condition for master mode

- Acknowledgement failure after address/data transmission

- Detection of misplaced start or stop condition

- Overrun/underrun if clock stretching is disabled

## 5.10 Input/output specifications

The product features four I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

- Caution: In STM8AF5286UC device, the following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor,

- configured as output push-pull low.

The following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor, - configured as output push-pull low. 1.

2. HS stands for high sink capability.

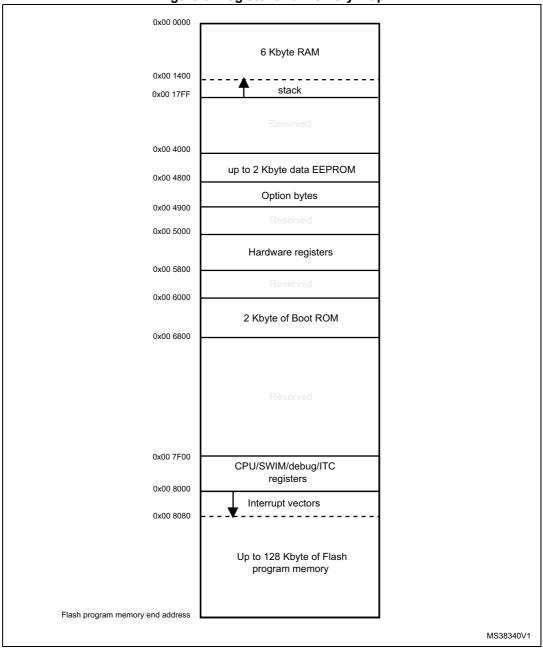

# 7 Memory and register map

## 7.1 Memory map

Figure 8. Register and memory map

| Address                   | Block | ck Register label Register name |                                 |      |

|---------------------------|-------|---------------------------------|---------------------------------|------|

| 0x00 5200                 |       | SPI_CR1                         | SPI control register 1          | 0x00 |

| 0x00 5201                 |       | SPI_CR2                         | SPI control register 2          | 0x00 |

| 0x00 5202                 |       | SPI_ICR                         | SPI interrupt control register  | 0x00 |

| 0x00 5203                 | SPI   | SPI_SR                          | SPI status register             | 0x02 |

| 0x00 5204                 | 381   | SPI_DR                          | SPI data register               | 0x00 |

| 0x00 5205                 |       | SPI_CRCPR                       | SPI CRC polynomial register     | 0x07 |

| 0x00 5206                 |       | SPI_RXCRCR                      | SPI Rx CRC register             | 0xFF |

| 0x00 5207                 |       | SPI_TXCRCR                      | SPI Tx CRC register             | 0xFF |

| 0x00 5208 to<br>0x00 520F |       | R                               | eserved area (8 bytes)          |      |

| 0x00 5210                 |       | I2C_CR1                         | I2C control register 1          | 0x00 |

| 0x00 5211                 |       | I2C_CR2                         | I2C control register 2          | 0x00 |

| 0x00 5212                 |       | I2C_FREQR                       | I2C frequency register          | 0x00 |

| 0x00 5213                 |       | I2C_OARL                        | I2C own address register low    | 0x00 |

| 0x00 5214                 |       | I2C_OARH                        | I2C own address register high   | 0x00 |

| 0x00 5215                 |       |                                 |                                 |      |

| 0x00 5216                 | I2C   | I2C_DR                          | I2C data register               | 0x00 |

| 0x00 5217                 | 120   | I2C_SR1                         | I2C status register 1           | 0x00 |

| 0x00 5218                 |       | I2C_SR2                         | I2C status register 2           | 0x00 |

| 0x00 5219                 |       | I2C_SR3                         | I2C status register 3           | 0x00 |

| 0x00 521A                 |       | I2C_ITR                         | I2C interrupt control register  | 0x00 |

| 0x00 521B                 |       | I2C_CCRL                        | I2C clock control register low  | 0x00 |

| 0x00 521C                 |       | I2C_CCRH                        | I2C clock control register high | 0x00 |

| 0x00 521D                 |       | I2C_TRISER                      | I2C TRISE register              | 0x02 |

| 0x00 521E to<br>0x00 522F |       | Re                              | eserved area (18 bytes)         |      |

Table 14. General hardware register map (continued)

| Address                      | Block | Register label | Register name                                | Reset<br>status |

|------------------------------|-------|----------------|----------------------------------------------|-----------------|

| 0x00 7F81<br>to<br>0x00 7F8F |       |                | Reserved area (15 bytes)                     |                 |

| 0x00 7F90                    |       | DM_BK1RE       | DM breakpoint 1 register extended byte       | 0xFF            |

| 0x00 7F91                    |       | DM_BK1RH       | DM breakpoint 1 register high byte           | 0xFF            |

| 0x00 7F92                    |       | DM_BK1RL       | DM breakpoint 1 register low byte            | 0xFF            |

| 0x00 7F93                    |       | DM_BK2RE       | DM breakpoint 2 register extended byte       | 0xFF            |

| 0x00 7F94                    |       | DM_BK2RH       | DM breakpoint 2 register high byte           | 0xFF            |

| 0x00 7F95                    | DM    | DM_BK2RL       | DM breakpoint 2 register low byte            | 0xFF            |

| 0x00 7F96                    |       | DM_CR1         | DM debug module control register 1           | 0x00            |

| 0x00 7F97                    |       | DM_CR2         | DM debug module control register 2 0x0       |                 |

| 0x00 7F98                    |       | DM_CSR1        | DM debug module control/status register 1 0x |                 |

| 0x00 7F99                    |       | DM_CSR2        | DM debug module control/status register 2 0  |                 |

| 0x00 7F9A                    |       | DM_ENFCTR      | DM enable function register                  | 0xFF            |

| 0x00 7F9B<br>to 0x00<br>7F9F |       |                | Reserved area (5 bytes)                      |                 |

#### Table 15. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

2. Product dependent value, see Figure 8: Register and memory map.

| Address   | Block | Register label | Register name                                             | Reset<br>status |  |

|-----------|-------|----------------|-----------------------------------------------------------|-----------------|--|

| 0x00 5800 |       | TMU_K1         | Temporary memory unprotection key register 1              | 0x00            |  |

| 0x00 5801 |       | TMU_K2         | Temporary memory unprotection key register 2              | 0x00            |  |

| 0x00 5802 |       | TMU_K3         | TMU_K3 Temporary memory unprotection key register 3       |                 |  |

| 0x00 5803 |       | TMU_K4         | TMU_K4 Temporary memory unprotection key register 4       |                 |  |

| 0x00 5804 | TMU   | TMU_K5         | TMU_K5 Temporary memory unprotection key register 5       |                 |  |

| 0x00 5805 |       | TMU_K6         | Temporary memory unprotection key register 6              | 0x00            |  |

| 0x00 5806 |       | TMU_K7         | Temporary memory unprotection key register 7              | 0x00            |  |

| 0x00 5807 |       | TMU_K8         | Temporary memory unprotection key register 8              | 0x00            |  |

| 0x00 5808 |       | TMU_CSR        | Temporary memory unprotection control and status register | 0x00            |  |

#### Table 16. Temporary memory unprotection registers

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT12           | TMU_KEY 5 [7:0]: Temporary unprotection key 4<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                                  |

| OPT13           | TMU_KEY 6 [7:0]: Temporary unprotection key 5           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |

| OPT14           | TMU_KEY 7 [7:0]: Temporary unprotection key 6           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |

| OPT15           | TMU_KEY 8 [7:0]: Temporary unprotection key 7           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |

| OPT16           | <ul> <li>TMU_MAXATT [7:0]: TMU access failure counter</li> <li>TMU_MAXATT can be initialized with the desired value only if TMU is disabled (TMU[3:0]=0101 in OPT6 option byte).</li> <li>When TMU is enabled, any attempt to temporary remove the readout protection by using wrong key values increments the counter.</li> <li>When the option byte value reaches 0x08, the Flash memory and data EEPROM are erased.</li> </ul> |

| OPT17           | <b>BL[7:0]: Bootloader enable</b><br>If this option byte is set to 0x55 (complementary value 0xAA) the<br>bootloader program is activated also in case of a programmed code<br>memory (for more details, see the bootloader user manual, UM0560).                                                                                                                                                                                 |

#### Table 19. Option byte description (continued)

DocID14395 Rev 15

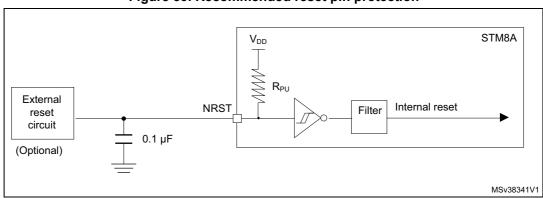

Figure 39. Recommended reset pin protection

## 10.3.8 TIM 1, 2, 3, and 4 electrical specifications

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}}$  and  $T_{\text{A}}.$

Table 40. TIM 1, 2, 3, and 4 electrical specifications

| Symbol           | Parameter                                     | Conditions | Min | Тур | Мах | Unit |

|------------------|-----------------------------------------------|------------|-----|-----|-----|------|

| f <sub>EXT</sub> | Timer external clock frequency <sup>(1)</sup> | -          | -   | -   | 24  | MHz  |

1. Not tested in production.

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

#### Electromagnetic interference (EMI)

Emission tests conform to the IEC 61967-2 standard for test software, board layout and pin loading.

|                             |                                                                | Conditions             |                             |                                     |           |           |      |

|-----------------------------|----------------------------------------------------------------|------------------------|-----------------------------|-------------------------------------|-----------|-----------|------|

| Symbol P                    | Parameter                                                      | Conorol                | Monitorod                   | Max f <sub>CPU</sub> <sup>(1)</sup> |           |           | Unit |

|                             |                                                                | General<br>conditions  | Monitored<br>frequency band | 8<br>MHz                            | 16<br>MHz | 24<br>MHz |      |

|                             |                                                                | V <sub>DD</sub> = 5 V, | 0.1 MHz to 30 MHz           | 15                                  | 17        | 22        |      |

| S <sub>EMI</sub> Peak level | T <sub>A</sub> = 25 °C,<br>LQFP80 package<br>conforming to IEC | 30 MHz to 130 MHz      | 18                          | 22                                  | 16        | dBµV      |      |

|                             |                                                                | 130 MHz to 1 GHz       | -1                          | 3                                   | 5         | чομν      |      |

|                             | EMI level                                                      | 61967-2                | -                           | 2                                   | 2.5       | 2.5       |      |

| Table 46. EMI data |

|--------------------|

|--------------------|

1. Guaranteed by characterization results, not tested in production.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                            | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = 25$ °C, conforming<br>to JESD22-A114           | 3A    | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = 25 °C, conforming<br>to JESD22-C101  | 3     | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (charge device model) | $T_A = 25 \ ^{\circ}C$ , conforming<br>to JESD22-A115 | В     | 200                             |      |

Table 47. ESD absolute maximum ratings

1. Guaranteed by characterization results, not tested in production

|        |        | millimeters |        |        | inches |        |  |

|--------|--------|-------------|--------|--------|--------|--------|--|

| Symbol |        |             |        |        |        |        |  |

|        | Min    | Тур         | Max    | Min    | Тур    | Max    |  |

| А      | -      | -           | 1.600  | -      | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551 | 0.0571 |  |

| b      | 0.220  | 0.320       | 0.380  | 0.0087 | 0.0126 | 0.0150 |  |

| С      | 0.090  | -           | 0.200  | 0.0035 | -      | 0.0079 |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |

| D3     | -      | 12.350      | -      | -      | 0.4862 | -      |  |

| E      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |

| E3     | -      | 12.350      | -      | -      | 0.4862 | -      |  |

| е      | -      | 0.650       | -      | -      | 0.0256 | -      |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236 | 0.0295 |  |

| L1     | -      | 1.000       | -      | -      | 0.0394 | -      |  |

| k      | 0°     | 3.5°        | 7°     | 0°     | 3.5°   | 7°     |  |

| CCC    | -      | -           | 0.100  | -      | -      | 0.0039 |  |

# Table 49. LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data<sup>(1)</sup>

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13-Oct-2016 | 14       | <ul> <li>Updated:</li> <li>Title of <i>Figure 7: STM8AF52x6 VFQFPN32 32-pin pinout</i>,<br/>(previously STM8AF5286UC VFQFPN32 32-pin pinout)</li> <li>Footnotes of <i>Figure 60: STM8AF526x/8x/Ax and</i><br/><i>STM8AF6269/8x/Ax ordering information scheme1</i></li> <li><i>Table 11: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin</i><br/><i>description</i> replaced "STM8AF5286UC VQFPN32" with<br/>"STM8AF52x6 VQFPN32" at header row</li> <li>Section 10.2: Absolute maximum ratings</li> <li>Section : Device marking on page 93</li> <li>Section : Device marking on page 96</li> <li>Section : Device marking on page 104</li> <li>Section : Device marking on page 108</li> <li>Added:</li> <li>Footnote on <i>Figure 47: LQFP80 marking example (package top</i><br/><i>view)</i>, <i>Figure 50: LQFP64 marking example (package top view)</i>,<br/><i>Figure 56: LQFP32 marking example (package top view)</i>,<br/><i>Figure 59: VFQFPN32 marking example (package top view)</i>.</li> </ul> |  |  |

| 10-Nov-2016 | 15       | Updated header row and PA6/USART_CK pin row on <i>Table 11: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |