Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af5269tay |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

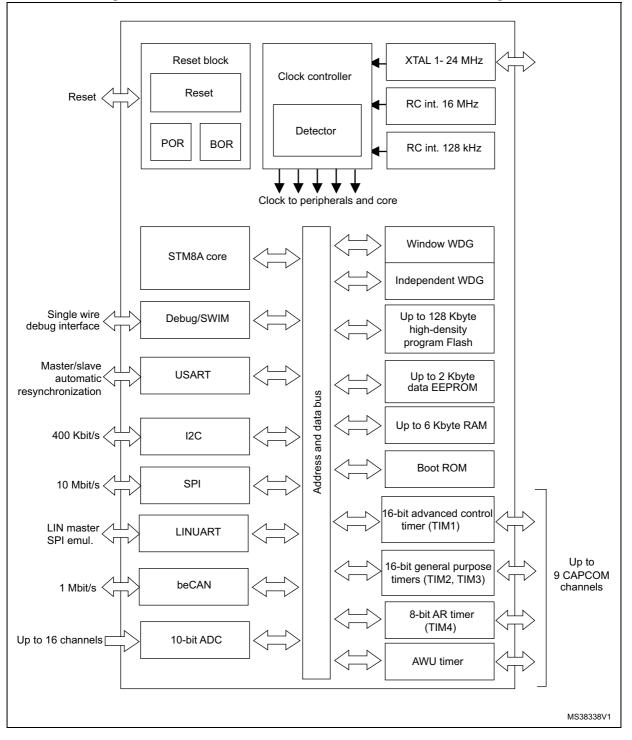

# 4 Block diagram

Figure 1. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax block diagram

DocID14395 Rev 15

## 5.5.3 128 kHz low-speed internal RC oscillator (LSI)

The frequency of this clock is 128 kHz and it is independent from the main clock. It drives the independent watchdog or the AWU wakeup timer.

In systems which do not need independent clock sources for the watchdog counters, the 128 kHz signal can be used as the system clock. This configuration has to be enabled by setting an option byte (OPT3/OPT3N, bit LSI\_EN).

## 5.5.4 24 MHz high-speed external crystal oscillator (HSE)

The external high-speed crystal oscillator can be selected to deliver the main clock in normal Run mode. It operates with quartz crystals and ceramic resonators.

- Frequency range: 1 MHz to 24 MHz

- Crystal oscillation mode: preferred fundamental

- I/Os: standard I/O pins multiplexed with OSCIN, OSCOUT

## 5.5.5 External clock input

An external clock signal can be applied to the OSCIN input pin of the crystal oscillator. The frequency range is 0 to 24 MHz.

## 5.5.6 Clock security system (CSS)

The clock security system protects against a system stall in case of an external crystal clock failure.

In case of a clock failure an interrupt is generated and the high-speed internal clock (HSI) is automatically selected with a frequency of 2 MHz (16 MHz/8).

| ······································ |                  |  |  |  |

|----------------------------------------|------------------|--|--|--|

| Control bit                            | Peripheral       |  |  |  |

| PCKEN17                                | TIM1             |  |  |  |

| PCKEN16                                | TIM3             |  |  |  |

| PCKEN15                                | TIM2             |  |  |  |

| PCKEN14                                | TIM4             |  |  |  |

| PCKEN13                                | LINUART          |  |  |  |

| PCKEN12                                | USART            |  |  |  |

| PCKEN11                                | SPI              |  |  |  |

| PCKEN10                                | l <sup>2</sup> C |  |  |  |

#### Table 4. Peripheral clock gating bits (CLK\_PCKENR1)

## 5.9.3 Serial peripheral interface (SPI)

The devices covered by this datasheet contain one SPI. The SPI is available on all the supported packages.

- Maximum speed: 10 Mbit/s or f<sub>MASTER</sub>/2 for master, 8 Mbit/s or f<sub>MASTER</sub> /2 for slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave mode/master mode management by hardware or software for both master and slave

- Programmable clock polarity and phase

- Programmable data order with MSB-first or LSB-first shifting

- Dedicated transmission and reception flags with interrupt capability

- SPI bus busy status flag

- Hardware CRC feature for reliable communication:

- CRC value can be transmitted as last byte in Tx mode

- CRC error checking for last received byte

## 5.9.4 Inter integrated circuit (I<sup>2</sup>C) interface

The devices covered by this datasheet contain one  $I^2C$  interface. The interface is available on all the supported packages.

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

- Status flags:

- Transmitter/receiver mode flag

- End-of-byte transmission flag

- I<sup>2</sup>C busy flag

- Error flags:

- Arbitration lost condition for master mode

- Acknowledgement failure after address/data transmission

- Detection of misplaced start or stop condition

- Overrun/underrun if clock stretching is disabled

# 5.10 Input/output specifications

The product features four I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

- Caution: In STM8AF5286UC device, the following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor,

- configured as output push-pull low.

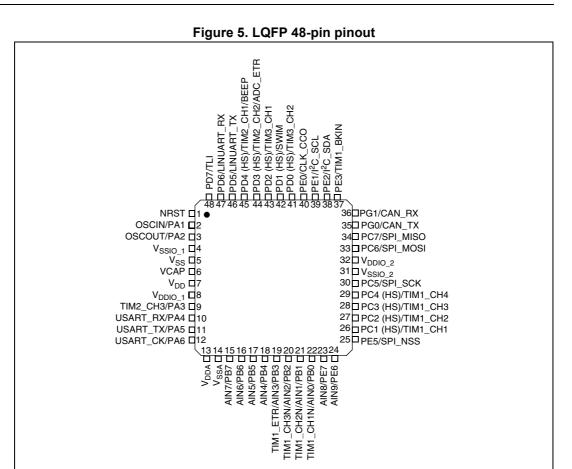

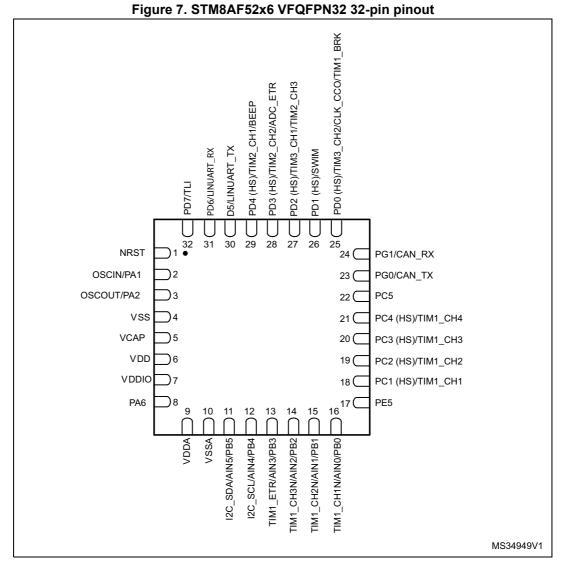

1. The CAN interface is only available on STM8AF52xx product lines.

2. HS stands for high sink capability.

The following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor, - configured as output push-pull low. 1.

2. HS stands for high sink capability.

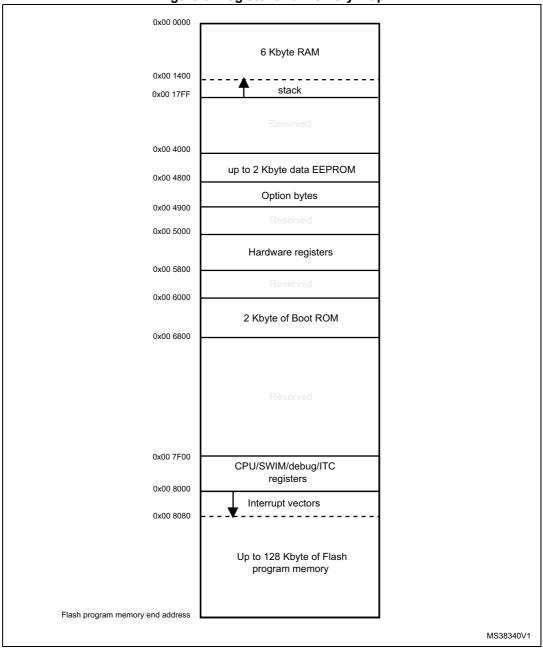

# 7 Memory and register map

# 7.1 Memory map

Figure 8. Register and memory map

| Address                   | Block | Register label | Register name                   | Reset<br>status |

|---------------------------|-------|----------------|---------------------------------|-----------------|

| 0x00 5200                 |       | SPI_CR1        | SPI control register 1          | 0x00            |

| 0x00 5201                 |       | SPI_CR2        | SPI control register 2          | 0x00            |

| 0x00 5202                 |       | SPI_ICR        | SPI interrupt control register  | 0x00            |

| 0x00 5203                 | SPI   | SPI_SR         | SPI status register             | 0x02            |

| 0x00 5204                 | 381   | SPI_DR         | SPI data register               | 0x00            |

| 0x00 5205                 |       | SPI_CRCPR      | SPI CRC polynomial register     | 0x07            |

| 0x00 5206                 |       | SPI_RXCRCR     | SPI Rx CRC register             | 0xFF            |

| 0x00 5207                 |       | SPI_TXCRCR     | SPI Tx CRC register             | 0xFF            |

| 0x00 5208 to<br>0x00 520F |       | R              | eserved area (8 bytes)          |                 |

| 0x00 5210                 |       | I2C_CR1        | I2C control register 1          | 0x00            |

| 0x00 5211                 |       | I2C_CR2        | I2C control register 2          | 0x00            |

| 0x00 5212                 |       | I2C_FREQR      | I2C frequency register          | 0x00            |

| 0x00 5213                 |       | I2C_OARL       | I2C own address register low    | 0x00            |

| 0x00 5214                 |       | I2C_OARH       | I2C own address register high   | 0x00            |

| 0x00 5215                 |       |                |                                 |                 |

| 0x00 5216                 | I2C   | I2C_DR         | I2C data register               | 0x00            |

| 0x00 5217                 | 120   | I2C_SR1        | I2C status register 1           | 0x00            |

| 0x00 5218                 |       | I2C_SR2        | I2C status register 2           | 0x00            |

| 0x00 5219                 |       | I2C_SR3        | I2C status register 3           | 0x00            |

| 0x00 521A                 |       | I2C_ITR        | I2C interrupt control register  | 0x00            |

| 0x00 521B                 |       | I2C_CCRL       | I2C clock control register low  | 0x00            |

| 0x00 521C                 |       | I2C_CCRH       | I2C clock control register high | 0x00            |

| 0x00 521D                 |       | I2C_TRISER     | I2C TRISE register              | 0x02            |

| 0x00 521E to<br>0x00 522F |       | Re             | eserved area (18 bytes)         |                 |

Table 14. General hardware register map (continued)

# **10** Electrical characteristics

## 10.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

## 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = -40$  °C,  $T_A = 25$  °C, and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production.

## 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5.0$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

#### 10.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 10.1.4 Loading capacitor

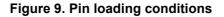

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

| Symbol                | Parameter                                      | Conditions              | Min              | Тур               | Мах  | Unit |  |

|-----------------------|------------------------------------------------|-------------------------|------------------|-------------------|------|------|--|

| +                     | V <sub>DD</sub> rise time rate                 | -                       | 2 <sup>(1)</sup> | -                 | 8    |      |  |

| t <sub>VDD</sub>      | V <sub>DD</sub> fall time rate                 | -                       | 2 <sup>(1)</sup> | -                 | ∞    | µs/V |  |

| +                     | Reset release delay                            | V <sub>DD</sub> rising  | -                | 1                 | 1.7  | ms   |  |

| t <sub>TEMP</sub>     | Reset generation delay                         | V <sub>DD</sub> falling | -                | 3                 | -    | μs   |  |

| V <sub>IT+</sub>      | Power-on reset<br>threshold <sup>(2) (3)</sup> | -                       | 2.65             | 2.8               | 2.95 | v    |  |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold                   | -                       | 2.58             | 2.73              | 2.88 | v    |  |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis                  | -                       | -                | 70 <sup>(1)</sup> | -    | mV   |  |

Table 25. Operating conditions at power-up/power-down

1. Guaranteed by design, not tested in production.

2. If V<sub>DD</sub> is below 3 V, the code execution is guaranteed above the V<sub>IT-</sub> and V<sub>IT+</sub> thresholds. RAM content is kept. The EEPROM programming sequence must not be initiated.

3. There is inrush current into V<sub>DD</sub> present after device power on to charge C<sub>EXT</sub> capacitor. This inrush energy depends from C<sub>EXT</sub> capacitor value. For example, a C<sub>EXT</sub> of 1  $\mu$ F requires Q=1  $\mu$ F x 1.8 V = 1.8  $\mu$ C.

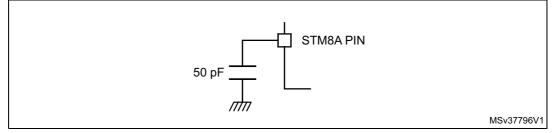

## **10.3.1 VCAP external capacitor**

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 24*. Care should be taken to limit the series inductance to less than 15 nH.

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

#### **10.3.2** Supply current characteristics

The current consumption is measured as described in *Figure 9 on page 59* and *Figure 10 on page 60*.

If not explicitly stated, general conditions of temperature and voltage apply.

| Symbol                              | Parameter                    | Conditions                    | Min | Тур | Мах | Unit |  |  |

|-------------------------------------|------------------------------|-------------------------------|-----|-----|-----|------|--|--|

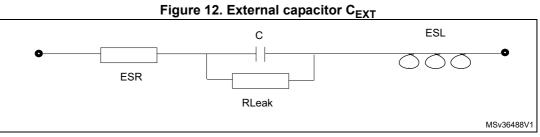

| R <sub>F</sub>                      | Feedback resistor            | -                             | -   | 220 | -   | kΩ   |  |  |

| $C_{L1}/C_{L2}^{(1)}$               | Recommended load capacitance | -                             | -   | -   | 20  | pF   |  |  |

| 9 <sub>m</sub>                      | Oscillator trans conductance | -                             | 5   | -   | -   | mA/V |  |  |

| t <sub>SU(HSE)</sub> <sup>(2)</sup> | Startup time                 | V <sub>DD</sub> is stabilized | -   | 2.8 | -   | ms   |  |  |

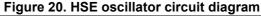

Table 32. HSE oscillator characteristics

1. The oscillator needs two load capacitors,  $C_{L1}$  and  $C_{L2}$ , to act as load for the crystal. The total load capacitance ( $C_{Load}$ ) is  $(C_{L1} * C_{L2})/(C_{L1} + C_{L2})$ . If  $C_{L1} = C_{L2}$ ,  $C_{load} = C_{L1/2}$ . Some oscillators have built-in load capacitors,  $C_{L1}$  and  $C_{L2}$ .

2. This value is the startup time, measured from the moment it is enabled (by software) until a stabilized 24 MHz oscillation is reached. It can vary with the crystal type that is used.

## HSE oscillator critical g<sub>m</sub> formula

The crystal characteristics have to be checked with the following formula:

#### Equation 1

$g_m \gg g_{mcrit}$

where  $g_{mcrit}$  can be calculated with the crystal parameters as follows:

#### **Equation 2**

$$g_{mcrit} = (2 \times \Pi \times {}^{f}HSE)^{2} \times R_{m}(2Co + C)^{2}$$

$\begin{array}{l} \textbf{R}_m: \mbox{ Notional resistance (see crystal specification)} \\ \textbf{L}_m: \mbox{ Notional inductance (see crystal specification)} \\ \textbf{C}_m: \mbox{ Notional capacitance (see crystal specification)} \\ \textbf{Co}: \mbox{ Shunt capacitance (see crystal specification)} \\ \textbf{C}_{L1} = \textbf{C}_{L2} = \textbf{C}: \mbox{ Grounded external capacitance} \end{array}$

DocID14395 Rev 15

## **10.3.4** Internal clock sources and timing characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

### High-speed internal RC oscillator (HSI)

| Symbol               | Parameter                                    | Conditions                                                                                                                               | Min | Тур | Max              | Unit |

|----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------|------|

| f <sub>HSI</sub>     | Frequency                                    | -                                                                                                                                        | -   | 16  | -                | MHz  |

| ACC <sub>HS</sub>    | HSI oscillator user trimming accuracy        | Trimmed by the application for any $V_{DD}$ and $T_{A}$ conditions                                                                       | -1  | -   | 1                | %    |

|                      | HSI oscillator accuracy (factory calibrated) | $\label{eq:V_DD} \begin{split} V_{DD} &= 3.0 \ V \leq V_{DD} \leq 5.5 \ V, \\ -40 \ ^{\circ}C \leq T_A \leq 150 \ ^{\circ}C \end{split}$ | -5  | -   | 5                |      |

| t <sub>su(HSI)</sub> | HSI oscillator wakeup time                   | -                                                                                                                                        | -   | -   | 2 <sup>(1)</sup> | μs   |

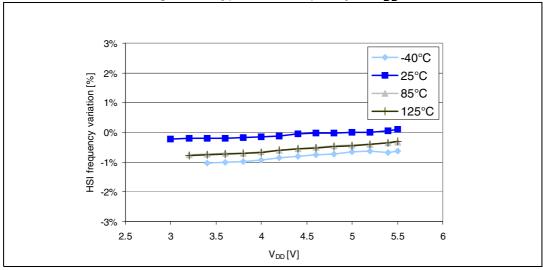

## Table 33. HSI oscillator characteristics

1. Guaranteed by characterization results, not tested in production.

Figure 21. Typical HSI frequency vs  $V_{DD}$

| Symbol           | Parameter                            | Condition                      | Min                  | Max | Unit   |

|------------------|--------------------------------------|--------------------------------|----------------------|-----|--------|

| T <sub>WE</sub>  | Temperature for writing and erasing  | -                              | -40                  | 150 | °C     |

| N                | Data memory endurance <sup>(1)</sup> | T <sub>A</sub> = 25 °C         | 300 k                | -   | cycles |

| N <sub>WE</sub>  | (erase/write cycles)                 | $T_A = -40^{\circ}C$ to 125 °C | 100 k <sup>(2)</sup> | -   | cycles |

| +                | Data retention time                  | T <sub>A</sub> = 25 °C         | 40 <sup>(2)(3)</sup> | -   | Voare  |

| t <sub>RET</sub> |                                      | T <sub>A</sub> = 55 °C         | 20 <sup>(2)(3)</sup> | -   | years  |

#### Table 37. Data memory

1. The physical granularity of the memory is four bytes, so cycling is performed on four bytes even when a write/erase operation addresses a single byte.

2. More information on the relationship between data retention time and number of write/erase cycles is available in a separate technical document.

3. Retention time for 256B of data memory after up to 1000 cycles at 125 °C.

# 10.3.6 I/O port pin characteristics

## **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage, using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                          | Parameter                                                         | Conditions                                                                              | Min                     | Тур                      | Мах                     | Unit |

|---------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------|--------------------------|-------------------------|------|

| V <sub>IL</sub>                 | Low-level input voltage                                           |                                                                                         | -0.3 V                  |                          | 0.3 x V <sub>DD</sub>   |      |

| V <sub>IH</sub>                 | High-level input voltage                                          | _                                                                                       | 0.7 x V <sub>DD</sub>   |                          | V <sub>DD</sub> + 0.3 V |      |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>                                         |                                                                                         | -                       | 0.1 x<br>V <sub>DD</sub> | -                       | V    |

| M                               |                                                                   | Standard I/0, V <sub>DD</sub> = 5 V,<br>I = 3 mA                                        | V <sub>DD</sub> - 0.5 V | -                        | -                       |      |

| ∙он                             | V <sub>OH</sub> High-level output voltage                         | Standard I/0, V <sub>DD</sub> = 3 V,<br>I = 1.5 mA                                      | V <sub>DD</sub> - 0.4 V | -                        | -                       |      |

|                                 |                                                                   | High sink and true open<br>drain I/0, V <sub>DD</sub> = 5 V<br>I = 8 mA                 | -                       | -                        | 0.5                     |      |

| $V_{OL}$                        | Low-level output voltage                                          | Standard I/0, V <sub>DD</sub> = 5 V<br>I = 3 mA                                         | -                       | -                        | 0.6                     | V    |

|                                 |                                                                   | Standard I/0, V <sub>DD</sub> = 3 V<br>I = 1.5 mA                                       | -                       | -                        | 0.4                     |      |

| R <sub>pu</sub>                 | Pull-up resistor                                                  | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$                                                     | 35                      | 50                       | 65                      | kΩ   |

|                                 |                                                                   | Fast I/Os<br>Load = 50 pF                                                               | -                       | -                        | 35 <sup>(2)</sup>       |      |

|                                 | Rise and fall time                                                | Standard and high sink I/Os<br>Load = 50 pF                                             | -                       | -                        | 125 <sup>(2)</sup>      | 20   |

| t <sub>R</sub> , t <sub>F</sub> | (10% - 90%)                                                       | Fast I/Os<br>Load = 20 pF                                                               | -                       | -                        | 20 <sup>(2)</sup>       | ns   |

|                                 |                                                                   | Standard and high sink I/Os<br>Load = 20 pF                                             | -                       | -                        | 50 <sup>(2)</sup>       |      |

| l <sub>lkg</sub>                | Digital input pad leakage current                                 | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                        | -                       | -                        | ±1                      | μA   |

| 1                               | Analog input pad leakage                                          | $V_{SS} \le V_{IN} \le V_{DD}$<br>-40 °C < T <sub>A</sub> < 125 °C                      | -                       | -                        | ±250                    | 24   |

| l <sub>Ikg ana</sub>            | current                                                           | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub><br>-40 °C < T <sub>A</sub> < 150 °C | -                       | -                        | ±500                    | nA   |

| l <sub>lkg(inj)</sub>           | Leakage current in<br>adjacent I/O <sup>(3)</sup>                 | Injection current ±4 mA                                                                 | -                       | -                        | ±1 <sup>(3)</sup>       | μA   |

| I <sub>DDIO</sub>               | Total current on either<br>V <sub>DDIO</sub> or V <sub>SSIO</sub> | Including injection currents                                                            | -                       | -                        | 60                      | mA   |

1. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results, not tested in production.

# 10.3.10 I<sup>2</sup>C interface characteristics

| 0h.e.l                                     | Demonster                                               | Standard           | Standard mode I <sup>2</sup> C |                    | de l <sup>2</sup> C <sup>(1)</sup> | 11 14 |

|--------------------------------------------|---------------------------------------------------------|--------------------|--------------------------------|--------------------|------------------------------------|-------|

| Symbol                                     | Parameter                                               | Min <sup>(2)</sup> | Max <sup>(2)</sup>             | Min <sup>(2)</sup> | Max <sup>(2)</sup>                 | Unit  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                      | 4.7                | -                              | 1.3                | -                                  |       |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                     | 4.0                | -                              | 0.6                | -                                  | μs    |

| t <sub>su(SDA)</sub>                       | SDA setup time                                          | 250                | -                              | 100                | -                                  |       |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                      | 0 <sup>(3)</sup>   | -                              | 0 <sup>(4)</sup>   | 900 <sup>(3)</sup>                 |       |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time<br>(V <sub>DD</sub> 3 V to 5.5 V) | -                  | 1000                           | -                  | 300                                | ns    |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time<br>(V <sub>DD</sub> 3 V to 5.5 V) | -                  | 300                            | -                  | 300                                |       |

| t <sub>h(STA)</sub>                        | START condition hold time                               | 4.0                | -                              | 0.6                | -                                  |       |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time                     | 4.7                | -                              | 0.6                | -                                  | μs    |

| t <sub>su(STO)</sub>                       | STOP condition setup time                               | 4.0                | -                              | 0.6                | -                                  | μs    |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free)                 | 4.7                | -                              | 1.3                | -                                  | μs    |

| Cb                                         | Capacitive load for each bus line                       | -                  | 400                            | -                  | 400                                | pF    |

## Table 42. I<sup>2</sup>C characteristics

1.  $f_{MASTER},$  must be at least 8 MHz to achieve max fast I^2C speed (400 kHz)  $\,$

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

## 10.3.12 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter Conditions                                                                                                              |                                                                                                                                                                                                                            | Level/class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = 25 \ ^{\circ}\text{C}, \\ \text{f}_{\text{MASTER}} = 16 \ \text{MHz} \ (\text{HSI clock}), \\ \text{Conforms to IEC 1000-4-2} \end{array}$ | 3/B         |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>f <sub>MASTER</sub> = 16 MHz (HSI clock),<br>Conforms to IEC 1000-4-4                                                                                                                  | 4/A         |

#### Table 45. EMS data

#### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter                  | Conditions              | Class <sup>(1)</sup> |

|--------|----------------------------|-------------------------|----------------------|

|        |                            | $T_A = 25 \ ^\circ C$   |                      |

|        | Statia latah un alaga      | T <sub>A</sub> = 85 °C  | ٨                    |

| LU     | LU Static latch-up class - | T <sub>A</sub> = 125 °C | A                    |

|        |                            | T <sub>A</sub> = 150 °C |                      |

| Table 48. Electrica | I sensitivities |

|---------------------|-----------------|

|---------------------|-----------------|

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

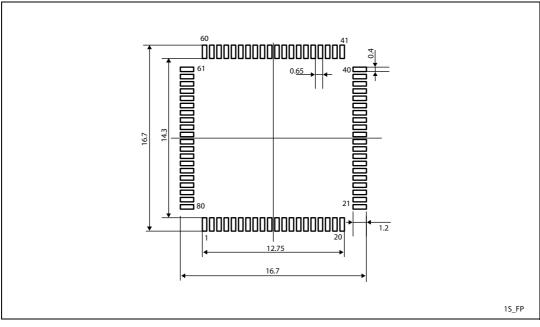

1. Dimensions are expressed in millimeters.

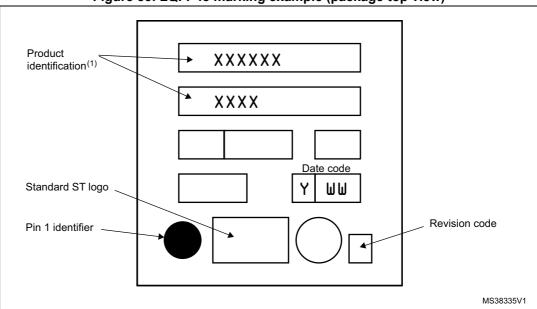

#### Figure 53. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13-Oct-2016 | 14       | <ul> <li>Updated:</li> <li>Title of <i>Figure 7: STM8AF52x6 VFQFPN32 32-pin pinout</i>,<br/>(previously STM8AF5286UC VFQFPN32 32-pin pinout)</li> <li>Footnotes of <i>Figure 60: STM8AF526x/8x/Ax and</i><br/><i>STM8AF6269/8x/Ax ordering information scheme1</i></li> <li><i>Table 11: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin</i><br/><i>description</i> replaced "STM8AF5286UC VQFPN32" with<br/>"STM8AF52x6 VQFPN32" at header row</li> <li>Section 10.2: Absolute maximum ratings</li> <li>Section : Device marking on page 93</li> <li>Section : Device marking on page 96</li> <li>Section : Device marking on page 104</li> <li>Section : Device marking on page 108</li> <li>Added:</li> <li>Footnote on <i>Figure 47: LQFP80 marking example (package top</i><br/><i>view)</i>, <i>Figure 50: LQFP64 marking example (package top view)</i>,<br/><i>Figure 56: LQFP32 marking example (package top view)</i>,<br/><i>Figure 59: VFQFPN32 marking example (package top view)</i>.</li> </ul> |

| 10-Nov-2016 | 15       | Updated header row and PA6/USART_CK pin row on <i>Table 11:</i><br>STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |