Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 6x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

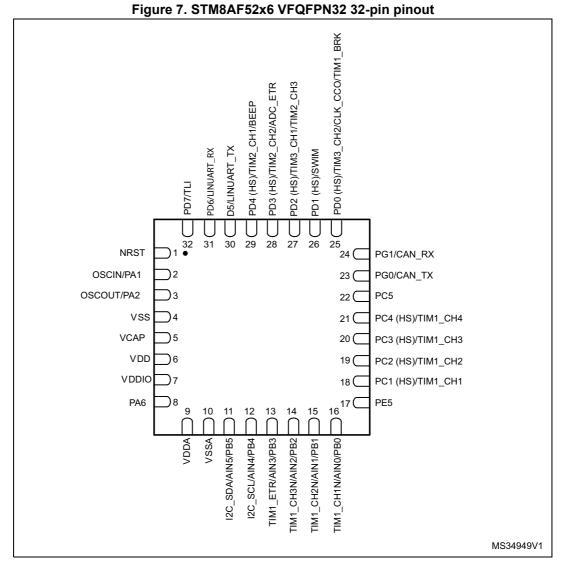

| Package / Case             | 32-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af52a6ucy |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM8AF526x/8x/Ax and STM8AF6269/8x/Ax automotive 8-bit microcontrollers described in this datasheet offer from 32 Kbyte to 128 Kbyte of non volatile memory and integrated true data EEPROM. They are referred to as high density STM8A devices in STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

The STM8AF52 series features a CAN interface.

All devices of the STM8A product line provide the following benefits: reduced system cost, performance and robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, wtachdog, and brown-out reset.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map, and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8A family thanks to their advanced core which is made in a state-of-the art technology for automotive applications with 3.3 V to 5.5 V operating supply.

All STM8A and ST7 microcontrollers are supported by the same tools including STVD/STVP development environment, the STice emulator and a low-cost, third party incircuit debugging tool.

# 5.7 Timers

## 5.7.1 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications. The watchdog timer activity is controlled by the application program or option bytes. Once the watchdog is activated, it cannot be disabled by the user program without going through reset.

#### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application timing perfectly. The application software must refresh the counter before time-out and during a limited time window. If the counter is refreshed outside this time window, a reset is issued.

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure. If the hardware watchdog feature is enabled through the device option bits, the watchdog is automatically enabled at power-on, and generates a reset unless the key register is written by software before the counter reaches the end of count.

## 5.7.2 Auto-wakeup counter

This counter is used to cyclically wakeup the device in Active-halt mode. It can be clocked by the internal 128 kHz internal low-frequency RC oscillator or external clock.

LSI clock can be internally connected to TIM3 input capture channel 1 for calibration.

#### 5.7.3 Beeper

This function generates a rectangular signal in the range of 1, 2 or 4 kHz which can be output on a pin. This is useful when audible sounds without interference need to be generated for use in the application.

## 5.7.4 Advanced control and general purpose timers

STM8A devices described in this datasheet, contain up to three 16-bit advanced control and general purpose timers providing nine CAPCOM channels in total. A CAPCOM channel can be used either as input compare, output compare or PWM channel. These timers are named TIM1, TIM2 and TIM3.

# 5.10 Input/output specifications

The product features four I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

- Caution: In STM8AF5286UC device, the following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor,

- configured as output push-pull low.

The following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor, - configured as output push-pull low. 1.

2. HS stands for high sink capability.

|        | Pir    |        | mber                          |                     |                            |      |          | npu |                |           | Out   |    | P  | descript                               | ion (continued)                    |                                                      |

|--------|--------|--------|-------------------------------|---------------------|----------------------------|------|----------|-----|----------------|-----------|-------|----|----|----------------------------------------|------------------------------------|------------------------------------------------------|

|        |        |        |                               |                     |                            |      |          | .pu | •              |           | Jud   |    | 1  |                                        |                                    |                                                      |

| LQFP80 | LQFP64 | LQFP48 | STM8AF62xx<br>LQFP32/VFQFPN32 | STM8AF52x6 VFQFPN32 | Pin name                   | Type | Floating | Mpu | Ext. interrupt | High sink | Speed | OD | ЬP | Main<br>function<br>(after<br>reset)   | Default<br>alternate<br>function   | Alternate<br>function<br>after remap<br>[option bit] |

| 38     | -      | -      | -                             | -                   | PH7/<br>TIM1_CH1N          | I/O  | x        | х   | -              | -         | O1    | х  | х  | Port H7                                | Timer 1 -<br>inverted<br>channel 2 | -                                                    |

| 39     | 31     | 23     | -                             | -                   | PE7/AIN8                   | I/O  | X        | Х   | I              | -         | 01    | х  | х  | Port E7                                | Analog<br>input 8                  | -                                                    |

| 40     | 32     | 24     |                               |                     | PE6/AIN9                   | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port E6                                | Analog<br>input 9                  | -                                                    |

| 41     | 33     | 25     | 17                            | 17                  | PE5/SPI_NSS <sup>(2)</sup> | I/O  | x        | х   | х              | -         | 01    | х  | x  | Port E5                                | SPI<br>master/<br>slave<br>select  | -                                                    |

| 42     | -      | -      | -                             | -                   | PC0/ADC_ETR                | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port C0                                | ADC<br>trigger<br>input            | -                                                    |

| 43     | 34     | 26     | 18                            | 18                  | PC1/TIM1_CH1               | I/O  | Х        | Х   | Х              | HS        | O3    | х  | х  | Port C1 Timer 1 - channel 1            |                                    | -                                                    |

| 44     | 35     | 27     | 19                            | 19                  | PC2/TIM1_CH2               | I/O  | x        | х   | х              | HS        | O3    | х  | х  | Port C2                                | Timer 1-<br>channel 2              | -                                                    |

| 45     | 36     | 28     | 20                            | 20                  | PC3/TIM1_CH3               | I/O  | x        | х   | х              | HS        | O3    | х  | х  | Port C3                                | Timer 1 -<br>channel 3             | -                                                    |

| 46     | 37     | 29     | 21                            | 21                  | PC4/TIM1_CH4               | I/O  | X        | х   | х              | HS        | O3    | х  | х  | Port C4                                | Timer 1 -<br>channel 4             | -                                                    |

| 47     | 38     | 30     | 22                            | 22                  | PC5/SPI_SCK <sup>(2)</sup> | I/O  | Х        | Х   | Х              | -         | O3    | Х  | Х  | Port C5                                | SPI clock                          | -                                                    |

| 48     | 39     | 31     | -                             | I                   | V <sub>SSIO_2</sub>        | S    | -        | -   | -              | -         | -     | -  | -  |                                        | ground                             | -                                                    |

| 49     | 40     | 32     | -                             | I                   | V <sub>DDIO_2</sub>        | S    | -        | -   | -              | I         | -     | -  | -  | I/O pow                                | er supply                          | -                                                    |

| 50     | 41     | 33     | 23                            | -                   | PC6/SPI_MOSI               | I/O  | x        | х   | х              | -         | O3    | х  | x  | Port C6 SPI master<br>out/<br>slave in |                                    | -                                                    |

| 51     | 42     | 34     | 24                            | -                   | PC7/SPI_MISO               | I/O  | x        | х   | х              | -         | O3    | х  | x  | Port C7                                | SPI master<br>in/ slave<br>out     | -                                                    |

| 52     | 43     | 35     | -                             | 23                  | PG0/CAN_TX                 | I/O  | x        | х   | -              | -         | 01    | х  | х  | Port G0                                | CAN<br>transmit                    | -                                                    |

| 53     | 44     | 36     | -                             | 24                  | PG1/CAN_RX                 | I/O  | X        | х   | -              | -         | 01    | х  | х  | Port G1                                | CAN<br>receive                     | -                                                    |

| 54     | 45     | -      | -                             | -                   | PG2                        | I/O  | X        | Х   | -              | -         | 01    | Х  | Х  | Port G2                                | -                                  | -                                                    |

| Table 11. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description | (continued) |

|-----------------------------------------------------------------|-------------|

|                                                                 |             |

| Address   | Block  | Register label | Register name                     | Reset               |

|-----------|--------|----------------|-----------------------------------|---------------------|

|           |        | -              | -                                 | status              |

| 0x00 5014 |        | PE_ODR         | Port E data output latch register | 0x00                |

| 0x00 5015 |        | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016 | Port E | PE_DDR         | Port E data direction register    | 0x00                |

| 0x00 5017 |        | PE_CR1         | Port E control register 1         | 0x00                |

| 0x00 5018 |        | PE_CR2         | Port E control register 2         | 0x00                |

| 0x00 5019 |        | PF_ODR         | Port F data output latch register | 0x00                |

| 0x00 501A |        | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B | Port F | PF_DDR         | Port F data direction register    | 0x00                |

| 0x00 501C |        | PF_CR1         | Port F control register 1         | 0x00                |

| 0x00 501D |        | PF_CR2         | Port F control register 2         | 0x00                |

| 0x00 501E |        | PG_ODR         | Port G data output latch register | 0x00                |

| 0x00 501F | Port G | PG_IDR         | Port G input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5020 |        | PG_DDR         | Port G data direction register    | 0x00                |

| 0x00 5021 |        | PG_CR1         | Port G control register 1         | 0x00                |

| 0x00 5022 |        | PG_CR2         | Port G control register 2         | 0x00                |

| 0x00 5023 |        | PH_ODR         | Port H data output latch register | 0x00                |

| 0x00 5024 |        | PH_IDR         | Port H input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5025 | Port H | PH_DDR         | Port H data direction register    | 0x00                |

| 0x00 5026 |        | PH_CR1         | Port H control register 1         | 0x00                |

| 0x00 5027 |        | PH_CR2         | Port H control register 2         | 0x00                |

| 0x00 5028 |        | PI_ODR         | Port I data output latch register | 0x00                |

| 0x00 5029 |        | PI_IDR         | Port I input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 502A | Port I | PI_DDR         | Port I data direction register    | 0x00                |

| 0x00 502B |        | PI_CR1         | Port I control register 1         | 0x00                |

| 0x00 502C |        | PI_CR2         | Port I control register 2         | 0x00                |

| Table 13 I/O | port hardware register map (continued) |   |

|--------------|----------------------------------------|---|

|              | port naruware register map (continueu) | , |

1. Depends on the external circuitry.

| Address Block             |                          | Register label                                 | Register label Register name                     |                     |  |  |

|---------------------------|--------------------------|------------------------------------------------|--------------------------------------------------|---------------------|--|--|

| 0x00 505A                 |                          | FLASH_CR1                                      | Flash control register 1                         | 0x00                |  |  |

| 0x00 505B                 |                          | FLASH_CR2                                      | Flash control register 2                         | 0x00                |  |  |

| 0x00 505C                 |                          | FLASH_NCR2                                     | Flash complementary control register 2           | 0xFF                |  |  |

| 0x00 505D                 | Flash                    | FLASH_FPR                                      | Flash protection register                        | 0x00                |  |  |

| 0x00 505E                 |                          | FLASH_NFPR                                     | Flash complementary protection register          | 0xFF                |  |  |

| 0x00 505F                 |                          | FLASH_IAPSR                                    | Flash in-application programming status register | 0x40                |  |  |

| 0x00 5060 to<br>0x005061  |                          | Reserved area (2 bytes)                        |                                                  |                     |  |  |

| 0x00 5062                 | Flash                    | FLASH_PUKR                                     | Flash Program memory unprotection register       | 0x00                |  |  |

| 0x00 5063                 | Reserved area (1 byte)   |                                                |                                                  |                     |  |  |

| 0x00 5064                 | Flash                    | FLASH_DUKR                                     | Data EEPROM unprotection register                | 0x00                |  |  |

| 0x00 5065 to<br>0x00 509F |                          | Re                                             | eserved area (59 bytes)                          |                     |  |  |

| 0x00 50A0                 | ITC                      | EXTI_CR1 External interrupt control register 1 |                                                  | 0x00                |  |  |

| 0x00 50A1                 | ne                       | EXTI_CR2                                       | External interrupt control register 2            | 0x00                |  |  |

| 0x00 50A2 to<br>0x00 50B2 |                          | Re                                             | eserved area (17 bytes)                          |                     |  |  |

| 0x00 50B3                 | RST                      | RST_SR                                         | Reset status register                            | 0xXX <sup>(1)</sup> |  |  |

| 0x00 50B4 to<br>0x00 50BF | Reserved area (12 bytes) |                                                |                                                  |                     |  |  |

| 0x00 50C0                 | CLK                      | CLK_ICKR                                       | Internal clock control register                  | 0x01                |  |  |

| 0x00 50C1                 | ULN                      | CLK_ECKR                                       | External clock control register                  | 0x00                |  |  |

| 0x00 50C2                 |                          | F                                              | Reserved area (1 byte)                           |                     |  |  |

Table 14. General hardware register map

| Address                   | Block | Register label            | Register name        | Reset<br>status     |  |  |  |

|---------------------------|-------|---------------------------|----------------------|---------------------|--|--|--|

| 0x00 5437                 | beCAN | CAN_PF                    | CAN paged register F | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5438 to<br>0x00 57FF |       | Reserved area (968 bytes) |                      |                     |  |  |  |

Table 14. General hardware register map (continued)

1. Depends on the previous reset source.

2. Write only register.

3. If the bootloader is enabled, it is initialized to 0x00.

#### Table 15. CPU/SWIM/debug module/interrupt controller registers

| Address                      | Block              | Register label | Register name                          | Reset<br>status     |

|------------------------------|--------------------|----------------|----------------------------------------|---------------------|

| 0x00 7F00                    |                    | А              | Accumulator                            | 0x00                |

| 0x00 7F01                    |                    | PCE            | Program counter extended               | 0x00                |

| 0x00 7F02                    |                    | PCH            | Program counter high                   | 0x80                |

| 0x00 7F03                    |                    | PCL            | Program counter low                    | 0x00                |

| 0x00 7F04                    |                    | ХН             | X index register high                  | 0x00                |

| 0x00 7F05                    | CPU <sup>(1)</sup> | XL             | X index register low                   | 0x00                |

| 0x00 7F06                    |                    | YH             | Y index register high                  | 0x00                |

| 0x00 7F07                    |                    | YL             | Y index register low                   | 0x00                |

| 0x00 7F08                    |                    | SPH            | Stack pointer high                     | 0x17 <sup>(2)</sup> |

| 0x00 7F09                    |                    | SPL            | Stack pointer low                      | 0xFF                |

| 0x00 7F0A                    |                    | CC             | Condition code register                | 0x28                |

| 0x00 7F0B<br>to 0x00<br>7F5F |                    |                | Reserved area (85 bytes)               |                     |

| 0x00 7F60                    | CPU                | CFG_GCR        | Global configuration register          | 0x00                |

| 0x00 7F70                    |                    | ITC_SPR1       | Interrupt software priority register 1 | 0xFF                |

| 0x00 7F71                    |                    | ITC_SPR2       | Interrupt software priority register 2 | 0xFF                |

| 0x00 7F72                    |                    | ITC_SPR3       | Interrupt software priority register 3 | 0xFF                |

| 0x00 7F73                    | ITC                | ITC_SPR4       | Interrupt software priority register 4 | 0xFF                |

| 0x00 7F74                    | ne                 | ITC_SPR5       | Interrupt software priority register 5 | 0xFF                |

| 0x00 7F75                    |                    | ITC_SPR6       | Interrupt software priority register 6 | 0xFF                |

| 0x00 7F76                    |                    | ITC_SPR7       | Interrupt software priority register 7 | 0xFF                |

| 0x00 7F77                    |                    | ITC_SPR8       | Interrupt software priority register 8 | 0xFF                |

| 0x00 7F78<br>to<br>0x00 7F79 |                    |                | Reserved area (2 bytes)                |                     |

| 0x00 7F80                    | SWIM               | SWIM_CSR       | SWIM control status register           | 0x00                |

DocID14395 Rev 15

| Option byte no. | Description                                                                                                                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | LSI_EN: Low speed internal clock enable<br>0: LSI clock is not available as CPU clock source<br>1: LSI clock is available as CPU clock source                                                                                    |

| 0072            | IWDG_HW: Independent watchdog<br>0: IWDG Independent watchdog activated by software<br>1: IWDG Independent watchdog activated by hardware                                                                                        |

| OPT3            | WWDG_HW: Window watchdog activation<br>0: WWDG window watchdog activated by software<br>1: WWDG window watchdog activated by hardware                                                                                            |

|                 | WWDG_HALT: Window watchdog reset on Halt<br>0: No reset generated on Halt if WWDG active<br>1: Reset generated on Halt if WWDG active                                                                                            |

|                 | EXTCLK: External clock selection<br>0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                                                                                           |

| OPT4            | CKAWUSEL: Auto-wakeup unit/clock<br>0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU                                                                                         |

|                 | PRSC[1:0]: AWU clock prescaler<br>00: 24 MHz to 128 kHz prescaler<br>01: 16 MHz to 128 kHz prescaler<br>10: 8 MHz to 128 kHz prescaler<br>11: 4 MHz to 128 kHz prescaler                                                         |

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time<br>This configures the stabilization time to 0.5, 8, 128, and 2048 HSE cycles<br>with corresponding option byte values of 0xE1, 0xD2, 0xB4, and 0x00.                     |

| OPT6            | <b>TMU</b> [3:0]: Enable temporary memory unprotection<br>0101: TMU disabled (permanent ROP).<br>Any other value: TMU enabled.                                                                                                   |

| OPT7            | <ul> <li>WAIT STATE: Wait state configuration</li> <li>This option configures the number of wait states inserted when reading from the Flash/data EEPROM memory.</li> <li>0: No wait state</li> <li>1: One wait state</li> </ul> |

| OPT8            | TMU_KEY 1 [7:0]: Temporary unprotection key 0           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                          |

| OPT9            | TMU_KEY 2 [7:0]: Temporary unprotection key 1           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                          |

| OPT10           | TMU_KEY 3 [7:0]: Temporary unprotection key 2<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                 |

| OPT11           | TMU_KEY 4 [7:0]: Temporary unprotection key 3           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                          |

| Table 19. Option byte description (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| OPT12           | TMU_KEY 5 [7:0]: Temporary unprotection key 4<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                                  |  |  |  |

| OPT13           | TMU_KEY 6 [7:0]: Temporary unprotection key 5           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |  |  |  |

| OPT14           | TMU_KEY 7 [7:0]: Temporary unprotection key 6           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |  |  |  |

| OPT15           | TMU_KEY 8 [7:0]: Temporary unprotection key 7<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                                  |  |  |  |

| OPT16           | <ul> <li>TMU_MAXATT [7:0]: TMU access failure counter</li> <li>TMU_MAXATT can be initialized with the desired value only if TMU is disabled (TMU[3:0]=0101 in OPT6 option byte).</li> <li>When TMU is enabled, any attempt to temporary remove the readout protection by using wrong key values increments the counter.</li> <li>When the option byte value reaches 0x08, the Flash memory and data EEPROM are erased.</li> </ul> |  |  |  |

| OPT17           | <b>BL[7:0]: Bootloader enable</b><br>If this option byte is set to 0x55 (complementary value 0xAA) the<br>bootloader program is activated also in case of a programmed code<br>memory (for more details, see the bootloader user manual, UM0560).                                                                                                                                                                                 |  |  |  |

## Table 19. Option byte description (continued)

# Table 27. Total current consumption in Halt and Active-halt modes. General conditions for $V_{DD}$ applied. $T_A = -40$ °C to 55 °C unless otherwise stated

|                     |                                                             |                                                      | Cond                         | ditions                                                |     |                    |      |

|---------------------|-------------------------------------------------------------|------------------------------------------------------|------------------------------|--------------------------------------------------------|-----|--------------------|------|

| Symbol              | Parameter                                                   | Main<br>voltage<br>regulator<br>(MVR) <sup>(1)</sup> | Flash<br>mode <sup>(2)</sup> | Clock source and temperature condition                 | Тур | Max                | Unit |

|                     | Supply current in                                           |                                                      | Power-                       | Clocks stopped                                         | 5   | 35 <sup>(3)</sup>  |      |

| I <sub>DD(H)</sub>  | Halt mode                                                   | Off                                                  | down                         | Clocks stopped,<br>T <sub>A</sub> = 25 °C              | 5   | 25                 |      |

|                     | Supply current in<br>Active-halt mode                       | On                                                   | Power-<br>down               | External clock 16 MHz<br>f <sub>MASTER</sub> = 125 kHz | 770 | 900 <sup>(3)</sup> | μA   |

|                     | with regulator on                                           |                                                      |                              | LSI clock 128 kHz                                      | 150 | 230 <sup>(3)</sup> |      |

| I <sub>DD(AH)</sub> | Supply current in<br>Active-halt mode<br>with regulator off |                                                      | Power-<br>down               | LSI clock 128 kHz                                      | 25  | 42 <sup>(3)</sup>  |      |

|                     |                                                             | Off                                                  |                              | LSI clock 128 kHz,<br>T <sub>A</sub> = 25 °C           | 25  | 30                 |      |

|                     | Wakeup time from<br>Active-halt mode<br>with regulator on   | On                                                   | Operating                    | T <sub>A</sub> =-40 to 150 °C                          | 10  | 30 <sup>(3)</sup>  | 116  |

| <sup>t</sup> wu(AH) | Wakeup time from<br>Active-halt mode<br>with regulator off  | Off                                                  | mode                         | 1 <sub>A</sub> - 40 10 150 C                           | 50  | 80 <sup>(3)</sup>  | μs   |

1. Configured by the REGAH bit in the CLK\_ICKR register.

2. Configured by the AHALT bit in the FLASH\_CR1 register.

3. Guaranteed by characterization results, not tested in production.

## Current consumption for on-chip peripherals

| Table 28. | Oscillator | current | consumption |

|-----------|------------|---------|-------------|

|-----------|------------|---------|-------------|

| Symbol | Parameter                                         | Conditions                                                                  |                           | Тур  | Max <sup>(1)</sup> | Unit |

|--------|---------------------------------------------------|-----------------------------------------------------------------------------|---------------------------|------|--------------------|------|

|        |                                                   | Quartz or<br>ceramic<br>resonator,<br>CL = 33 pF<br>V <sub>DD</sub> = 5 V   | f <sub>OSC</sub> = 24 MHz | 1    | 2.0 <sup>(3)</sup> |      |

|        | HSE oscillator current                            |                                                                             | f <sub>OSC</sub> = 16 MHz | 0.6  | -                  |      |

|        | consumption <sup>(2)</sup>                        |                                                                             | f <sub>OSC</sub> = 8 MHz  | 0.57 | -                  |      |

|        |                                                   | Quartz or<br>ceramic<br>resonator,<br>CL = 33 pF<br>V <sub>DD</sub> = 3.3 V | f <sub>OSC</sub> = 24 MHz | 0.5  | 1.0 <sup>(3)</sup> | mA   |

|        | HSE oscillator current consumption <sup>(2)</sup> |                                                                             | f <sub>OSC</sub> = 16 MHz | 0.25 | -                  |      |

|        |                                                   |                                                                             | f <sub>OSC</sub> = 8 MHz  | 0.18 | -                  |      |

1. During startup, the oscillator current consumption may reach 6 mA.

2. The supply current of the oscillator can be further optimized by selecting a high quality resonator with small R<sub>m</sub> value. Refer to crystal manufacturer for more details

3. Informative data.

# 10.3.5 Memory characteristics

#### Flash program memory/data EEPROM memory

General conditions: T<sub>A</sub> = -40 °C to 150 °C.

#### Table 35. Flash program memory/data EEPROM memory

| Symbol             | Parameter                                                                                        | Conditions                                                                                    | Min <sup>(1)</sup> | Тур | Max | Unit |

|--------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------|-----|-----|------|

| V <sub>DD</sub>    | Operating voltage<br>(all modes, execution/write/erase)                                          | f <sub>CPU</sub> is 16 to 24 MHz<br>with 1 ws<br>f <sub>CPU</sub> is 0 to 16 MHz<br>with 0 ws | 3.0                | -   | 5.5 | V    |

| V <sub>DD</sub>    | Operating voltage (code execution)                                                               | f <sub>CPU</sub> is 16 to 24 MHz<br>with 1 ws<br>f <sub>CPU</sub> is 0 to 16 MHz<br>with 0 ws | 2.6                | -   | 5.5 | v    |

| t <sub>prog</sub>  | Standard programming time (including<br>erase) for byte/word/block<br>(1 byte/4 bytes/128 bytes) | -                                                                                             | -                  | 6   | 6.6 |      |

| 1 - 3              | Fast programming time for 1 block (128 bytes)                                                    | -                                                                                             | -                  | 3   | 3.3 | ms   |

| t <sub>erase</sub> | Erase time for 1 block (128 bytes)                                                               | -                                                                                             | -                  | 3   | 3.3 |      |

1. Guaranteed by characterization results, not tested in production.

#### Table 36. Flash program memory

| Symbol           | Parameter                                                          | Condition              | Min  | Max | Unit   |

|------------------|--------------------------------------------------------------------|------------------------|------|-----|--------|

| T <sub>WE</sub>  | Temperature for writing and erasing                                | -                      | -40  | 150 | °C     |

| N <sub>WE</sub>  | Flash program memory endurance (erase/write cycles) <sup>(1)</sup> | T <sub>A</sub> = 25 °C | 1000 | -   | cycles |

| t                | Data retention time                                                | T <sub>A</sub> = 25 °C | 40   | -   | vears  |

| <sup>t</sup> RET |                                                                    | T <sub>A</sub> = 55 °C | 20   | -   | years  |

1. The physical granularity of the memory is four bytes, so cycling is performed on four bytes even when a write/erase operation addresses a single byte.

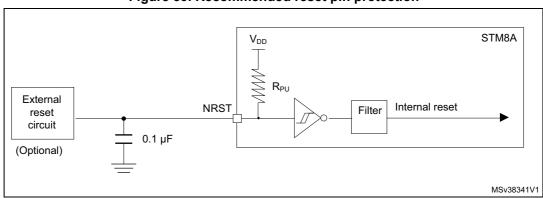

Figure 39. Recommended reset pin protection

# 10.3.8 TIM 1, 2, 3, and 4 electrical specifications

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}}$  and  $T_{\text{A}}.$

Table 40. TIM 1, 2, 3, and 4 electrical specifications

| Symbol           | Parameter                                     | Conditions | Min | Тур | Мах | Unit |

|------------------|-----------------------------------------------|------------|-----|-----|-----|------|

| f <sub>EXT</sub> | Timer external clock frequency <sup>(1)</sup> | -          | -   | -   | 24  | MHz  |

1. Not tested in production.

#### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

| LU     |                       | $T_A = 25 \ ^\circ C$   |                      |

|        | Statia latah un alaga | T <sub>A</sub> = 85 °C  | ٨                    |

|        | Static latch-up class | T <sub>A</sub> = 125 °C | A                    |

|        |                       | T <sub>A</sub> = 150 °C |                      |

| Table 48. Electrica | I sensitivities |

|---------------------|-----------------|

|---------------------|-----------------|

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

# 11.3 LQFP48 package information

Figure 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

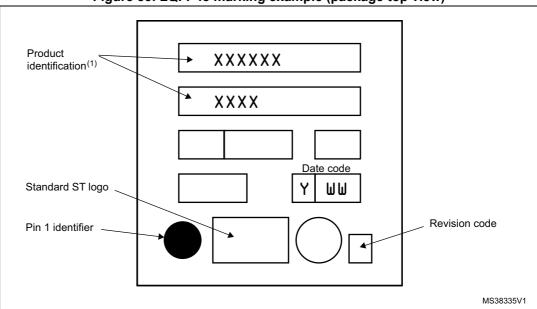

#### Figure 53. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.

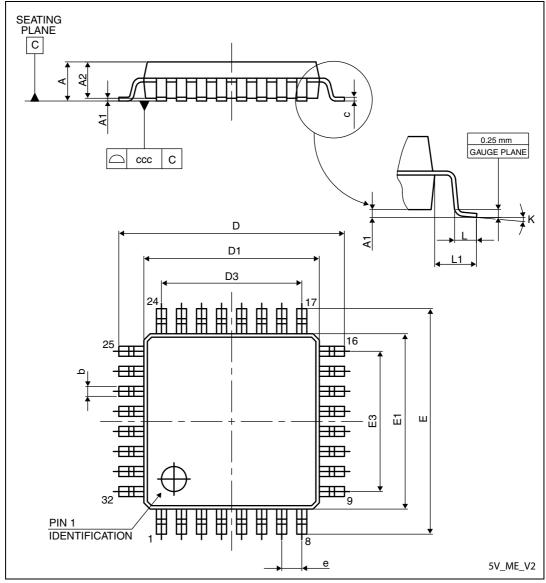

# 11.4 LQFP32 package information

Figure 54. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

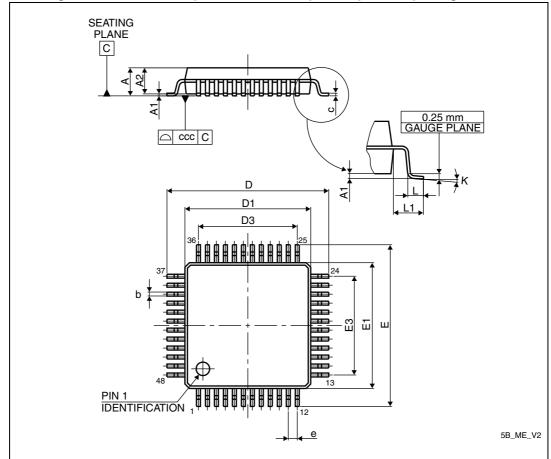

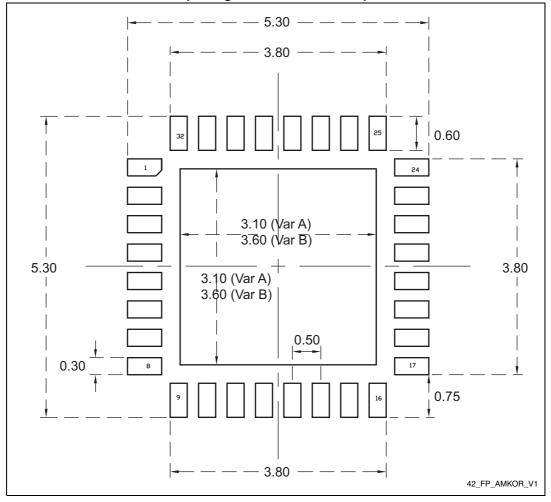

Figure 58. VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

# 13.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST visual develop (STVD) IDE and the ST visual programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8.

#### 13.2.1 STM8 toolset

The STM8 toolset with STVD integrated development environment and STVP programming software is available for free download at *www.st.com*. This package includes:

#### ST visual develop

Full-featured integrated development environment from STMicroelectronics, featuring:

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

#### ST visual programmer (STVP)

Easy-to-use, unlimited graphical interface allowing read, write and verification of the STM8A microcontroller's Flash memory. STVP also offers project mode for saving programming configurations and automating programming sequences.

#### 13.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of the application directly from an easy-to-use graphical interface. Available toolchains include:

#### C compiler for STM8

All compilers are available in free version with a limited code size depending on the compiler. For more information, refer to www.cosmic-software.com, www.raisonance.com, and www.iar.com.

#### STM8 assembler linker

Free assembly toolchain included in the STM8 toolset, which allows users to assemble and link their application source code.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-Sep-2008 | 3        | Replaced the salestype 'STM8H61xx' with 'STM8AH61xx on the first page.<br>Added 'part numbers' to heading rows of <i>Table 1: Device summary</i> .<br>Updated the 80-pin package silhouette on cover page in line with<br>POA 0062342-revD.<br><i>Table 18</i> : Renamed 'TMU key registers 0-7 [7:0]' as 'TMU key<br>registers 1-8 [7:0]'<br><i>Section 9</i> : Updated introductory text concerning option bytes which<br>do not need to be saved in a complementary form.<br><i>Table 18</i> : Renamed the option bits 'TMU[0:3]', 'NTMU[0:3]', and<br>'TMU_KEY 0-7 [7:0]' as 'TMU[3:0]', 'NTMU[3:0]', and 'TMU_KEY 1-8<br>[7:0]' respectively.<br><i>Table 21</i> : Updated values of option byte 5 (HSECNT[7:0]); inverted<br>the description of option byte 6 (TMU[3:0]); renamed option bytes 8<br>to 15 'TMU_KEY 0-7 [7:0]', as 'TMU_KEY 1-8 [7:0]'.<br>Updated 80-pin package information in line with POA 0062342-revD<br>in <i>Figure 45</i> and <i>Table 53</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 01-Jul-2009 | 4        | Added 'STM8AH61xx' and 'STM8AH51xx to document header.<br>Updated : <i>Features on page 1</i> (memories, timers, operating<br>temperature, ADC and I/Os).<br>Updated <i>Table 1: Device summary</i><br>Updated Kbyte value of program memory in <i>Section: Introduction</i><br>Changed the first two lines from the top in <i>Section: Description</i> .<br>Updated <i>Figure 1: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax</i><br><i>block diagram</i><br>Updated <i>Section 5: Product overview</i><br>In <i>Figure 5: LQFP 48-pin pinout</i> , added USART function to pins 10,<br>11, and 12; added CAN Tx and CAN Rx functions to pins 35 and 36<br>respectively.<br>Section <i>6: Pinouts and pin description:</i> deleted the text below the<br><i>Table 10: Legend/abbreviation for the pin description table</i><br><i>Table 11: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin</i><br><i>description:</i> 68th, 69th pin (LQFP80): replaced X with a dash for PP<br>output and Added a table footnote.<br>Updated <i>Figure 8: Register and memory map</i> .<br><i>Table 12: Memory model 128K:</i> updated footnote<br>Deleted the <i>Table: Stack and RAM partitioning</i><br><i>Table 17: STM8A interrupt table:</i> Updated priorities 13, 15, 17, 20<br>and 24 and changed table footnote<br>Updated <i>Section 7: Memory and register map</i><br>Updated <i>Table: Data memory, Table: I/O static characteristics,</i> and<br><i>Table 39: NRST pin characteristics.</i><br><i>Section 10.1.1: Minimum and maximum values:</i> added ambient<br>temperature T <sub>A</sub> = -40 °C<br>Updated <i>Table 20: Voltage characteristics.</i><br>Updated <i>Table 21: Current characteristics.</i><br>Updated <i>Table 22: Thermal characteristics.</i><br>Updated <i>Table 22: Thermal characteristics.</i><br>Updated <i>Table 22: Thermal characteristics.</i><br>Updated <i>Table 24: General operating conditions.</i> |

Table 55. Document revision history (continued)