Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |  |

|----------------------------|-----------------------------------------------------------------------|--|

| Product Status             | Not For New Designs                                                   |  |

| Core Processor             | STM8A                                                                 |  |

| Core Size                  | 8-Bit                                                                 |  |

| Speed                      | 24MHz                                                                 |  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                     |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |  |

| Number of I/O              | 38                                                                    |  |

| Program Memory Size        | 128KB (128K x 8)                                                      |  |

| Program Memory Type        | FLASH                                                                 |  |

| EEPROM Size                | 2K x 8                                                                |  |

| RAM Size                   | 6K x 8                                                                |  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |  |

| Data Converters            | A/D 10x10b                                                            |  |

| Oscillator Type            | Internal                                                              |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |  |

| Mounting Type              | Surface Mount                                                         |  |

| Package / Case             | 48-LQFP                                                               |  |

| Supplier Device Package    | -                                                                     |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af52a8tax |  |

# List of figures

| Figure 1.  | STM8AF526x/8x/Ax and STM8AF6269/8x/Ax block diagram                                             | 12 |

|------------|-------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Flash memory organization of STM8A products                                                     |    |

| Figure 3.  | LQFP 80-pin pinout                                                                              |    |

| Figure 4.  | LQFP 64-pin pinout                                                                              |    |

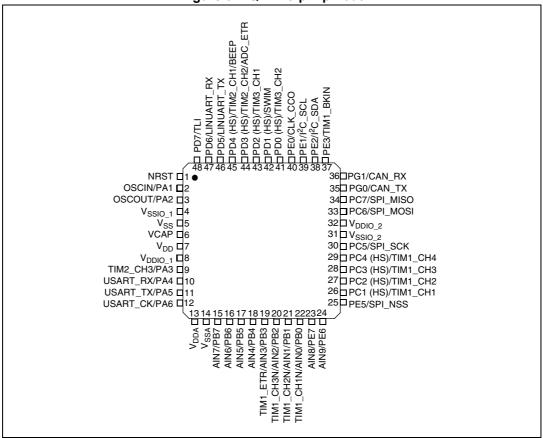

| Figure 5.  | LQFP 48-pin pinout                                                                              | 30 |

| Figure 6.  | STM8AF62xx LQFP/VFQFPN 32-pin pinout                                                            | 31 |

| Figure 7.  | STM8AF52x6 VFQFPN32 32-pin pinout                                                               | 32 |

| Figure 8.  | Register and memory map                                                                         |    |

| Figure 9.  | Pin loading conditions                                                                          |    |

| Figure 10. | Pin input voltage                                                                               |    |

| Figure 11. | fCPUmax versus VDD                                                                              |    |

| Figure 12. | External capacitor C <sub>EXT</sub>                                                             |    |

| Figure 13. | Typ. I <sub>DD(RUN)HSE</sub> vs. V <sub>DD</sub> @f <sub>CPU</sub> = 16 MHz, peripherals = on   | 67 |

| Figure 14. | Typ. $I_{DD(RUN)HSE}$ vs. $f_{CPU}$ @ $V_{DD}$ = 5.0 V, peripherals = on                        | 67 |

| Figure 15. | Typ. I <sub>DD(RUN)HSI</sub> vs. V <sub>DD</sub> @ f <sub>CPU</sub> = 16 MHz, peripherals = off | 67 |

| Figure 16. | Typ. I <sub>DD(WFI)HSE</sub> vs. V <sub>DD</sub> @ f <sub>CPU</sub> = 16 MHz, peripherals = on  | 67 |

| Figure 17. | Typ. I <sub>DD(WFI)HSE</sub> vs. f <sub>CPU</sub> @ V <sub>DD</sub> = 5.0 V, peripherals = on   | 67 |

| Figure 18. | Typ. I <sub>DD(WFI)HSI</sub> vs. V <sub>DD</sub> @ f <sub>CPU</sub> = 16 MHz, peripherals = off | 67 |

| Figure 19. | HSE external clock source                                                                       | 68 |

| Figure 20. | HSE oscillator circuit diagram                                                                  |    |

| Figure 21. | Typical HSI frequency vs V <sub>DD</sub>                                                        | 70 |

| Figure 22. | Typical LSI frequency vs V <sub>DD</sub>                                                        |    |

| Figure 23. | Typical V <sub>II</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ four temperatures              |    |

| Figure 24. | Typical pull-up resistance R <sub>PU</sub> vs V <sub>DD</sub> @ four temperatures               | 75 |

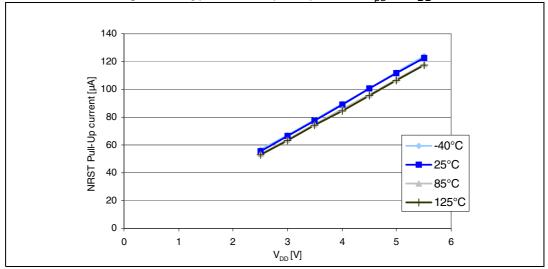

| Figure 25. | Typical pull-up current I <sub>pu</sub> vs V <sub>DD</sub> @ four temperatures <sup>(1)</sup>   |    |

| Figure 26. | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 $\stackrel{\checkmark}{V}$ (standard ports)                      |    |

| Figure 27. | Typ. $V_{OL}$ @ $V_{DD}$ = 5.0 V (standard ports)                                               | 76 |

| Figure 28. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 3.3 V (true open drain ports)                          | 76 |

| Figure 29. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 5.0 V (true open drain ports)                          | 76 |

| Figure 30. | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (high sink ports)                                              | 77 |

| Figure 31. | Typ. $V_{OL} @ V_{DD} = 5.0 \text{ V (high sink ports)}$                                        | 77 |

| Figure 32. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 3.3 V (standard ports)                                    | 77 |

| Figure 33. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 5.0 V (standard ports)                                    | 77 |

| Figure 34. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 3.3 V (high sink ports)                                   | 77 |

| Figure 35. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5.0 V$ (high sink ports)                                       | 77 |

| Figure 36. | Typical NRST V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ four temperatures         | 78 |

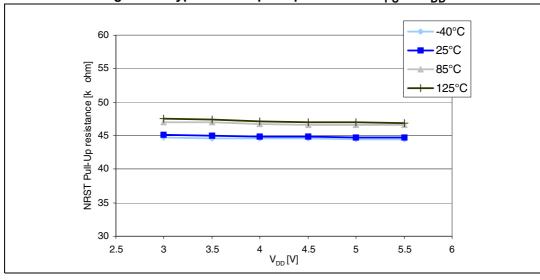

| Figure 37. | Typical NRST pull-up resistance R <sub>PU</sub> vs V <sub>DD</sub>                              | 79 |

| Figure 38. | Typical NRST pull-up current I <sub>pu</sub> vs V <sub>DD</sub>                                 | 79 |

| Figure 39. | Recommended reset pin protection                                                                | 80 |

| Figure 40. | SPI timing diagram in slave mode and with CPHA = 0                                              |    |

| Figure 41. | SPI timing diagram in slave mode and with CPHA = 1                                              | 82 |

| Figure 42. | SPI timing diagram - master mode                                                                | 83 |

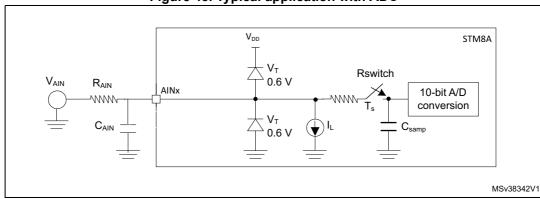

| Figure 43. | Typical application with ADC                                                                    | 85 |

| Figure 44. | ADC accuracy characteristics                                                                    |    |

| Figure 45. | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline                               | 90 |

| Figure 46. | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package                                       |    |

|            | recommended footprint                                                                           | 92 |

| Figure 47. | LQFP80 marking example (package top view)                                                       | 93 |

# 3 Product line-up

Table 2. STM8AF526x/8x/Ax product line-up with CAN

| Order code   | Package           | High<br>density<br>Flash<br>program<br>memory<br>(bytes) | RAM<br>(bytes) | Data<br>EEPROM<br>(bytes) | 10-bit<br>A/D<br>chan. | Timers<br>(IC/OC/PWM)                                     | Serial<br>interfaces                                  | I/0<br>wakeup<br>pins |

|--------------|-------------------|----------------------------------------------------------|----------------|---------------------------|------------------------|-----------------------------------------------------------|-------------------------------------------------------|-----------------------|

| STM8AF/P52AA | LQFP80            | 128 K                                                    |                |                           |                        |                                                           |                                                       | 68/37                 |

| STM8AF/P528A | (14x14)           | 64 K                                                     |                | 2 K                       |                        |                                                           |                                                       | 00/37                 |

| STM8AF/P52A9 | LOFP64            | 128 K                                                    |                | 2 K                       | 16                     | 1x8-bit: TIM4<br>3x16-bit: TIM1,<br>TIM2, TIM3<br>(9/9/9) | CAN,<br>LIN(UART),<br>SPI,<br>USART, I <sup>2</sup> C |                       |

| STM8AF/P5289 |                   | 64 K                                                     |                |                           |                        |                                                           |                                                       | 52/36                 |

| STM8AF/P5269 | (10/110)          | 32 K                                                     |                | 1 K                       |                        |                                                           |                                                       |                       |

| STM8AF/P52A8 |                   | 128 K                                                    | 6 K            | 21/                       |                        |                                                           |                                                       |                       |

| STM8AF/P5288 | LQFP48<br>(7x7)   | 64 K                                                     |                | 2 K 10                    |                        |                                                           | 38/35                                                 |                       |

| STM8AF/P5268 | (17.1)            | 32 K                                                     |                | 1K                        |                        |                                                           |                                                       |                       |

| STM8AF/P5286 |                   | 64 K                                                     |                |                           |                        | 1x8-bit: TIM4                                             | CAN,                                                  |                       |

| STM8AF/P52A6 | VFQFPN32<br>(5x5) | 128 K                                                    |                | 2 K                       | 2 K 6                  | 3x16-bit: TIM1,<br>TIM2, TIM3<br>(8/8/8)                  | LIN(UART),<br>I <sup>2</sup> C                        | 25/24                 |

Table 3. STM8AF6269/8x/Ax product line-up without CAN

| Order code   | Package           | High<br>density<br>Flash<br>program<br>memory<br>(bytes) | RAM<br>(bytes) | Data<br>EEPROM<br>(bytes) | 10-bit<br>A/D<br>chan. | Timers<br>(IC/OC/PWM)                                       | Serial<br>interfaces                          | I/0<br>wakeup<br>pins |                                  |            |       |

|--------------|-------------------|----------------------------------------------------------|----------------|---------------------------|------------------------|-------------------------------------------------------------|-----------------------------------------------|-----------------------|----------------------------------|------------|-------|

| STM8AF/P62AA | LQFP80            | 128 K                                                    |                |                           |                        |                                                             |                                               | 68/37                 |                                  |            |       |

| STM8AF/P628A | (14x14)           | 64 K                                                     |                | 2 K                       |                        | 6 1x8-bit: TIM4<br>3x16-bit: TIM1,<br>TIM2, TIM3<br>(9/9/9) | LIN(UART),<br>SPI,<br>USART, I <sup>2</sup> C | 00/37                 |                                  |            |       |

| STM8AF/P62A9 |                   | 128 K                                                    |                |                           | 16                     |                                                             |                                               |                       |                                  |            |       |

| STM8AF/P6289 | LQFP64<br>(10x10) | 64 K                                                     |                | 2 K                       |                        |                                                             |                                               | 52/36                 |                                  |            |       |

| STM8AF/P6269 | (*******)         | 32 K                                                     |                | 1 K                       |                        |                                                             |                                               |                       |                                  |            |       |

| STM8AF/P62A8 | LQFP48            | 128 K                                                    | 6 K            |                           | 10                     |                                                             |                                               | 38/35                 |                                  |            |       |

| STM8AF/P6288 | (7x7)             | (x7)                                                     |                |                           | 10                     |                                                             |                                               | 30/35                 |                                  |            |       |

| STM8AF/P6286 | LQFP32<br>(7x7)   | 64 K                                                     |                |                           |                        | 64 K                                                        | 2 K                                           | 7                     | 1x8-bit: TIM4<br>3x16-bit: TIM1, | LIN(UART), | 25/23 |

| STM8AF/P62A6 | VFQFPN32<br>(5x5) | 128 K                                                    |                |                           | TIM2, TIM3<br>(8/8/8)  | SPI, I <sup>2</sup> C                                       | 25/23                                         |                       |                                  |            |       |

## 5.5.3 128 kHz low-speed internal RC oscillator (LSI)

The frequency of this clock is 128 kHz and it is independent from the main clock. It drives the independent watchdog or the AWU wakeup timer.

In systems which do not need independent clock sources for the watchdog counters, the 128 kHz signal can be used as the system clock. This configuration has to be enabled by setting an option byte (OPT3/OPT3N, bit LSI\_EN).

### 5.5.4 24 MHz high-speed external crystal oscillator (HSE)

The external high-speed crystal oscillator can be selected to deliver the main clock in normal Run mode. It operates with quartz crystals and ceramic resonators.

- Frequency range: 1 MHz to 24 MHz

- Crystal oscillation mode: preferred fundamental

- I/Os: standard I/O pins multiplexed with OSCIN, OSCOUT

## 5.5.5 External clock input

An external clock signal can be applied to the OSCIN input pin of the crystal oscillator. The frequency range is 0 to 24 MHz.

## 5.5.6 Clock security system (CSS)

The clock security system protects against a system stall in case of an external crystal clock failure.

In case of a clock failure an interrupt is generated and the high-speed internal clock (HSI) is automatically selected with a frequency of 2 MHz (16 MHz/8).

**Control bit Peripheral** PCKEN17 TIM1 PCKEN16 TIM3 PCKEN15 TIM2 PCKFN14 TIM4 PCKEN13 LINUART PCKEN12 USART PCKEN11 SPI I<sup>2</sup>C PCKEN10

Table 4. Peripheral clock gating bits (CLK\_PCKENR1)

#### 5.7 **Timers**

#### 5.7.1 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications. The watchdog timer activity is controlled by the application program or option bytes. Once the watchdog is activated, it cannot be disabled by the user program without going through reset.

### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application timing perfectly. The application software must refresh the counter before time-out and during a limited time window. If the counter is refreshed outside this time window, a reset is issued.

### Independent watchdog timer

The independent watchdog peripheral can be used to resolve malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure. If the hardware watchdog feature is enabled through the device option bits, the watchdog is automatically enabled at power-on, and generates a reset unless the key register is written by software before the counter reaches the end of count.

#### 5.7.2 Auto-wakeup counter

This counter is used to cyclically wakeup the device in Active-halt mode. It can be clocked by the internal 128 kHz internal low-frequency RC oscillator or external clock.

LSI clock can be internally connected to TIM3 input capture channel 1 for calibration.

#### 5.7.3 Beeper

This function generates a rectangular signal in the range of 1, 2 or 4 kHz which can be output on a pin. This is useful when audible sounds without interference need to be generated for use in the application.

#### 5.7.4 Advanced control and general purpose timers

STM8A devices described in this datasheet, contain up to three 16-bit advanced control and general purpose timers providing nine CAPCOM channels in total. A CAPCOM channel can be used either as input compare, output compare or PWM channel. These timers are named TIM1, TIM2 and TIM3.

20/125 DocID14395 Rev 15

## 5.9.3 Serial peripheral interface (SPI)

The devices covered by this datasheet contain one SPI. The SPI is available on all the supported packages.

- Maximum speed: 10 Mbit/s or f<sub>MASTER</sub>/2 for master, 8 Mbit/s or f<sub>MASTER</sub> /2 for slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave mode/master mode management by hardware or software for both master and slave

- Programmable clock polarity and phase

- Programmable data order with MSB-first or LSB-first shifting

- · Dedicated transmission and reception flags with interrupt capability

- SPI bus busy status flag

- Hardware CRC feature for reliable communication:

- CRC value can be transmitted as last byte in Tx mode

- CRC error checking for last received byte

## 5.9.4 Inter integrated circuit (I<sup>2</sup>C) interface

The devices covered by this datasheet contain one I<sup>2</sup>C interface. The interface is available on all the supported packages.

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

- Status flags:

- Transmitter/receiver mode flag

- End-of-byte transmission flag

- I<sup>2</sup>C busy flag

- Error flags:

- Arbitration lost condition for master mode

- Acknowledgement failure after address/data transmission

- Detection of misplaced start or stop condition

- Overrun/underrun if clock stretching is disabled

## 5.10 Input/output specifications

The product features four I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitt-trigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

### Caution:

In STM8AF5286UC device, the following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software:

- configured as input with internal pull-up/down resistor,

- configured as output push-pull low.

Figure 5. LQFP 48-pin pinout

- 1. The CAN interface is only available on STM8AF52xx product lines.

- 2. HS stands for high sink capability.

57

Table 14. General hardware register map (continued)

| Address                   | Block                    | Register label | Register name                              | Reset<br>status     |

|---------------------------|--------------------------|----------------|--------------------------------------------|---------------------|

| 0x00 50C3                 |                          | CLK_CMSR       | Clock master status register               | 0xE1                |

| 0x00 50C4                 |                          | CLK_SWR        | Clock master switch register               | 0xE1                |

| 0x00 50C5                 |                          | CLK_SWCR       | Clock switch control register              | 0xXX                |

| 0x00 50C6                 |                          | CLK_CKDIVR     | Clock divider register                     | 0x18                |

| 0x00 50C7                 |                          | CLK_PCKENR1    | Peripheral clock gating register 1         | 0xFF                |

| 0x00 50C8                 | CLK                      | CLK_CSSR       | Clock security system register             | 0x00                |

| 0x00 50C9                 | <b>0 1</b> · ·           | CLK_CCOR       | Configurable clock control register        | 0x00                |

| 0x00 50CA                 |                          | CLK_PCKENR2    | Peripheral clock gating register 2         | 0xFF                |

| 0x00 50CB                 |                          |                | Reserved area (1 byte)                     |                     |

| 0x00 50CC                 |                          | CLK_HSITRIMR   | HSI clock calibration trimming register    | 0x00                |

| 0x00 50CD                 |                          | CLK_SWIMCCR    | SWIM clock control register                | 0bXXXX<br>XXX0      |

| 0x00 50CE<br>to 0x00 50D0 |                          | R              | eserved area (3 bytes)                     |                     |

| 0x00 50D1                 | WWDG                     | WWDG_CR        | WWDG control register                      | 0x7F                |

| 0x00 50D2                 | WWDG                     | WWDG_WR        | WWDR window register                       | 0x7F                |

| 0x00 50D3 to<br>0x00 50DF |                          | Re             | eserved area (13 bytes)                    |                     |

| 0x00 50E0                 |                          | IWDG_KR        | IWDG key register                          | 0xXX <sup>(2)</sup> |

| 0x00 50E1                 | IWDG                     | IWDG_PR        | IWDG prescaler register                    | 0x00                |

| 0x00 50E2                 |                          | IWDG_RLR       | IWDG reload register                       | 0xFF                |

| 0x00 50E3 to<br>0x00 50EF |                          | Re             | eserved area (13 bytes)                    |                     |

| 0x00 50F0                 |                          | AWU_CSR1       | AWU control/status register 1              | 0x00                |

| 0x00 50F1                 | AWU                      | AWU_APR        | AWU asynchronous prescaler buffer register | 0x3F                |

| 0x00 50F2                 |                          | AWU_TBR        | AWU timebase selection register            | 0x00                |

| 0x00 50F3                 | BEEP                     | BEEP_CSR       | BEEP control/status register               | 0x1F                |

| 0x00 50F4 to<br>0x00 50FF | Reserved area (12 bytes) |                |                                            |                     |

Table 14. General hardware register map (continued)

| Address                   | Block                    | Register label          | Register name                   | Reset<br>status |  |  |

|---------------------------|--------------------------|-------------------------|---------------------------------|-----------------|--|--|

| 0x00 5200                 |                          | SPI_CR1                 | SPI control register 1          | 0x00            |  |  |

| 0x00 5201                 |                          | SPI_CR2                 | SPI control register 2          | 0x00            |  |  |

| 0x00 5202                 |                          | SPI_ICR                 | SPI interrupt control register  | 0x00            |  |  |

| 0x00 5203                 | SPI                      | SPI_SR                  | SPI status register             | 0x02            |  |  |

| 0x00 5204                 | 581                      | SPI_DR                  | SPI data register               | 0x00            |  |  |

| 0x00 5205                 |                          | SPI_CRCPR               | SPI CRC polynomial register     | 0x07            |  |  |

| 0x00 5206                 |                          | SPI_RXCRCR              | SPI Rx CRC register             | 0xFF            |  |  |

| 0x00 5207                 |                          | SPI_TXCRCR              | SPI Tx CRC register             | 0xFF            |  |  |

| 0x00 5208 to<br>0x00 520F |                          | Reserved area (8 bytes) |                                 |                 |  |  |

| 0x00 5210                 |                          | I2C_CR1                 | I2C control register 1          | 0x00            |  |  |

| 0x00 5211                 |                          | I2C_CR2                 | I2C control register 2          | 0x00            |  |  |

| 0x00 5212                 |                          | I2C_FREQR               | I2C frequency register          | 0x00            |  |  |

| 0x00 5213                 |                          | I2C_OARL                | I2C own address register low    | 0x00            |  |  |

| 0x00 5214                 |                          | I2C_OARH                | I2C own address register high   | 0x00            |  |  |

| 0x00 5215                 |                          |                         |                                 |                 |  |  |

| 0x00 5216                 | I2C                      | I2C_DR                  | I2C data register               | 0x00            |  |  |

| 0x00 5217                 | 120                      | I2C_SR1                 | I2C status register 1           | 0x00            |  |  |

| 0x00 5218                 |                          | I2C_SR2                 | I2C status register 2           | 0x00            |  |  |

| 0x00 5219                 |                          | I2C_SR3                 | I2C status register 3           | 0x00            |  |  |

| 0x00 521A                 |                          | I2C_ITR                 | I2C interrupt control register  | 0x00            |  |  |

| 0x00 521B                 |                          | I2C_CCRL                | I2C clock control register low  | 0x00            |  |  |

| 0x00 521C                 |                          | I2C_CCRH                | I2C clock control register high | 0x00            |  |  |

| 0x00 521D                 |                          | I2C_TRISER              | I2C TRISE register              | 0x02            |  |  |

| 0x00 521E to<br>0x00 522F | Reserved area (18 bytes) |                         |                                 |                 |  |  |

Table 29. Programming current consumption

| Symbol                | Parameter           | Conditions                                                                                          | Тур | Max | Unit |

|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------|-----|-----|------|

| I <sub>DD(PROG)</sub> | Programming current | V <sub>DD</sub> = 5 V, -40 °C to 150 °C, erasing<br>and programming data or Flash<br>program memory | 1.0 | 1.7 | mA   |

Table 30. Typical peripheral current consumption  $V_{DD} = 5.0 V^{(1)}$

| Symbol                          | Parameter                                         | Typ.<br>f <sub>master</sub> = 2 MHz | Typ.<br>f <sub>master</sub> = 16 MHz | Typ.<br>f <sub>master</sub> =24 MHz | Unit |

|---------------------------------|---------------------------------------------------|-------------------------------------|--------------------------------------|-------------------------------------|------|

| I <sub>DD(TIM1)</sub>           | TIM1 supply current <sup>(2)</sup>                | 0.03                                | 0.23                                 | 0.34                                |      |

| I <sub>DD(TIM2)</sub>           | TIM2 supply current (2)                           | 0.02                                | 0.12                                 | 0.19                                |      |

| I <sub>DD(TIM3)</sub>           | TIM3 supply current <sup>(2)</sup>                | 0.01                                | 0.1                                  | 0.16                                |      |

| I <sub>DD(TIM4)</sub>           | TIM4 supply current <sup>(2)</sup>                | 0.004                               | 0.03                                 | 0.05                                |      |

| I <sub>DD(USART)</sub>          | USART supply current <sup>(2)</sup>               | 0.03                                | 0.09                                 | 0.15                                |      |

| I <sub>DD(LINUART)</sub>        | LINUART supply current <sup>(2)</sup>             | 0.03                                | 0.11                                 | 0.18                                |      |

| I <sub>DD(SPI)</sub>            | SPI supply current <sup>(2)</sup>                 | 0.01                                | 0.04                                 | 0.07                                | mA   |

| I <sub>DD(I<sup>2</sup>C)</sub> | I <sup>2</sup> C supply current <sup>(2)</sup>    | 0.02                                | 0.06                                 | 0.91                                |      |

| I <sub>DD(CAN)</sub>            | CAN supply current <sup>(3)</sup>                 | 0.06                                | 0.30                                 | 0.40                                |      |

| I <sub>DD(AWU)</sub>            | AWU supply current <sup>(2)</sup>                 | 0.003                               | 0.02                                 | 0.05                                |      |

| I <sub>DD(TOT_DIG)</sub>        | All digital peripherals on                        | 0.22                                | 1                                    | 2.4                                 |      |

| I <sub>DD(ADC)</sub>            | ADC supply current when converting <sup>(4)</sup> | 0.93                                | 0.95                                 | 0.96                                |      |

Typical values not tested in production. Since the peripherals are powered by an internally regulated, constant digital supply voltage, the values are similar in the full supply voltage range.

66/125 DocID14395 Rev 15

<sup>2.</sup> Data based on a differential I<sub>DD</sub> measurement between no peripheral clocked and a single active peripheral. This measurement does not include the pad toggling consumption.

<sup>3.</sup> Data based on a differential IDD measurement between reset configuration (CAN disabled) and a permanent CAN data transmit sequence in loopback mode at 1 MHz. This measurement does not include the pad toggling consumption.

<sup>4.</sup> Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions.

Figure 37. Typical NRST pull-up resistance R<sub>PU</sub> vs V<sub>DD</sub>

The reset network shown in *Figure 39* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below V<sub>IL(NRST)</sub> max (see *Table 39: NRST pin characteristics*), otherwise the reset is not taken into account internally.

For power consumption sensitive applications, the external reset capacitor value can be reduced to limit the charge/discharge current. If NRST signal is used to reset external circuitry, attention must be taken to the charge/discharge time of the external capacitor to fulfill the external devices reset timing conditions. Minimum recommended capacity is 10 nF.

## 10.3.11 10-bit ADC characteristics

Subject to general operating conditions for  $V_{DDA}$ ,  $f_{MASTER}$  and  $T_A$  unless otherwise specified.

| Symbol                        | Parameter                                   | Conditions                                | Min               | Тур  | Max               | Unit    |  |

|-------------------------------|---------------------------------------------|-------------------------------------------|-------------------|------|-------------------|---------|--|

| f <sub>ADC</sub>              | ADC clock frequency                         | -                                         | 111 kHz           | -    | 4 MHz             | kHz/MHz |  |

| V <sub>DDA</sub>              | Analog supply                               | -                                         | 3                 | -    | 5.5               |         |  |

| V <sub>REF+</sub>             | Positive reference voltage                  | -                                         | 2.75              | -    | $V_{DDA}$         |         |  |

| V <sub>REF-</sub>             | Negative reference voltage                  | -                                         | $V_{SSA}$         | -    | 0.5               | V       |  |

|                               |                                             | -                                         | $V_{SSA}$         | -    | $V_{DDA}$         | -       |  |

| V <sub>AIN</sub> Co           | Conversion voltage range <sup>(1)</sup>     | Devices with external V <sub>REF+</sub> / | V <sub>REF-</sub> | -    | V <sub>REF+</sub> |         |  |

| C <sub>samp</sub>             | Internal sample and hold capacitor          | -                                         | -                 | -    | 3                 | pF      |  |

| t <sub>S</sub> <sup>(1)</sup> | Sampling time                               | f <sub>ADC</sub> = 2 MHz                  | -                 | 1.5  | -                 |         |  |

| is                            | (3 x 1/f <sub>ADC</sub> )                   | f <sub>ADC</sub> = 4 MHz                  | -                 | 0.75 | -                 |         |  |

| +.                            | Wakeup time from standby                    | f <sub>ADC</sub> = 2 MHz                  | -                 | 7    | -                 | μs      |  |

| t <sub>STAB</sub>             | wakeup time nom standby                     | f <sub>ADC</sub> = 4 MHz                  | -                 | 3.5  | -                 |         |  |

|                               | Total conversion time including             | f <sub>ADC</sub> = 2 MHz                  | -                 | 7    | -                 |         |  |

| t <sub>CONV</sub>             | sampling time<br>(14 x 1/f <sub>ADC</sub> ) | f <sub>ADC</sub> = 4 MHz                  | -                 | 3.5  | -                 |         |  |

| R <sub>switch</sub>           | Equivalent switch resistance                | -                                         | -                 | -    | 30                | kΩ      |  |

**Table 43. ADC characteristics**

During the sample time, the sampling capacitance, C<sub>samp</sub> (3 pF typ), can be charged/discharged by the

external source. The internal resistance of the analog source must allow the capacitance to reach its final

voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no

effect on the conversion result.

Figure 43. Typical application with ADC

1. Legend:  $R_{AIN}$  = external resistance,  $C_{AIN}$  = capacitors,  $C_{samp}$  = internal sample and hold capacitor.

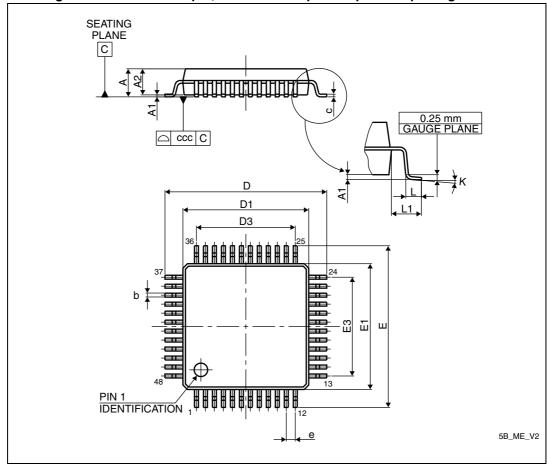

## 11.3 LQFP48 package information

Figure 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

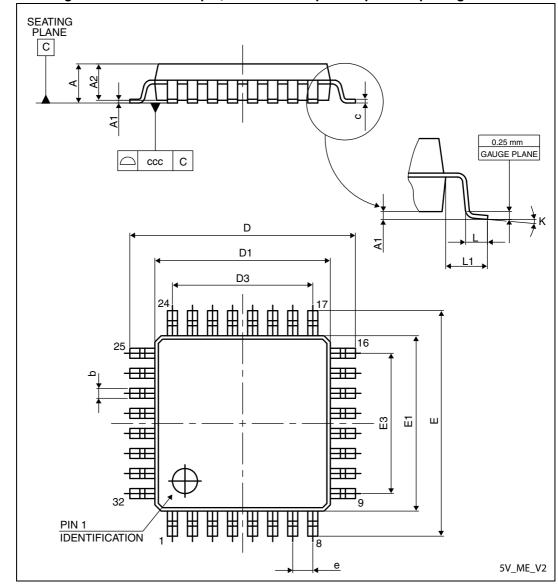

## 11.4 LQFP32 package information

Figure 54. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

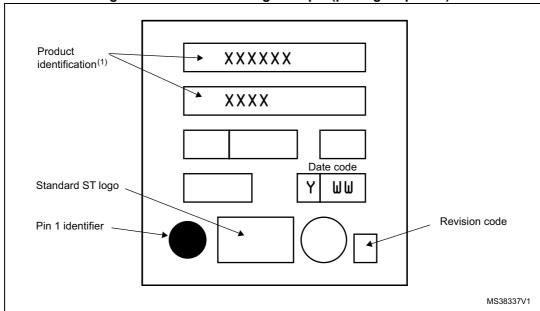

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 56. LQFP32 marking example (package top view)

1. Parts marked as "ES","E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.

104/125 DocID14395 Rev 15

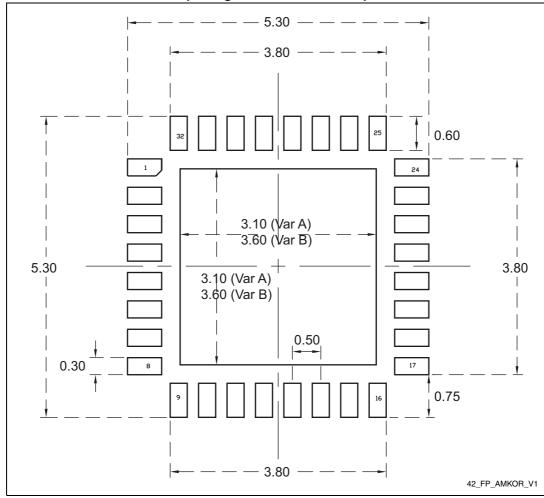

Figure 58. VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

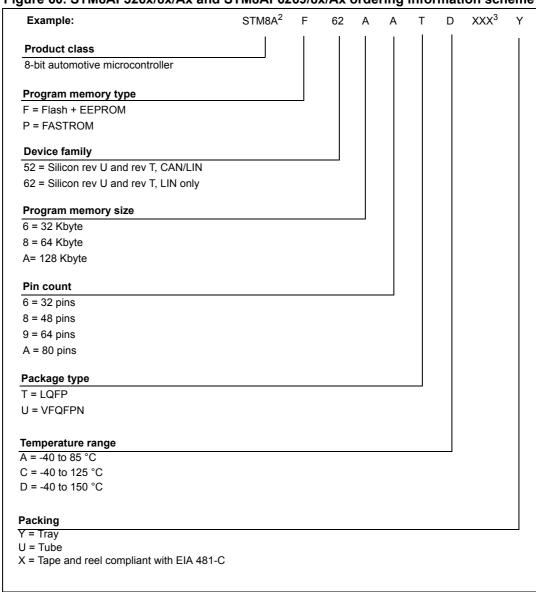

## 12 Ordering information

- For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to www.st.com or contact the nearest ST Sales Office.

- Qualified and characterized according to AEC Q100 and Q003 or equivalent, advanced screening according to AEC Q001 and Q002 or equivalent.

- Customer specific FASTROM code or custom device configuration. This field shows 'SSS' if the device contains a super set silicon, usually equipped with bigger memory and more I/Os. This silicon is supposed to be replaced later by the target silicon.

# 14 Revision history

Table 55. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-Jan-2008 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22-Aug-2008 | 2        | Added 'H' products to the datasheet (Flash no EEPROM).  Section: Features on cover page: Updated Memories, Reset and supply management, Communication interfaces and I/Os; reduced wakeup pins by 1.  Table 1: Device summary: Removed STM8AF6168, STM8AF6148, STM8AF6166, STM8AF6146, STM8AF5166, STM8AF5176, and STM8AF5166.  Section 1: Introduction, Section 5: Product overview, Section 9: Option bytes, Section 6.2: Alternate function remapping, Table 21: Current characteristics: Updated reference documentation: RM0009, PM0047, and UM0470.  Section 2: Description: added information about peak performance. Section 3: Product line-up: Removed STM8A common features table.  Table 4: Peripheral clock gating bits (CLK_PCKENR1): Removed STM8AF5186T, STM8AF5176T, STM8AF5168T, and STM8AF5186T, STM8AF5176T, STM8AF5168T, and STM8AF6168T, STM8AF5166T, STM8AF6148T, and STM8AF6168T, STM8AF6166T, STM8AF6148T, and STM8AF6146T.  Section 5: Peripheral clock gating bits (CLK_PCKENR2): Removed STM8AF6146T.  Section 5: 5: Peripheral clock gating bits (CLK_PCKENR2): Removed STM8AF6146T.  Section 5: 5: Set kHz low-speed internal RC oscillator (LSI): Major modification, TMU included.  Section 5: 5: 2: 16 MHz high-speed internal RC oscillator (LSI): User trimming updated.  Section 5: 5: External clock input: Maximum frequency conditional 32 Kbyte/128 Kbyte.  Section 5: 5: External clock input: Maximum frequency conditional 32 Kbyte/128 Kbyte.  Section 5: 8: Analog to digital converter (ADC): Scan for 128 Kbyte removed.  Section 5: 8: Analog to digital converter (ADC): Scan for 128 Kbyte removed.  Section 5: 8: Analog to digital converter (ADC): Scan for 128 Kbyte removed.  Section 5: 9: Communication interfaces, Section 5: 9:3: Serial peripheral interface (SPI): SPI 10 Mb/s.  Figure 3: LQFP 80-pin pinout, Figure 4: LQFP 64-pin pinout, Figure 6: STM8AF62xx LQFP/VFQFPN 32-pin pinout. Amended footnote 1.  Table 12: Memory model 128K: HS output changed from 20 mA to 8 mA.  Section 7: 3: Supply current characteristics Note on typical/WC values adde |

Table 55. Document revision history (continued)

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Aug-2008 | 2<br>(continued) | Table 18: Typ. IDD(WFI)HSI vs. VDD @ fCPU = 16 MHz, peripherals = off: Replaced the source blocks 'simple USART', 'very low-end timer (timer 4)', and 'EEPROM' with 'LINUART', 'timer4' and 'reserved' respectively, added TMU registers.  Table 20: HSE oscillator circuit diagram: Updated OPT6 and NOPT6, added OPT7 to 17 (TMU, BL)  Table 21: Typical HSI frequency vs VDD: Updated OPT1 UBC[7:0], OPT4 CKAWUSEL, OPT4 PRSC [1:0], and OPT6, added OPT7 to 16 (TMU).  Table 23: Operating lifetime: Amended footnotes.  Table 23: Operating lifetime: Amended footnotes.  Table 26: Total current consumption in Run, Wait and Slow mode. General conditions for VDD apply, TA = -40 °C to 150 °C: Added parameter 'voltage and current operating conditions'.  Table 27: Total current consumption in Halt and Active-halt modes. General conditions for VDD applied. TA = -40 °C to 55 °C unless otherwise stated: Amended footnotes.  Table 28: Oscillator current consumption: Replaced.  Table 29: Programming current consumption: Amended maximum data and footnotes.  Table 21: Current characteristics: Replaced.  Table 22: Thermal characteristics: Added and amended I <sub>DD(RUN)</sub> data; amended I <sub>DDWFI</sub> data; amended footnotes.  Table 32: HSE oscillator characteristics: Filled in, amended maximum data and footnotes.  Figure 13 to Figure 18: info on peripheral activity added.  Table 33: HSI oscillator characteristics: Modified f <sub>HSE_ext</sub> data and added V <sub>HSEdnl</sub> data.  Table 35: Flash program memory/data EEPROM memory: Removed ACC <sub>HSI</sub> parameters and replaced with ACC <sub>HS</sub> parameters; amended data and footnotes.  Table 37: Data memory: Updated names and data of N <sub>RW</sub> and t <sub>RET</sub> parameters.  Table 40: TIM 1, 2, 3, and 4 electrical specifications: Added V <sub>OH</sub> and V <sub>OL</sub> parameters; Updated I <sub>lkg ana</sub> parameter.  Removed: Output driving current (standard ports), Output driving current (frue open drain ports), and Output driving current (high sink ports).  Table 40: EMI data: Updated f <sub>ADC</sub> , t <sub>S</sub> , and t <sub>CONV</sub> data.  Table: ADC accuracy for VDDA = 3.3 V: removed th |

Table 55. Document revision history (continued)

| Date        | Revision          | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-Mar-2014 | 10<br>(continued) | Added:  - Figure 7: STM8AF52x6 VFQFPN32 32-pin pinout;  - the caution in Section 5.10: Input/output specifications,  - The table footnote "Not recommended for new designs" to Table:  STM8AF/H/P51xx product line-up with CAN and Table:  STM8AF/H/P61xx product line-up without CAN.  - The figure footnotes to Figure 7: STM8AF52x6 VFQFPN32 32-pin pinout and Figure: VFQFPN 32-lead very thin fine pitch quad flat no-lead package (5 x 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13-Jun-2014 | 11                | Added STM8AF52A6 part number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 09-Jun-2015 | 12                | Added:  - the third table footnote to Table 25: Operating conditions at power-up/power-down,  - Figure 47: LQFP80 marking example (package top view),  - Figure 50: LQFP64 marking example (package top view),  - Figure 53: LQFP48 marking example (package top view),  - Figure 56: LQFP32 marking example (package top view),  - Figure 59: VFQFPN32 marking example (package top view),  - the footnote about the device marking to Figure 60:  STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information scheme1.  Removed STM8AF51xx and STM8AF61xx obsolete root part numbers, and consequently "H" products:  - Table 1: Device summary,  - Section 1: Introduction,  - Section 2: Description,  - Section 3: Product line-up,  - Table 12: Memory model 128K,  - Section 10.3: Operating conditions,  - Figure 60: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information scheme1.  Moved Section 11.6: Thermal characteristics to Section 11: Package information.  Updated:  - the product naming in the document headers and captions,  - the standard reference for EMI characteristics in Table 46: EMI data. |

| 13-Jun-2016 | 13                | Updated Table 53: VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package mechanical data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |