Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af52a9tcx |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Introduction

This datasheet refers to the STM8AF526x/8x/Ax and STM8AF6269/8x/Ax products with 32 to 128 Kbyte of program memory.

In the order code, the letter 'F' refers to product versions with Flash and data EEPROM and 'P' to product versions with FASTROM. The identifiers 'F' and 'P' do not coexist in a given order code.

The datasheet contains the description of family features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8A microcontroller memory, registers and peripherals, please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8S and STM8A Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

# 2 Description

The STM8AF526x/8x/Ax and STM8AF6269/8x/Ax automotive 8-bit microcontrollers described in this datasheet offer from 32 Kbyte to 128 Kbyte of non volatile memory and integrated true data EEPROM. They are referred to as high density STM8A devices in STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

The STM8AF52 series features a CAN interface.

All devices of the STM8A product line provide the following benefits: reduced system cost, performance and robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, wtachdog, and brown-out reset.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map, and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8A family thanks to their advanced core which is made in a state-of-the art technology for automotive applications with 3.3 V to 5.5 V operating supply.

All STM8A and ST7 microcontrollers are supported by the same tools including STVD/STVP development environment, the STice emulator and a low-cost, third party incircuit debugging tool.

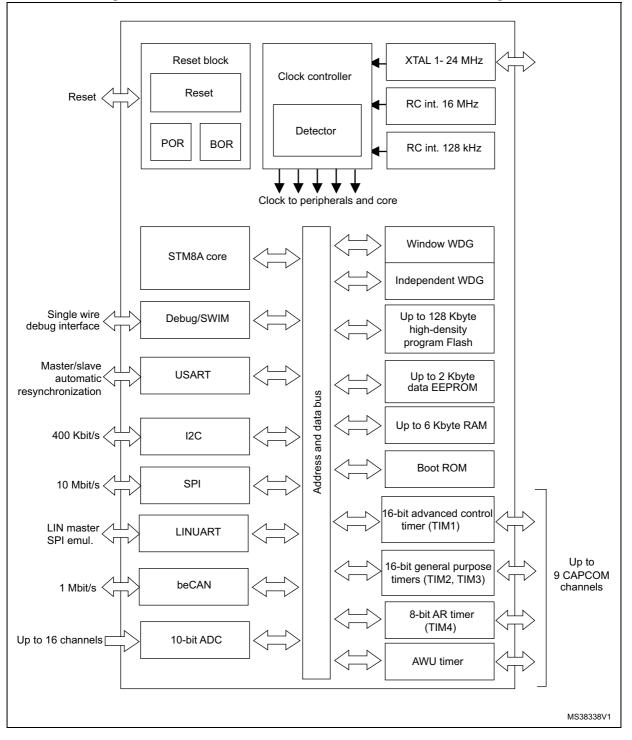

# 4 Block diagram

Figure 1. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax block diagram

DocID14395 Rev 15

### 5.5.3 128 kHz low-speed internal RC oscillator (LSI)

The frequency of this clock is 128 kHz and it is independent from the main clock. It drives the independent watchdog or the AWU wakeup timer.

In systems which do not need independent clock sources for the watchdog counters, the 128 kHz signal can be used as the system clock. This configuration has to be enabled by setting an option byte (OPT3/OPT3N, bit LSI\_EN).

### 5.5.4 24 MHz high-speed external crystal oscillator (HSE)

The external high-speed crystal oscillator can be selected to deliver the main clock in normal Run mode. It operates with quartz crystals and ceramic resonators.

- Frequency range: 1 MHz to 24 MHz

- Crystal oscillation mode: preferred fundamental

- I/Os: standard I/O pins multiplexed with OSCIN, OSCOUT

#### 5.5.5 External clock input

An external clock signal can be applied to the OSCIN input pin of the crystal oscillator. The frequency range is 0 to 24 MHz.

#### 5.5.6 Clock security system (CSS)

The clock security system protects against a system stall in case of an external crystal clock failure.

In case of a clock failure an interrupt is generated and the high-speed internal clock (HSI) is automatically selected with a frequency of 2 MHz (16 MHz/8).

| ······································ |                  |  |  |  |  |  |  |  |

|----------------------------------------|------------------|--|--|--|--|--|--|--|

| Control bit                            | Peripheral       |  |  |  |  |  |  |  |

| PCKEN17                                | TIM1             |  |  |  |  |  |  |  |

| PCKEN16                                | TIM3             |  |  |  |  |  |  |  |

| PCKEN15                                | TIM2             |  |  |  |  |  |  |  |

| PCKEN14                                | TIM4             |  |  |  |  |  |  |  |

| PCKEN13                                | LINUART          |  |  |  |  |  |  |  |

| PCKEN12                                | USART            |  |  |  |  |  |  |  |

| PCKEN11                                | SPI              |  |  |  |  |  |  |  |

| PCKEN10                                | l <sup>2</sup> C |  |  |  |  |  |  |  |

#### Table 4. Peripheral clock gating bits (CLK\_PCKENR1)

### 5.10 Input/output specifications

The product features four I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

- Caution: In STM8AF5286UC device, the following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor,

- configured as output push-pull low.

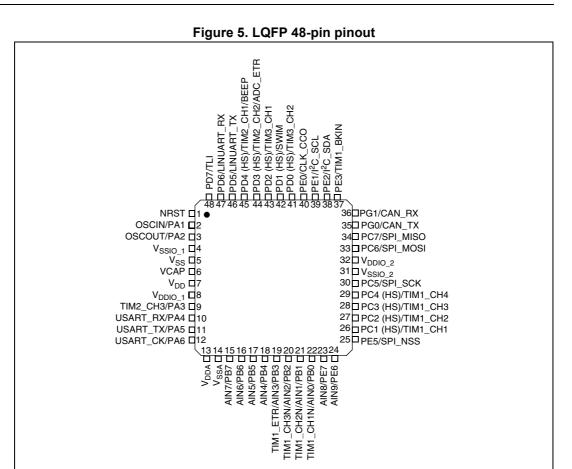

1. The CAN interface is only available on STM8AF52xx product lines.

2. HS stands for high sink capability.

|        | Pir    |        | mber                          |                     | WOAF 5202/02/A    |      |          | npu |                | -         | Out   |    |    |                                      | (*******                           | ,                                                    |

|--------|--------|--------|-------------------------------|---------------------|-------------------|------|----------|-----|----------------|-----------|-------|----|----|--------------------------------------|------------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | STM8AF62xx<br>LQFP32/VFQFPN32 | STM8AF52x6 VFQFPN32 | Pin name          | Type | Floating | Mpu | Ext. interrupt | High sink | Speed | OD | ЬР | Main<br>function<br>(after<br>reset) | Default<br>alternate<br>function   | Alternate<br>function<br>after remap<br>[option bit] |

| 22     | 18     | -      | -                             | -                   | V <sub>REF+</sub> | s    | -        | -   | -              | -         | -     | -  | -  | ADC positive<br>reference<br>voltage |                                    | -                                                    |

| 23     | 19     | 13     | 9                             | 9                   | V <sub>DDA</sub>  | S    | -        | -   | -              | -         | -     | -  | -  | Analog power supply                  |                                    | -                                                    |

| 24     | 20     | 14     | 10                            | 10                  | V <sub>SSA</sub>  | S    | -        | -   | -              | -         | -     | -  | -  | -                                    | g ground                           | -                                                    |

| 25     | 21     | -      | -                             | -                   | V <sub>REF-</sub> | S    | -        | -   | -              | -         | -     | -  | -  | ADC negative<br>reference voltage    |                                    | -                                                    |

| 26     | 22     | -      | -                             | -                   | PF0/AIN10         | I/O  | x        | х   | -              | -         | 01    | х  | х  | Port F0 Analog<br>input 10           |                                    | -                                                    |

| 27     | 23     | 15     | -                             | -                   | PB7/AIN7          | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port B7                              | Analog<br>input 7                  | -                                                    |

| 28     | 24     | 16     | -                             | -                   | PB6/AIN6          | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port B6                              | Analog<br>input 6                  | -                                                    |

| 29     | 25     | 17     | 11                            | 11                  | PB5/AIN5          | I/O  | x        | х   | х              | -         | 01    | х  | x  | Port B5                              | Analog<br>input 5                  | I <sup>2</sup> C_SDA<br>[AFR6]                       |

| 30     | 26     | 18     | 12                            | 12                  | PB4/AIN4          | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port B4                              | Analog<br>input 4                  | I <sup>2</sup> C_SCL<br>[AFR6]                       |

| 31     | 27     | 19     | 13                            | 13                  | PB3/AIN3          | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port B3                              | Analog<br>input 3                  | TIM1_ETR<br>[AFR5]                                   |

| 32     | 28     | 20     | 14                            | 14                  | PB2/AIN2          | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port B2                              | Analog<br>input                    | TIM1_CH3N<br>[AFR5]                                  |

| 33     | 29     | 21     | 15                            | 15                  | PB1/AIN1          | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port B1                              | Analog<br>input 1                  | TIM1_CH2N<br>[AFR5]                                  |

| 34     | 30     | 22     | 16                            | 16                  | PB0/AIN0          | I/O  | x        | х   | х              | -         | 01    | х  | х  | Port B0                              | Analog<br>input 0                  | TIM1_CH1N<br>[AFR5]                                  |

| 35     | -      | -      | -                             | -                   | PH4/TIM1_ETR      | I/O  | x        | х   | -              | -         | 01    | х  | x  | Port H4                              | Timer 1 -<br>trigger<br>input      | -                                                    |

| 36     | -      | -      | -                             | -                   | PH5/<br>TIM1_CH3N | I/O  | x        | х   | -              | -         | 01    | х  | x  | Port H5                              | Timer 1 -<br>inverted<br>channel 3 | -                                                    |

| 37     | -      | -      | -                             | -                   | PH6/<br>TIM1_CH2N | I/O  | x        | x   | -              | -         | 01    | х  | x  | Port H6                              | Timer 1 -<br>inverted<br>channel 2 | -                                                    |

| Table 11. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax p | oin description (conti | nued) |

|---------------------------------------------------|------------------------|-------|

|                                                   |                        |       |

## 6.2 Alternate function remapping

As shown in the rightmost column of *Table 11*, some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function remap) option bits. Refer to *Section 9: Option bytes on page 54*. When the remapping option is active, the default alternate function is no longer available.

To use an alternate function, the corresponding peripheral must be enabled in the peripheral registers.

Alternate function remapping does not effect GPIO capabilities of the I/O ports (see the GPIO section of STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016).

| Flash program<br>memory size | Flash program<br>memory end<br>address | RAM size | RAM end<br>address | Stack roll-over<br>address |  |

|------------------------------|----------------------------------------|----------|--------------------|----------------------------|--|

| 128 K                        | 0x00 27FFF                             |          |                    |                            |  |

| 64 K                         | 0x00 17FFF                             | 6 K      | 0x00 17FF          | 0x00 1400                  |  |

| 32 K                         | 0x00 0FFFF                             |          |                    |                            |  |

Table 12. Memory model 128K

## 7.2 Register map

In this section the memory and register map of the devices covered by this datasheet is described. For a detailed description of the functionality of the registers, refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016.

| Address   | Block  | Register label | Register name                     | Reset<br>status     |

|-----------|--------|----------------|-----------------------------------|---------------------|

| 0x00 5000 |        | PA_ODR         | Port A data output latch register | 0x00                |

| 0x00 5001 |        | PA_IDR         | Port A input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5002 | Port A | PA_DDR         | Port A data direction register    | 0x00                |

| 0x00 5003 |        | PA_CR1         | Port A control register 1         | 0x00                |

| 0x00 5004 |        | PA_CR2         | Port A control register 2         | 0x00                |

| 0x00 5005 |        | PB_ODR         | Port B data output latch register | 0x00                |

| 0x00 5006 |        | PB_IDR         | Port B input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5007 | Port B | PB_DDR         | Port B data direction register    | 0x00                |

| 0x00 5008 |        | PB_CR1         | Port B control register 1         | 0x00                |

| 0x00 5009 |        | PB_CR2         | Port B control register 2         | 0x00                |

| 0x00 500A |        | PC_ODR         | Port C data output latch register | 0x00                |

| 0x00 500B |        | PB_IDR         | Port C input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 500C | Port C | PC_DDR         | Port C data direction register    | 0x00                |

| 0x00 500D |        | PC_CR1         | Port C control register 1         | 0x00                |

| 0x00 500E |        | PC_CR2         | Port C control register 2         | 0x00                |

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00                |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00                |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x02                |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00                |

Table 13. I/O port hardware register map

| Address                   | Block | Register label                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Register name                          | Reset<br>status |  |

|---------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|--|

| 0x00 5320                 |       | TIM3_CR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TIM3 control register 1                | 0x00            |  |

| 0x00 5321                 |       | TIM3_IER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TIM3 interrupt enable register         | 0x00            |  |

| 0x00 5322                 |       | TIM3_CR1<br>TIM3_IER<br>TIM3_SR1<br>TIM3_SR2<br>TIM3_EGR<br>TIM3_CCMR1<br>TIM3_CCMR1<br>TIM3_CCR11<br>TIM3_CCR11<br>TIM3_CNTRH<br>TIM3_CNTRH<br>TIM3_CNTRL<br>TIM3_ARRH<br>TIM3_ARRH<br>TIM3_ARRH<br>TIM3_CCR1L<br>TIM3_CCR1L<br>TIM3_CCR1L<br>TIM3_CCR1L<br>TIM3_CCR1L<br>TIM3_CCR2H<br>TIM3_CCR2H<br>TIM3_CCR2H<br>TIM3_CCR2H<br>TIM3_CCR2H<br>TIM3_CCR2H<br>TIM3_CCR2L<br>Ref<br>TIM4_CR1<br>TIM4_IER<br>TIM4_EGR<br>TIM4_SR<br>TIM4_SR<br>TIM4_SR<br>TIM4_CNTR<br>TIM4_PSCR<br>TIM4_ARR | TIM3 status register 1                 | 0x00            |  |

| 0x00 5323                 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TIM3 status register 2                 | 0x00            |  |

| 0x00 5324                 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TIM3 event generation register         | 0x00            |  |

| 0x00 5325                 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TIM3 capture/compare mode register 1   | 0x00            |  |

| 0x00 5326                 |       | TIM3_CCMR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIM3 capture/compare mode register 2   | 0x00            |  |

| 0x00 5327                 |       | TIM3_CCER1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIM3 capture/compare enable register 1 | 0x00            |  |

| 0x00 5328                 | TIM3  | TIM3_CNTRH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIM3 counter high                      | 0x00            |  |

| 0x00 5329                 |       | TIM3_CNTRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIM3 counter low                       | 0x00            |  |

| 0x00 532A                 |       | TIM3_PSCR TIM3 prescaler register                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |                 |  |

| 0x00 532B                 |       | TIM3_ARRH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TIM3 auto-reload register high         | 0xFF            |  |

| 0x00 532C                 |       | TIM3_ARRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TIM3 auto-reload register low          | 0xFF            |  |

| 0x00 532D                 |       | TIM3_CCR1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIM3 capture/compare register 1 high   | 0x00            |  |

| 0x00 532E                 |       | TIM3_CCR1L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIM3 capture/compare register 1 low    | 0x00            |  |

| 0x00 532F                 |       | TIM3_CCR2H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIM3 capture/compare register 2 high   | 0x00            |  |

| 0x00 5330                 |       | TIM3_SR1         TIM3_SR2         TIM3_EGR         TIM3_CCMR1         TIM3_CCMR2         TIM3_CCMR1         TIM3_CCMR1         TIM3_CCR1         TIM3_RRL         TIM3_CCR1H         TIM3_CCR1H         TIM3_CCR1L         TIM3_CCR1L         TIM3_CCR1L         TIM3_CCR1L         TIM3_CCR2H         TIM3_CCR2L         FIM3_CCR2L         TIM3_CCR2L         TIM3_CCR2L         TIM4_ER         TIM4_SR         TIM4_PSCR         TIM4_ARR                                               | TIM3 capture/compare register 2 low    | 0x00            |  |

| 0x00 5331 to<br>0x00 533F |       | Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | eserved area (15 bytes)                |                 |  |

| 0x00 5340                 |       | TIM4_CR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TIM4 control register 1                | 0x00            |  |

| 0x00 5341                 |       | TIM4_IER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TIM4 interrupt enable register         | 0x00            |  |

| 0x00 5342                 |       | TIM4_SR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TIM4 status register                   | 0x00            |  |

| 0x00 5343                 | TIM4  | TIM3_CNTRH         TIM3_CNTRL         TIM3_PSCR         TIM3_ARRH         TIM3_CCR1H         TIM3_CCR1L         TIM3_CCR1L         TIM3_CCR2H         TIM3_CCR2H         TIM3_CCR2H         TIM3_CCR2L         TIM3_CCR2L         TIM4_CR1         TIM4_EGR         TIM4_PSCR         TIM4_ARR                                                                                                                                                                                              | TIM4 event generation register         | 0x00            |  |

| 0x00 5344                 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TIM4 counter                           | 0x00            |  |

| 0x00 5345                 |       | TIM4_PSCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TIM4 prescaler register                | 0x00            |  |

| 0x00 5346                 |       | TIM4_ARR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TIM4 auto-reload register              | 0xFF            |  |

| 0x00 5347 to<br>0x00 53FF |       | Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | served area (185 bytes)                |                 |  |

Table 14. General hardware register map (continued)

# 9 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated block of the memory. Each option byte has to be stored twice, for redundancy, in a regular form (OPTx) and a complemented one (NOPTx), except for the ROP (read-out protection) option byte and option bytes 8 to 16.

Option bytes can be modified in ICP mode (via SWIM) by accessing the EEPROM address shown in *Table 18: Option bytes* below.

Option bytes can also be modified 'on the fly' by the application in IAP mode, except the ROP and UBC options that can only be changed in ICP mode (via SWIM).

Refer to the STM8 Flash programming manual (PM0047) and STM8 SWIM communication protocol and debug module user manual (UM0470) for information on SWIM programming procedures.

| Addr.        | Option                          | Option<br>byte<br>no. | Option bits |             |       |       |             |               |              |               |                    |  |

|--------------|---------------------------------|-----------------------|-------------|-------------|-------|-------|-------------|---------------|--------------|---------------|--------------------|--|

| Auur.        | name                            |                       | 7           | 6           | 5     | 4     | 3           | 2             | 1            | 0             | default<br>setting |  |

| 0x00<br>4800 | Read-out<br>protection<br>(ROP) | OPT0                  |             | ROP[7:0]    |       |       |             |               |              |               |                    |  |

| 0x00<br>4801 | User boot<br>code               | OPT1                  |             | UBC[7:0]    |       |       |             |               |              |               |                    |  |

| 0x00<br>4802 | (UBC)                           | NOPT1                 |             | NUBC[7:0]   |       |       |             |               |              |               |                    |  |

| 0x00<br>4803 | Alternate function              | OPT2                  | AFR7        | AFR6        | AFR5  | AFR4  | AFR3        | AFR2          | AFR1         | AFR0          | 0x00               |  |

| 0x00<br>4804 | remapping<br>(AFR)              | NOPT2                 | NAFR7       | NAFR6       | NAFR5 | NAFR4 | NAFR3       | NAFR2         | NAFR1        | NAFR0         | 0xFF               |  |

| 0x00<br>4805 | Watchdog                        | OPT3                  |             | Rese        | erved |       | LSI_<br>EN  | IWDG<br>_HW   | WWD<br>G_HW  | WWDG<br>_HALT | 0x00               |  |

| 0x00<br>4806 | option                          | NOPT3                 |             | Rese        | erved |       | NLSI_<br>EN | NIWD<br>G_HW  | NWWD<br>G_HW | NWWG<br>_HALT | 0xFF               |  |

| 0x00<br>4807 | Clock                           | OPT4                  |             | Rese        | erved |       | EXT<br>CLK  | CKAW<br>USEL  | PRSC1        | PRSC0         | 0x00               |  |

| 0x00<br>4808 | option                          | NOPT4                 |             | Reserved    |       |       |             | NCKAW<br>USEL | NPRSC1       | NPRSC<br>0    | 0xFF               |  |

| 0x00<br>4809 | HSE clock                       | OPT5                  |             | HSECNT[7:0] |       |       |             |               |              | 0x00          |                    |  |

| 0x00<br>480A | startup                         | NOPT5                 |             |             |       | NHSE  | ECNT[7:0    | ]             |              |               | 0xFF               |  |

#### Table 18. Option bytes

# **10** Electrical characteristics

### 10.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = -40$  °C,  $T_A = 25$  °C, and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production.

#### 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5.0$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

#### 10.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

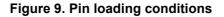

#### 10.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

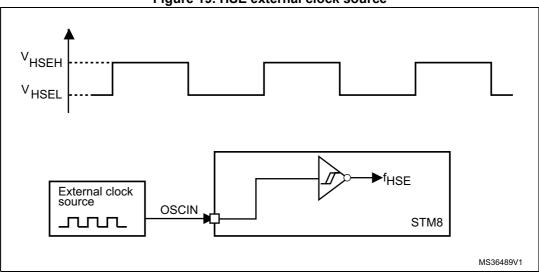

### **10.3.3** External clock sources and timing characteristics

#### **HSE external clock**

An HSE clock can be generated by feeding an external clock signal of up to 24 MHz to the OSCIN pin.

Clock characteristics are subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                               | Conditions                        | Min                   | Тур | Мах                   | Unit |

|-----------------------|-----------------------------------------|-----------------------------------|-----------------------|-----|-----------------------|------|

| f <sub>HSE_ext</sub>  | User external clock source<br>frequency | T <sub>A</sub> = -40 °C to 150 °C | 0 <sup>(1)</sup>      | -   | 24                    | MHz  |

| V <sub>HSEdHL</sub>   | Comparator hysteresis                   | -                                 | 0.1 x V <sub>DD</sub> | -   | -                     |      |

| V <sub>HSEH</sub>     | OSCIN high-level input pin voltage      | -                                 | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | V    |

| V <sub>HSEL</sub>     | OSCIN low-level input pin voltage       | -                                 | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> |      |

| I <sub>LEAK_HSE</sub> | OSCIN input leakage current             | $V_{SS} < V_{IN} < V_{DD}$        | -1                    | -   | +1                    | μA   |

Table 31. HSE external clock characteristics

1. If CSS is used, the external clock must have a frequency above 500 kHz.

#### Figure 19. HSE external clock source

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied using a crystal/ceramic resonator oscillator of up to 24 MHz. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

1. Dimensions are expressed in millimeters.

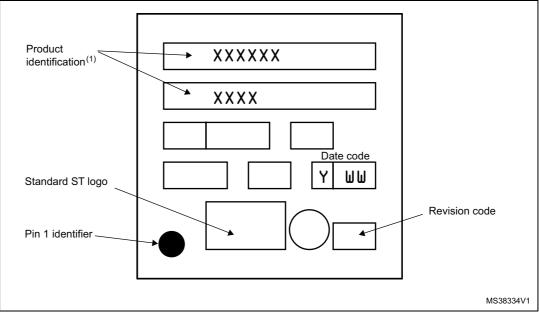

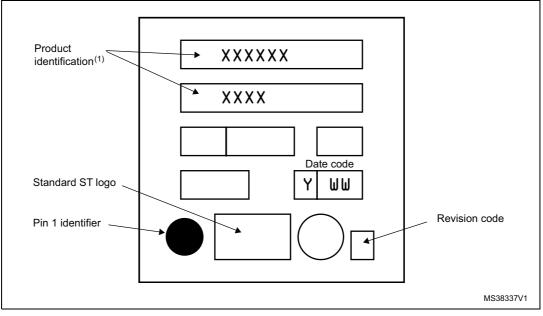

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 50. LQFP64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 56. LQFP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.

### **11.6.2** Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the order code (see *Figure 60: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information scheme1 on page 111*).

The following example shows how to calculate the temperature range needed for a given application.

Assuming the following application conditions:

- Maximum ambient temperature T<sub>Amax</sub> = 82 °C (measured according to JESD51-2)

- I<sub>DDmax</sub> = 8 mA

- V<sub>DD</sub> = 5 V

- maximum 20 I/Os used at the same time in output at low-level with  $I_{OL}$  = 8 mA

P<sub>INTmax</sub> = 8 mA x 5 V = 400 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives:

$P_{INTmax}$  = 400 mW and  $P_{IOmax}$  64 mW  $P_{Dmax}$  = 400 mW + 64 mW

Thus:

P<sub>Dmax</sub> = 464 mW.

Using the values obtained in *Table 54: Thermal characteristics*  $T_{Jmax}$  is calculated as follows:

For LQFP64 46 °C/W

T<sub>imax</sub> = 82 °C + (46 °C/W x 464 mW) = 82 °C + 21 °C = 103 ° C

This is within the range of the suffix C version parts (-40  $^{\circ}$ C < T<sub>i</sub> < 125  $^{\circ}$  C).

Parts must be ordered at least with the temperature range suffix C.

### 13.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST visual develop (STVD) IDE and the ST visual programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8.

#### 13.2.1 STM8 toolset

The STM8 toolset with STVD integrated development environment and STVP programming software is available for free download at *www.st.com*. This package includes:

#### ST visual develop

Full-featured integrated development environment from STMicroelectronics, featuring:

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

#### ST visual programmer (STVP)

Easy-to-use, unlimited graphical interface allowing read, write and verification of the STM8A microcontroller's Flash memory. STVP also offers project mode for saving programming configurations and automating programming sequences.

#### 13.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of the application directly from an easy-to-use graphical interface. Available toolchains include:

#### C compiler for STM8

All compilers are available in free version with a limited code size depending on the compiler. For more information, refer to www.cosmic-software.com, www.raisonance.com, and www.iar.com.

#### STM8 assembler linker

Free assembly toolchain included in the STM8 toolset, which allows users to assemble and link their application source code.

## **13.3 Programming tools**

During the development cycle, STice provides in-circuit programming of the STM8A Flash microcontroller on the application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8A.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.