Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 68                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af52aatay |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 47.<br>Table 48.<br>Table 49. | ESD absolute maximum ratings                                                |

|-------------------------------------|-----------------------------------------------------------------------------|

|                                     | mechanical data                                                             |

| Table 50.                           | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                           |

|                                     | package mechanical data                                                     |

| Table 51.                           | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                     |

|                                     | mechanical data                                                             |

| Table 52.                           | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                     |

|                                     | mechanical data                                                             |

| Table 53.                           | VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad |

|                                     | flat package mechanical data                                                |

| Table 54.                           | Thermal characteristics                                                     |

| Table 55.                           | Document revision history                                                   |

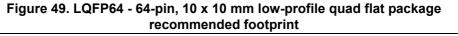

| Figure 48.<br>Figure 49. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline              |

|--------------------------|--------------------------------------------------------------------------------|

|                          | recommended footprint                                                          |

| Figure 50.               | LQFP64 marking example (package top view)96                                    |

| Figure 51.               | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                |

| Figure 52.               | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                        |

| -                        | recommended footprint                                                          |

| Figure 53.               | LQFP48 marking example (package top view)                                      |

| Figure 54.               | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline                |

| Figure 55.               | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                        |

| U                        | recommended footprint                                                          |

| Figure 56.               | LQFP32 marking example (package top view)                                      |

| Figure 57.               | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad      |

| 0                        | flat package outline                                                           |

| Figure 58.               | VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad    |

| U                        | flat package recommended footprint                                             |

| Figure 59.               | VFQFPN32 marking example (package top view)                                    |

| Figure 60.               | STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information scheme <sup>1</sup> |

# 2 Description

The STM8AF526x/8x/Ax and STM8AF6269/8x/Ax automotive 8-bit microcontrollers described in this datasheet offer from 32 Kbyte to 128 Kbyte of non volatile memory and integrated true data EEPROM. They are referred to as high density STM8A devices in STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

The STM8AF52 series features a CAN interface.

All devices of the STM8A product line provide the following benefits: reduced system cost, performance and robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, wtachdog, and brown-out reset.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map, and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8A family thanks to their advanced core which is made in a state-of-the art technology for automotive applications with 3.3 V to 5.5 V operating supply.

All STM8A and ST7 microcontrollers are supported by the same tools including STVD/STVP development environment, the STice emulator and a low-cost, third party incircuit debugging tool.

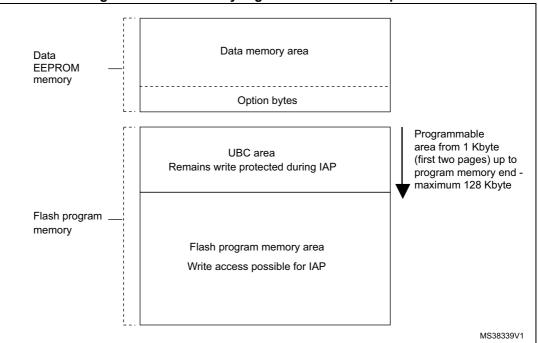

# 5.4.2 Write protection (WP)

Write protection in application mode is intended to avoid unintentional overwriting of the memory. The write protection can be removed temporarily by executing a specific sequence in the user software.

# 5.4.3 Protection of user boot code (UBC)

If the user chooses to update the Flash program memory using a specific boot code to perform in application programming (IAP), this boot code needs to be protected against unwanted modification.

In the STM8A a memory area of up to 128 Kbytes can be protected from overwriting at user option level. Other than the standard write protection, the UBC protection can exclusively be modified via the debug interface, the user software cannot modify the UBC protection status.

The UBC memory area contains the reset and interrupt vectors and its size can be adjusted in increments of 512 bytes by programming the UBC and NUBC option bytes (see *Section 9: Option bytes on page 54*).

Figure 2. Flash memory organization of STM8A products

# 5.4.4 Read-out protection (ROP)

The STM8A provides a read-out protection of the code and data memory which can be activated by an option byte setting (see the ROP option byte in section 10).

The read-out protection prevents reading and writing Flash program memory, data memory and option bytes via the debug module and SWIM interface. This protection is active in all device operation modes. Any attempt to remove the protection by overwriting the ROP option byte triggers a global erase of the program and data memory.

DocID14395 Rev 15

Detailed feature list:

- Full duplex, asynchronous communications

- NRZ standard format (mark/space)

- High-precision baud rate generator system

- Common programmable transmit and receive baud rates up to f<sub>MASTER</sub>/16

- Programmable data word length (8 or 9 bits)

- Configurable stop bits: Support for 1 or 2 stop bits

- LIN master mode:

- LIN break and delimiter generation

- LIN break and delimiter detection with separate flag and interrupt source for readback checking.

- Transmitter clock output for synchronous communication

- Separate enable bits for transmitter and receiver

- Transfer detection flags:

- Receive buffer full

- Transmit buffer empty

- End of transmission flags

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Six interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Parity error

- LIN break and delimiter detection

- Two interrupt vectors:

- Transmitter interrupt

- Receiver interrupt

- Reduced power consumption mode

- Wakeup from mute mode (by idle line detection or address mark detection)

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line

### 5.9.3 Serial peripheral interface (SPI)

The devices covered by this datasheet contain one SPI. The SPI is available on all the supported packages.

- Maximum speed: 10 Mbit/s or f<sub>MASTER</sub>/2 for master, 8 Mbit/s or f<sub>MASTER</sub> /2 for slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave mode/master mode management by hardware or software for both master and slave

- Programmable clock polarity and phase

- Programmable data order with MSB-first or LSB-first shifting

- Dedicated transmission and reception flags with interrupt capability

- SPI bus busy status flag

- Hardware CRC feature for reliable communication:

- CRC value can be transmitted as last byte in Tx mode

- CRC error checking for last received byte

# 5.9.4 Inter integrated circuit (I<sup>2</sup>C) interface

The devices covered by this datasheet contain one  $I^2C$  interface. The interface is available on all the supported packages.

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

- Status flags:

- Transmitter/receiver mode flag

- End-of-byte transmission flag

- I<sup>2</sup>C busy flag

- Error flags:

- Arbitration lost condition for master mode

- Acknowledgement failure after address/data transmission

- Detection of misplaced start or stop condition

- Overrun/underrun if clock stretching is disabled

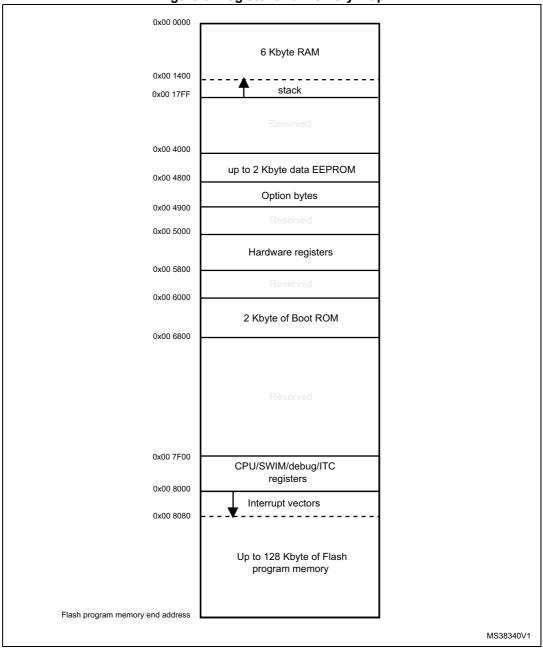

# 7 Memory and register map

# 7.1 Memory map

Figure 8. Register and memory map

| Address                   | Block                     | Register label                                  | Register name                          | Reset<br>status |  |  |

|---------------------------|---------------------------|-------------------------------------------------|----------------------------------------|-----------------|--|--|

| 0x00 5320                 |                           | TIM3_CR1                                        | TIM3 control register 1                | 0x00            |  |  |

| 0x00 5321                 |                           | TIM3_IER                                        | TIM3 interrupt enable register         | 0x00            |  |  |

| 0x00 5322                 |                           | TIM3_SR1                                        | TIM3 status register 1                 | 0x00            |  |  |

| 0x00 5323                 |                           | TIM3_SR2                                        | TIM3 status register 2                 | 0x00            |  |  |

| 0x00 5324                 |                           | TIM3_EGR                                        | TIM3 event generation register         | 0x00            |  |  |

| 0x00 5325                 |                           | TIM3_CCMR1                                      | TIM3 capture/compare mode register 1   | 0x00            |  |  |

| 0x00 5326                 |                           | TIM3_CCMR2                                      | TIM3 capture/compare mode register 2   | 0x00            |  |  |

| 0x00 5327                 |                           | TIM3_CCER1                                      | TIM3 capture/compare enable register 1 | 0x00            |  |  |

| 0x00 5328                 | TIM3                      | TIM3_CNTRH                                      | TIM3 counter high                      | 0x00            |  |  |

| 0x00 5329                 |                           | TIM3_CNTRL                                      | TIM3 counter low                       | 0x00            |  |  |

| 0x00 532A                 |                           | TIM3_PSCR                                       | TIM3 prescaler register                | 0x00            |  |  |

| 0x00 532B                 |                           | TIM3_ARRH                                       | TIM3 auto-reload register high         | 0xFF            |  |  |

| 0x00 532C                 |                           | TIM3_ARRL                                       | TIM3 auto-reload register low          | 0xFF            |  |  |

| 0x00 532D                 |                           | TIM3_CCR1H TIM3 capture/compare register 1 high |                                        | 0x00            |  |  |

| 0x00 532E                 |                           | TIM3_CCR1L                                      | TIM3 capture/compare register 1 low    | 0x00            |  |  |

| 0x00 532F                 |                           | TIM3_CCR2H                                      | TIM3 capture/compare register 2 high   | 0x00            |  |  |

| 0x00 5330                 |                           | TIM3_CCR2L                                      | TIM3 capture/compare register 2 low    | 0x00            |  |  |

| 0x00 5331 to<br>0x00 533F |                           | Re                                              | eserved area (15 bytes)                |                 |  |  |

| 0x00 5340                 |                           | TIM4_CR1                                        | TIM4 control register 1                | 0x00            |  |  |

| 0x00 5341                 |                           | TIM4_IER                                        | TIM4 interrupt enable register         | 0x00            |  |  |

| 0x00 5342                 |                           | TIM4_SR                                         | TIM4 status register                   | 0x00            |  |  |

| 0x00 5343                 | TIM4                      | TIM4_EGR                                        | TIM4 event generation register         | 0x00            |  |  |

| 0x00 5344                 |                           | TIM4_CNTR                                       | TIM4 counter                           | 0x00            |  |  |

| 0x00 5345                 |                           | TIM4_PSCR                                       | TIM4 prescaler register                | 0x00            |  |  |

| 0x00 5346                 |                           | TIM4_ARR                                        | TIM4 auto-reload register              | 0xFF            |  |  |

| 0x00 5347 to<br>0x00 53FF | Reserved area (185 bytes) |                                                 |                                        |                 |  |  |

Table 14. General hardware register map (continued)

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT12           | TMU_KEY 5 [7:0]: Temporary unprotection key 4<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                                  |

| OPT13           | TMU_KEY 6 [7:0]: Temporary unprotection key 5           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |

| OPT14           | TMU_KEY 7 [7:0]: Temporary unprotection key 6           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |

| OPT15           | TMU_KEY 8 [7:0]: Temporary unprotection key 7           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |

| OPT16           | <ul> <li>TMU_MAXATT [7:0]: TMU access failure counter</li> <li>TMU_MAXATT can be initialized with the desired value only if TMU is disabled (TMU[3:0]=0101 in OPT6 option byte).</li> <li>When TMU is enabled, any attempt to temporary remove the readout protection by using wrong key values increments the counter.</li> <li>When the option byte value reaches 0x08, the Flash memory and data EEPROM are erased.</li> </ul> |

| OPT17           | <b>BL[7:0]: Bootloader enable</b><br>If this option byte is set to 0x55 (complementary value 0xAA) the<br>bootloader program is activated also in case of a programmed code<br>memory (for more details, see the bootloader user manual, UM0560).                                                                                                                                                                                 |

## Table 19. Option byte description (continued)

| Symbol                                        | Parameter                                      | Conditions              | Min              | Тур               | Мах  | Unit |  |

|-----------------------------------------------|------------------------------------------------|-------------------------|------------------|-------------------|------|------|--|

| +                                             | V <sub>DD</sub> rise time rate                 | -                       | 2 <sup>(1)</sup> | -                 | 8    |      |  |

| t <sub>VDD</sub>                              | V <sub>DD</sub> fall time rate                 | -                       | 2 <sup>(1)</sup> | -                 | ∞    | µs/V |  |

| +                                             | Reset release delay                            | V <sub>DD</sub> rising  | -                | 1                 | 1.7  | ms   |  |

| t <sub>TEMP</sub>                             | Reset generation delay                         | V <sub>DD</sub> falling | -                | 3                 | -    | μs   |  |

| V <sub>IT+</sub>                              | Power-on reset<br>threshold <sup>(2) (3)</sup> | -                       | 2.65             | 2.8               | 2.95 | v    |  |

| V <sub>IT-</sub> Brown-out reset<br>threshold |                                                | -                       | 2.58             | 2.73              | 2.88 | v    |  |

| V <sub>HYS(BOR)</sub>                         | Brown-out reset<br>hysteresis                  | -                       | -                | 70 <sup>(1)</sup> | -    | mV   |  |

Table 25. Operating conditions at power-up/power-down

1. Guaranteed by design, not tested in production.

2. If V<sub>DD</sub> is below 3 V, the code execution is guaranteed above the V<sub>IT-</sub> and V<sub>IT+</sub> thresholds. RAM content is kept. The EEPROM programming sequence must not be initiated.

3. There is inrush current into V<sub>DD</sub> present after device power on to charge C<sub>EXT</sub> capacitor. This inrush energy depends from C<sub>EXT</sub> capacitor value. For example, a C<sub>EXT</sub> of 1  $\mu$ F requires Q=1  $\mu$ F x 1.8 V = 1.8  $\mu$ C.

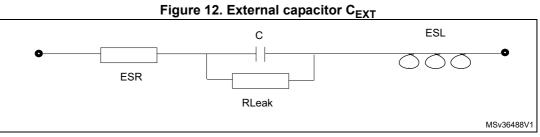

## **10.3.1 VCAP external capacitor**

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 24*. Care should be taken to limit the series inductance to less than 15 nH.

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

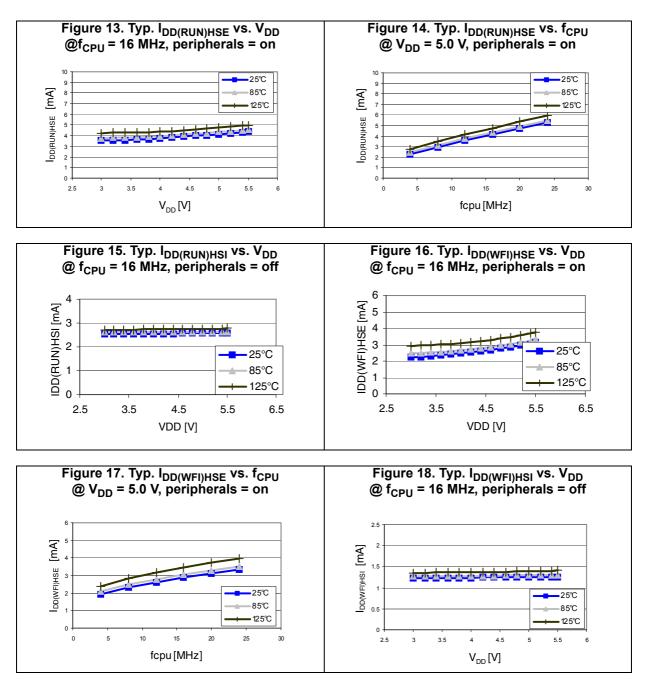

#### **10.3.2** Supply current characteristics

The current consumption is measured as described in *Figure 9 on page 59* and *Figure 10 on page 60*.

If not explicitly stated, general conditions of temperature and voltage apply.

| Symbol                               | Parameter                        | Con                                                                                                 | Тур                                                 | Мах                      | Unit                |                    |

|--------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------|---------------------|--------------------|

|                                      |                                  | All peripherals                                                                                     | f <sub>CPU</sub> = 24 MHz 1 ws                      | 8.7                      | 16.8 <sup>(2)</sup> |                    |

|                                      |                                  | clocked, code                                                                                       | f <sub>CPU</sub> = 16 MHz                           | 7.4                      | 14                  |                    |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>  | Supply current in<br>Run mode    | executed from Flash program memory,                                                                 | f <sub>CPU</sub> = 8 MHz                            | 4.0                      | 7.4 <sup>(2)</sup>  |                    |

|                                      |                                  | HSE external clock                                                                                  | f <sub>CPU</sub> = 4 MHz                            | 2.4                      | 4.1 <sup>(2)</sup>  |                    |

|                                      |                                  | (without resonator)                                                                                 | f <sub>CPU</sub> = 2 MHz                            | 1.5                      | 2.5                 |                    |

|                                      |                                  |                                                                                                     | f <sub>CPU</sub> = 24 MHz                           | 4.4                      | 6.0 <sup>(2)</sup>  |                    |

|                                      | Supply current in<br>Run mode    | All peripherals<br>clocked, code<br>executed from RAM,<br>HSE external clock<br>(without resonator) | f <sub>CPU</sub> = 16 MHz                           | 3.7                      | 5.0                 | -                  |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>  |                                  |                                                                                                     | f <sub>CPU</sub> = 8 MHz                            | 2.2                      | 3.0 <sup>(2)</sup>  |                    |

|                                      |                                  |                                                                                                     | f <sub>CPU</sub> = 4 MHz                            | 1.4                      | 2.0 <sup>(2)</sup>  |                    |

|                                      |                                  |                                                                                                     | f <sub>CPU</sub> = 2 MHz                            | 1.0                      | 1.5                 | mA                 |

|                                      | Supply current in<br>Wait mode   | CPU stopped, all<br>peripherals off, HSE<br>external clock                                          | f <sub>CPU</sub> = 24 MHz                           | 2.4                      | 3.1 <sup>(2)</sup>  |                    |

|                                      |                                  |                                                                                                     | f <sub>CPU</sub> = 16 MHz                           | 1.65                     | 2.5                 |                    |

| I <sub>DD(WFI)</sub> <sup>(1)</sup>  |                                  |                                                                                                     | f <sub>CPU</sub> = 8 MHz                            | 1.15                     | 1.9 <sup>(2)</sup>  |                    |

|                                      |                                  |                                                                                                     | external clock                                      | f <sub>CPU</sub> = 4 MHz | 0.90                | 1.6 <sup>(2)</sup> |

|                                      |                                  |                                                                                                     | f <sub>CPU</sub> = 2 MHz                            | 0.80                     | 1.5                 |                    |

| I <sub>DD(SLOW)</sub> <sup>(1)</sup> |                                  | f <sub>CPU</sub> scaled down,<br>all peripherals off,                                               | External clock 16 MHz<br>f <sub>CPU</sub> = 125 kHz | 1.50                     | 1.95                |                    |

|                                      | Slow mode code executed from RAM |                                                                                                     | LSI internal RC<br>f <sub>CPU</sub> = 128 kHz       | 1.50                     | 1.80 <sup>(2)</sup> |                    |

# Table 26. Total current consumption in Run, Wait and Slow mode. General conditions for $V_{DD}$ apply, $T_A$ = -40 °C to 150 °C

1. The current due to I/O utilization is not taken into account in these values.

2. Guaranteed by design, not tested in production.

#### **Current consumption curves**

*Figure 13* to *Figure 18* show typical current consumption measured with code executing in RAM.

DocID14395 Rev 15

| Symbol               | Parameter                            | Condition                      | Min                  | Max | Unit   |

|----------------------|--------------------------------------|--------------------------------|----------------------|-----|--------|

| T <sub>WE</sub>      | Temperature for writing and erasing  | -                              | -40                  | 150 | °C     |

| N                    | Data memory endurance <sup>(1)</sup> | T <sub>A</sub> = 25 °C         | 300 k                | -   | cycles |

| N <sub>WE</sub> (e   | (erase/write cycles)                 | $T_A = -40^{\circ}C$ to 125 °C | 100 k <sup>(2)</sup> | -   | Cycles |

| t <sub>RET</sub> Dat | Data retention time                  | T <sub>A</sub> = 25 °C         | 40 <sup>(2)(3)</sup> | -   | years  |

|                      |                                      | T <sub>A</sub> = 55 °C         | 20 <sup>(2)(3)</sup> | -   |        |

#### Table 37. Data memory

1. The physical granularity of the memory is four bytes, so cycling is performed on four bytes even when a write/erase operation addresses a single byte.

2. More information on the relationship between data retention time and number of write/erase cycles is available in a separate technical document.

3. Retention time for 256B of data memory after up to 1000 cycles at 125 °C.

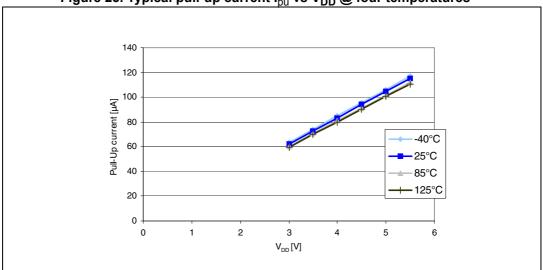

Figure 25. Typical pull-up current I<sub>pu</sub> vs V<sub>DD</sub> @ four temperatures<sup>(1)</sup>

1. The pull-up is a pure resistor (slope goes through 0).

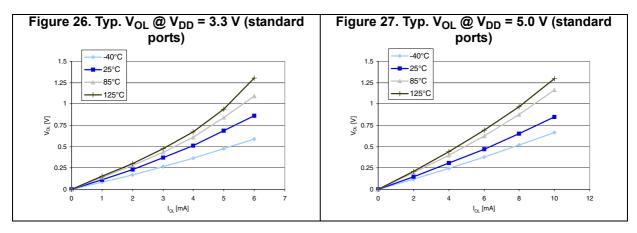

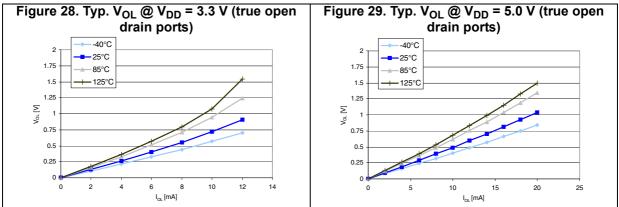

#### Typical output level curves

*Figure 26* to *Figure 35* show typical output level curves measured with output on a single pin.

DocID14395 Rev 15

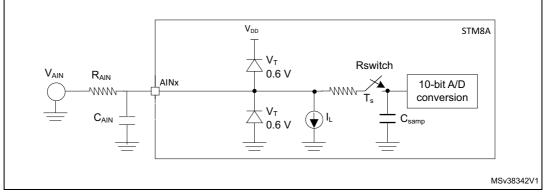

## 10.3.11 10-bit ADC characteristics

Subject to general operating conditions for  $V_{\text{DDA}},\,f_{\text{MASTER}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol              | Parameter                                   | Conditions                                                             | Min               | Тур  | Max               | Unit    |

|---------------------|---------------------------------------------|------------------------------------------------------------------------|-------------------|------|-------------------|---------|

| f <sub>ADC</sub>    | ADC clock frequency                         | -                                                                      | 111 kHz           | -    | 4 MHz             | kHz/MHz |

| V <sub>DDA</sub>    | Analog supply                               | -                                                                      | 3                 | -    | 5.5               |         |

| $V_{REF^+}$         | Positive reference voltage                  | -                                                                      | 2.75              | -    | V <sub>DDA</sub>  |         |

| V <sub>REF-</sub>   | Negative reference voltage                  | -                                                                      | V <sub>SSA</sub>  | -    | 0.5               | V       |

|                     |                                             | -                                                                      | V <sub>SSA</sub>  | -    | V <sub>DDA</sub>  |         |

| V <sub>AIN</sub>    | Conversion voltage range <sup>(1)</sup>     | Devices with<br>external V <sub>REF+</sub> /<br>V <sub>REF-</sub> pins | V <sub>REF-</sub> | -    | V <sub>REF+</sub> |         |

| C <sub>samp</sub>   | Internal sample and hold capacitor          | -                                                                      | -                 | -    | 3                 | pF      |

| ts <sup>(1)</sup>   | Sampling time                               | f <sub>ADC</sub> = 2 MHz                                               | -                 | 1.5  | -                 |         |

| LS Y                | (3 x 1/f <sub>ADC</sub> )                   | f <sub>ADC</sub> = 4 MHz                                               | -                 | 0.75 | -                 |         |

| +                   | Makeun time frem standby                    | f <sub>ADC</sub> = 2 MHz                                               | -                 | 7    | -                 |         |

| t <sub>stab</sub>   | Wakeup time from standby                    | f <sub>ADC</sub> = 4 MHz                                               | -                 | 3.5  | -                 | μs      |

|                     | Total conversion time including             | f <sub>ADC</sub> = 2 MHz                                               | -                 | 7    | -                 |         |

| t <sub>CONV</sub>   | sampling time<br>(14 x 1/f <sub>ADC</sub> ) | f <sub>ADC</sub> = 4 MHz                                               | -                 | 3.5  | -                 |         |

| R <sub>switch</sub> | Equivalent switch resistance                | -                                                                      | -                 | -    | 30                | kΩ      |

During the sample time, the sampling capacitance, C<sub>samp</sub> (3 pF typ), can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result.

#### Figure 43. Typical application with ADC

1. Legend:  $R_{AIN}$  = external resistance,  $C_{AIN}$  = capacitors,  $C_{samp}$  = internal sample and hold capacitor.

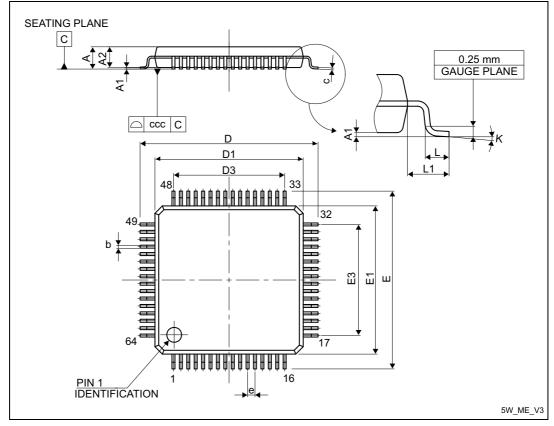

# 11.2 LQFP64 package information

Figure 48. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 50. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat |

|-------------------------------------------------------------|

| package mechanical data                                     |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Max   | Min                   | Тур    | Мах    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

# Table 50. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

# 13.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST visual develop (STVD) IDE and the ST visual programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8.

#### 13.2.1 STM8 toolset

The STM8 toolset with STVD integrated development environment and STVP programming software is available for free download at *www.st.com*. This package includes:

#### ST visual develop

Full-featured integrated development environment from STMicroelectronics, featuring:

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

#### ST visual programmer (STVP)

Easy-to-use, unlimited graphical interface allowing read, write and verification of the STM8A microcontroller's Flash memory. STVP also offers project mode for saving programming configurations and automating programming sequences.

### 13.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of the application directly from an easy-to-use graphical interface. Available toolchains include:

#### C compiler for STM8

All compilers are available in free version with a limited code size depending on the compiler. For more information, refer to www.cosmic-software.com, www.raisonance.com, and www.iar.com.

#### STM8 assembler linker

Free assembly toolchain included in the STM8 toolset, which allows users to assemble and link their application source code.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 16-Sep-2008 | 3        | Replaced the salestype 'STM8H61xx' with 'STM8AH61xx on the first page.<br>Added 'part numbers' to heading rows of <i>Table 1: Device summary</i> .<br>Updated the 80-pin package silhouette on cover page in line with<br>POA 0062342-revD.<br><i>Table 18</i> : Renamed 'TMU key registers 0-7 [7:0]' as 'TMU key<br>registers 1-8 [7:0]'<br><i>Section 9</i> : Updated introductory text concerning option bytes which<br>do not need to be saved in a complementary form.<br><i>Table 18</i> : Renamed the option bits 'TMU[0:3]', 'NTMU[0:3]', and<br>'TMU_KEY 0-7 [7:0]' as 'TMU[3:0]', 'NTMU[3:0]', and 'TMU_KEY 1-8<br>[7:0]' respectively.<br><i>Table 21</i> : Updated values of option byte 5 (HSECNT[7:0]); inverted<br>the description of option byte 6 (TMU[3:0]); renamed option bytes 8<br>to 15 'TMU_KEY 0-7 [7:0]', as 'TMU_KEY 1-8 [7:0]'.<br>Updated 80-pin package information in line with POA 0062342-revD<br>in <i>Figure 45</i> and <i>Table 53</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 01-Jul-2009 | 4        | Added 'STM8AH61xx' and 'STM8AH51xx to document header.<br>Updated : <i>Features on page 1</i> (memories, timers, operating<br>temperature, ADC and I/Os).<br>Updated <i>Table 1: Device summary</i><br>Updated Kbyte value of program memory in <i>Section: Introduction</i><br>Changed the first two lines from the top in <i>Section: Description</i> .<br>Updated <i>Figure 1: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax</i><br><i>block diagram</i><br>Updated <i>Section 5: Product overview</i><br>In <i>Figure 5: LQFP 48-pin pinout</i> , added USART function to pins 10,<br>11, and 12; added CAN Tx and CAN Rx functions to pins 35 and 36<br>respectively.<br>Section 6: <i>Pinouts and pin description:</i> deleted the text below the<br><i>Table 10: Legend/abbreviation for the pin description table</i><br><i>Table 11: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin</i><br><i>description:</i> 68th, 69th pin (LQFP80): replaced X with a dash for PP<br>output and Added a table footnote.<br>Updated <i>Figure 8: Register and memory map</i> .<br><i>Table 12: Memory model 128K:</i> updated footnote<br>Deleted the <i>Table: Stack and RAM partitioning</i><br><i>Table 17: STM8A interrupt table:</i> Updated priorities 13, 15, 17, 20<br>and 24 and changed table footnote<br>Updated <i>Section 7: Memory and register map</i><br>Updated <i>Table: Data memory, Table:</i> I/O static characteristics, and<br><i>Table 39: NRST pin characteristics.</i><br><i>Section 10.1.1: Minimum and maximum values:</i> added ambient<br>temperature T <sub>A</sub> = -40 °C<br>Updated <i>Table 20: Voltage characteristics.</i><br>Updated <i>Table 21: Current characteristics.</i><br>Updated <i>Table 22: Thermal characteristics.</i><br>Updated <i>Table 22: Thermal characteristics.</i><br>Updated <i>Table 24: General operating conditions.</i> |  |  |

Table 55. Document revision history (continued)

| Table 55. Document revision history (continued) |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date                                            | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 18-Jul-2012                                     | 9<br>(continued) | Table 26: Total current consumption in Run, Wait and Slow mode.General conditions for VDD apply, TA = -40 °C to 150 °C: updatedconditions for I <sub>DD(RUN)</sub> :Table 38: I/O static characteristics: added new condition and newmax values for rise and fall time; updated footnote 2.Section 10.3.7: Reset pin characteristics: updated text belowFigure 38: Typical NRST pull-up current Ipu vs VDDFigure 39: Recommended reset pin protection: updated unit ofcapacitor.Table 41: SPI characteristics: updated SCK high and low timeconditions and values.Figure 42: SPI timing diagram - master mode: replaced 'SCK input'signals with 'SCK output' signals.Updated Table 49: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flatpackage mechanical data, Table 50: LQFP64 - 64-pin, 10 x 10 mmlow-profile quad flat package mechanical data, Table 51: LQFP48 -48-pin, 7 x 7 mm low-profile quad flat package mechanical data,Table 52: LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat packagemechanical data, Table 53: VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mmpitch very thin profile fine pitch quad flat package mechanical dataReplaced Figure 48: LQFP64 - 64-pin, 10 x 10 mm low-profile quadflat package outline, Figure 51: LQFP48 - 48-pin, 7 x 7 mm low-romile quad flat package outlineAdded Figure 49: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage recommended footprint, Figure 52: LQFP48 - 48-pin, 7 xr mm low-profile quad flat package outlineAdded Figure 57: VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch verythin profile quad flat package recommended footprint and |  |  |  |

| 31-Mar-2014                                     | 10               | <ul> <li>Updated:</li> <li>Table 1: Device summary,</li> <li>Table: STM8AF52xx product line-up with CAN,</li> <li>Table: STM8AF/H/P51xx product line-up with CAN,</li> <li>Table: STM8AF/H/P61xx product line-up without CAN,</li> <li>Table 11: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description,</li> <li>The maximum speed in Section 5.9.3: Serial peripheral interface (SPI),</li> <li>t<sub>TEMP</sub> Reset release delay /VDD rising typical and max values in Table 25: Operating conditions at power-up/power-down,</li> <li>The symbol t<sub>IFP(NRST)</sub> with t<sub>INFP(NRST)</sub> in Table 39: NRST pin characteristics,</li> <li>The address and comment for Reset in Table 17: STM8A interrupt table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |