Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6269tcy |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet refers to the STM8AF526x/8x/Ax and STM8AF6269/8x/Ax products with 32 to 128 Kbyte of program memory.

In the order code, the letter 'F' refers to product versions with Flash and data EEPROM and 'P' to product versions with FASTROM. The identifiers 'F' and 'P' do not coexist in a given order code.

The datasheet contains the description of family features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8A microcontroller memory, registers and peripherals, please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8S and STM8A Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

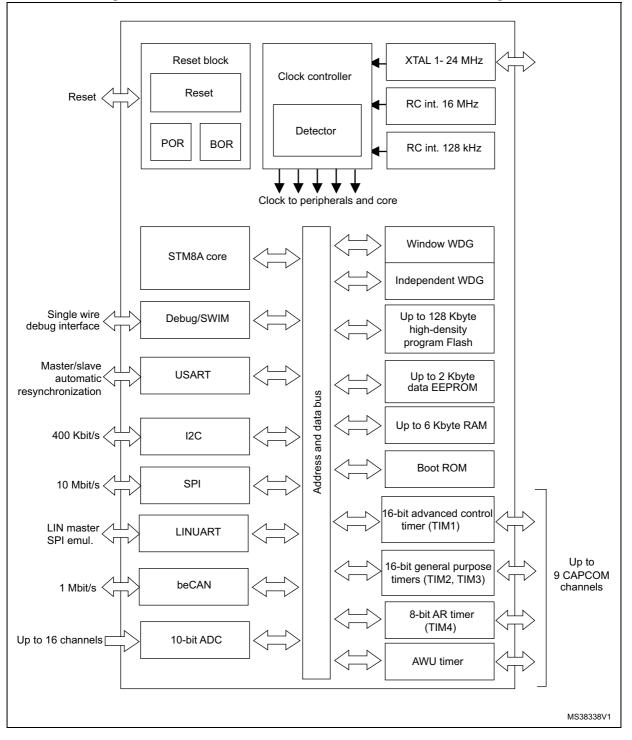

# 4 Block diagram

Figure 1. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax block diagram

DocID14395 Rev 15

# 5 **Product overview**

This section is intended to describe the family features that are actually implemented in the products covered by this datasheet.

For more detailed information on each feature please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

# 5.1 STM8A central processing unit (CPU)

The 8-bit STM8A core is a modern CISC core and has been designed for code efficiency and performance. It contains 21 internal registers (six directly addressable in each execution context), 20 addressing modes including indexed indirect and relative addressing and 80 instructions.

## 5.1.1 Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus with single cycle fetching for most instructions

- X and Y 16-bit index registers, enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter with 16-Mbyte linear memory space

- 16-bit stack pointer with access to a 64 Kbyte stack

- 8-bit condition code register with seven condition flags for the result of the last instruction.

## 5.1.2 Addressing

- 20 addressing modes

- Indexed indirect addressing mode for look-up tables located anywhere in the address space

- Stack pointer relative addressing mode for efficient implementation of local variables and parameter passing

#### 5.1.3 Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

## 5.5.3 128 kHz low-speed internal RC oscillator (LSI)

The frequency of this clock is 128 kHz and it is independent from the main clock. It drives the independent watchdog or the AWU wakeup timer.

In systems which do not need independent clock sources for the watchdog counters, the 128 kHz signal can be used as the system clock. This configuration has to be enabled by setting an option byte (OPT3/OPT3N, bit LSI\_EN).

## 5.5.4 24 MHz high-speed external crystal oscillator (HSE)

The external high-speed crystal oscillator can be selected to deliver the main clock in normal Run mode. It operates with quartz crystals and ceramic resonators.

- Frequency range: 1 MHz to 24 MHz

- Crystal oscillation mode: preferred fundamental

- I/Os: standard I/O pins multiplexed with OSCIN, OSCOUT

## 5.5.5 External clock input

An external clock signal can be applied to the OSCIN input pin of the crystal oscillator. The frequency range is 0 to 24 MHz.

#### 5.5.6 Clock security system (CSS)

The clock security system protects against a system stall in case of an external crystal clock failure.

In case of a clock failure an interrupt is generated and the high-speed internal clock (HSI) is automatically selected with a frequency of 2 MHz (16 MHz/8).

|             | <b>J</b>         |

|-------------|------------------|

| Control bit | Peripheral       |

| PCKEN17     | TIM1             |

| PCKEN16     | TIM3             |

| PCKEN15     | TIM2             |

| PCKEN14     | TIM4             |

| PCKEN13     | LINUART          |

| PCKEN12     | USART            |

| PCKEN11     | SPI              |

| PCKEN10     | l <sup>2</sup> C |

#### Table 4. Peripheral clock gating bits (CLK\_PCKENR1)

#### 5.9.3 Serial peripheral interface (SPI)

The devices covered by this datasheet contain one SPI. The SPI is available on all the supported packages.

- Maximum speed: 10 Mbit/s or f<sub>MASTER</sub>/2 for master, 8 Mbit/s or f<sub>MASTER</sub> /2 for slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave mode/master mode management by hardware or software for both master and slave

- Programmable clock polarity and phase

- Programmable data order with MSB-first or LSB-first shifting

- Dedicated transmission and reception flags with interrupt capability

- SPI bus busy status flag

- Hardware CRC feature for reliable communication:

- CRC value can be transmitted as last byte in Tx mode

- CRC error checking for last received byte

## 5.9.4 Inter integrated circuit (I<sup>2</sup>C) interface

The devices covered by this datasheet contain one  $I^2C$  interface. The interface is available on all the supported packages.

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

- Status flags:

- Transmitter/receiver mode flag

- End-of-byte transmission flag

- I<sup>2</sup>C busy flag

- Error flags:

- Arbitration lost condition for master mode

- Acknowledgement failure after address/data transmission

- Detection of misplaced start or stop condition

- Overrun/underrun if clock stretching is disabled

## 5.10 Input/output specifications

The product features four I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

- Caution: In STM8AF5286UC device, the following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor,

- configured as output push-pull low.

| Address   | Block                   | Register label                         | Register name                     | Reset               |

|-----------|-------------------------|----------------------------------------|-----------------------------------|---------------------|

|           |                         | -                                      | -                                 | status              |

| 0x00 5014 |                         | PE_ODR                                 | Port E data output latch register | 0x00                |

| 0x00 5015 |                         | PE_IDR                                 | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016 | Port E                  | PE_DDR                                 | Port E data direction register    | 0x00                |

| 0x00 5017 |                         | PE_CR1                                 | Port E control register 1         | 0x00                |

| 0x00 5018 |                         | PE_CR2                                 | Port E control register 2         | 0x00                |

| 0x00 5019 |                         | PF_ODR                                 | Port F data output latch register | 0x00                |

| 0x00 501A |                         | PF_IDR                                 | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B | Port F                  | PF_DDR                                 | Port F data direction register    | 0x00                |

| 0x00 501C |                         | PF_CR1                                 | Port F control register 1         | 0x00                |

| 0x00 501D |                         | PF_CR2 Port F control register 2       |                                   | 0x00                |

| 0x00 501E |                         | PG_ODR                                 | Port G data output latch register | 0x00                |

| 0x00 501F |                         | 0xXX <sup>(1)</sup>                    |                                   |                     |

| 0x00 5020 | Port G                  | PG_DDR                                 | Port G data direction register    | 0x00                |

| 0x00 5021 |                         | PG_CR1                                 | Port G control register 1         | 0x00                |

| 0x00 5022 | PG_CR2 Port G control r |                                        | Port G control register 2         | 0x00                |

| 0x00 5023 |                         | PH_ODR                                 | Port H data output latch register | 0x00                |

| 0x00 5024 |                         | PH_IDR                                 | Port H input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5025 | Port H                  | PH_DDR                                 | Port H data direction register    | 0x00                |

| 0x00 5026 |                         | PH_CR1                                 | Port H control register 1         | 0x00                |

| 0x00 5027 |                         | PH_CR2                                 | Port H control register 2         | 0x00                |

| 0x00 5028 |                         | PI_ODR                                 | Port I data output latch register | 0x00                |

| 0x00 5029 |                         | PI_IDR Port I input pin value register |                                   | 0xXX <sup>(1)</sup> |

| 0x00 502A | Port I                  | PI_DDR                                 | Port I data direction register    | 0x00                |

| 0x00 502B |                         | PI_CR1                                 | Port I control register 1         | 0x00                |

| 0x00 502C |                         | PI_CR2                                 | Port I control register 2         | 0x00                |

| Table 13 I/O | port hardware register map (continued) |   |

|--------------|----------------------------------------|---|

|              | port naruware register map (continueu) | , |

1. Depends on the external circuitry.

| Address                   | Block | Register label                           | ster label Register name                |      |  |  |

|---------------------------|-------|------------------------------------------|-----------------------------------------|------|--|--|

| 0x00 5300                 |       | TIM2_CR1                                 | TIM2 control register 1                 | 0x00 |  |  |

| 0x00 5301                 |       | TIM2_IER                                 | TIM2 interrupt enable register          | 0x00 |  |  |

| 0x00 5302                 |       | TIM2_SR1                                 | TIM2 status register 1                  | 0x00 |  |  |

| 0x00 5303                 |       | TIM2_SR2                                 | TIM2 status register 2                  | 0x00 |  |  |

| 0x00 5304                 |       | TIM2_EGR                                 | TIM2 event generation register          | 0x00 |  |  |

| 0x00 5305                 |       | TIM2_CCMR1                               | TIM2 capture/compare mode register 1    | 0x00 |  |  |

| 0x00 5306                 |       | TIM2_CCMR2                               | TIM2 capture/compare mode register 2    | 0x00 |  |  |

| 0x00 5307                 |       | TIM2_CCMR3                               | TIM2 capture/compare mode register 3    | 0x00 |  |  |

| 0x00 5308                 |       | TIM2_CCER1                               | TIM2 capture/compare enable register 1  | 0x00 |  |  |

| 0x00 5309                 |       | TIM2_CCER2                               | TIM2 capture/compare enable register 2  | 0x00 |  |  |

| 0x00 530A                 | TIM2  | TIM2_CNTRH                               | TIM2 counter high                       | 0x00 |  |  |

| 0x00 530B                 |       | TIM2_CNTRL                               | TIM2 counter low                        | 0x00 |  |  |

| 00 530C0x                 |       | TIM2_PSCR TIM2 prescaler register        |                                         | 0x00 |  |  |

| 0x00 530D                 |       | TIM2_ARRH TIM2 auto-reload register high |                                         | 0xFF |  |  |

| 0x00 530E                 |       | TIM2_ARRL                                | TIM2_ARRL TIM2 auto-reload register low |      |  |  |

| 0x00 530F                 |       | TIM2_CCR1H                               | TIM2 capture/compare register 1 high    | 0x00 |  |  |

| 0x00 5310                 |       | TIM2_CCR1L                               | TIM2 capture/compare register 1 low     | 0x00 |  |  |

| 0x00 5311                 |       | TIM2_CCR2H                               | TIM2 capture/compare reg. 2 high        | 0x00 |  |  |

| 0x00 5312                 |       | TIM2_CCR2L                               | TIM2 capture/compare register 2 low     | 0x00 |  |  |

| 0x00 5313                 |       | TIM2_CCR3H                               | TIM2 capture/compare register 3 high    | 0x00 |  |  |

| 0x00 5314                 |       | TIM2_CCR3L                               | TIM2 capture/compare register 3 low     | 0x00 |  |  |

| 0x00 5315 to<br>0x00 531F |       |                                          |                                         |      |  |  |

Table 14. General hardware register map (continued)

| Address                   | Block                            | Register label                                                                              | Register label Register name                    |      |  |  |  |

|---------------------------|----------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------|------|--|--|--|

| 0x00 5320                 | TIM3_CR1 TIM3 control register 1 |                                                                                             |                                                 |      |  |  |  |

| 0x00 5321                 |                                  | TIM3_IER       TIM3 interrupt enable register         TIM3_SR1       TIM3 status register 1 |                                                 |      |  |  |  |

| 0x00 5322                 |                                  |                                                                                             |                                                 |      |  |  |  |

| 0x00 5323                 |                                  | TIM3_SR2 TIM3 status register 2                                                             |                                                 |      |  |  |  |

| 0x00 5324                 |                                  | TIM3_EGR                                                                                    | 0x00                                            |      |  |  |  |

| 0x00 5325                 |                                  | TIM3_CCMR1                                                                                  | TIM3 capture/compare mode register 1            | 0x00 |  |  |  |

| 0x00 5326                 |                                  | TIM3_CCMR2                                                                                  | TIM3 capture/compare mode register 2            | 0x00 |  |  |  |

| 0x00 5327                 |                                  | TIM3_CCER1                                                                                  | TIM3 capture/compare enable register 1          | 0x00 |  |  |  |

| 0x00 5328                 | TIM3                             | TIM3_CNTRH                                                                                  | TIM3 counter high                               | 0x00 |  |  |  |

| 0x00 5329                 |                                  | TIM3_CNTRL                                                                                  | TIM3 counter low                                | 0x00 |  |  |  |

| 0x00 532A                 |                                  | TIM3_PSCR                                                                                   | TIM3_PSCR TIM3 prescaler register               |      |  |  |  |

| 0x00 532B                 |                                  | TIM3_ARRH TIM3 auto-reload register high                                                    |                                                 | 0xFF |  |  |  |

| 0x00 532C                 |                                  | TIM3_ARRL TIM3 auto-reload register low                                                     |                                                 | 0xFF |  |  |  |

| 0x00 532D                 |                                  | TIM3_CCR1H TIM3 capture/compare register 1 high                                             |                                                 | 0x00 |  |  |  |

| 0x00 532E                 |                                  | TIM3_CCR1L TIM3 capture/compare register 1 low                                              |                                                 | 0x00 |  |  |  |

| 0x00 532F                 |                                  | TIM3_CCR2H                                                                                  | TIM3_CCR2H TIM3 capture/compare register 2 high |      |  |  |  |

| 0x00 5330                 |                                  | TIM3_CCR2L TIM3 capture/compare register 2 low                                              |                                                 | 0x00 |  |  |  |

| 0x00 5331 to<br>0x00 533F |                                  | Re                                                                                          | eserved area (15 bytes)                         |      |  |  |  |

| 0x00 5340                 |                                  | TIM4_CR1                                                                                    | TIM4 control register 1                         | 0x00 |  |  |  |

| 0x00 5341                 |                                  | TIM4_IER                                                                                    | TIM4 interrupt enable register                  | 0x00 |  |  |  |

| 0x00 5342                 |                                  | TIM4_SR                                                                                     | TIM4 status register                            | 0x00 |  |  |  |

| 0x00 5343                 | TIM4                             | TIM4_EGR                                                                                    |                                                 |      |  |  |  |

| 0x00 5344                 |                                  | TIM4_CNTR                                                                                   |                                                 |      |  |  |  |

| 0x00 5345                 |                                  | TIM4_PSCR                                                                                   |                                                 |      |  |  |  |

| 0x00 5346                 |                                  | TIM4_ARR                                                                                    | TIM4 auto-reload register                       | 0xFF |  |  |  |

| 0x00 5347 to<br>0x00 53FF |                                  |                                                                                             |                                                 |      |  |  |  |

Table 14. General hardware register map (continued)

| Address                      | Block | Register label | ister label Register name                 |      |  |  |

|------------------------------|-------|----------------|-------------------------------------------|------|--|--|

| 0x00 7F81<br>to<br>0x00 7F8F |       |                | Reserved area (15 bytes)                  |      |  |  |

| 0x00 7F90                    |       | DM_BK1RE       | DM breakpoint 1 register extended byte    | 0xFF |  |  |

| 0x00 7F91                    |       | DM_BK1RH       | DM breakpoint 1 register high byte        | 0xFF |  |  |

| 0x00 7F92                    |       | DM_BK1RL       | DM breakpoint 1 register low byte         | 0xFF |  |  |

| 0x00 7F93                    |       | DM_BK2RE       | DM breakpoint 2 register extended byte    | 0xFF |  |  |

| 0x00 7F94                    |       | DM_BK2RH       | DM breakpoint 2 register high byte        | 0xFF |  |  |

| 0x00 7F95                    | DM    | DM_BK2RL       | DM breakpoint 2 register low byte         | 0xFF |  |  |

| 0x00 7F96                    |       | DM_CR1         | DM debug module control register 1        | 0x00 |  |  |

| 0x00 7F97                    |       | DM_CR2         | DM debug module control register 2        | 0x00 |  |  |

| 0x00 7F98                    |       | DM_CSR1        | DM debug module control/status register 1 | 0x10 |  |  |

| 0x00 7F99                    |       | DM_CSR2        | DM debug module control/status register 2 | 0x00 |  |  |

| 0x00 7F9A                    |       | DM_ENFCTR      | DM enable function register               | 0xFF |  |  |

| 0x00 7F9B<br>to 0x00<br>7F9F |       |                | Reserved area (5 bytes)                   |      |  |  |

#### Table 15. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

2. Product dependent value, see Figure 8: Register and memory map.

| Address   | Block | Register label                                      | Register label Register name                              |      |  |  |

|-----------|-------|-----------------------------------------------------|-----------------------------------------------------------|------|--|--|

| 0x00 5800 |       | TMU_K1                                              | Temporary memory unprotection key register 1              | 0x00 |  |  |

| 0x00 5801 |       | TMU_K2                                              | Temporary memory unprotection key register 2              | 0x00 |  |  |

| 0x00 5802 |       | TMU_K3                                              | Temporary memory unprotection key register 3              | 0x00 |  |  |

| 0x00 5803 |       | TMU_K4                                              | Temporary memory unprotection key register 4              | 0x00 |  |  |

| 0x00 5804 | TMU   | TMU_K5                                              | Temporary memory unprotection key register 5              | 0x00 |  |  |

| 0x00 5805 |       | TMU_K6 Temporary memory unprotection key register 6 |                                                           | 0x00 |  |  |

| 0x00 5806 |       | TMU_K7                                              | TMU_K7 Temporary memory unprotection key register 7       |      |  |  |

| 0x00 5807 |       | TMU_K8                                              | Temporary memory unprotection key register 8              | 0x00 |  |  |

| 0x00 5808 |       | TMU_CSR                                             | Temporary memory unprotection control and status register | 0x00 |  |  |

#### Table 16. Temporary memory unprotection registers

| Symbol                               | Parameter                                                                                             | Con                                                                                                 | ditions                                             | Тур                 | Мах                 | Unit |

|--------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------|---------------------|------|

|                                      |                                                                                                       | All peripherals                                                                                     | f <sub>CPU</sub> = 24 MHz 1 ws                      | 8.7                 | 16.8 <sup>(2)</sup> |      |

|                                      |                                                                                                       | clocked, code                                                                                       | f <sub>CPU</sub> = 16 MHz                           | 7.4                 | 14                  |      |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>  | Supply current in<br>Run mode                                                                         | executed from Flash program memory,                                                                 | f <sub>CPU</sub> = 8 MHz                            | 4.0                 | 7.4 <sup>(2)</sup>  |      |

|                                      |                                                                                                       | HSE external clock                                                                                  | f <sub>CPU</sub> = 4 MHz                            | 2.4                 | 4.1 <sup>(2)</sup>  |      |

|                                      |                                                                                                       | (without resonator)                                                                                 | f <sub>CPU</sub> = 2 MHz                            | 1.5                 | 2.5                 |      |

|                                      | I <sub>DD(RUN)</sub> <sup>(1)</sup> Supply current in<br>Run mode                                     |                                                                                                     | f <sub>CPU</sub> = 24 MHz                           | 4.4                 | 6.0 <sup>(2)</sup>  |      |

|                                      |                                                                                                       | All peripherals<br>clocked, code<br>executed from RAM,<br>HSE external clock<br>(without resonator) | f <sub>CPU</sub> = 16 MHz                           | 3.7                 | 5.0                 |      |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>  |                                                                                                       |                                                                                                     | f <sub>CPU</sub> = 8 MHz                            | 2.2                 | 3.0 <sup>(2)</sup>  |      |

|                                      |                                                                                                       |                                                                                                     | f <sub>CPU</sub> = 4 MHz                            | 1.4                 | 2.0 <sup>(2)</sup>  |      |

|                                      |                                                                                                       |                                                                                                     | f <sub>CPU</sub> = 2 MHz                            | 1.0                 | 1.5                 | mA   |

|                                      |                                                                                                       |                                                                                                     | f <sub>CPU</sub> = 24 MHz                           | 2.4                 | 3.1 <sup>(2)</sup>  |      |

|                                      |                                                                                                       | CPU stopped, all                                                                                    | f <sub>CPU</sub> = 16 MHz                           | 1.65                | 2.5                 |      |

| I <sub>DD(WFI)</sub> <sup>(1)</sup>  | Supply current in Wait mode                                                                           | peripherals off, HSE                                                                                | f <sub>CPU</sub> = 8 MHz                            | 1.15                | 1.9 <sup>(2)</sup>  |      |

|                                      |                                                                                                       | external clock                                                                                      | f <sub>CPU</sub> = 4 MHz                            | 0.90                | 1.6 <sup>(2)</sup>  |      |

|                                      |                                                                                                       |                                                                                                     | f <sub>CPU</sub> = 2 MHz                            | 0.80                | 1.5                 |      |

| . (1)                                | Supply current in Slow mode f <sub>CPU</sub> scaled down, all peripherals off, code executed from RAM | all peripherals off,                                                                                | External clock 16 MHz<br>f <sub>CPU</sub> = 125 kHz | 1.50                | 1.95                |      |

| I <sub>DD(SLOW)</sub> <sup>(1)</sup> |                                                                                                       | LSI internal RC<br>f <sub>CPU</sub> = 128 kHz                                                       | 1.50                                                | 1.80 <sup>(2)</sup> |                     |      |

# Table 26. Total current consumption in Run, Wait and Slow mode. General conditions for $V_{DD}$ apply, $T_A$ = -40 °C to 150 °C

1. The current due to I/O utilization is not taken into account in these values.

2. Guaranteed by design, not tested in production.

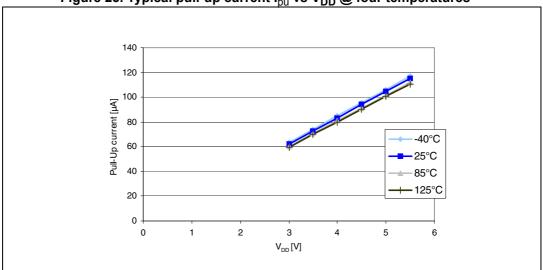

Figure 25. Typical pull-up current I<sub>pu</sub> vs V<sub>DD</sub> @ four temperatures<sup>(1)</sup>

1. The pull-up is a pure resistor (slope goes through 0).

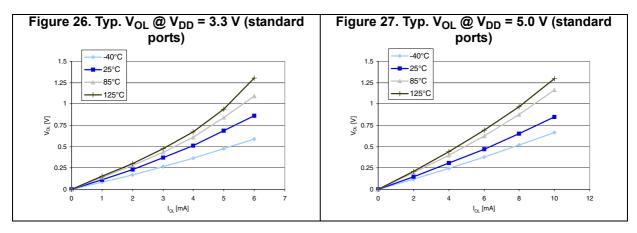

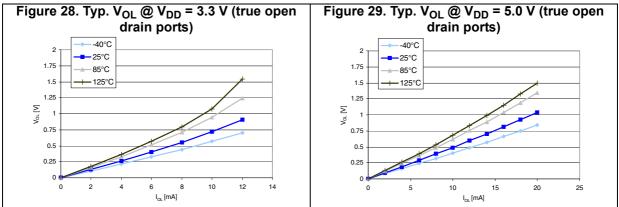

#### Typical output level curves

*Figure 26* to *Figure 35* show typical output level curves measured with output on a single pin.

DocID14395 Rev 15

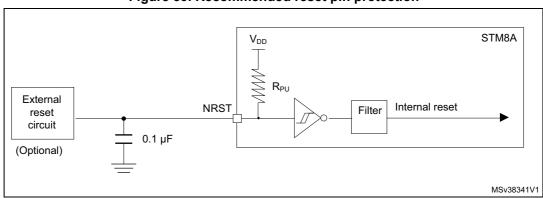

Figure 39. Recommended reset pin protection

## 10.3.8 TIM 1, 2, 3, and 4 electrical specifications

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}}$  and  $T_{\text{A}}.$

Table 40. TIM 1, 2, 3, and 4 electrical specifications

| Symbol           | Parameter                                     | Conditions | Min | Тур | Мах | Unit |

|------------------|-----------------------------------------------|------------|-----|-----|-----|------|

| f <sub>EXT</sub> | Timer external clock frequency <sup>(1)</sup> | -          | -   | -   | 24  | MHz  |

1. Not tested in production.

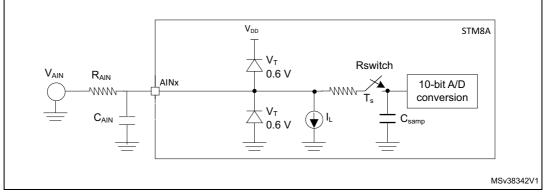

## 10.3.11 10-bit ADC characteristics

Subject to general operating conditions for  $V_{\text{DDA}},\,f_{\text{MASTER}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol              | Parameter                                   | Conditions                                                             | Min               | Тур  | Max               | Unit    |

|---------------------|---------------------------------------------|------------------------------------------------------------------------|-------------------|------|-------------------|---------|

| f <sub>ADC</sub>    | ADC clock frequency                         | -                                                                      | 111 kHz           | -    | 4 MHz             | kHz/MHz |

| V <sub>DDA</sub>    | Analog supply                               | -                                                                      | 3                 | -    | 5.5               |         |

| $V_{REF^+}$         | Positive reference voltage                  | -                                                                      | 2.75              | -    | V <sub>DDA</sub>  |         |

| V <sub>REF-</sub>   | Negative reference voltage                  | -                                                                      | V <sub>SSA</sub>  | -    | 0.5               | V       |

|                     |                                             | -                                                                      | V <sub>SSA</sub>  | -    | V <sub>DDA</sub>  |         |

| V <sub>AIN</sub>    | Conversion voltage range <sup>(1)</sup>     | Devices with<br>external V <sub>REF+</sub> /<br>V <sub>REF-</sub> pins | V <sub>REF-</sub> | -    | V <sub>REF+</sub> |         |

| C <sub>samp</sub>   | Internal sample and hold capacitor          | -                                                                      | -                 | -    | 3                 | pF      |

| ts <sup>(1)</sup>   | Sampling time                               | f <sub>ADC</sub> = 2 MHz                                               | -                 | 1.5  | -                 |         |

| LS Y                | (3 x 1/f <sub>ADC</sub> )                   | f <sub>ADC</sub> = 4 MHz                                               | -                 | 0.75 | -                 |         |

| +                   | Wakeup time from standby                    | f <sub>ADC</sub> = 2 MHz                                               | -                 | 7    | -                 |         |

| t <sub>stab</sub>   | wakeup time nom standby                     | f <sub>ADC</sub> = 4 MHz                                               | -                 | 3.5  | -                 | μs      |

| t <sub>CONV</sub>   | Total conversion time including             | f <sub>ADC</sub> = 2 MHz                                               | -                 | 7    | -                 |         |

|                     | sampling time<br>(14 x 1/f <sub>ADC</sub> ) | f <sub>ADC</sub> = 4 MHz                                               | -                 | 3.5  | -                 |         |

| R <sub>switch</sub> | Equivalent switch resistance                | -                                                                      | -                 | -    | 30                | kΩ      |

During the sample time, the sampling capacitance, C<sub>samp</sub> (3 pF typ), can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result.

#### Figure 43. Typical application with ADC

1. Legend:  $R_{AIN}$  = external resistance,  $C_{AIN}$  = capacitors,  $C_{samp}$  = internal sample and hold capacitor.

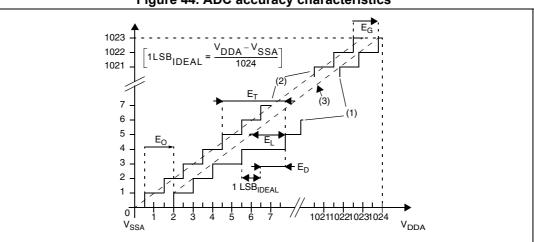

| Symbol         | Parameter                                   | Conditions               | Тур                | Max <sup>(1)</sup> | Unit |  |

|----------------|---------------------------------------------|--------------------------|--------------------|--------------------|------|--|

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       |                          | 1.4                | 3 <sup>(3)</sup>   |      |  |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 |                          |                    | 3                  |      |  |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz | 0.1                | 2                  |      |  |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> |                          | 0.9                | 1                  |      |  |

| E <sub>L</sub> | Integral linearity error <sup>(2)</sup>     |                          | 0.7                | 1.5                | LSB  |  |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       |                          | 1.9 <sup>(4)</sup> | 4 <sup>(4)</sup>   | LOD  |  |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 |                          | 1.3 <sup>(4)</sup> | 4 <sup>(4)</sup>   |      |  |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 4 MHz | 0.6 <sup>(4)</sup> | 3 <sup>(4)</sup>   |      |  |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> |                          | 1.5 <sup>(4)</sup> | 2 <sup>(4)</sup>   |      |  |

| E <sub>L</sub> | Integral linearity error <sup>(2)</sup>     |                          | 1.2 <sup>(4)</sup> | 1.5 <sup>(4)</sup> |      |  |

Table 44. ADC accuracy for  $V_{DDA} = 5 V$

1. Guaranteed by characterization results, not tested in production.

ADC accuracy vs. injection current: Any positive or negative injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 10.3.6 does not affect the ADC accuracy. 2.

TUE 2LSB can be reached on specific sales types on the whole temperature range. 3.

4. Target values.

Figure 44. ADC accuracy characteristics

1. Example of an actual transfer curve

2. The ideal transfer curve

3. End point correlation line

$E_T$  = Total unadjusted error: Maximum deviation between the actual and the ideal transfer curves.  $E_G$  = Offset error: Deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: Deviation between the last ideal transition and the last actual one.

$E_{D}^{c}$  = Differential linearity error: Maximum deviation between actual steps and the ideal one.  $E_{L}^{c}$  = Integral linearity error: Maximum deviation between any actual transition and the end point correlation line.

#### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter             | Conditions                                                            | Class <sup>(1)</sup> |

|--------|-----------------------|-----------------------------------------------------------------------|----------------------|

| LU     | Static latch-up class | $T_A = 25 \ ^\circ C$                                                 |                      |

|        |                       | tatic latch-up class $T_{A} = 85 \text{ °C}$ $T_{A} = 125 \text{ °C}$ |                      |

|        |                       |                                                                       |                      |

| Table 48. Electrica | I sensitivities |

|---------------------|-----------------|

|---------------------|-----------------|

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

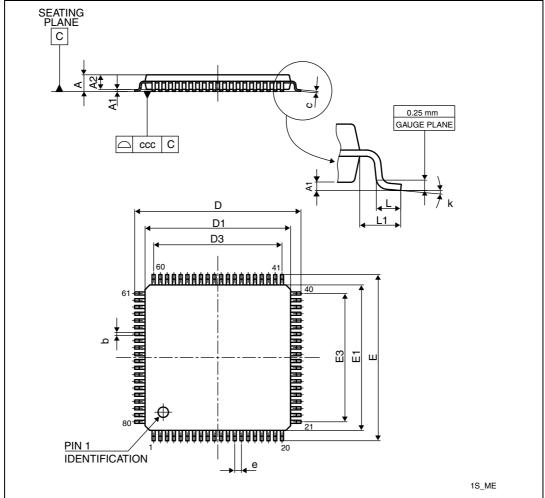

# 11 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com.* ECOPACK<sup>®</sup> is an ST trademark.

## 11.1 LQFP80 package information

Figure 45. LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| E      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

# Table 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Aug-2008 | 2<br>(continued) | Table 18: Typ. IDD(WFI)HSI vs. VDD @ fCPU = 16 MHz, peripherals= off: Replaced the source blocks 'simple USART', 'very low-endtimer (timer 4)', and 'EEPROM' with 'LINUART', timer4' and'reserved' respectively, added TMU registers.Table 20: HSE oscillator circuit diagram: Updated OPT6 and NOPT6,added OPT7 to 17 (TMU, BL)Table 21: Typical HSI frequency vs VDD: Updated OPT1 UBC[7:0],OPT4 CKAWUSEL, OPT4 PRSC [1:0], and OPT6, added OPT7 to16 (TMU).Table 23: Operating lifetime: Amended footnotes.Table 26: Total current consumption in Run, Wait and Slow mode.General conditions for VDD apply, TA = -40 °C to 150 °C: Addedparameter 'voltage and current operating conditions'.Table 28: Oscillator current consumption: Replaced.Table 28: Oscillator current consumption: Replaced.Table 29: Programming current consumption: Replaced.Table 21: Current characteristics: Replaced.Table 22: Thermal characteristics: Replaced.Table 23: HSE oscillator characteristics: Replaced.Table 23: HSE oscillator characteristics: Filled in, amended IDD(RUN)data; amended Ip_D(WFI) data; amended footnotes.Figure 13 to Figure 18: info on peripheral activity added.Table 35: Flash program memory/data EEPROM memory: RemovedACC <sub>HSI</sub> parameters and replaced with ACC <sub>HS</sub> parameters; amendeddata of fortotes.Table 37: Data memory. Updated names and data of N <sub>RW</sub> and t <sub>RET</sub> parameters.Table 37: Data memory. Updated names and data of N <sub>RW</sub> and t <sub>RET</sub> parameters.Table 37: Data memory. Updated names and data of N <sub>RW</sub> and t <sub>RET</sub> |

## Table 55. Document revision history (continued)

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30-Jan-2011 | 8<br>(continued) | Removed note 1 in <i>Table 24: General operating conditions</i> and note<br>1 below <i>Figure 11: fCPUmax versus VDD.</i><br>Removed note 3 in <i>Table 26: Total current consumption in Run, Wait</i><br><i>and Slow mode. General conditions</i> for VDD apply, $TA = -40$ °C to<br>150 °C.<br>Removed note 2 in <i>Table 31: HSE external clock characteristics</i> and<br><i>Table 35: Flash program memory/data EEPROM memory</i><br>Removed note 1 in <i>Table 37: Data memory</i> . Modified T <sub>WE</sub> maximum<br>value in <i>Table 36: Flash program memory</i> and <i>Table 37: Data</i><br><i>memory</i> .<br>Added t <sub>IFP(NRST)</sub> and renamed V <sub>F(NRST)</sub> t <sub>IFP</sub> in <i>Table 39: NRST pin</i><br><i>characteristics</i> .<br>Added recommendation concerning NRST pin level, and power<br>consumption sensitive applications, above <i>Figure 39:</i><br><i>Recommended reset pin protection,</i> and updated external capacitor<br>value.<br>Updated <i>Note 1</i> in <i>Table 40: TIM 1, 2, 3, and 4 electrical</i><br><i>specifications</i> .<br>Updated <i>Note 1</i> in <i>Table 41: SPI characteristics</i> .<br>Moved know limitations to separate errata sheet.<br>Added "not recommended for new design" note to device family 51,<br>memory size 7 and 9, and temperature range B, in <i>Figure 60:</i><br><i>STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information</i><br><i>scheme1</i> .<br>Added Raisonance compiler in <i>Section 13.2: Software tools</i> . |

| 18-Jul-2012 | 9                | Updated wildcards of document part numbers.<br>Added VFQFPN package.<br>Added STM8AF62A6 part number.<br><i>Table 1: Device summary</i> updated footnote <i>1</i> and added footnote <i>2</i> .<br><i>Table: STM8AF52xx product line-up with CAN</i> and <i>Table:</i><br><i>STM8AF62xx product line-up without CAN</i> : added "P" version for all<br>order codes; updated size of data EEPROM for 64K devices to 2K<br>instead of 1.5K; updated RAM.<br><i>Figure 1: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax block</i><br><i>diagram</i> : updated POR, BOR and WDG; removed PDR; added<br>legend.<br><i>Section 5.4: Flash program and data EEPROM</i> : removed non<br>relevant bullet points and added a sentence about the factory<br>program.<br>Added <i>Table 4: Peripheral clock gating bits (CLK_PCKENR1)</i> and<br>updated <i>Table 5: Peripheral clock gating bits (CLK_PCKENR2)</i><br><i>Section : ADC features</i> : updated ADC input range.<br><i>Table 12: Memory model 128K:</i> updated RAM size, RAM end<br>addresses, and stack roll-over addresses; updated footnote <i>1</i><br><i>Table 18: Option bytes:</i> updated factory default setting for NOPT17;<br>updated footnotes.<br><i>Table 20: Voltage characteristics:</i> updated V <sub>DDX</sub> - V <sub>DD</sub> to V <sub>DDX</sub> - V <sub>SS</sub> .<br><i>Table 24: General operating conditions:</i> updated V <sub>CAP</sub> -                                                                                                        |