Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    |                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6286tcy |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.7 Timers

#### 5.7.1 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications. The watchdog timer activity is controlled by the application program or option bytes. Once the watchdog is activated, it cannot be disabled by the user program without going through reset.

#### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application timing perfectly. The application software must refresh the counter before time-out and during a limited time window. If the counter is refreshed outside this time window, a reset is issued.

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure. If the hardware watchdog feature is enabled through the device option bits, the watchdog is automatically enabled at power-on, and generates a reset unless the key register is written by software before the counter reaches the end of count.

### 5.7.2 Auto-wakeup counter

This counter is used to cyclically wakeup the device in Active-halt mode. It can be clocked by the internal 128 kHz internal low-frequency RC oscillator or external clock.

LSI clock can be internally connected to TIM3 input capture channel 1 for calibration.

#### 5.7.3 Beeper

This function generates a rectangular signal in the range of 1, 2 or 4 kHz which can be output on a pin. This is useful when audible sounds without interference need to be generated for use in the application.

### 5.7.4 Advanced control and general purpose timers

STM8A devices described in this datasheet, contain up to three 16-bit advanced control and general purpose timers providing nine CAPCOM channels in total. A CAPCOM channel can be used either as input compare, output compare or PWM channel. These timers are named TIM1, TIM2 and TIM3.

Detailed feature list:

- Full duplex, asynchronous communications

- NRZ standard format (mark/space)

- High-precision baud rate generator system

- Common programmable transmit and receive baud rates up to f<sub>MASTER</sub>/16

- Programmable data word length (8 or 9 bits)

- Configurable stop bits: Support for 1 or 2 stop bits

- LIN master mode:

- LIN break and delimiter generation

- LIN break and delimiter detection with separate flag and interrupt source for readback checking.

- Transmitter clock output for synchronous communication

- Separate enable bits for transmitter and receiver

- Transfer detection flags:

- Receive buffer full

- Transmit buffer empty

- End of transmission flags

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Six interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Parity error

- LIN break and delimiter detection

- Two interrupt vectors:

- Transmitter interrupt

- Receiver interrupt

- Reduced power consumption mode

- Wakeup from mute mode (by idle line detection or address mark detection)

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line

# 5.10 Input/output specifications

The product features four I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

- Caution: In STM8AF5286UC device, the following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor,

- configured as output push-pull low.

|        | Pir    |        | mber                          |                     | WOAF 5202/02/A           |      | 1        | npu |                |           | Out   |                  | <u>.</u> |                                      |                                  | ,                                                    |

|--------|--------|--------|-------------------------------|---------------------|--------------------------|------|----------|-----|----------------|-----------|-------|------------------|----------|--------------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | STM8AF62xx<br>LQFP32/VFQFPN32 | STM8AF52x6 VFQFPN32 | Pin name                 | Type | Floating | Wpu | Ext. interrupt | High sink | Speed | OD               | Ъ        | Main<br>function<br>(after<br>reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 55     | 46     | -      | -                             | -                   | PG3                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G3                              | -                                | -                                                    |

| 56     | 47     | -      | -                             | -                   | PG4                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G4                              | -                                | -                                                    |

| 57     | 48     | -      | -                             | -                   | PI0                      | I/O  | Х        | Х   | 1              | -         | 01    | Х                | Х        | Port I0                              | -                                | -                                                    |

| 58     | -      | -      | -                             | -                   | PI1                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I1                              | -                                | -                                                    |

| 59     | -      | -      | -                             | -                   | Pl2                      | I/O  | Х        | Х   | 1              | -         | 01    | Х                | Х        | Port I2                              | -                                | -                                                    |

| 60     | -      | -      | -                             | -                   | PI3                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I3                              | -                                | -                                                    |

| 61     | -      | -      | -                             | -                   | PI4                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I4                              | -                                | -                                                    |

| 62     | -      | -      | -                             | -                   | PI5                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I5                              | -                                | -                                                    |

| 63     | 49     | -      | -                             | -                   | PG5                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G5                              | -                                | -                                                    |

| 64     | 50     | -      | -                             | -                   | PG6                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G6                              | -                                | -                                                    |

| 65     | 51     | -      | -                             | -                   | PG7                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G7                              | -                                | -                                                    |

| 66     | 52     | -      | -                             | -                   | PE4                      | I/O  | Х        | Х   | Х              | -         | 01    | Х                | Х        | Port E4                              | -                                | -                                                    |

| 67     | 53     | 37     | -                             | -                   | PE3/TIM1_BKIN            | I/O  | Х        | х   | х              | -         | 01    | х                | х        | Port E3                              | Timer 1 -<br>break input         | -                                                    |

| 68     | 54     | 38     | -                             | -                   | PE2/I <sup>2</sup> C_SDA | I/O  | Х        | -   | Х              | -         | 01    | T <sup>(3)</sup> | -        | Port E2                              | l <sup>2</sup> C data            | -                                                    |

| 69     | 55     | 39     | -                             | -                   | PE1/I <sup>2</sup> C_SCL | I/O  | Х        | -   | Х              | -         | 01    | T <sup>(3)</sup> | -        | Port E1                              | I <sup>2</sup> C clock           | -                                                    |

| 70     | 56     | 40     | -                             | -                   | PE0/CLK_CCO              | I/O  | X        | х   | х              | -         | O3    | х                | x        | Port E0                              | Configurab<br>le clock<br>output | -                                                    |

| 71     | -      | -      | -                             | -                   | PI6                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I6                              | -                                | -                                                    |

| 72     | -      | -      | -                             | -                   | PI7                      | I/O  | X        | Х   | -              | -         | 01    | Х                | Х        | Port I7                              | -                                | -                                                    |

| 73     | 57     | 41     | 25                            | 25                  | PD0/TIM3_CH2             | I/O  | x        | x   | x              | HS        | O3    | х                | x        | Port D0                              | Timer 3 -<br>channel 2           | TIM1_BKIN<br>[AFR3]/<br>CLK_CCO<br>[AFR2]            |

| 74     | 58     | 42     | 26                            | 26                  | PD1/SWIM <sup>(4)</sup>  | I/O  | х        | x   | х              | HS        | 04    | х                | х        | Port D1                              | SWIM data interface              | -                                                    |

| 75     | 59     | 43     | 27                            | 27                  | PD2/TIM3_CH1             | I/O  | X        | х   | х              | HS        | O3    | х                | х        | Port D2                              | Timer 3 -<br>channel 1           | TIM2_CH3<br>[AFR1]                                   |

| 76     | 60     | 44     | 28                            | 28                  | PD3/TIM2_CH2             | I/O  | x        | х   | х              | HS        | O3    | х                | х        | Port D3                              | Timer 2 -<br>channel 2           | ADC_ETR<br>[AFR0]                                    |

| 77     | 61     | 45     | 29                            | 29                  | PD4/TIM2_CH1/<br>BEEP    | I/O  | x        | х   | х              | HS        | O3    | х                | х        | Port D4                              | Timer 2 -<br>channel 1           | BEEP output<br>[AFR7]                                |

## Table 11. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description (continued)

|        | Pir    | n nu   | mber                          |                     |                        |      | h        | npu | t              |           | Out   | put | - |                                      |                                  |                                                      |

|--------|--------|--------|-------------------------------|---------------------|------------------------|------|----------|-----|----------------|-----------|-------|-----|---|--------------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | STM8AF62xx<br>LQFP32/VFQFPN32 | STM8AF52x6 VFQFPN32 | Pin name               | Type | Floating | Wpu | Ext. interrupt | High sink | Speed | OD  | Ъ | Main<br>function<br>(after<br>reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 78     | 62     | 46     | 30                            | 30                  | PD5/<br>LINUART_TX     | I/O  | x        | х   | x              | -         | 01    | х   | x | Port D5                              | LINUART<br>data<br>transmit      | -                                                    |

| 79     | 63     | 47     | 31                            | 31                  | PD6/<br>LINUART_RX     | I/O  | x        | х   | х              | -         | 01    | х   | x | Port D6                              | LINUART<br>data<br>receive       | -                                                    |

| 80     | 64     | 48     | 32                            | 32                  | PD7/TLI <sup>(5)</sup> | I/O  | x        | х   | х              | -         | 01    | х   | х | Port D7                              | Top level<br>interrupt           | -                                                    |

#### Table 11. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description (continued)

In Halt/Active-halt mode, this pin behaves as follows:

The input/output path is disabled.

If the HSE clock is used for wakeup, the internal weak pull-up is disabled.

If the HSE clock is off, the internal weak pull-up setting is used. It is configured through Px\_CR1[7:0] bits of the corresponding port control register. Px\_CR1[7:0] bits must be set correctly to ensure that the pin is not left floating in Halt/Active halt mode. Halt/Active-halt mode.

2. SPI and USTART are not available in STM8AF5286UC, refer to Figure 7: STM8AF52x6 VFQFPN32 32-pin pinout for the pin names.

In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, week pull-up and protection diode to V<sub>DD</sub> are not implemented)

4. The PD1 pin is in input pull-up during the reset phase and after reset release.

5. If this pin is configured as interrupt pin, it will trigger the TLI.

# 6.2 Alternate function remapping

As shown in the rightmost column of *Table 11*, some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function remap) option bits. Refer to *Section 9: Option bytes on page 54*. When the remapping option is active, the default alternate function is no longer available.

To use an alternate function, the corresponding peripheral must be enabled in the peripheral registers.

Alternate function remapping does not effect GPIO capabilities of the I/O ports (see the GPIO section of STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016).

| Address Block |        | Register label | Register name                     | Reset               |

|---------------|--------|----------------|-----------------------------------|---------------------|

|               |        | -              |                                   | status              |

| 0x00 5014     |        | PE_ODR         | Port E data output latch register | 0x00                |

| 0x00 5015     |        | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016     | Port E | PE_DDR         | Port E data direction register    | 0x00                |

| 0x00 5017     |        | PE_CR1         | Port E control register 1         | 0x00                |

| 0x00 5018     |        | PE_CR2         | Port E control register 2         | 0x00                |

| 0x00 5019     |        | PF_ODR         | Port F data output latch register | 0x00                |

| 0x00 501A     |        | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B     | Port F | PF_DDR         | Port F data direction register    | 0x00                |

| 0x00 501C     |        | PF_CR1         | Port F control register 1         | 0x00                |

| 0x00 501D     |        | PF_CR2         | Port F control register 2         | 0x00                |

| 0x00 501E     |        | PG_ODR         | Port G data output latch register | 0x00                |

| 0x00 501F     |        | PG_IDR         | Port G input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5020     | Port G | PG_DDR         | Port G data direction register    | 0x00                |

| 0x00 5021     |        | PG_CR1         | Port G control register 1         | 0x00                |

| 0x00 5022     |        | PG_CR2         | Port G control register 2         | 0x00                |

| 0x00 5023     |        | PH_ODR         | Port H data output latch register | 0x00                |

| 0x00 5024     |        | PH_IDR         | Port H input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5025     | Port H | PH_DDR         | Port H data direction register    | 0x00                |

| 0x00 5026     |        | PH_CR1         | Port H control register 1         | 0x00                |

| 0x00 5027     |        | PH_CR2         | Port H control register 2         | 0x00                |

| 0x00 5028     |        | PI_ODR         | Port I data output latch register | 0x00                |

| 0x00 5029     |        | PI_IDR         | Port I input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 502A     | Port I | PI_DDR         | Port I data direction register    | 0x00                |

| 0x00 502B     |        | PI_CR1         | Port I control register 1         | 0x00                |

| 0x00 502C     |        | PI_CR2         | Port I control register 2         | 0x00                |

| Table 13 I/O | port hardware register map (continued) |   |

|--------------|----------------------------------------|---|

|              | port naruware register map (continueu) | , |

1. Depends on the external circuitry.

| Symbol                               | Parameter                     | Con                                                   | ditions                                             | Тур  | Мах                 | Unit |

|--------------------------------------|-------------------------------|-------------------------------------------------------|-----------------------------------------------------|------|---------------------|------|

|                                      |                               | All peripherals                                       | f <sub>CPU</sub> = 24 MHz 1 ws                      | 8.7  | 16.8 <sup>(2)</sup> |      |

|                                      |                               | clocked, code                                         | f <sub>CPU</sub> = 16 MHz                           | 7.4  | 14                  |      |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>  | Supply current in<br>Run mode | executed from Flash program memory,                   | f <sub>CPU</sub> = 8 MHz                            | 4.0  | 7.4 <sup>(2)</sup>  |      |

|                                      |                               | HSE external clock                                    | f <sub>CPU</sub> = 4 MHz                            | 2.4  | 4.1 <sup>(2)</sup>  |      |

|                                      |                               | (without resonator)                                   | f <sub>CPU</sub> = 2 MHz                            | 1.5  | 2.5                 |      |

|                                      |                               |                                                       | f <sub>CPU</sub> = 24 MHz                           | 4.4  | 6.0 <sup>(2)</sup>  |      |

|                                      | Supply current in Run mode    | All peripherals clocked, code                         | f <sub>CPU</sub> = 16 MHz                           | 3.7  | 5.0                 |      |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>  |                               | executed from RAM,                                    | f <sub>CPU</sub> = 8 MHz                            | 2.2  | 3.0 <sup>(2)</sup>  |      |

|                                      |                               | HSE external clock<br>(without resonator)             | f <sub>CPU</sub> = 4 MHz                            | 1.4  | 2.0 <sup>(2)</sup>  |      |

|                                      |                               | , , ,                                                 | f <sub>CPU</sub> = 2 MHz                            | 1.0  | 1.5                 | mA   |

|                                      |                               |                                                       | f <sub>CPU</sub> = 24 MHz                           | 2.4  | 3.1 <sup>(2)</sup>  |      |

|                                      |                               | CPU stopped, all                                      | f <sub>CPU</sub> = 16 MHz                           | 1.65 | 2.5                 |      |

| I <sub>DD(WFI)</sub> <sup>(1)</sup>  | Supply current in Wait mode   | peripherals off, HSE                                  | f <sub>CPU</sub> = 8 MHz                            | 1.15 | 1.9 <sup>(2)</sup>  |      |

|                                      |                               | external clock                                        | f <sub>CPU</sub> = 4 MHz                            | 0.90 | 1.6 <sup>(2)</sup>  |      |

|                                      |                               |                                                       | f <sub>CPU</sub> = 2 MHz                            | 0.80 | 1.5                 |      |

| (1)                                  | Supply current in             | f <sub>CPU</sub> scaled down,<br>all peripherals off, | External clock 16 MHz<br>f <sub>CPU</sub> = 125 kHz | 1.50 | 1.95                |      |

| I <sub>DD(SLOW)</sub> <sup>(1)</sup> | Slow mode                     | code executed from RAM                                | LSI internal RC<br>f <sub>CPU</sub> = 128 kHz       | 1.50 | 1.80 <sup>(2)</sup> |      |

# Table 26. Total current consumption in Run, Wait and Slow mode. General conditions for $V_{DD}$ apply, $T_A$ = -40 °C to 150 °C

1. The current due to I/O utilization is not taken into account in these values.

2. Guaranteed by design, not tested in production.

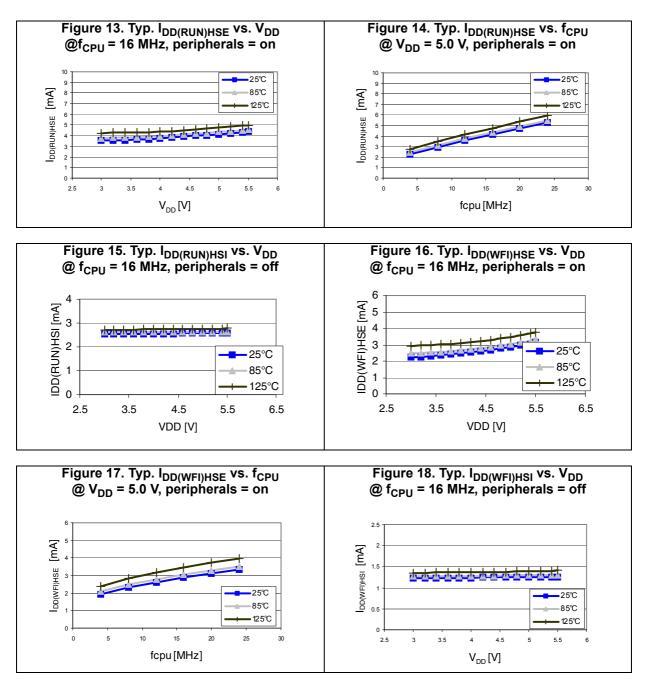

#### **Current consumption curves**

*Figure 13* to *Figure 18* show typical current consumption measured with code executing in RAM.

DocID14395 Rev 15

## **10.3.4** Internal clock sources and timing characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

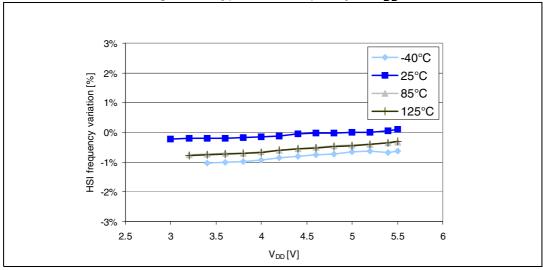

#### High-speed internal RC oscillator (HSI)

| Symbol               | Parameter                                    | Conditions                                                                                                                               | Min | Тур | Max              | Unit |

|----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------|------|

| f <sub>HSI</sub>     | Frequency                                    | -                                                                                                                                        | -   | 16  | -                | MHz  |

| ACC <sub>HS</sub>    | HSI oscillator user trimming accuracy        | Trimmed by the application for any $V_{DD}$ and $T_{A}$ conditions                                                                       | -1  | -   | 1                | %    |

|                      | HSI oscillator accuracy (factory calibrated) | $\label{eq:V_DD} \begin{split} V_{DD} &= 3.0 \ V \leq V_{DD} \leq 5.5 \ V, \\ -40 \ ^{\circ}C \leq T_A \leq 150 \ ^{\circ}C \end{split}$ | -5  | -   | 5                |      |

| t <sub>su(HSI)</sub> | HSI oscillator wakeup time                   | -                                                                                                                                        | -   | -   | 2 <sup>(1)</sup> | μs   |

#### Table 33. HSI oscillator characteristics

1. Guaranteed by characterization results, not tested in production.

Figure 21. Typical HSI frequency vs  $V_{DD}$

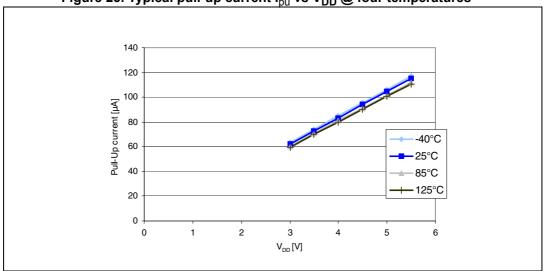

Figure 25. Typical pull-up current I<sub>pu</sub> vs V<sub>DD</sub> @ four temperatures<sup>(1)</sup>

1. The pull-up is a pure resistor (slope goes through 0).

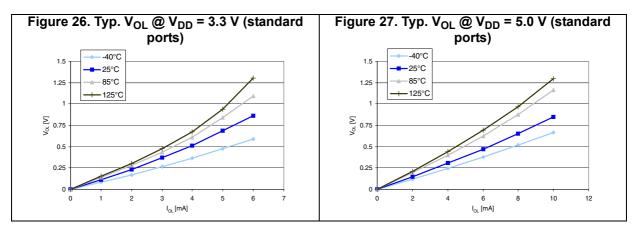

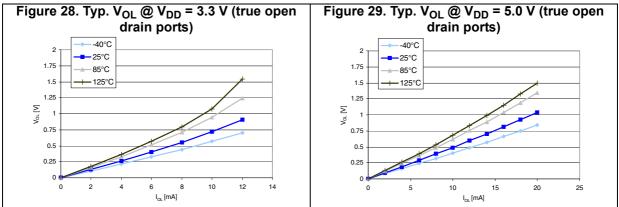

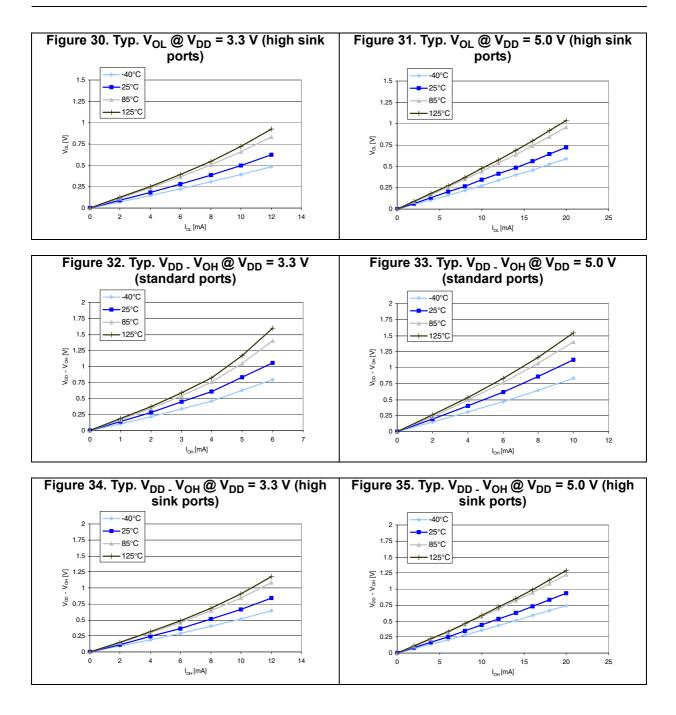

#### Typical output level curves

*Figure 26* to *Figure 35* show typical output level curves measured with output on a single pin.

DocID14395 Rev 15

DocID14395 Rev 15

# 10.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                                             | Conditions             | Min                         | Тур | Max                 | Unit |

|-------------------------|-------------------------------------------------------|------------------------|-----------------------------|-----|---------------------|------|

| V <sub>IL(NRST)</sub>   | NRST low-level input voltage <sup>(1)</sup>           | -                      | V <sub>SS</sub>             | -   | $0.3 \times V_{DD}$ |      |

| V <sub>IH(NRST)</sub>   | NRST high-level input voltage <sup>(1)</sup>          | -                      | $0.7 	ext{ x V}_{	ext{DD}}$ | -   | V <sub>DD</sub>     | V    |

| V <sub>OL(NRST)</sub>   | NRST low-level output voltage <sup>(1)</sup>          | I <sub>OL</sub> = 3 mA | -                           | -   | 0.6                 |      |

| R <sub>PU(NRST)</sub>   | NRST pull-up resistor                                 | -                      | 30                          | 40  | 60                  | kΩ   |

| t <sub>IFP</sub>        | NRST input filtered pulse <sup>(1)</sup>              | -                      | 85                          | -   | 315                 |      |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse duration <sup>(2)</sup> | -                      | 500                         | -   | -                   | ns   |

| Table 39.  | NRST | pin | characteristics |

|------------|------|-----|-----------------|

| 10.010 001 |      | P   | onaraotoriotioo |

1. Guaranteed by characterization results, not tested in production.

2. Guaranteed by design, not tested in production.

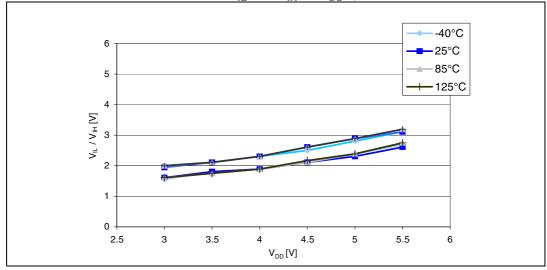

## Figure 36. Typical NRST $V_{\rm IL}$ and $V_{\rm IH}$ vs $V_{\rm DD}$ @ four temperatures

|                |                                             | ,                        |                    | 1                  |      |

|----------------|---------------------------------------------|--------------------------|--------------------|--------------------|------|

| Symbol         | Parameter                                   | Conditions               | Тур                | Max <sup>(1)</sup> | Unit |

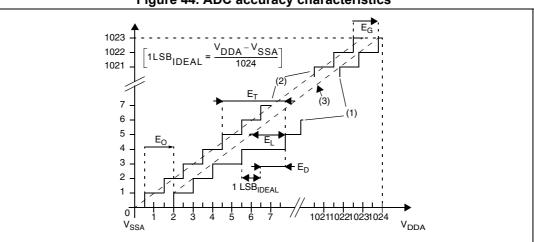

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       |                          | 1.4                | 3 <sup>(3)</sup>   |      |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 |                          | 0.8                | 3                  |      |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz | 0.1                | 2                  |      |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> |                          | 0.9                | 1                  |      |

| E <sub>L</sub> | Integral linearity error <sup>(2)</sup>     |                          | 0.7                | 1.5                | LSB  |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       |                          | 1.9 <sup>(4)</sup> | 4 <sup>(4)</sup>   | LOD  |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 |                          | 1.3 <sup>(4)</sup> | 4 <sup>(4)</sup>   |      |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 4 MHz | 0.6 <sup>(4)</sup> | 3 <sup>(4)</sup>   |      |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> |                          | 1.5 <sup>(4)</sup> | 2 <sup>(4)</sup>   |      |

| E <sub>L</sub> | Integral linearity error <sup>(2)</sup>     |                          | 1.2 <sup>(4)</sup> | 1.5 <sup>(4)</sup> |      |

Table 44. ADC accuracy for  $V_{DDA} = 5 V$

1. Guaranteed by characterization results, not tested in production.

ADC accuracy vs. injection current: Any positive or negative injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 10.3.6 does not affect the ADC accuracy. 2.

TUE 2LSB can be reached on specific sales types on the whole temperature range. 3.

4. Target values.

Figure 44. ADC accuracy characteristics

1. Example of an actual transfer curve

2. The ideal transfer curve

3. End point correlation line

$E_T$  = Total unadjusted error: Maximum deviation between the actual and the ideal transfer curves.  $E_G$  = Offset error: Deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: Deviation between the last ideal transition and the last actual one.

$E_{D}^{c}$  = Differential linearity error: Maximum deviation between actual steps and the ideal one.  $E_{L}^{c}$  = Integral linearity error: Maximum deviation between any actual transition and the end point correlation line.

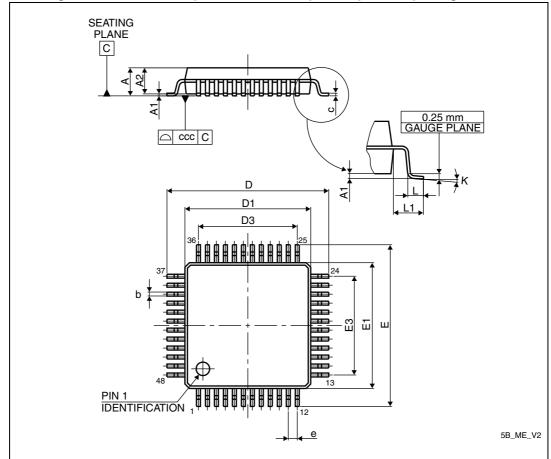

# 11.3 LQFP48 package information

Figure 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

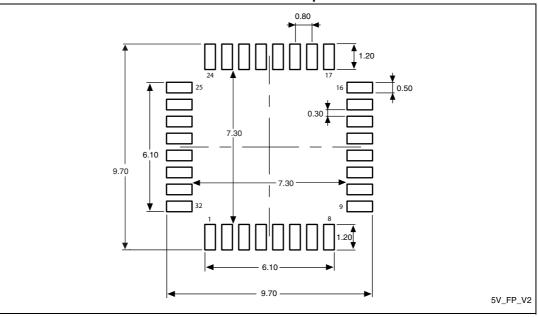

# Figure 55. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

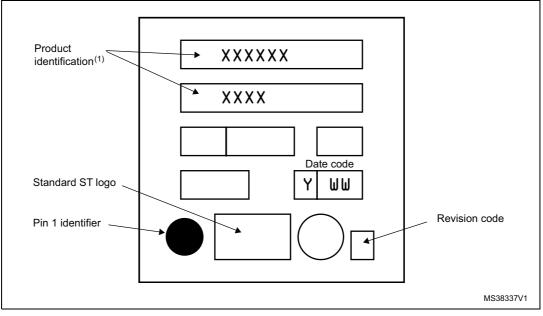

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 56. LQFP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.

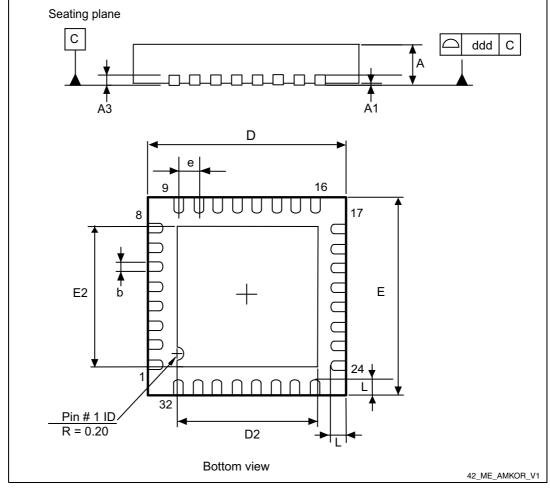

# 11.5 VFQFPN32 package information

Figure 57. VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package outline

1. Drawing is not to scale.

57

# 13 STM8 development tools

Development tools for the STM8A microcontrollers include the

- STice emulation system offering tracing and code profiling

- STVD high-level language debugger including assembler and visual development environment seamless integration of third party C compilers

- STVP Flash programming software

In addition, the STM8A comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

# 13.1 Emulation and in-circuit debugging tools

The STM8 tool line includes the STice emulation system offering a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8A application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full-featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including tracing, profiling and code coverage analysis to help detect execution bottlenecks and dead code.

In addition, STice offers in-circuit debugging and programming of STM8A microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows users to order exactly what they need to meet their development requirements and to adapt their emulation system to support existing and future ST microcontrollers.

## 13.1.1 STice key features

- Program and data trace recording up to 128 K records

- Advanced breakpoints with up to 4 levels of conditions

- Data breakpoints

- Real-time read/write of all device resources during emulation

- Occurrence and time profiling and code coverage analysis (new features)

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- 1 input and 2 output triggers

- USB 2.0 high-speed interface to host PC

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows users to specify the components they need to meet their development requirements and adapt to future requirements

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

# **13.3 Programming tools**

During the development cycle, STice provides in-circuit programming of the STM8A Flash microcontroller on the application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8A.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.