Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 38                                                                    |

| Program Memory Size        | 64KB (64K × 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 10x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6288tdy |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

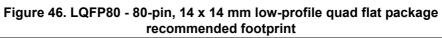

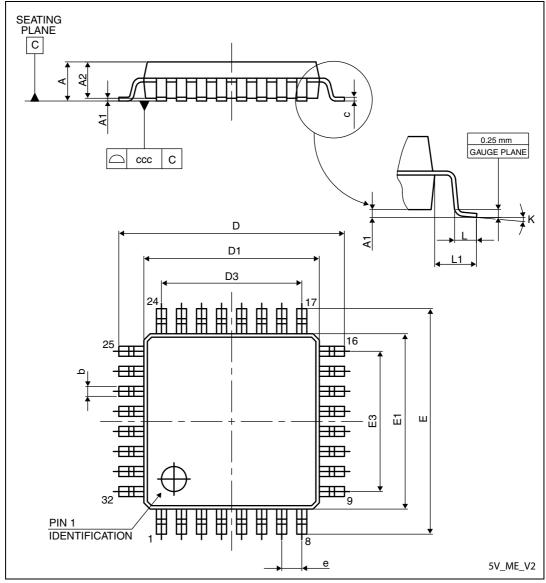

| Figure 48.<br>Figure 49. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline              |

|--------------------------|--------------------------------------------------------------------------------|

|                          | recommended footprint                                                          |

| Figure 50.               | LQFP64 marking example (package top view)96                                    |

| Figure 51.               | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                |

| Figure 52.               | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                        |

| -                        | recommended footprint                                                          |

| Figure 53.               | LQFP48 marking example (package top view)                                      |

| Figure 54.               | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline                |

| Figure 55.               | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                        |

| U                        | recommended footprint                                                          |

| Figure 56.               | LQFP32 marking example (package top view)                                      |

| Figure 57.               | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad      |

| 0                        | flat package outline                                                           |

| Figure 58.               | VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad    |

| U                        | flat package recommended footprint                                             |

| Figure 59.               | VFQFPN32 marking example (package top view)                                    |

| Figure 60.               | STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information scheme <sup>1</sup> |

# 2 Description

The STM8AF526x/8x/Ax and STM8AF6269/8x/Ax automotive 8-bit microcontrollers described in this datasheet offer from 32 Kbyte to 128 Kbyte of non volatile memory and integrated true data EEPROM. They are referred to as high density STM8A devices in STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

The STM8AF52 series features a CAN interface.

All devices of the STM8A product line provide the following benefits: reduced system cost, performance and robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, wtachdog, and brown-out reset.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map, and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8A family thanks to their advanced core which is made in a state-of-the art technology for automotive applications with 3.3 V to 5.5 V operating supply.

All STM8A and ST7 microcontrollers are supported by the same tools including STVD/STVP development environment, the STice emulator and a low-cost, third party incircuit debugging tool.

# 3 Product line-up

| Order code   | Package           | High<br>density<br>Flash<br>program<br>memory<br>(bytes) | RAM<br>(bytes) | Data<br>EEPROM<br>(bytes) | 10-bit<br>A/D<br>chan. | Timers<br>(IC/OC/PWM)                                     | Serial<br>interfaces                     | l/0<br>wakeup<br>pins |  |

|--------------|-------------------|----------------------------------------------------------|----------------|---------------------------|------------------------|-----------------------------------------------------------|------------------------------------------|-----------------------|--|

| STM8AF/P52AA | LQFP80            | 128 K                                                    |                |                           |                        |                                                           |                                          | 68/37                 |  |

| STM8AF/P528A | (14x14)           | 64 K                                                     |                | 2 K                       |                        | 1x8-bit: TIM4<br>3x16-bit: TIM1,<br>TIM2, TIM3<br>(9/9/9) | CAN,<br>LIN(UART),<br>SPI,<br>USART, I²C | 00/37                 |  |

| STM8AF/P52A9 |                   | 128 K                                                    |                |                           | 16                     |                                                           |                                          |                       |  |

| STM8AF/P5289 | LQFP64<br>(10x10) | 64 K                                                     |                |                           |                        |                                                           |                                          | 52/36                 |  |

| STM8AF/P5269 | ()                | 32 K                                                     |                | 1 K                       |                        |                                                           |                                          |                       |  |

| STM8AF/P52A8 |                   | 128 K                                                    | 6 K            | 2 1                       |                        |                                                           |                                          |                       |  |

| STM8AF/P5288 | LQFP48<br>(7x7)   | 64 K                                                     |                | 2 K                       | 10                     |                                                           |                                          | 38/35                 |  |

| STM8AF/P5268 | (17.17)           | 32 K                                                     |                | 1K                        |                        |                                                           |                                          |                       |  |

| STM8AF/P5286 |                   | 64 K                                                     |                |                           |                        | 1x8-bit: TIM4                                             | CAN,                                     |                       |  |

| STM8AF/P52A6 | VFQFPN32<br>(5x5) | 128 K                                                    |                | 2 K                       | 6                      | 3x16-bit: TIM1,<br>TIM2, TIM3<br>(8/8/8)                  | LIN(UART),<br>I <sup>2</sup> C           | 25/24                 |  |

#### Table 2. STM8AF526x/8x/Ax product line-up with CAN

#### Table 3. STM8AF6269/8x/Ax product line-up without CAN

| Order code   | Package           | High<br>density<br>Flash<br>program<br>memory<br>(bytes) | RAM<br>(bytes) | Data<br>EEPROM<br>(bytes) | 10-bit<br>A/D<br>chan. | Timers<br>(IC/OC/PWM)                                     | Serial<br>interfaces             | l/0<br>wakeup<br>pins |  |

|--------------|-------------------|----------------------------------------------------------|----------------|---------------------------|------------------------|-----------------------------------------------------------|----------------------------------|-----------------------|--|

| STM8AF/P62AA | LQFP80            | 128 K                                                    |                |                           |                        |                                                           |                                  | 68/37                 |  |

| STM8AF/P628A | (14x14)           | 64 K                                                     |                | 2 K                       |                        | 1x8-bit: TIM4<br>3x16-bit: TIM1,<br>TIM2, TIM3<br>(9/9/9) | LIN(UART),<br>SPI,<br>USART, I²C | 00/37                 |  |

| STM8AF/P62A9 |                   | 128 K                                                    |                |                           | 16                     |                                                           |                                  |                       |  |

| STM8AF/P6289 | LQFP64<br>(10x10) | 64 K                                                     |                | 2 K                       |                        |                                                           |                                  | 52/36                 |  |

| STM8AF/P6269 | ()                | 32 K                                                     |                | 1 K                       |                        |                                                           |                                  |                       |  |

| STM8AF/P62A8 | LQFP48            | 128 K                                                    | 6 K            |                           | 10                     |                                                           |                                  | 38/35                 |  |

| STM8AF/P6288 | (7x7)             |                                                          |                |                           | 10                     |                                                           |                                  | 30/35                 |  |

| STM8AF/P6286 | LQFP32<br>(7x7)   | 64 K                                                     |                | 2 K                       | 7                      | 1x8-bit: TIM4<br>3x16-bit: TIM1,                          | LIN(UART),                       | 25/22                 |  |

| STM8AF/P62A6 | VFQFPN32<br>(5x5) | 128 K                                                    |                |                           | 1                      | TIM2, TIM3<br>(8/8/8)                                     | SPI, I²C                         | 25/23                 |  |

Legend: ADC: Analog-to-digital converter beCAN: Controller area network BOR: Brownout reset I<sup>2</sup>C: Inter-integrated circuit multimaster interface IWDG: Independent window watchdog LINUART: Local interconnect network universal asynchronous receiver transmitter POR: Power on reset SPI: Serial peripheral interface SWIM: Single wire interface module USART: Universal synchronous asynchronous receiver transmitter Window WDG: Window watchdog

## 5.5.3 128 kHz low-speed internal RC oscillator (LSI)

The frequency of this clock is 128 kHz and it is independent from the main clock. It drives the independent watchdog or the AWU wakeup timer.

In systems which do not need independent clock sources for the watchdog counters, the 128 kHz signal can be used as the system clock. This configuration has to be enabled by setting an option byte (OPT3/OPT3N, bit LSI\_EN).

## 5.5.4 24 MHz high-speed external crystal oscillator (HSE)

The external high-speed crystal oscillator can be selected to deliver the main clock in normal Run mode. It operates with quartz crystals and ceramic resonators.

- Frequency range: 1 MHz to 24 MHz

- Crystal oscillation mode: preferred fundamental

- I/Os: standard I/O pins multiplexed with OSCIN, OSCOUT

### 5.5.5 External clock input

An external clock signal can be applied to the OSCIN input pin of the crystal oscillator. The frequency range is 0 to 24 MHz.

### 5.5.6 Clock security system (CSS)

The clock security system protects against a system stall in case of an external crystal clock failure.

In case of a clock failure an interrupt is generated and the high-speed internal clock (HSI) is automatically selected with a frequency of 2 MHz (16 MHz/8).

|             | <b>J</b>         |

|-------------|------------------|

| Control bit | Peripheral       |

| PCKEN17     | TIM1             |

| PCKEN16     | TIM3             |

| PCKEN15     | TIM2             |

| PCKEN14     | TIM4             |

| PCKEN13     | LINUART          |

| PCKEN12     | USART            |

| PCKEN11     | SPI              |

| PCKEN10     | l <sup>2</sup> C |

#### Table 4. Peripheral clock gating bits (CLK\_PCKENR1)

## 5.8 Analog to digital converter (ADC)

The STM8A products described in this datasheet contain a 10-bit successive approximation ADC with up to 16 multiplexed input channels, depending on the package.

The ADC name differs between the datasheet and the STM8A/S reference manual (see *Table 8*).

| Table | 8. | ADC | naming |

|-------|----|-----|--------|

|-------|----|-----|--------|

| Peripheral name in datasheet | Peripheral name in reference manual<br>(RM0016) |

|------------------------------|-------------------------------------------------|

| ADC                          | ADC2                                            |

#### **ADC** features

- 10-bit resolution

- Single and continuous conversion modes

- Programmable prescaler: f<sub>MASTER</sub> divided by 2 to 18

- Conversion trigger on timer events, and external events

- Interrupt generation at end of conversion

- Selectable alignment of 10-bit data in 2 x 8 bit result registers

- Shadow registers for data consistency

- ADC input range: V<sub>SSA</sub> ≤V<sub>IN</sub> ≤V<sub>DDA</sub>

- Schmitt-trigger on analog inputs can be disabled to reduce power consumption

## 5.9 Communication interfaces

The following sections give a brief overview of the communication peripheral. Some peripheral names differ between the datasheet and STM8S series and STM8AF series 8-bit microcontrollers reference manual (see *Table 9*).

| Peripheral name in datasheet | Peripheral name in reference manual<br>(RM0016) |

|------------------------------|-------------------------------------------------|

| USART                        | UART1                                           |

| LINUART                      | UART3                                           |

#### Table 9. Communication peripheral naming correspondence

## 5.9.1 Universal synchronous/asynchronous receiver transmitter (USART)

The devices covered by this datasheet contain one USART interface. The USART can operate in standard SCI mode (serial communication interface, asynchronous) or in SPI emulation mode. It is equipped with a 16 bit fractional prescaler. It features LIN master support.

|        | Pir    | n nu   | mber                          |                     | TT. STWOAF520            |      |          | npu |                |           | Out   |    |   |                                      |                                  |                                                      |

|--------|--------|--------|-------------------------------|---------------------|--------------------------|------|----------|-----|----------------|-----------|-------|----|---|--------------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | STM8AF62xx<br>LQFP32/VFQFPN32 | STM8AF52x6 VFQFPN32 | Pin name                 | Type | Floating | Wpu | Ext. interrupt | High sink | Speed | QO | Ъ | Main<br>function<br>(after<br>reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 1      | 1      | 1      | 1                             | 1                   | NRST                     | I/O  | -        | Х   | -              | -         | -     | -  | - | R                                    | eset                             | -                                                    |

| 2      | 2      | 2      | 2                             | 2                   | PA1/OSCIN <sup>(1)</sup> | I/O  | x        | х   | -              | -         | 01    | х  | х | Port A1                              | Resonator/<br>crystal in         | -                                                    |

| 3      | 3      | 3      | 3                             | 3                   | PA2/OSCOUT               | I/O  | x        | х   | х              | -         | 01    | х  | х | Port A2                              | Resonator/<br>crystal out        | -                                                    |

| 4      | 4      | 4      | -                             | 1                   | V <sub>SSIO_1</sub>      | S    | I        | -   | I              | -         | -     | -  | - | I/O ground                           |                                  | -                                                    |

| 5      | 5      | 5      | 4                             | 4                   | V <sub>SS</sub>          | S    | -        | -   | I              | -         | I     | -  | - | Digital                              | l ground                         | -                                                    |

| 6      | 6      | 6      | 5                             | 5                   | VCAP                     | S    | -        | -   | -              | -         | -     | -  | - | 1.8 V regulator<br>capacitor         |                                  | -                                                    |

| 7      | 7      | 7      | 6                             | 6                   | V <sub>DD</sub>          | S    | -        | -   | -              | -         | -     | -  | - | Digital po                           | wer supply                       | -                                                    |

| 8      | 8      | 8      | 7                             | 7                   | V <sub>DDIO_1</sub>      | S    | I        | -   | I              | -         | -     | -  | - | I/O power supply                     |                                  | -                                                    |

| 9      | 9      | 9      | -                             | -                   | PA3/TIM2_CH3             | I/O  | x        | х   | х              | -         | 01    | х  | х | Port A3                              | Timer 2 -<br>channel 3           | TIM3_CH1<br>[AFR1]                                   |

| 10     | 10     | 10     | -                             | -                   | PA4/USART_RX             | I/O  | x        | х   | х              | -         | O3    | х  | х | Port A4                              | USART<br>receive                 | -                                                    |

| 11     | 11     | 11     | -                             | -                   | PA5/USART_TX             | I/O  | x        | х   | х              | -         | O3    | х  | х | Port A5                              | USART<br>transmit                | -                                                    |

| 12     | 12     | 12     | -                             | 8                   | PA6/USART_CK             | I/O  | x        | х   | х              | -         | O3    | х  | х | Port A6                              | USART<br>synchro<br>nous clock   | -                                                    |

| 13     | -      | -      | -                             | -                   | PH0                      | I/O  | Х        | Х   | -              | HS        | O3    | Х  | Х | Port H0                              | -                                | -                                                    |

| 14     | -      | -      | -                             | -                   | PH1                      | I/O  | Х        | Х   | -              | HS        | O3    | Х  | Х | Port H1                              | -                                | -                                                    |

| 15     | -      | -      | -                             | -                   | PH2                      | I/O  | X        | Х   | 1              | -         | 01    | Х  | Х | Port H2                              | -                                | -                                                    |

| 16     | -      | -      | -                             | 1                   | PH3                      | I/O  | X        | Х   | I              | -         | 01    | Х  | Х | Port H3                              | -                                | -                                                    |

| 17     | 13     | -      | -                             | -                   | PF7/AIN15                | I/O  | x        | х   | -              | -         | 01    | х  | х | Port F7                              | Analog<br>input 15               | -                                                    |

| 18     | 14     | -      | -                             | -                   | PF6/AIN14                | I/O  | x        | х   | -              | -         | 01    | х  | х | Port F6                              | Analog<br>input 14               | -                                                    |

| 19     | 15     | -      | -                             | -                   | PF5/AIN13                | I/O  | x        | х   | -              | -         | 01    | х  | х | Port F5                              | Analog<br>input 13               | -                                                    |

| 20     | 16     | -      | 8                             | -                   | PF4/AIN12                | I/O  | x        | х   | -              | -         | 01    | х  | х | Port F4                              | Analog<br>input 12               | -                                                    |

| 21     | 17     | -      | -                             | -                   | PF3/AIN11                | I/O  | x        | х   | -              | -         | 01    | х  | х | Port F3                              | Analog<br>input 11               | -                                                    |

| Table 11. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

|        | Pir    |        | mber                          |                     | M8AF526x/8x/A              |      |          | npu |                |           | Out   |    | P | descript                             |                                    |                                                      |

|--------|--------|--------|-------------------------------|---------------------|----------------------------|------|----------|-----|----------------|-----------|-------|----|---|--------------------------------------|------------------------------------|------------------------------------------------------|

|        |        |        |                               |                     |                            |      |          | .pu | •              |           | Jud   |    | 1 |                                      |                                    |                                                      |

| LQFP80 | LQFP64 | LQFP48 | STM8AF62xx<br>LQFP32/VFQFPN32 | STM8AF52x6 VFQFPN32 | Pin name                   | Type | Floating | Mpu | Ext. interrupt | High sink | Speed | OD | Ч | Main<br>function<br>(after<br>reset) | Default<br>alternate<br>function   | Alternate<br>function<br>after remap<br>[option bit] |

| 38     | -      | -      | -                             | -                   | PH7/<br>TIM1_CH1N          | I/O  | x        | х   | -              | -         | O1    | х  | х | Port H7                              | Timer 1 -<br>inverted<br>channel 2 | -                                                    |

| 39     | 31     | 23     | -                             | -                   | PE7/AIN8                   | I/O  | X        | Х   | I              | -         | 01    | х  | х | Port E7                              | Analog<br>input 8                  | -                                                    |

| 40     | 32     | 24     |                               |                     | PE6/AIN9                   | I/O  | x        | х   | х              | -         | 01    | х  | х | Port E6                              | Analog<br>input 9                  | -                                                    |

| 41     | 33     | 25     | 17                            | 17                  | PE5/SPI_NSS <sup>(2)</sup> | I/O  | x        | х   | х              | -         | 01    | х  | x | Port E5                              | SPI<br>master/<br>slave<br>select  | -                                                    |

| 42     | -      | -      | -                             | -                   | PC0/ADC_ETR                | I/O  | x        | х   | х              | -         | 01    | х  | х | Port C0                              | ADC<br>trigger<br>input            | -                                                    |

| 43     | 34     | 26     | 18                            | 18                  | PC1/TIM1_CH1               | I/O  | Х        | Х   | Х              | HS        | O3    | х  | х | Port C1                              | Timer 1 -<br>channel 1             | -                                                    |

| 44     | 35     | 27     | 19                            | 19                  | PC2/TIM1_CH2               | I/O  | x        | х   | х              | HS        | O3    | х  | х | Port C2                              | Timer 1-<br>channel 2              | -                                                    |

| 45     | 36     | 28     | 20                            | 20                  | PC3/TIM1_CH3               | I/O  | x        | х   | х              | HS        | O3    | х  | х | Port C3                              | Timer 1 -<br>channel 3             | -                                                    |

| 46     | 37     | 29     | 21                            | 21                  | PC4/TIM1_CH4               | I/O  | X        | х   | х              | HS        | O3    | х  | х | Port C4                              | Timer 1 -<br>channel 4             | -                                                    |

| 47     | 38     | 30     | 22                            | 22                  | PC5/SPI_SCK <sup>(2)</sup> | I/O  | Х        | Х   | Х              | -         | O3    | Х  | Х | Port C5 SPI clock                    |                                    | -                                                    |

| 48     | 39     | 31     | -                             | I                   | V <sub>SSIO_2</sub>        | S    | -        | -   | -              | -         | -     | -  | - |                                      | ground                             | -                                                    |

| 49     | 40     | 32     | -                             | I                   | V <sub>DDIO_2</sub>        | S    | -        | -   | -              | I         | -     | -  | - | I/O pow                              | er supply                          | -                                                    |

| 50     | 41     | 33     | 23                            | -                   | PC6/SPI_MOSI               | I/O  | x        | х   | х              | -         | O3    | х  | x | Port C6                              | SPI master<br>out/<br>slave in     | -                                                    |

| 51     | 42     | 34     | 24                            | -                   | PC7/SPI_MISO               | I/O  | x        | х   | х              | -         | O3    | х  | x | Port C7                              | SPI master<br>in/ slave<br>out     | -                                                    |

| 52     | 43     | 35     | -                             | 23                  | PG0/CAN_TX                 | I/O  | x        | х   | -              | -         | 01    | х  | х | Port G0                              | CAN<br>transmit                    | -                                                    |

| 53     | 44     | 36     | -                             | 24                  | PG1/CAN_RX                 | I/O  | X        | х   | -              | -         | 01    | х  | х | Port G1                              | CAN<br>receive                     | -                                                    |

| 54     | 45     | -      | -                             | -                   | PG2                        | I/O  | X        | Х   | -              | -         | 01    | Х  | Х | Port G2                              | -                                  | -                                                    |

| Table 11. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description | (continued) |

|-----------------------------------------------------------------|-------------|

|                                                                 |             |

## 6.2 Alternate function remapping

As shown in the rightmost column of *Table 11*, some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function remap) option bits. Refer to *Section 9: Option bytes on page 54*. When the remapping option is active, the default alternate function is no longer available.

To use an alternate function, the corresponding peripheral must be enabled in the peripheral registers.

Alternate function remapping does not effect GPIO capabilities of the I/O ports (see the GPIO section of STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016).

| Table 14. General hardware register map (continued) |                                   |                                       |                                           |                     |

|-----------------------------------------------------|-----------------------------------|---------------------------------------|-------------------------------------------|---------------------|

| Address                                             | Block                             | Register label                        | Register name                             | Reset<br>status     |

| 0x00 5400                                           |                                   | ADC _CSR                              | ADC control/status register               | 0x00                |

| 0x00 5401                                           |                                   | ADC_CR1 ADC configuration register 1  |                                           | 0x00                |

| 0x00 5402                                           |                                   | ADC_CR2 ADC configuration register    |                                           | 0x00                |

| 0x00 5403                                           |                                   | ADC_CR3 ADC configuration register 3  |                                           | 0x00                |

| 0x00 5404                                           | ADC                               | ADC_DRH ADC data register high        |                                           | 0xXX                |

| 0x00 5405                                           |                                   | ADC_DRL                               | ADC data register low                     | 0xXX                |

| 0x00 5406                                           |                                   | ADC_TDRH                              | ADC Schmitt trigger disable register high | 0x00                |

| 0x00 5407                                           |                                   | ADC_TDRL                              | ADC Schmitt trigger disable register low  | 0x00                |

| 0x00 5408 to<br>0x00 541F                           |                                   | Reserved area (24 bytes)              |                                           |                     |

| 0x00 5420                                           |                                   | CAN_MCR                               | CAN master control register               | 0x02                |

| 0x00 5421                                           |                                   | CAN_MSR                               | CAN master status register                | 0x02                |

| 0x00 5422                                           |                                   | CAN_TSR                               | CAN transmit status register              | 0x00                |

| 0x00 5423                                           |                                   | CAN_TPR                               | CAN transmit priority register            | 0x0C                |

| 0x00 5424                                           | CAN_RFR CAN receive FIFO register |                                       | CAN receive FIFO register                 | 0x00                |

| 0x00 5425                                           |                                   | CAN_IER CAN interrupt enable register |                                           | 0x00                |

| 0x00 5426                                           |                                   | CAN_DGR                               | CAN diagnosis register                    | 0x0C                |

| 0x00 5427                                           |                                   | CAN_FPSR CAN page selection register  |                                           | 0x00                |

| 0x00 5428                                           |                                   | CAN_P0                                | CAN paged register 0                      | 0xXX <sup>(3)</sup> |

| 0x00 5429                                           |                                   | CAN_P1                                | CAN paged register 1                      | 0xXX <sup>(3)</sup> |

| 0x00 542A                                           |                                   | CAN_P2                                | CAN paged register 2                      | 0xXX <sup>(3)</sup> |

| 0x00 542B                                           | beCAN                             | CAN_P3                                | CAN paged register 3                      | 0xXX <sup>(3)</sup> |

| 0x00 542C                                           |                                   | CAN_P4                                | CAN paged register 4                      | 0xXX <sup>(3)</sup> |

| 0x00 542D                                           |                                   | CAN_P5 CAN paged register 5           |                                           | 0xXX <sup>(3)</sup> |

| 0x00 542E                                           |                                   | CAN_P6                                | CAN paged register 6                      | 0xXX <sup>(3)</sup> |

| 0x00 542F                                           | CAN_P7 CAN paged register 7       |                                       | 0xXX <sup>(3)</sup>                       |                     |

| 0x00 5430                                           |                                   | CAN_P8 CAN paged register 8           |                                           | 0xXX <sup>(3)</sup> |

| 0x00 5431                                           |                                   | CAN_P9                                | CAN paged register 9                      | 0xXX <sup>(3)</sup> |

| 0x00 5432                                           |                                   | CAN_PA                                | CAN paged register A                      | 0xXX <sup>(3)</sup> |

| 0x00 5433                                           |                                   | CAN_PB                                | CAN paged register B                      | 0xXX <sup>(3)</sup> |

| 0x00 5434                                           |                                   | CAN_PC                                | CAN paged register C                      | 0xXX <sup>(3)</sup> |

| 0x00 5435                                           |                                   | CAN_PD                                | CAN paged register D                      | 0xXX <sup>(3)</sup> |

| 0x00 5436                                           |                                   | CAN_PE                                | CAN paged register E                      | 0xXX <sup>(3)</sup> |

|                                                     |                                   |                                       |                                           |                     |

Table 14. General hardware register map (continued)

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OPT12           | TMU_KEY 5 [7:0]: Temporary unprotection key 4<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                                  |  |  |

| OPT13           | TMU_KEY 6 [7:0]: Temporary unprotection key 5<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                                  |  |  |

| OPT14           | TMU_KEY 7 [7:0]: Temporary unprotection key 6           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |  |  |

| OPT15           | TMU_KEY 8 [7:0]: Temporary unprotection key 7           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                                           |  |  |

| OPT16           | <ul> <li>TMU_MAXATT [7:0]: TMU access failure counter</li> <li>TMU_MAXATT can be initialized with the desired value only if TMU is disabled (TMU[3:0]=0101 in OPT6 option byte).</li> <li>When TMU is enabled, any attempt to temporary remove the readout protection by using wrong key values increments the counter.</li> <li>When the option byte value reaches 0x08, the Flash memory and data EEPROM are erased.</li> </ul> |  |  |

| OPT17           | <b>BL[7:0]: Bootloader enable</b><br>If this option byte is set to 0x55 (complementary value 0xAA) the<br>bootloader program is activated also in case of a programmed code<br>memory (for more details, see the bootloader user manual, UM0560).                                                                                                                                                                                 |  |  |

### Table 19. Option byte description (continued)

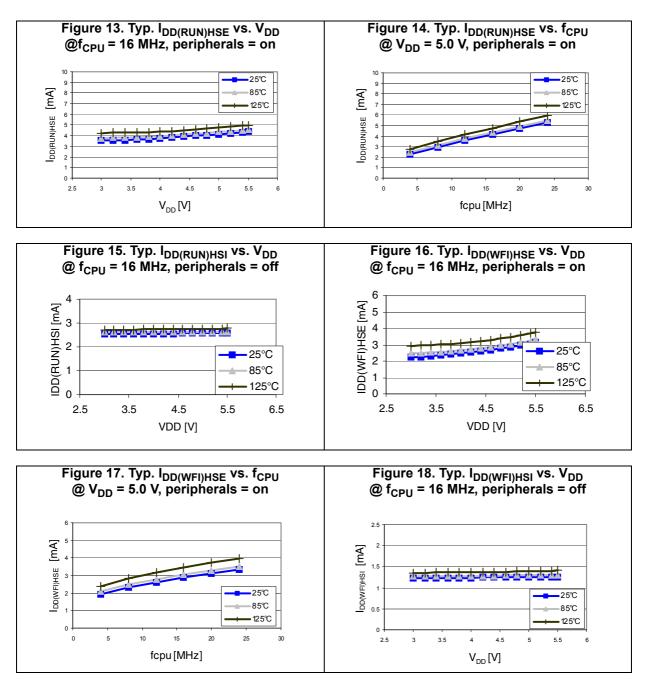

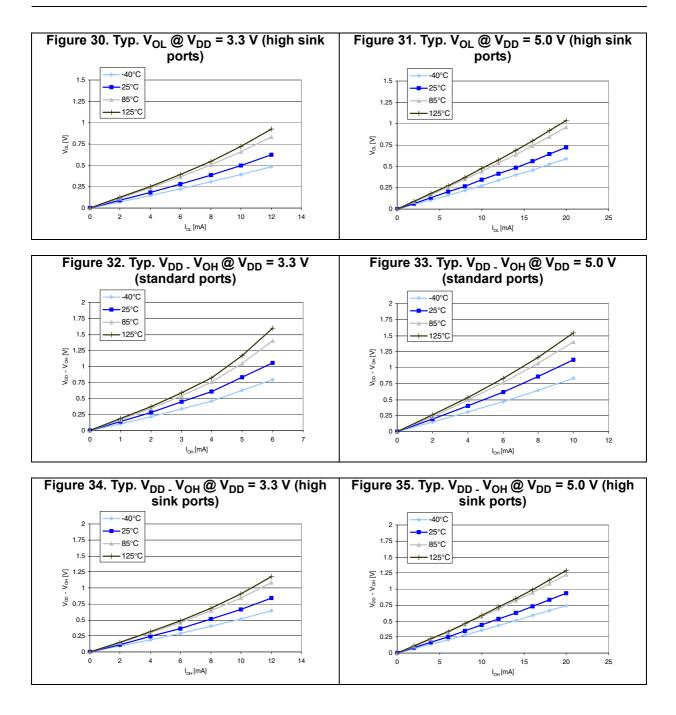

#### **Current consumption curves**

*Figure 13* to *Figure 18* show typical current consumption measured with code executing in RAM.

DocID14395 Rev 15

## **10.3.3** External clock sources and timing characteristics

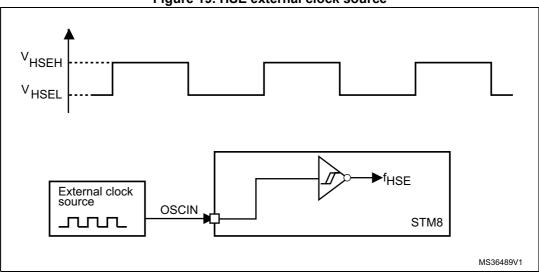

#### **HSE external clock**

An HSE clock can be generated by feeding an external clock signal of up to 24 MHz to the OSCIN pin.

Clock characteristics are subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                               | Conditions                        | Min                   | Тур | Мах                   | Unit |

|-----------------------|-----------------------------------------|-----------------------------------|-----------------------|-----|-----------------------|------|

| f <sub>HSE_ext</sub>  | User external clock source<br>frequency | T <sub>A</sub> = -40 °C to 150 °C | 0 <sup>(1)</sup>      | -   | 24                    | MHz  |

| V <sub>HSEdHL</sub>   | Comparator hysteresis                   | -                                 | 0.1 x V <sub>DD</sub> | -   | -                     |      |

| V <sub>HSEH</sub>     | OSCIN high-level input pin voltage      | -                                 | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | V    |

| V <sub>HSEL</sub>     | OSCIN low-level input pin voltage       | -                                 | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> |      |

| I <sub>LEAK_HSE</sub> | OSCIN input leakage current             | $V_{SS} < V_{IN} < V_{DD}$        | -1                    | -   | +1                    | μA   |

Table 31. HSE external clock characteristics

1. If CSS is used, the external clock must have a frequency above 500 kHz.

#### Figure 19. HSE external clock source

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied using a crystal/ceramic resonator oscillator of up to 24 MHz. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

## **10.3.4** Internal clock sources and timing characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

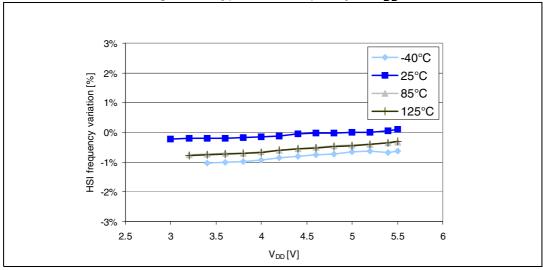

#### High-speed internal RC oscillator (HSI)

| Symbol               | Parameter                                    | Conditions                                                                                                                               | Min | Тур | Max              | Unit |  |

|----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------|------|--|

| f <sub>HSI</sub>     | Frequency                                    | -                                                                                                                                        | -   | 16  | -                | MHz  |  |

| ACC <sub>HS</sub>    | HSI oscillator user trimming accuracy        | Trimmed by the application for any $V_{DD}$ and $T_{A}$ conditions                                                                       | -1  | -   | 1                | 5    |  |

|                      | HSI oscillator accuracy (factory calibrated) | $\label{eq:V_DD} \begin{split} V_{DD} &= 3.0 \ V \leq V_{DD} \leq 5.5 \ V, \\ -40 \ ^{\circ}C \leq T_A \leq 150 \ ^{\circ}C \end{split}$ | -5  | -   | 5                |      |  |

| t <sub>su(HSI)</sub> | HSI oscillator wakeup time                   | -                                                                                                                                        | -   | -   | 2 <sup>(1)</sup> | μs   |  |

### Table 33. HSI oscillator characteristics

1. Guaranteed by characterization results, not tested in production.

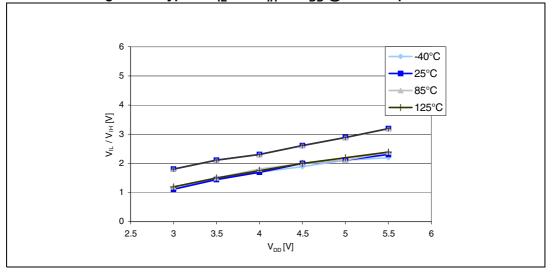

Figure 21. Typical HSI frequency vs  $V_{DD}$

- 2. Guaranteed by design.

- 3. Guaranteed by characterization results, not tested in production.

## Figure 24. Typical pull-up resistance $R_{PU}$ vs $V_{DD}$ @ four temperatures

DocID14395 Rev 15

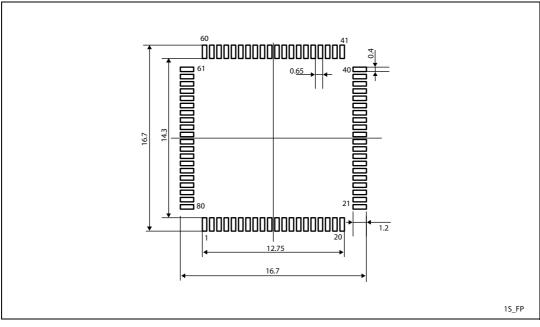

1. Dimensions are expressed in millimeters.

## 11.4 LQFP32 package information

Figure 54. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13-Oct-2016 | 14       | <ul> <li>Updated:</li> <li>Title of <i>Figure 7: STM8AF52x6 VFQFPN32 32-pin pinout</i>,<br/>(previously STM8AF5286UC VFQFPN32 32-pin pinout)</li> <li>Footnotes of <i>Figure 60: STM8AF526x/8x/Ax and</i><br/><i>STM8AF6269/8x/Ax ordering information scheme1</i></li> <li><i>Table 11: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin</i><br/><i>description</i> replaced "STM8AF5286UC VQFPN32" with<br/>"STM8AF52x6 VQFPN32" at header row</li> <li>Section 10.2: Absolute maximum ratings</li> <li>Section : Device marking on page 93</li> <li>Section : Device marking on page 96</li> <li>Section : Device marking on page 104</li> <li>Section : Device marking on page 108</li> <li>Added:</li> <li>Footnote on <i>Figure 47: LQFP80 marking example (package top</i><br/><i>view)</i>, <i>Figure 50: LQFP64 marking example (package top view)</i>,<br/><i>Figure 56: LQFP32 marking example (package top view)</i>,<br/><i>Figure 59: VFQFPN32 marking example (package top view)</i>.</li> </ul> |  |

| 10-Nov-2016 | 15       | Updated header row and PA6/USART_CK pin row on <i>Table 11:</i><br>STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID14395 Rev 15