Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 68                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-LQFP                                                               |

| Supplier Device Package    | 80-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af628atcy |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The ROP circuit may provide a temporary access for debugging or failure analysis. The temporary read access is protected by a user defined, 8-byte keyword stored in the option byte area. This keyword must be entered via the SWIM interface to temporarily unlock the device.

If desired, the temporary unlock mechanism can be permanently disabled by the user through OPT6/NOPT6 option bytes.

## 5.5 Clock controller

The clock controller distributes the system clock coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness.

#### 5.5.1 Features

- Clock sources

- 16 MHz high-speed internal RC oscillator (HSI)

- 128 kHz low-speed internal RC (LSI)

- 1-24 MHz high-speed external crystal (HSE)

- Up to 24 MHz high-speed user-external clock (HSE user-ext)

- **Reset**: After reset the microcontroller restarts by default with an internal 2-MHz clock (16 MHz/8). The clock source and speed can be changed by the application program as soon as the code execution starts.

- **Safe clock switching**: Clock sources can be changed safely on the fly in Run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

- **Clock management**: To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Wakeup**: In case the device wakes up from low-power modes, the internal RC oscillator (16 MHz/8) is used for quick startup. After a stabilization time, the device switches to the clock source that was selected before Halt mode was entered.

- **Clock security system (CSS)**: The CSS permits monitoring of external clock sources and automatic switching to the internal RC (16 MHz/8) in case of a clock failure.

- **Configurable main clock output (CCO)**: This feature permits to output a clock signal for use by the application.

### 5.5.2 16 MHz high-speed internal RC oscillator (HSI)

- Default clock after reset 2 MHz (16 MHz/8)

- Fast wakeup time

#### **User trimming**

The register CLK\_HSITRIMR with two trimming bits plus one additional bit for the sign permits frequency tuning by the application program. The adjustment range covers all possible frequency variations versus supply voltage and temperature. This trimming does not change the initial production setting.

DocID14395 Rev 15

|        | Pir    |        | mber                          |                     | WOAF 5202/02/A           |      | 1        | npu |                |           | Out   |                  | <u>.</u> |                                      |                                  | ,                                                    |

|--------|--------|--------|-------------------------------|---------------------|--------------------------|------|----------|-----|----------------|-----------|-------|------------------|----------|--------------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | STM8AF62xx<br>LQFP32/VFQFPN32 | STM8AF52x6 VFQFPN32 | Pin name                 | Type | Floating | Wpu | Ext. interrupt | High sink | Speed | OD               | Ъ        | Main<br>function<br>(after<br>reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 55     | 46     | -      | -                             | -                   | PG3                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G3                              | -                                | -                                                    |

| 56     | 47     | -      | -                             | -                   | PG4                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G4                              | -                                | -                                                    |

| 57     | 48     | -      | -                             | -                   | PI0                      | I/O  | Х        | Х   | 1              | -         | 01    | Х                | Х        | Port I0                              | -                                | -                                                    |

| 58     | -      | -      | -                             | -                   | PI1                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I1                              | -                                | -                                                    |

| 59     | -      | -      | -                             | -                   | Pl2                      | I/O  | Х        | Х   | 1              | -         | 01    | Х                | Х        | Port I2                              | -                                | -                                                    |

| 60     | -      | -      | -                             | -                   | PI3                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I3                              | -                                | -                                                    |

| 61     | -      | -      | -                             | -                   | PI4                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I4                              | -                                | -                                                    |

| 62     | -      | -      | -                             | -                   | PI5                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I5                              | -                                | -                                                    |

| 63     | 49     | -      | -                             | -                   | PG5                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G5                              | -                                | -                                                    |

| 64     | 50     | -      | -                             | -                   | PG6                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G6                              | -                                | -                                                    |

| 65     | 51     | -      | -                             | -                   | PG7                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port G7                              | -                                | -                                                    |

| 66     | 52     | -      | -                             | -                   | PE4                      | I/O  | Х        | Х   | Х              | -         | 01    | Х                | Х        | Port E4                              | -                                | -                                                    |

| 67     | 53     | 37     | -                             | -                   | PE3/TIM1_BKIN            | I/O  | Х        | х   | х              | -         | 01    | х                | х        | Port E3                              | Timer 1 -<br>break input         | -                                                    |

| 68     | 54     | 38     | -                             | -                   | PE2/I <sup>2</sup> C_SDA | I/O  | Х        | -   | Х              | -         | 01    | T <sup>(3)</sup> | -        | Port E2                              | l <sup>2</sup> C data            | -                                                    |

| 69     | 55     | 39     | -                             | -                   | PE1/I <sup>2</sup> C_SCL | I/O  | Х        | -   | Х              | -         | 01    | T <sup>(3)</sup> | -        | Port E1                              | I <sup>2</sup> C clock           | -                                                    |

| 70     | 56     | 40     | -                             | -                   | PE0/CLK_CCO              | I/O  | X        | х   | х              | -         | O3    | х                | x        | Port E0                              | Configurab<br>le clock<br>output | -                                                    |

| 71     | -      | -      | -                             | -                   | Pl6                      | I/O  | Х        | Х   | -              | -         | 01    | Х                | Х        | Port I6                              | -                                | -                                                    |

| 72     | -      | -      | -                             | -                   | PI7                      | I/O  | X        | Х   | -              | -         | 01    | Х                | Х        | Port I7                              | -                                | -                                                    |

| 73     | 57     | 41     | 25                            | 25                  | PD0/TIM3_CH2             | I/O  | x        | x   | х              | HS        | O3    | х                | x        | Port D0                              | Timer 3 -<br>channel 2           | TIM1_BKIN<br>[AFR3]/<br>CLK_CCO<br>[AFR2]            |

| 74     | 58     | 42     | 26                            | 26                  | PD1/SWIM <sup>(4)</sup>  | I/O  | х        | x   | х              | HS        | 04    | х                | х        | Port D1                              | SWIM data<br>interface           | -                                                    |

| 75     | 59     | 43     | 27                            | 27                  | PD2/TIM3_CH1             | I/O  | x        | х   | х              | HS        | O3    | х                | х        | Port D2                              | Timer 3 -<br>channel 1           | TIM2_CH3<br>[AFR1]                                   |

| 76     | 60     | 44     | 28                            | 28                  | PD3/TIM2_CH2             | I/O  | x        | х   | х              | HS        | O3    | х                | х        | Port D3                              | Timer 2 -<br>channel 2           | ADC_ETR<br>[AFR0]                                    |

| 77     | 61     | 45     | 29                            | 29                  | PD4/TIM2_CH1/<br>BEEP    | I/O  | x        | х   | х              | HS        | O3    | х                | х        | Port D4                              | Timer 2 -<br>channel 1           | BEEP output<br>[AFR7]                                |

## Table 11. STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description (continued)

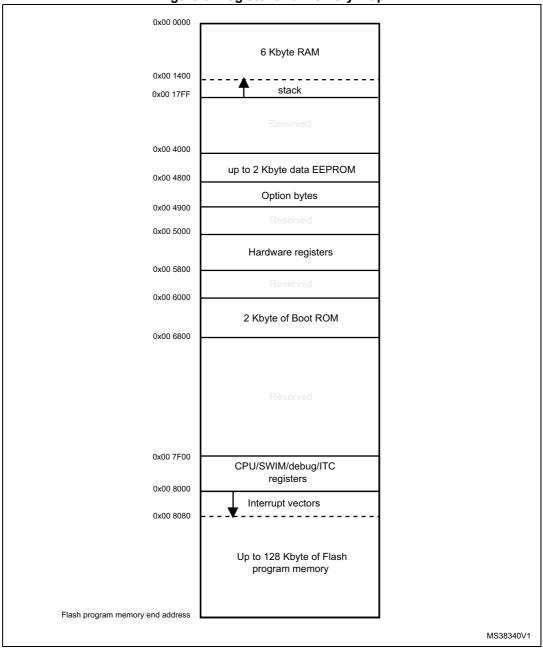

# 7 Memory and register map

# 7.1 Memory map

Figure 8. Register and memory map

| Address   | Block  | Register label | Register name                     | Reset               |

|-----------|--------|----------------|-----------------------------------|---------------------|

|           |        | -              | -                                 | status              |

| 0x00 5014 |        | PE_ODR         | Port E data output latch register | 0x00                |

| 0x00 5015 |        | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016 | Port E | PE_DDR         | Port E data direction register    | 0x00                |

| 0x00 5017 |        | PE_CR1         | Port E control register 1         | 0x00                |

| 0x00 5018 |        | PE_CR2         | Port E control register 2         | 0x00                |

| 0x00 5019 |        | PF_ODR         | Port F data output latch register | 0x00                |

| 0x00 501A |        | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B | Port F | PF_DDR         | Port F data direction register    | 0x00                |

| 0x00 501C |        | PF_CR1         | Port F control register 1         | 0x00                |

| 0x00 501D |        | PF_CR2         | Port F control register 2         | 0x00                |

| 0x00 501E |        | PG_ODR         | Port G data output latch register | 0x00                |

| 0x00 501F |        | PG_IDR         | Port G input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5020 | Port G | PG_DDR         | Port G data direction register    | 0x00                |

| 0x00 5021 |        | PG_CR1         | Port G control register 1         | 0x00                |

| 0x00 5022 |        | PG_CR2         | Port G control register 2         | 0x00                |

| 0x00 5023 |        | PH_ODR         | Port H data output latch register | 0x00                |

| 0x00 5024 |        | PH_IDR         | Port H input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5025 | Port H | PH_DDR         | Port H data direction register    | 0x00                |

| 0x00 5026 |        | PH_CR1         | Port H control register 1         | 0x00                |

| 0x00 5027 |        | PH_CR2         | Port H control register 2         | 0x00                |

| 0x00 5028 |        | PI_ODR         | Port I data output latch register | 0x00                |

| 0x00 5029 |        | PI_IDR         | Port I input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 502A | Port I | PI_DDR         | Port I data direction register    | 0x00                |

| 0x00 502B |        | PI_CR1         | Port I control register 1         | 0x00                |

| 0x00 502C |        | PI_CR2         | Port I control register 2         | 0x00                |

| Table 13 I/O | port hardware register map (continued) |   |

|--------------|----------------------------------------|---|

|              | port naruware register map (continueu) | , |

1. Depends on the external circuitry.

| Address                   | Block         | Register label | Register name                          | Reset<br>status |

|---------------------------|---------------|----------------|----------------------------------------|-----------------|

| 0x00 5250                 |               | TIM1_CR1       | TIM1 control register 1                | 0x00            |

| 0x00 5251                 |               | TIM1 CR2       | TIM1 control register 2                | 0x00            |

| 0x00 5252                 |               | <br>TIM1_SMCR  | TIM1 slave mode control register       | 0x00            |

| 0x00 5253                 |               | <br>TIM1_ETR   | TIM1 external trigger register         | 0x00            |

| 0x00 5254                 |               | <br>TIM1_IER   | TIM1 Interrupt enable register         | 0x00            |

| 0x00 5255                 |               | TIM1_SR1       | TIM1 status register 1                 | 0x00            |

| 0x00 5256                 |               | TIM1_SR2       | TIM1 status register 2                 | 0x00            |

| 0x00 5257                 |               | TIM1_EGR       | TIM1 event generation register         | 0x00            |

| 0x00 5258                 |               | TIM1_CCMR1     | TIM1 capture/compare mode register 1   | 0x00            |

| 0x00 5259                 |               | TIM1_CCMR2     | TIM1 capture/compare mode register 2   | 0x00            |

| 0x00 525A                 |               | TIM1_CCMR3     | TIM1 capture/compare mode register 3   | 0x00            |

| 0x00 525B                 |               | TIM1_CCMR4     | TIM1 capture/compare mode register 4   | 0x00            |

| 0x00 525C                 |               | TIM1_CCER1     | TIM1 capture/compare enable register 1 | 0x00            |

| 0x00 525D                 |               | TIM1_CCER2     | TIM1 capture/compare enable register 2 | 0x00            |

| 0x00 525E                 |               | TIM1_CNTRH     | TIM1 counter high                      | 0x00            |

| 0x00 525F                 | <b>TIN 44</b> | TIM1_CNTRL     | TIM1 counter low                       | 0x00            |

| 0x00 5260                 | TIM1          | TIM1_PSCRH     | TIM1 prescaler register high           | 0x00            |

| 0x00 5261                 |               | TIM1_PSCRL     | TIM1 prescaler register low            | 0x00            |

| 0x00 5262                 |               | TIM1_ARRH      | TIM1 auto-reload register high         | 0xFF            |

| 0x00 5263                 |               | TIM1_ARRL      | TIM1 auto-reload register low          | 0xFF            |

| 0x00 5264                 |               | TIM1_RCR       | TIM1 repetition counter register       | 0x00            |

| 0x00 5265                 |               | TIM1_CCR1H     | TIM1 capture/compare register 1 high   | 0x00            |

| 0x00 5266                 |               | TIM1_CCR1L     | TIM1 capture/compare register 1 low    | 0x00            |

| 0x00 5267                 |               | TIM1_CCR2H     | TIM1 capture/compare register 2 high   | 0x00            |

| 0x00 5268                 |               | TIM1_CCR2L     | TIM1 capture/compare register 2 low    | 0x00            |

| 0x00 5269                 |               | TIM1_CCR3H     | TIM1 capture/compare register 3 high   | 0x00            |

| 0x00 526A                 |               | TIM1_CCR3L     | TIM1 capture/compare register 3 low    | 0x00            |

| 0x00 526B                 |               | TIM1_CCR4H     | TIM1 capture/compare register 4 high   | 0x00            |

| 0x00 526C                 |               | TIM1_CCR4L     | TIM1 capture/compare register 4 low    | 0x00            |

| 0x00 526D                 |               | TIM1_BKR       | TIM1 break register                    | 0x00            |

| 0x00 526E                 |               | TIM1_DTR       | TIM1 dead-time register                | 0x00            |

| 0x00 526F                 |               | TIM1_OISR      | TIM1 output idle state register        | 0x00            |

| 0x00 5270 to<br>0x00 52FF |               | Re             | served area (147 bytes)                |                 |

Table 14. General hardware register map (continued)

|                           | Table 14. General hardware register map (continued) |                |                                           |                     |  |  |  |  |  |

|---------------------------|-----------------------------------------------------|----------------|-------------------------------------------|---------------------|--|--|--|--|--|

| Address                   | Block                                               | Register label | Register name                             | Reset<br>status     |  |  |  |  |  |

| 0x00 5400                 |                                                     | ADC _CSR       | ADC control/status register               | 0x00                |  |  |  |  |  |

| 0x00 5401                 |                                                     | ADC_CR1        | ADC configuration register 1              | 0x00                |  |  |  |  |  |

| 0x00 5402                 |                                                     | ADC_CR2        | ADC configuration register 2              | 0x00                |  |  |  |  |  |

| 0x00 5403                 | ADC                                                 | ADC_CR3        | ADC configuration register 3              | 0x00                |  |  |  |  |  |

| 0x00 5404                 | ADC                                                 | ADC_DRH        | ADC data register high                    | 0xXX                |  |  |  |  |  |

| 0x00 5405                 |                                                     | ADC_DRL        | ADC data register low                     | 0xXX                |  |  |  |  |  |

| 0x00 5406                 |                                                     | ADC_TDRH       | ADC Schmitt trigger disable register high | 0x00                |  |  |  |  |  |

| 0x00 5407                 |                                                     | ADC_TDRL       | ADC Schmitt trigger disable register low  | 0x00                |  |  |  |  |  |

| 0x00 5408 to<br>0x00 541F |                                                     | Re             | Reserved area (24 bytes)                  |                     |  |  |  |  |  |

| 0x00 5420                 |                                                     | CAN_MCR        | CAN master control register               | 0x02                |  |  |  |  |  |

| 0x00 5421                 |                                                     | CAN_MSR        | CAN master status register                | 0x02                |  |  |  |  |  |

| 0x00 5422                 |                                                     | CAN_TSR        | CAN transmit status register              | 0x00                |  |  |  |  |  |

| 0x00 5423                 |                                                     | CAN_TPR        | CAN transmit priority register            | 0x0C                |  |  |  |  |  |

| 0x00 5424                 |                                                     | CAN_RFR        | CAN receive FIFO register                 | 0x00                |  |  |  |  |  |

| 0x00 5425                 |                                                     | CAN_IER        | CAN interrupt enable register             | 0x00                |  |  |  |  |  |

| 0x00 5426                 |                                                     | CAN_DGR        | CAN diagnosis register                    | 0x0C                |  |  |  |  |  |

| 0x00 5427                 |                                                     | CAN_FPSR       | CAN page selection register               | 0x00                |  |  |  |  |  |

| 0x00 5428                 |                                                     | CAN_P0         | CAN paged register 0                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 5429                 |                                                     | CAN_P1         | CAN paged register 1                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 542A                 |                                                     | CAN_P2         | CAN paged register 2                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 542B                 | beCAN                                               | CAN_P3         | CAN paged register 3                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 542C                 |                                                     | CAN_P4         | CAN paged register 4                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 542D                 |                                                     | CAN_P5         | CAN paged register 5                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 542E                 |                                                     | CAN_P6         | CAN paged register 6                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 542F                 |                                                     | CAN_P7         | CAN paged register 7                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 5430                 |                                                     | CAN_P8         | CAN paged register 8                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 5431                 |                                                     | CAN_P9         | CAN paged register 9                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 5432                 |                                                     | CAN_PA         | CAN paged register A                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 5433                 |                                                     | CAN_PB         | CAN paged register B                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 5434                 |                                                     | CAN_PC         | CAN paged register C                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 5435                 |                                                     | CAN_PD         | CAN paged register D                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

| 0x00 5436                 |                                                     | CAN_PE         | CAN paged register E                      | 0xXX <sup>(3)</sup> |  |  |  |  |  |

|                           |                                                     |                |                                           |                     |  |  |  |  |  |

Table 14. General hardware register map (continued)

# 9 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated block of the memory. Each option byte has to be stored twice, for redundancy, in a regular form (OPTx) and a complemented one (NOPTx), except for the ROP (read-out protection) option byte and option bytes 8 to 16.

Option bytes can be modified in ICP mode (via SWIM) by accessing the EEPROM address shown in *Table 18: Option bytes* below.

Option bytes can also be modified 'on the fly' by the application in IAP mode, except the ROP and UBC options that can only be changed in ICP mode (via SWIM).

Refer to the STM8 Flash programming manual (PM0047) and STM8 SWIM communication protocol and debug module user manual (UM0470) for information on SWIM programming procedures.

| Addr.        | Option                          | Option<br>byte |       |                                                                     |       | Opt   | ion bits    |               |              |               | Factory default |

|--------------|---------------------------------|----------------|-------|---------------------------------------------------------------------|-------|-------|-------------|---------------|--------------|---------------|-----------------|

| Auur.        | name                            | no.            | 7     | 6                                                                   | 5     | 4     | 3           | 2             | 1            | 0             | setting         |

| 0x00<br>4800 | Read-out<br>protection<br>(ROP) | OPT0           |       |                                                                     |       | RC    | )P[7:0]     |               |              |               | 0x00            |

| 0x00<br>4801 | User boot<br>code               | OPT1           |       | UBC[7:0]                                                            |       |       |             |               |              |               | 0x00            |

| 0x00<br>4802 | (UBC)                           | NOPT1          |       |                                                                     |       | NU    | BC[7:0]     |               |              |               | 0xFF            |

| 0x00<br>4803 | Alternate function              | OPT2           | AFR7  | AFR6                                                                | AFR5  | AFR4  | AFR3        | AFR2          | AFR1         | AFR0          | 0x00            |

| 0x00<br>4804 | remapping<br>(AFR)              | NOPT2          | NAFR7 | NAFR6                                                               | NAFR5 | NAFR4 | NAFR3       | NAFR2         | NAFR1        | NAFR0         | 0xFF            |

| 0x00<br>4805 | Watchdog                        | OPT3           |       | Reserved     LSI_<br>EN     IWDG     WWD       WWD     HWL     HALT |       |       |             |               |              | 0x00          |                 |

| 0x00<br>4806 | option                          | NOPT3          |       | Reserved                                                            |       |       |             | NIWD<br>G_HW  | NWWD<br>G_HW | NWWG<br>_HALT | 0xFF            |

| 0x00<br>4807 | Clock                           | OPT4           |       | Rese                                                                | erved |       | EXT<br>CLK  | CKAW<br>USEL  | PRSC1        | PRSC0         | 0x00            |

| 0x00<br>4808 | option                          | NOPT4          |       | Rese                                                                | erved |       | NEXT<br>CLK | NCKAW<br>USEL | NPRSC1       | NPRSC<br>0    | 0xFF            |

| 0x00<br>4809 | HSE clock                       | OPT5           |       | HSECNT[7:0]                                                         |       |       |             |               |              | 0x00          |                 |

| 0x00<br>480A | startup                         | NOPT5          |       |                                                                     |       | NHSE  | ECNT[7:0    | ]             |              |               | 0xFF            |

#### Table 18. Option bytes

# **10** Electrical characteristics

## 10.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = -40$  °C,  $T_A = 25$  °C, and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production.

#### 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5.0$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

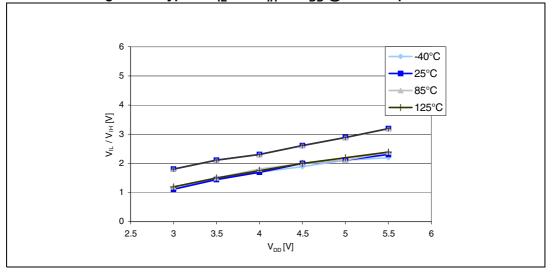

#### 10.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

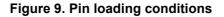

#### 10.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

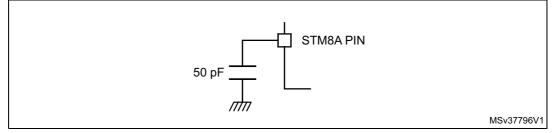

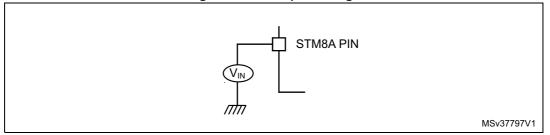

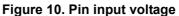

## 10.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 10*.

## **10.2** Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 20: Voltage characteristics*, *Table 21: Current characteristics* and *Table 22: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect the device's reliability. The device's mission profile (application conditions) is compliant with the JEDEC JESD47 qualification standard, extended mission profiles are available on demand.

| Symbol                             | Ratings                                                           | Min                   | Мах                                        | Unit |

|------------------------------------|-------------------------------------------------------------------|-----------------------|--------------------------------------------|------|

| V <sub>DDx</sub> - V <sub>SS</sub> | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                  | 6.5                                        |      |

| V <sub>IN</sub>                    | Input voltage on true open drain pins (PE1, PE2) <sup>(2)</sup>   | V <sub>SS</sub> - 0.3 | 6.5                                        | V    |

| V IN                               | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3                      |      |

| V <sub>DDx</sub> - V <sub>DD</sub> | Variations between different power pins                           | -                     | 50                                         | mV   |

| $ V_{SSx} - V_{SS} $               | Variations between all the different ground pins                  | -                     | 50                                         | IIIV |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                                   |                       | ite maximum<br>cal sensitivity)<br>page 88 | -    |

#### Table 20. Voltage characteristics

1. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

#### **Operating conditions** 10.3

|                   | Table 24. Gener                                      | al operating condition                            | 13   | 1    |      |

|-------------------|------------------------------------------------------|---------------------------------------------------|------|------|------|

| Symbol            | Parameter                                            | Conditions                                        | Min  | Max  | Unit |

| £                 | Internal CBL clock fraguancy                         | 1 wait state<br>T <sub>A</sub> = -40 °C to 150 °C | 16   | 24   | MHz  |

| f <sub>CPU</sub>  | Internal CPU clock frequency                         | 0 wait state<br>T <sub>A</sub> = -40 °C to 150 °C | 0    | 16   |      |

| $V_{DD/}V_{DDIO}$ | Standard operating voltage                           | -                                                 | 3.0  | 5.5  | V    |

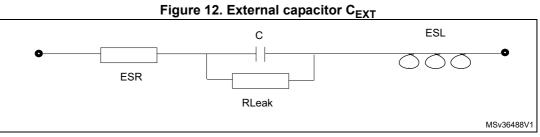

| (1)               | C <sub>EXT</sub> : capacitance of external capacitor | -                                                 | 470  | 3300 | nF   |

| $V_{CAP}^{(1)}$   | ESR of external capacitor                            | at 1 MHz <sup>(2)</sup>                           | -    | 0.3  | Ω    |

|                   | ESL of external capacitor                            |                                                   | -    | 0.3  | nH   |

|                   |                                                      | Suffix A                                          |      | 85   | °C   |

| T <sub>A</sub>    | Ambient temperature                                  | Suffix C                                          | - 40 | 125  |      |

|                   |                                                      | Suffix D                                          |      | 150  |      |

|                   |                                                      | Suffix A                                          |      | 90   |      |

| TJ                | Junction temperature range                           | Suffix C                                          | - 40 | 130  |      |

|                   |                                                      | Suffix D                                          |      | 155  |      |

| Table | 24.      | General | operating | conditions  |

|-------|----------|---------|-----------|-------------|

| labic | <u> </u> | General | operating | contaitions |

Care should be taken when selecting the capacitor, due to its tolerance, as well as the parameter dependency on temperature, DC bias and frequency in addition to other factors. The parameter maximum value must be respected for the full application range.

2. This frequency of 1 MHz as a condition for  $V_{CAP}$  parameters is given by design of internal regulator.

fcpu [MHz] 24 Functionality guaranteed @TA -40 to 150 °C at 1 waitstate Functionality. not guaranteed 16 in this area 12 Functionality guaranteed @TA -40 to 150 °C at 0 waitstate 8 4 0 3.0 4.0 5.0 5.5 Supply voltage [V] MSv44121V1

## Figure 11. f<sub>CPUmax</sub> versus V<sub>DD</sub>

|                       |                                                | ••••••                  |                  | <b>P</b> • • • • • • • • • • • • • • • • • • • | -    |      |  |

|-----------------------|------------------------------------------------|-------------------------|------------------|------------------------------------------------|------|------|--|

| Symbol                | Parameter                                      | Conditions              | Min              | Тур                                            | Мах  | Unit |  |

|                       | V <sub>DD</sub> rise time rate                 | -                       | 2 <sup>(1)</sup> | -                                              | 8    |      |  |

| t <sub>VDD</sub>      | V <sub>DD</sub> fall time rate                 | -                       | 2 <sup>(1)</sup> | -                                              | ∞    | μs/V |  |

| +                     | Reset release delay                            | V <sub>DD</sub> rising  | -                | 1                                              | 1.7  | ms   |  |

| t <sub>TEMP</sub>     | Reset generation delay                         | V <sub>DD</sub> falling | -                | 3                                              | -    | μs   |  |

| V <sub>IT+</sub>      | Power-on reset<br>threshold <sup>(2) (3)</sup> | -                       | 2.65             | 2.8                                            | 2.95 | v    |  |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold                   | -                       | 2.58             | 2.73                                           | 2.88 | v    |  |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis                  | -                       | -                | 70 <sup>(1)</sup>                              | -    | mV   |  |

Table 25. Operating conditions at power-up/power-down

1. Guaranteed by design, not tested in production.

2. If V<sub>DD</sub> is below 3 V, the code execution is guaranteed above the V<sub>IT-</sub> and V<sub>IT+</sub> thresholds. RAM content is kept. The EEPROM programming sequence must not be initiated.

3. There is inrush current into V<sub>DD</sub> present after device power on to charge C<sub>EXT</sub> capacitor. This inrush energy depends from C<sub>EXT</sub> capacitor value. For example, a C<sub>EXT</sub> of 1  $\mu$ F requires Q=1  $\mu$ F x 1.8 V = 1.8  $\mu$ C.

### **10.3.1 VCAP external capacitor**

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 24*. Care should be taken to limit the series inductance to less than 15 nH.

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

#### **10.3.2** Supply current characteristics

The current consumption is measured as described in *Figure 9 on page 59* and *Figure 10 on page 60*.

If not explicitly stated, general conditions of temperature and voltage apply.

|                       |                     | r rogramming current consumpt                                                                       |     |     |      |

|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------|-----|-----|------|

| Symbol                | Parameter           | Conditions                                                                                          | Тур | Max | Unit |

| I <sub>DD(PROG)</sub> | Programming current | V <sub>DD</sub> = 5 V, -40 °C to 150 °C, erasing<br>and programming data or Flash<br>program memory | 1.0 | 1.7 | mA   |

#### Table 29. Programming current consumption

## Table 30. Typical peripheral current consumption $V_{DD} = 5.0 V^{(1)}$

| Symbol                          | Parameter                                         | Typ.<br>f <sub>master</sub> = 2 MHz | Typ.<br>f <sub>master</sub> = 16 MHz | Typ.<br>f <sub>master</sub> =24 MHz | Unit |

|---------------------------------|---------------------------------------------------|-------------------------------------|--------------------------------------|-------------------------------------|------|

| I <sub>DD(TIM1)</sub>           | TIM1 supply current <sup>(2)</sup>                | 0.03                                | 0.23                                 | 0.34                                |      |

| I <sub>DD(TIM2)</sub>           | TIM2 supply current <sup>(2)</sup>                | 0.02                                | 0.12                                 | 0.19                                |      |

| I <sub>DD(TIM3)</sub>           | TIM3 supply current <sup>(2)</sup>                | 0.01                                | 0.1                                  | 0.16                                |      |

| I <sub>DD(TIM4)</sub>           | TIM4 supply current <sup>(2)</sup>                | 0.004                               | 0.03                                 | 0.05                                |      |

| I <sub>DD(USART)</sub>          | USART supply current <sup>(2)</sup>               | 0.03                                | 0.09                                 | 0.15                                |      |

| I <sub>DD(LINUART)</sub>        | LINUART supply current <sup>(2)</sup>             | 0.03                                | 0.11                                 | 0.18                                |      |

| I <sub>DD(SPI)</sub>            | SPI supply current <sup>(2)</sup>                 | 0.01                                | 0.04                                 | 0.07                                | mA   |

| I <sub>DD(I<sup>2</sup>C)</sub> | I <sup>2</sup> C supply current <sup>(2)</sup>    | 0.02                                | 0.06                                 | 0.91                                |      |

| I <sub>DD(CAN)</sub>            | CAN supply current <sup>(3)</sup>                 | 0.06                                | 0.30                                 | 0.40                                |      |

| I <sub>DD(AWU)</sub>            | AWU supply current <sup>(2)</sup>                 | 0.003                               | 0.02                                 | 0.05                                |      |

| I <sub>DD(TOT_DIG)</sub>        | All digital peripherals on                        | 0.22                                | 1                                    | 2.4                                 |      |

| I <sub>DD(ADC)</sub>            | ADC supply current when converting <sup>(4)</sup> | 0.93                                | 0.95                                 | 0.96                                |      |

1. Typical values not tested in production. Since the peripherals are powered by an internally regulated, constant digital supply voltage, the values are similar in the full supply voltage range.

2. Data based on a differential I<sub>DD</sub> measurement between no peripheral clocked and a single active peripheral. This measurement does not include the pad toggling consumption.

3. Data based on a differential IDD measurement between reset configuration (CAN disabled) and a permanent CAN data transmit sequence in loopback mode at 1 MHz. This measurement does not include the pad toggling consumption.

4. Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions.

- 2. Guaranteed by design.

- 3. Guaranteed by characterization results, not tested in production.

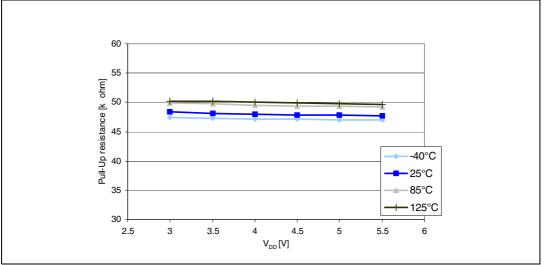

## Figure 24. Typical pull-up resistance $R_{PU}$ vs $V_{DD}$ @ four temperatures

1. Measurement points are at CMOS levels: 0.3  $V_{DD}$  and 0.7  $V_{DD}$ .

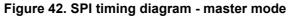

|        | millimeters |        |        | inches |        |        |  |

|--------|-------------|--------|--------|--------|--------|--------|--|

| Symbol |             |        |        |        |        |        |  |

|        | Min         | Тур    | Max    | Min    | Тур    | Max    |  |

| А      | -           | -      | 1.600  | -      | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150  | 0.0020 | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531 | 0.0551 | 0.0571 |  |

| b      | 0.220       | 0.320  | 0.380  | 0.0087 | 0.0126 | 0.0150 |  |

| С      | 0.090       | -      | 0.200  | 0.0035 | -      | 0.0079 |  |

| D      | 15.800      | 16.000 | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |

| D3     | -           | 12.350 | -      | -      | 0.4862 | -      |  |

| E      | 15.800      | 16.000 | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |

| E3     | -           | 12.350 | -      | -      | 0.4862 | -      |  |

| е      | -           | 0.650  | -      | -      | 0.0256 | -      |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177 | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -      | -      | 0.0394 | -      |  |

| k      | 0°          | 3.5°   | 7°     | 0°     | 3.5°   | 7°     |  |

| CCC    | -           | -      | 0.100  | -      | -      | 0.0039 |  |

# Table 49. LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data<sup>(1)</sup>

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

|        | nat package mechanical data |       |       |                       |        |        |

|--------|-----------------------------|-------|-------|-----------------------|--------|--------|

| Symbol | millimeters                 |       |       | inches <sup>(1)</sup> |        |        |

|        | Min                         | Тур   | Max   | Min                   | Тур    | Мах    |

| А      | 0.800                       | 0.900 | 1.000 | 0.0315                | 0.0354 | 0.0394 |

| A1     | 0.000                       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| A3     | -                           | 0.200 | -     | -                     | 0.0079 | -      |

| b      | 0.180                       | 0.250 | 0.300 | 0.0071                | 0.0098 | 0.0118 |

| D      | 4.850                       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| D2     | 3.500                       | 3.600 | 3.700 | 0.1378                | 0.1417 | 0.1457 |

| E      | 4.850                       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| E2     | 3.500                       | 3.600 | 3.700 | 0.1378                | 0.1417 | 0.1457 |

| е      | -                           | 0.500 | -     | -                     | 0.0197 | -      |

| L      | 0.300                       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| ddd    | -                           | -     | 0.050 | -                     | -      | 0.0020 |

# Table 53. VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quadflat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## **13.3 Programming tools**

During the development cycle, STice provides in-circuit programming of the STM8A Flash microcontroller on the application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8A.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.

| Table 55. Document revision history (continued) |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

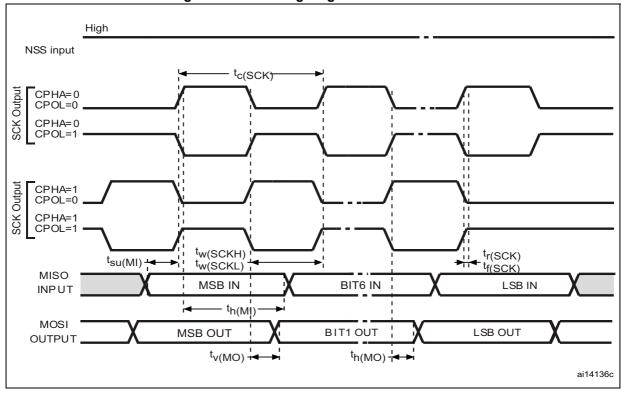

| 18-Jul-2012                                     | 9<br>(continued) | Table 26: Total current consumption in Run, Wait and Slow mode.General conditions for VDD apply, TA = -40 °C to 150 °C: updatedconditions for I <sub>DD(RUN)</sub> :Table 38: I/O static characteristics: added new condition and newmax values for rise and fall time; updated footnote 2.Section 10.3.7: Reset pin characteristics: updated text belowFigure 38: Typical NRST pull-up current Ipu vs VDDFigure 39: Recommended reset pin protection: updated unit ofcapacitor.Table 41: SPI characteristics: updated SCK high and low timeconditions and values.Figure 42: SPI timing diagram - master mode: replaced 'SCK input'signals with 'SCK output' signals.Updated Table 49: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flatpackage mechanical data, Table 50: LQFP64 - 64-pin, 10 x 10 mmlow-profile quad flat package mechanical data, Table 52: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data,Table 52: LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat packagemechanical data, Table 53: VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mmpitch very thin profile fine pitch quad flat package mechanical dataReplaced Figure 48: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage outline, Figure 51: LQFP48 - 48-pin, 7 x 7 mm low-rom low-profile quad flat package outlineAdded Figure 49: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage outline, Figure 51: LQFP48 - 48-pin, 7 x 7 mm low-rom low-profile quad flat package outlineAdded Figure 49: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage recommended footprint, Figure 52: LQFP48 - 48-pin, 7 x 7 mm low- |  |  |

| 31-Mar-2014                                     | 10               | <ul> <li>Updated:</li> <li>Table 1: Device summary,</li> <li>Table: STM8AF52xx product line-up with CAN,</li> <li>Table: STM8AF/H/P51xx product line-up with CAN,</li> <li>Table: STM8AF/H/P61xx product line-up without CAN,</li> <li>Table 11: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax pin description,</li> <li>The maximum speed in Section 5.9.3: Serial peripheral interface (SPI),</li> <li>t<sub>TEMP</sub> Reset release delay /VDD rising typical and max values in Table 25: Operating conditions at power-up/power-down,</li> <li>The symbol t<sub>IFP(NRST)</sub> with t<sub>INFP(NRST)</sub> in Table 39: NRST pin characteristics,</li> <li>The address and comment for Reset in Table 17: STM8A interrupt table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID14395 Rev 15