Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-VFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af62a6ucx |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 48.<br>Figure 49. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline              |

|--------------------------|--------------------------------------------------------------------------------|

|                          | recommended footprint                                                          |

| Figure 50.               | LQFP64 marking example (package top view)96                                    |

| Figure 51.               | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                |

| Figure 52.               | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                        |

| -                        | recommended footprint                                                          |

| Figure 53.               | LQFP48 marking example (package top view)                                      |

| Figure 54.               | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline                |

| Figure 55.               | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                        |

| U                        | recommended footprint                                                          |

| Figure 56.               | LQFP32 marking example (package top view)                                      |

| Figure 57.               | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad      |

| 0                        | flat package outline                                                           |

| Figure 58.               | VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad    |

| U                        | flat package recommended footprint                                             |

| Figure 59.               | VFQFPN32 marking example (package top view)                                    |

| Figure 60.               | STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information scheme <sup>1</sup> |

## 5.5.3 128 kHz low-speed internal RC oscillator (LSI)

The frequency of this clock is 128 kHz and it is independent from the main clock. It drives the independent watchdog or the AWU wakeup timer.

In systems which do not need independent clock sources for the watchdog counters, the 128 kHz signal can be used as the system clock. This configuration has to be enabled by setting an option byte (OPT3/OPT3N, bit LSI\_EN).

## 5.5.4 24 MHz high-speed external crystal oscillator (HSE)

The external high-speed crystal oscillator can be selected to deliver the main clock in normal Run mode. It operates with quartz crystals and ceramic resonators.

- Frequency range: 1 MHz to 24 MHz

- Crystal oscillation mode: preferred fundamental

- I/Os: standard I/O pins multiplexed with OSCIN, OSCOUT

## 5.5.5 External clock input

An external clock signal can be applied to the OSCIN input pin of the crystal oscillator. The frequency range is 0 to 24 MHz.

#### 5.5.6 Clock security system (CSS)

The clock security system protects against a system stall in case of an external crystal clock failure.

In case of a clock failure an interrupt is generated and the high-speed internal clock (HSI) is automatically selected with a frequency of 2 MHz (16 MHz/8).

|             | <b>J</b>         |

|-------------|------------------|

| Control bit | Peripheral       |

| PCKEN17     | TIM1             |

| PCKEN16     | TIM3             |

| PCKEN15     | TIM2             |

| PCKEN14     | TIM4             |

| PCKEN13     | LINUART          |

| PCKEN12     | USART            |

| PCKEN11     | SPI              |

| PCKEN10     | l <sup>2</sup> C |

#### Table 4. Peripheral clock gating bits (CLK\_PCKENR1)

|             | Jan 9 and ( a 1 |

|-------------|-----------------|

| Control bit | Peripheral      |

| PCKEN27     | CAN             |

| PCKEN26     | Reserved        |

| PCKEN25     | Reserved        |

| PCKEN24     | Reserved        |

| PCKEN23     | ADC             |

| PCKEN22     | AWU             |

| PCKEN21     | Reserved        |

| PCKEN20     | Reserved        |

|             |                 |

#### Table 5. Peripheral clock gating bits (CLK PCKENR2)

# 5.6 Low-power operating modes

For efficient power management, the application can be put in one of four different lowpower modes. Users can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- Wait mode

In this mode, the CPU is stopped but peripherals are kept running. The wakeup is

performed by an internal or external interrupt or reset.

- Active-halt mode with regulator on

In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in Active-halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

• Active-halt mode with regulator off

This mode is the same as Active-halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

Halt mode

CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

In all modes the CPU and peripherals remain permanently powered on, the system clock is applied only to selected modules. The RAM content is preserved and the brown-out reset circuit remains activated.

- Interrupt:

- Successful address/data communication

- Error condition

- Wakeup from Halt

- Wakeup from Halt on address detection in slave mode

#### 5.9.5 Controller area network interface (beCAN)

The beCAN controller (basic enhanced CAN), interfaces the CAN network and supports the CAN protocol version 2.0A and B. It is equipped with a receive FIFO and a very versatile filter bank. Together with a filter match index, this allows a very efficient message handling in today's car network architectures. The CPU is significantly unloaded. The maximum transmission speed is 1 Mbit/s.

#### Transmission

- Three transmit mailboxes

- Configurable transmit priority by identifier or order request

#### Reception

- 11- and 29-bit ID

- 1 receive FIFO (3 messages deep)

- Software-efficient mailbox mapping at a unique address space

- FMI (filter match index) stored with message for quick message association

- Configurable FIFO overrun

- Time stamp on SOF reception

- 6 filter banks, 2 x 32 bytes (scalable to 4 x 16-bit) each, enabling various masking configurations, such as 12 filters for 29-bit ID or 48 filters for 11-bit ID.

- Filtering modes (mixable):

- Mask mode permitting ID range filtering

- ID list mode

#### Interrupt management

- Maskable interrupt

- Software-efficient mailbox mapping at a unique address space

# 5.10 Input/output specifications

The product features four I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

- Caution: In STM8AF5286UC device, the following I/O ports are not automatically configured by hardware: PA3, PA4, PA5, PA6, PF4, PB6, PB7, PE0, PE1, PE2, PE3, PE6, PE7. As a consequence, they must be put into one of the following configurations by software: - configured as input with internal pull-up/down resistor,

- configured as output push-pull low.

| Flash program<br>memory size | Flash program<br>memory end<br>address | RAM size | RAM end<br>address | Stack roll-over<br>address |

|------------------------------|----------------------------------------|----------|--------------------|----------------------------|

| 128 K                        | 0x00 27FFF                             |          |                    |                            |

| 64 K                         | 0x00 17FFF                             | 6 K      | 0x00 17FF          | 0x00 1400                  |

| 32 K                         | 0x00 0FFFF                             |          |                    |                            |

Table 12. Memory model 128K

# 7.2 Register map

In this section the memory and register map of the devices covered by this datasheet is described. For a detailed description of the functionality of the registers, refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016.

| Address   | Block  | Register label | Register name                     | Reset<br>status     |

|-----------|--------|----------------|-----------------------------------|---------------------|

| 0x00 5000 |        | PA_ODR         | Port A data output latch register | 0x00                |

| 0x00 5001 |        | PA_IDR         | Port A input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5002 | Port A | PA_DDR         | Port A data direction register    | 0x00                |

| 0x00 5003 |        | PA_CR1         | Port A control register 1         | 0x00                |

| 0x00 5004 |        | PA_CR2         | Port A control register 2         | 0x00                |

| 0x00 5005 |        | PB_ODR         | Port B data output latch register | 0x00                |

| 0x00 5006 |        | PB_IDR         | Port B input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5007 | Port B | PB_DDR         | Port B data direction register    | 0x00                |

| 0x00 5008 |        | PB_CR1         | Port B control register 1         | 0x00                |

| 0x00 5009 |        | PB_CR2         | Port B control register 2         | 0x00                |

| 0x00 500A |        | PC_ODR         | Port C data output latch register | 0x00                |

| 0x00 500B |        | PB_IDR         | Port C input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 500C | Port C | PC_DDR         | Port C data direction register    | 0x00                |

| 0x00 500D |        | PC_CR1         | Port C control register 1         | 0x00                |

| 0x00 500E |        | PC_CR2         | Port C control register 2         | 0x00                |

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00                |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00                |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x02                |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00                |

Table 13. I/O port hardware register map

| Address   | Block  | Register label | Register name                     | Reset               |

|-----------|--------|----------------|-----------------------------------|---------------------|

|           |        | -              | -                                 | status              |

| 0x00 5014 |        | PE_ODR         | Port E data output latch register | 0x00                |

| 0x00 5015 |        | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016 | Port E | PE_DDR         | Port E data direction register    | 0x00                |

| 0x00 5017 |        | PE_CR1         | Port E control register 1         | 0x00                |

| 0x00 5018 |        | PE_CR2         | Port E control register 2         | 0x00                |

| 0x00 5019 |        | PF_ODR         | Port F data output latch register | 0x00                |

| 0x00 501A |        | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B | Port F | PF_DDR         | Port F data direction register    | 0x00                |

| 0x00 501C |        | PF_CR1         | Port F control register 1         | 0x00                |

| 0x00 501D |        | PF_CR2         | Port F control register 2         | 0x00                |

| 0x00 501E |        | PG_ODR         | Port G data output latch register | 0x00                |

| 0x00 501F |        | PG_IDR         | Port G input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5020 | Port G | PG_DDR         | Port G data direction register    | 0x00                |

| 0x00 5021 |        | PG_CR1         | Port G control register 1         | 0x00                |

| 0x00 5022 |        | PG_CR2         | Port G control register 2         | 0x00                |

| 0x00 5023 |        | PH_ODR         | Port H data output latch register | 0x00                |

| 0x00 5024 |        | PH_IDR         | Port H input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5025 | Port H | PH_DDR         | Port H data direction register    | 0x00                |

| 0x00 5026 |        | PH_CR1         | Port H control register 1         | 0x00                |

| 0x00 5027 |        | PH_CR2         | Port H control register 2         | 0x00                |

| 0x00 5028 |        | PI_ODR         | Port I data output latch register | 0x00                |

| 0x00 5029 |        | PI_IDR         | Port I input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 502A | Port I | PI_DDR         | Port I data direction register    | 0x00                |

| 0x00 502B |        | PI_CR1         | Port I control register 1         | 0x00                |

| 0x00 502C |        | PI_CR2         | Port I control register 2         | 0x00                |

| Table 13 I/O | port hardware register map (continued) |   |

|--------------|----------------------------------------|---|

|              | port naruware register map (continueu) | , |

1. Depends on the external circuitry.

|                           |       |                |                                        | Reset  |

|---------------------------|-------|----------------|----------------------------------------|--------|

| Address                   | Block | Register label | Register name                          | status |

| 0x00 5300                 |       | TIM2_CR1       | TIM2 control register 1                | 0x00   |

| 0x00 5301                 |       | TIM2_IER       | TIM2 interrupt enable register         | 0x00   |

| 0x00 5302                 |       | TIM2_SR1       | TIM2 status register 1                 | 0x00   |

| 0x00 5303                 |       | TIM2_SR2       | TIM2 status register 2                 | 0x00   |

| 0x00 5304                 |       | TIM2_EGR       | TIM2 event generation register         | 0x00   |

| 0x00 5305                 |       | TIM2_CCMR1     | TIM2 capture/compare mode register 1   | 0x00   |

| 0x00 5306                 |       | TIM2_CCMR2     | TIM2 capture/compare mode register 2   | 0x00   |

| 0x00 5307                 |       | TIM2_CCMR3     | TIM2 capture/compare mode register 3   | 0x00   |

| 0x00 5308                 |       | TIM2_CCER1     | TIM2 capture/compare enable register 1 | 0x00   |

| 0x00 5309                 |       | TIM2_CCER2     | TIM2 capture/compare enable register 2 | 0x00   |

| 0x00 530A                 | TIM2  | TIM2_CNTRH     | TIM2 counter high                      | 0x00   |

| 0x00 530B                 |       | TIM2_CNTRL     | TIM2 counter low                       | 0x00   |

| 00 530C0x                 |       | TIM2_PSCR      | TIM2 prescaler register                | 0x00   |

| 0x00 530D                 |       | TIM2_ARRH      | TIM2 auto-reload register high         | 0xFF   |

| 0x00 530E                 |       | TIM2_ARRL      | TIM2 auto-reload register low          | 0xFF   |

| 0x00 530F                 |       | TIM2_CCR1H     | TIM2 capture/compare register 1 high   | 0x00   |

| 0x00 5310                 |       | TIM2_CCR1L     | TIM2 capture/compare register 1 low    | 0x00   |

| 0x00 5311                 |       | TIM2_CCR2H     | TIM2 capture/compare reg. 2 high       | 0x00   |

| 0x00 5312                 |       | TIM2_CCR2L     | TIM2 capture/compare register 2 low    | 0x00   |

| 0x00 5313                 |       | TIM2_CCR3H     | TIM2 capture/compare register 3 high   | 0x00   |

| 0x00 5314                 |       | TIM2_CCR3L     | TIM2 capture/compare register 3 low    | 0x00   |

| 0x00 5315 to<br>0x00 531F |       | Re             | eserved area (11 bytes)                |        |

Table 14. General hardware register map (continued)

|                            | Option                | Option      |   |   |   | Opt      | ion bits  |      |   |                | Factory            |

|----------------------------|-----------------------|-------------|---|---|---|----------|-----------|------|---|----------------|--------------------|

| Addr.                      | name                  | byte<br>no. | 7 | 6 | 5 | 4        | 3         | 2    | 1 | 0              | default<br>setting |

| 0x00<br>480B               | тми                   | OPT6        |   |   |   | ΤN       | IU[3:0]   |      |   |                | 0x00               |

| 0x00<br>480C               | TIMU                  | NOPT6       |   |   |   | NTI      | MU[3:0]   |      |   |                | 0xFF               |

| 0x00<br>480D               | Flash wait            | OPT7        |   |   |   | Reserve  | ed        |      |   | WAIT<br>STATE  | 0x00               |

| 0x00<br>480E               | states                | NOPT7       |   |   |   | Reserve  | ed        |      |   | NWAIT<br>STATE | 0xFF               |

| 0x00<br>480F               |                       |             |   |   |   | Reserved | I         |      |   |                |                    |

| 0x00<br>4810               |                       | OPT8        |   |   |   | TMU_ł    | KEY 1 [7: | 0]   |   |                | 0x00               |

| 0x00<br>4811               |                       | OPT9        |   |   |   | TMU_ł    | KEY 2 [7: | 0]   |   |                | 0x00               |

| 0x00<br>4812               |                       | OPT10       |   |   |   | TMU_ł    | KEY 3 [7: | 0]   |   |                | 0x00               |

| 0x00<br>4813               |                       | OPT11       |   |   |   | TMU_ł    | KEY 4 [7: | 0]   |   |                | 0x00               |

| 0x00<br>4814               | тми                   | OPT12       |   |   |   | TMU_ł    | KEY 5 [7: | 0]   |   |                | 0x00               |

| 0x00<br>4815               |                       | OPT13       |   |   |   | TMU_ł    | KEY 6 [7: | 0]   |   |                | 0x00               |

| 0x00<br>4816               |                       | OPT14       |   |   |   | TMU_ł    | KEY 7 [7: | 0]   |   |                | 0x00               |

| 0x00<br>4817               |                       | OPT15       |   |   |   | TMU_ł    | KEY 8 [7: | 0]   |   |                | 0x00               |

| 0x00<br>4818               |                       | OPT16       |   |   |   | TMU_M    | AXATT [7  | 7:0] |   |                | 0xC7               |

| 0x00<br>4819<br>to<br>487D |                       |             |   |   |   | Reserved | 1         |      |   |                |                    |

| 0x00<br>487E               | Boot-                 | OPT17       |   |   |   | BI       | _ [7:0]   |      |   |                | 0x00               |

| 0x00<br>487F               | loader <sup>(1)</sup> | NOPT<br>17  |   |   |   | NB       | L [7:0]   |      |   |                | 0xFF               |

Table 18. Option bytes (continued)

This option consists of two bytes that must have a complementary value in order to be valid. If the option is invalid, it has no effect on EMC reset.

| Option byte no. | Description                                                                                                                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | LSI_EN: Low speed internal clock enable<br>0: LSI clock is not available as CPU clock source<br>1: LSI clock is available as CPU clock source                                                                                    |

| 0072            | IWDG_HW: Independent watchdog<br>0: IWDG Independent watchdog activated by software<br>1: IWDG Independent watchdog activated by hardware                                                                                        |

| OPT3            | WWDG_HW: Window watchdog activation<br>0: WWDG window watchdog activated by software<br>1: WWDG window watchdog activated by hardware                                                                                            |

|                 | WWDG_HALT: Window watchdog reset on Halt<br>0: No reset generated on Halt if WWDG active<br>1: Reset generated on Halt if WWDG active                                                                                            |

|                 | EXTCLK: External clock selection<br>0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                                                                                           |

| OPT4            | CKAWUSEL: Auto-wakeup unit/clock<br>0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU                                                                                         |

|                 | PRSC[1:0]: AWU clock prescaler<br>00: 24 MHz to 128 kHz prescaler<br>01: 16 MHz to 128 kHz prescaler<br>10: 8 MHz to 128 kHz prescaler<br>11: 4 MHz to 128 kHz prescaler                                                         |

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time<br>This configures the stabilization time to 0.5, 8, 128, and 2048 HSE cycles<br>with corresponding option byte values of 0xE1, 0xD2, 0xB4, and 0x00.                     |

| OPT6            | <b>TMU</b> [3:0]: Enable temporary memory unprotection<br>0101: TMU disabled (permanent ROP).<br>Any other value: TMU enabled.                                                                                                   |

| OPT7            | <ul> <li>WAIT STATE: Wait state configuration</li> <li>This option configures the number of wait states inserted when reading from the Flash/data EEPROM memory.</li> <li>0: No wait state</li> <li>1: One wait state</li> </ul> |

| OPT8            | TMU_KEY 1 [7:0]: Temporary unprotection key 0           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                          |

| OPT9            | TMU_KEY 2 [7:0]: Temporary unprotection key 1           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                          |

| OPT10           | TMU_KEY 3 [7:0]: Temporary unprotection key 2<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                 |

| OPT11           | TMU_KEY 4 [7:0]: Temporary unprotection key 3           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                          |

| Table 19. Option byte description (continued) |

|-----------------------------------------------|

|-----------------------------------------------|

# **10** Electrical characteristics

# 10.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = -40$  °C,  $T_A = 25$  °C, and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production.

#### 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5.0$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

#### 10.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

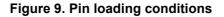

#### 10.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

| Symbol                | Parameter                                      | Conditions              | Min              | Тур               | Мах  | Unit |  |

|-----------------------|------------------------------------------------|-------------------------|------------------|-------------------|------|------|--|

| +                     | V <sub>DD</sub> rise time rate                 | -                       | 2 <sup>(1)</sup> | -                 | 8    |      |  |

| t <sub>VDD</sub>      | V <sub>DD</sub> fall time rate                 | -                       | 2 <sup>(1)</sup> | -                 | ∞    | µs/V |  |

| +                     | Reset release delay                            | V <sub>DD</sub> rising  | -                | 1                 | 1.7  | ms   |  |

| t <sub>TEMP</sub>     | Reset generation delay                         | V <sub>DD</sub> falling | -                | 3                 | -    | μs   |  |

| V <sub>IT+</sub>      | Power-on reset<br>threshold <sup>(2) (3)</sup> | -                       | 2.65             | 2.8               | 2.95 | v    |  |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold                   | -                       | 2.58             | 2.73              | 2.88 | V    |  |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis                  | -                       | -                | 70 <sup>(1)</sup> | -    | mV   |  |

Table 25. Operating conditions at power-up/power-down

1. Guaranteed by design, not tested in production.

2. If V<sub>DD</sub> is below 3 V, the code execution is guaranteed above the V<sub>IT-</sub> and V<sub>IT+</sub> thresholds. RAM content is kept. The EEPROM programming sequence must not be initiated.

3. There is inrush current into V<sub>DD</sub> present after device power on to charge C<sub>EXT</sub> capacitor. This inrush energy depends from C<sub>EXT</sub> capacitor value. For example, a C<sub>EXT</sub> of 1  $\mu$ F requires Q=1  $\mu$ F x 1.8 V = 1.8  $\mu$ C.

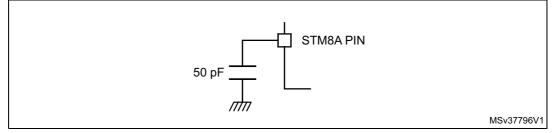

## **10.3.1 VCAP external capacitor**

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 24*. Care should be taken to limit the series inductance to less than 15 nH.

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

#### **10.3.2** Supply current characteristics

The current consumption is measured as described in *Figure 9 on page 59* and *Figure 10 on page 60*.

If not explicitly stated, general conditions of temperature and voltage apply.

| Symbol                               | Parameter                      | Conditions                                                                                                                                                                                                                     |                                                     | Тур  | Мах                 | Unit |

|--------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|---------------------|------|

|                                      |                                | All peripherals                                                                                                                                                                                                                | f <sub>CPU</sub> = 24 MHz 1 ws                      | 8.7  | 16.8 <sup>(2)</sup> |      |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>  |                                | All peripherals<br>clocked, code<br>executed from Flash<br>program memory,<br>HSE external clock<br>(without resonator)<br>All peripherals<br>clocked, code<br>executed from RAM,<br>HSE external clock<br>(without resonator) | f <sub>CPU</sub> = 16 MHz                           | 7.4  | 14                  |      |

|                                      | Supply current in<br>Run mode  |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 8 MHz                            | 4.0  | 7.4 <sup>(2)</sup>  |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 4 MHz                            | 2.4  | 4.1 <sup>(2)</sup>  |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 2 MHz                            | 1.5  | 2.5                 |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 24 MHz                           | 4.4  | 6.0 <sup>(2)</sup>  |      |

|                                      | Supply current in<br>Run mode  |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 16 MHz                           | 3.7  | 5.0                 | mA   |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 8 MHz                            | 2.2  | 3.0 <sup>(2)</sup>  |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 4 MHz                            | 1.4  | 2.0 <sup>(2)</sup>  |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 2 MHz                            | 1.0  | 1.5                 |      |

|                                      | Supply current in<br>Wait mode | CPU stopped, all<br>peripherals off, HSE<br>external clock                                                                                                                                                                     | f <sub>CPU</sub> = 24 MHz                           | 2.4  | 3.1 <sup>(2)</sup>  |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 16 MHz                           | 1.65 | 2.5                 |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 8 MHz                            | 1.15 | 1.9 <sup>(2)</sup>  |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 4 MHz                            | 0.90 | 1.6 <sup>(2)</sup>  |      |

|                                      |                                |                                                                                                                                                                                                                                | f <sub>CPU</sub> = 2 MHz                            | 0.80 | 1.5                 |      |

| I <sub>DD(SLOW)</sub> <sup>(1)</sup> | Supply current in Slow mode    | f <sub>CPU</sub> scaled down,<br>all peripherals off,<br>code executed from<br>RAM                                                                                                                                             | External clock 16 MHz<br>f <sub>CPU</sub> = 125 kHz | 1.50 | 1.95                |      |

|                                      |                                |                                                                                                                                                                                                                                | LSI internal RC<br>f <sub>CPU</sub> = 128 kHz       | 1.50 | 1.80 <sup>(2)</sup> |      |

# Table 26. Total current consumption in Run, Wait and Slow mode. General conditions for V<sub>DD</sub> apply, $T_A$ = -40 °C to 150 °C

1. The current due to I/O utilization is not taken into account in these values.

2. Guaranteed by design, not tested in production.

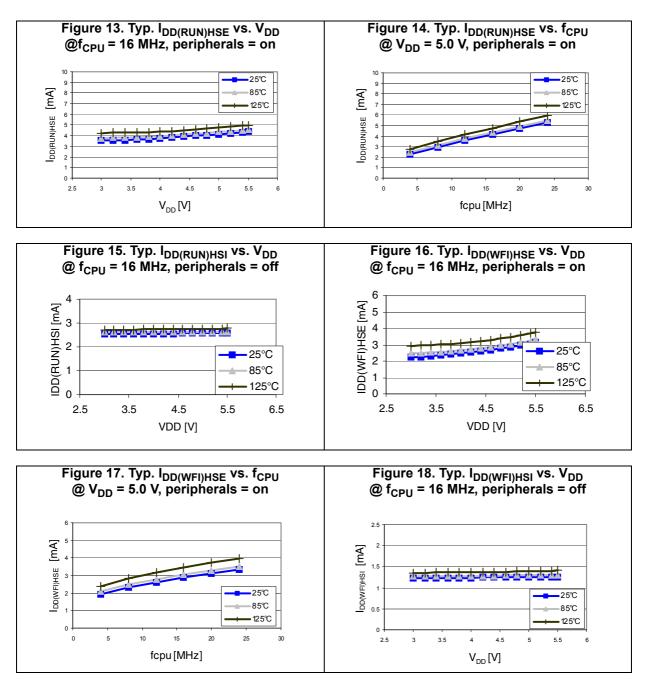

#### **Current consumption curves**

*Figure 13* to *Figure 18* show typical current consumption measured with code executing in RAM.

DocID14395 Rev 15

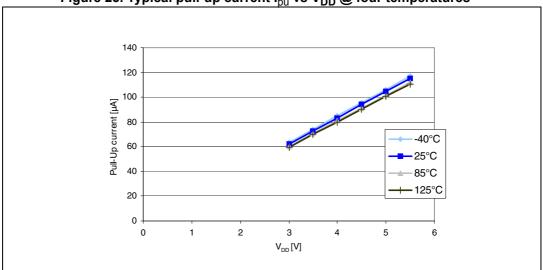

Figure 25. Typical pull-up current I<sub>pu</sub> vs V<sub>DD</sub> @ four temperatures<sup>(1)</sup>

1. The pull-up is a pure resistor (slope goes through 0).

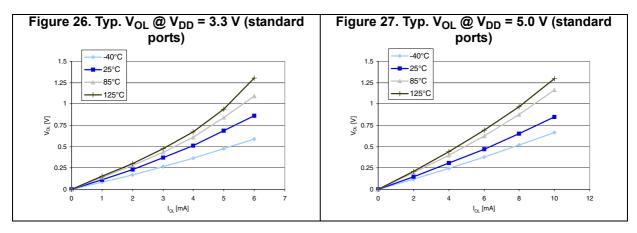

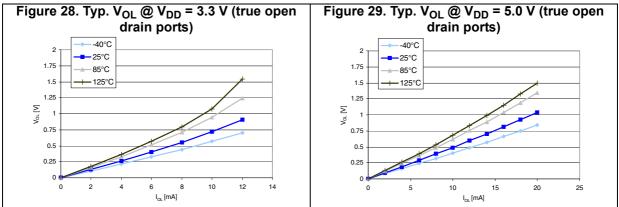

#### Typical output level curves

*Figure 26* to *Figure 35* show typical output level curves measured with output on a single pin.

DocID14395 Rev 15

#### Electromagnetic interference (EMI)

Emission tests conform to the IEC 61967-2 standard for test software, board layout and pin loading.

|                             |                                           | Conditions                  |                   |                                     |           |      |      |  |

|-----------------------------|-------------------------------------------|-----------------------------|-------------------|-------------------------------------|-----------|------|------|--|

| Symbol                      | Parameter                                 | Conorol                     | Monitorod         | Max f <sub>CPU</sub> <sup>(1)</sup> |           |      | Unit |  |

|                             | General<br>conditions                     | Monitored<br>frequency band | 8<br>MHz          | 16<br>MHz                           | 24<br>MHz |      |      |  |

|                             |                                           | V <sub>DD</sub> = 5 V,      | 0.1 MHz to 30 MHz | 15                                  | 17        | 22   |      |  |

| S <sub>EMI</sub> Peak level | T <sub>A</sub> = 25 °C,<br>LQFP80 package | 30 MHz to 130 MHz           | 18                | 22                                  | 16        | dDuV |      |  |

|                             |                                           | conforming to IEC           | 130 MHz to 1 GHz  | -1                                  | 3         | 5    | dBµV |  |

|                             | EMI level                                 | 61967-2                     | -                 | 2                                   | 2.5       | 2.5  | 1    |  |

| Table 46. EMI data |

|--------------------|

|--------------------|

1. Guaranteed by characterization results, not tested in production.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                            | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = 25 \ ^{\circ}C$ , conforming<br>to JESD22-A114 | 3A    | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = 25 °C, conforming<br>to JESD22-C101  | 3     | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (charge device model) | $T_A = 25 \ ^{\circ}C$ , conforming<br>to JESD22-A115 | В     | 200                             |      |

Table 47. ESD absolute maximum ratings

1. Guaranteed by characterization results, not tested in production

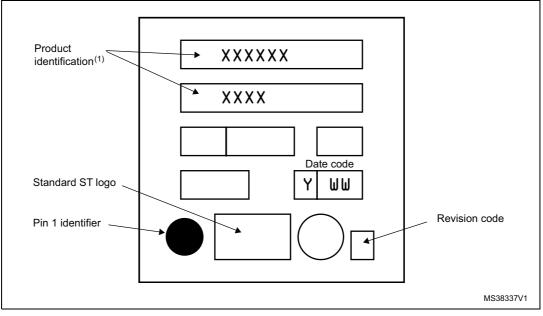

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 56. LQFP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.

# 13 STM8 development tools

Development tools for the STM8A microcontrollers include the

- STice emulation system offering tracing and code profiling

- STVD high-level language debugger including assembler and visual development environment seamless integration of third party C compilers

- STVP Flash programming software

In addition, the STM8A comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

# 13.1 Emulation and in-circuit debugging tools

The STM8 tool line includes the STice emulation system offering a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8A application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full-featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including tracing, profiling and code coverage analysis to help detect execution bottlenecks and dead code.

In addition, STice offers in-circuit debugging and programming of STM8A microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows users to order exactly what they need to meet their development requirements and to adapt their emulation system to support existing and future ST microcontrollers.

# 13.1.1 STice key features

- Program and data trace recording up to 128 K records

- Advanced breakpoints with up to 4 levels of conditions

- Data breakpoints

- Real-time read/write of all device resources during emulation

- Occurrence and time profiling and code coverage analysis (new features)

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- 1 input and 2 output triggers

- USB 2.0 high-speed interface to host PC

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows users to specify the components they need to meet their development requirements and adapt to future requirements

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

## 13.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST visual develop (STVD) IDE and the ST visual programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8.

#### 13.2.1 STM8 toolset

The STM8 toolset with STVD integrated development environment and STVP programming software is available for free download at *www.st.com*. This package includes:

#### ST visual develop

Full-featured integrated development environment from STMicroelectronics, featuring:

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

#### ST visual programmer (STVP)

Easy-to-use, unlimited graphical interface allowing read, write and verification of the STM8A microcontroller's Flash memory. STVP also offers project mode for saving programming configurations and automating programming sequences.

#### 13.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of the application directly from an easy-to-use graphical interface. Available toolchains include:

#### C compiler for STM8

All compilers are available in free version with a limited code size depending on the compiler. For more information, refer to www.cosmic-software.com, www.raisonance.com, and www.iar.com.

#### STM8 assembler linker

Free assembly toolchain included in the STM8 toolset, which allows users to assemble and link their application source code.

| Date        | Revision          | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-Mar-2014 | 10<br>(continued) | <ul> <li>Added:</li> <li><i>Figure 7: STM8AF52x6 VFQFPN32 32-pin pinout;</i></li> <li>the caution in <i>Section 5.10: Input/output specifications,</i></li> <li>The table footnote "Not recommended for new designs" to <i>Table: STM8AF/H/P51xx product line-up with CAN</i> and <i>Table: STM8AF/H/P61xx product line-up without CAN.</i></li> <li>The figure footnotes to <i>Figure 7: STM8AF52x6 VFQFPN32 32-pin pinout</i> and <i>Figure: VFQFPN 32-lead very thin fine pitch quad flat no-lead package (5 x 5)</i></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13-Jun-2014 | 11                | Added STM8AF52A6 part number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 09-Jun-2015 | 12                | <ul> <li>Added:</li> <li>the third table footnote to <i>Table 25: Operating conditions at power-up/power-down</i>,</li> <li><i>Figure 47: LQFP80 marking example (package top view)</i>,</li> <li><i>Figure 50: LQFP64 marking example (package top view)</i>,</li> <li><i>Figure 53: LQFP48 marking example (package top view)</i>,</li> <li><i>Figure 56: LQFP32 marking example (package top view)</i>,</li> <li><i>Figure 59: VFQFPN32 marking example (package top view)</i>,</li> <li><i>Figure 59: VFQFPN32 marking example (package top view)</i>,</li> <li>the footnote about the device marking to <i>Figure 60: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information scheme1</i>.</li> <li>Removed STM8AF51xx and STM8AF61xx obsolete root part numbers, and consequently "H" products:</li> <li><i>Table 1: Device summary</i>,</li> <li><i>Section 2: Description</i>,</li> <li><i>Section 3: Product line-up</i>,</li> <li><i>Table 12: Memory model 128K</i>,</li> <li><i>Section 10.3: Operating conditions</i>,</li> <li><i>Figure 60: STM8AF526x/8x/Ax and STM8AF6269/8x/Ax ordering information scheme1</i>.</li> <li>Moved Section 11.6: Thermal characteristics to Section 11: Package <i>information</i>.</li> <li>Updated:</li> <li>the product naming in the document headers and captions,</li> <li>the standard reference for EMI characteristics in <i>Table 46: EMI data</i>.</li> </ul> |

| 13-Jun-2016 | 13                | Updated Table 53: VFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package mechanical data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 55. Document revision history (continued)