Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                        |  |  |  |  |  |

|----------------------------|--------------------------------------------------------|--|--|--|--|--|

| Product Status             | Obsolete                                               |  |  |  |  |  |

| Core Processor             | 8051                                                   |  |  |  |  |  |

| Core Size                  | 8-Bit                                                  |  |  |  |  |  |

| Speed                      | 12MHz                                                  |  |  |  |  |  |

| Connectivity               | SIO, UART/USART                                        |  |  |  |  |  |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT        |  |  |  |  |  |

| Number of I/O              | 70                                                     |  |  |  |  |  |

| Program Memory Size        | 32KB (32K x 8)                                         |  |  |  |  |  |

| Program Memory Type        | FLASH                                                  |  |  |  |  |  |

| EEPROM Size                | -                                                      |  |  |  |  |  |

| RAM Size                   | 1.25K x 8                                              |  |  |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                            |  |  |  |  |  |

| Data Converters            | A/D 8x12b                                              |  |  |  |  |  |

| Oscillator Type            | Internal                                               |  |  |  |  |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                      |  |  |  |  |  |

| Mounting Type              | Surface Mount                                          |  |  |  |  |  |

| Package / Case             | 80-LQFP                                                |  |  |  |  |  |

| Supplier Device Package    | -                                                      |  |  |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z51f3221atx |  |  |  |  |  |

|                            |                                                        |  |  |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 7.3 A/D Converter Characteristics

#### Table 7-3 A/D Converter Characteristics

|                                 | Character        | 1151105                        | (T <sub>A</sub>        | = -40°C ~ +8 | 5°C, VDD= 1. | .8V ~ 5.5V, V | SS= 0V) |

|---------------------------------|------------------|--------------------------------|------------------------|--------------|--------------|---------------|---------|

| Parameter                       | Symbol           | Co                             | onditions              | MIN          | TYP          | MAX           | Unit    |

| Resolution                      |                  |                                | _                      |              | 12           | -             | bit     |

| Integral Linear Error           | ILE              |                                |                        | _            | _            | ±2            |         |

| Differential Linearity<br>Error | DLE              | AVREF= 2.7V – 5.5V<br>fx= 8MHz |                        | _            | _            | ±1            | LSB     |

| Zero Offset Error               | ZOE              |                                |                        | _            | _            | ±3            |         |

| Full Scale Error                | FSE              |                                |                        | _            | _            | ±3            |         |

| Conversion Time                 | t <sub>CON</sub> | 12bit resol                    | 12bit resolution, 8MHz |              | _            | _             | μS      |

| Analog Input Voltage            | V <sub>AN</sub>  |                                | _                      | AVSS         | -            | AVREF         |         |

| Analog Reference<br>Voltage     | AVREF            |                                | -                      | 1.8          | _            | VDD           | V       |

| Analog Ground<br>Voltage        | AVSS             |                                | _                      | VSS          | _            | VSS+0.3       |         |

| Analog Input Leakage<br>Current | I <sub>AN</sub>  | AVREF= 5.12V                   |                        | _            | _            | 10            | μA      |

|                                 | _                | Enable                         |                        | _            | 1            | 2             | mA      |

| ADC Operating Current           | ADC              | Disable                        | VDD= 5.12V             | -            | _            | 0.1           | μA      |

NOTES) 1. Zero offset error is the difference between 000000000 and the converted output for zero input voltage (VSS).

2. Full scale error is the difference between 1111111111 and the converted output for full-scale input voltage (AVREF).

#### 7.4 Power-On Reset Characteristics

#### Table 7-4 Power-On Reset Characteristics

|                         | (T <sub>A</sub> = -40°C ~ +85°C, VDD= 1.8V ~ 5.5V, VSS= 0V) |            |      |     |     |      |

|-------------------------|-------------------------------------------------------------|------------|------|-----|-----|------|

| Parameter               | Symbol                                                      | Conditions | MIN  | TYP | MAX | Unit |

| RESET Release Level     | V <sub>POR</sub>                                            | _          | -    | 1.4 | _   | V    |

| VDD Voltage Rising Time | t <sub>R</sub>                                              | -          | 0.05 | -   | -   | V/mS |

| POR Current             | IPOR                                                        | _          | _    | 0.2 | _   | μA   |

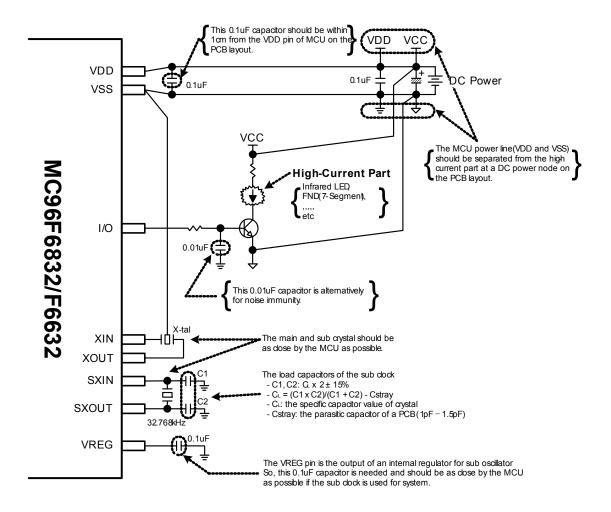

# 7.19 Recommended Circuit and Layout

Figure 7.15 Recommended Circuit and Layout

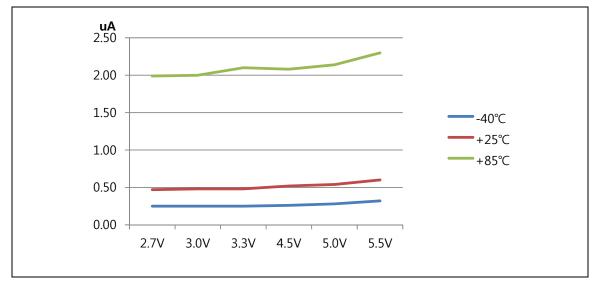

Figure 7.20 STOP (IDD5) Current

# 8. Memory

The Z51F3221 MCU addresses two separate address memory stores: Program memory and Data memory. The logical separation of Program and Data memory allows Data memory to be accessed by 8-bit addresses, which makes the 8-bit CPU access the data memory more rapidly. Nevertheless, 16-bit Data memory addresses can also be generated through the DPTR register.

The Z51F3221 MCU provides on-chip 32k bytes of the ISP type flash program memory, which can be read and written to. Internal data memory (IRAM) is 256 bytes and it includes the stack area. External data memory (XRAM) is 1k bytes and it includes 40 bytes of LCD display RAM.

# 8.1 Program Memory

A 16-bit program counter is capable of addressing up to 64k bytes, but this device has just 32k bytes program memory space.

Figure 8-1 shows the map of the lower part of the program memory. After reset, the CPU begins execution from location 0000H. Each interrupt is assigned a fixed location in program memory. The interrupt causes the CPU to jump to that location, where it commences execution of the service routine. External interrupt 10, for example, is assigned to location 000BH. If external interrupt 10 is going to be used, its service routine must begin at location 000BH. If the interrupt is not going to be used, its service location is available as general purpose program memory. If an interrupt service routine is short enough (as is often the case in control applications), it can reside entirely within that 8 byte interval. Longer service routines can use a jump instruction to skip over subsequent interrupt locations, if other interrupts are in use.

| Name  | Address | Dir | Default | Description                            |

|-------|---------|-----|---------|----------------------------------------|

| P7    | C8H     | R/W | 00H     | P7 Data Register                       |

| P7I0  | С9Н     | R/W | 00H     | P7 Direction Register                  |

| P7PU  | DDH     | R/W | 00H     | P7 Pull-up Resistor Selection Register |

| P7OD  | CFH     | R/W | 00H     | P7 Open-drain Selection Register       |

| P8    | D8H     | R/W | FFH     | P8 Data Register                       |

| P8IO  | D1H     | R/W | FFH     | P8 Direction Register                  |

| P8PU  | DEH     | R/W | 00H     | P8 Pull-up Resistor Selection Register |

| P8OD  | D2H     | R/W | FFH     | P8 Open-drain Selection Register       |

| P9CDR | E8H     | R/W | 00H     | P9 Control and Data Register           |

| PFSR0 | EDH     | R/W | 00H     | Port Function Selection Register 0     |

| PFSR1 | EEH     | R/W | 00H     | Port Function Selection Register 1     |

| PFSR2 | EFH     | R/W | 00H     | Port Function Selection Register 2     |

| PFSR3 | F1H     | R/W | 00H     | Port Function Selection Register 3     |

| PFSR4 | F2H     | R/W | 00H     | Port Function Selection Register 4     |

| PFSR5 | F3H     | R/W | 00H     | Port Function Selection Register 5     |

| PFSR6 | F4H     | R/W | 00H     | Port Function Selection Register 6     |

| PFSR7 | F5H     | R/W | 00H     | Port Function Selection Register 7     |

| PFSR8 | F6H     | R/W | 00H     | Port Function Selection Register 8     |

#### Table 9-1 Register Map (Continued)

# 9.4 P1 Port

# 9.4.1 P1 Port Description

P1 is 7-bit I/O port. P1 control registers consist of P1 data register (P1), P1 direction register (P1IO), debounce enable register (P1DB), P1 pull-up resistor selection register (P1PU), and P1 open-drain selection register (P1OD). Refer to the port function selection registers for the P1 function selection.

#### 9.4.2 Register description for P1

| P1 (P1 Data I | Register) : 88 | н         |               |          |                |       |                    |

|---------------|----------------|-----------|---------------|----------|----------------|-------|--------------------|

| 7             | 6              | 5         | 4             | 3        | 2              | 1     | 0                  |

| _             | P16            | P15       | P14           | P13      | P12            | P11   | P10                |

| _             | RW             | RW        | RW            | RW       | RW             | RW    | RW                 |

|               |                |           |               |          |                |       | Initial value : 08 |

|               | P1[6:0]        |           | I/O Data      |          |                |       |                    |

|               |                |           |               |          |                |       |                    |

| P1IO (P1 Dire | ection Registe | er) : 91H |               |          |                |       |                    |

| 7             | 6              | 5         | 4             | 3        | 2              | 1     | 0                  |

| -             | P1610          | P1510     | P14Ю          | P1310    | P1210          | P1110 | P10IO              |

| -             | RW             | RW        | RW            | RW       | RW             | RW    | RW                 |

|               |                |           |               |          |                |       | Initial value : 08 |

|               | P11            | O[6:0]    | P1 Data I/O D | irection |                |       |                    |

|               |                |           | 0 Input       |          |                |       |                    |

|               |                |           | 1 Outpu       | ut       |                |       |                    |

|               |                |           |               |          | ssible when ir |       |                    |

#### P1PU (P1 Pull-up Resistor Selection Register) : D5H

| 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0                 |    |

|---|-------|-------|-------|-------|-------|-------|-------------------|----|

| - | P16PU | P15PU | P14PU | P13PU | P12PU | P11PU | P10PU             |    |

| _ | RW                |    |

|   |       |       |       |       |       | I     | nitial value : 00 | ЭН |

Configure Pull-up Resistor of P1 Port

P1PU[6:0]

0 Disable

1 Enable

#### P1OD (P1 Open-drain Selection Register) : 93H

| 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0                 |    |

|---|-------|-------|-------|-------|-------|-------|-------------------|----|

| - | P16OD | P15OD | P14OD | P13OD | P120D | P110D | P100D             |    |

| - | RW                |    |

|   |       |       |       |       |       | I     | nitial value : 08 | ЗH |

Configure Open-drain of P1 Port

P1OD[6:0]

0 Push-pull output

1 Open-drain output

# 9.9 P6 Port

## 9.9.1 P6 Port Description

P6 is 8-bit I/O port. P6 control registers consist of P6 data register (P6), P6 direction register (P6IO), P6 pull-up resistor selection register (P6PU) and P6 open-drain selection register (P6OD). Refer to the port function selection registers for the P6 function selection.

# 9.9.2 Register description for P6

| 7                                             | 6                                                       | 5                                                         | 4                                                                                    | 3                                                                   | 2                                        | 1                               | 0                                                 |  |

|-----------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------|---------------------------------|---------------------------------------------------|--|

| P67                                           | P66                                                     | P65                                                       | P64                                                                                  | P63                                                                 | P62                                      | P61                             | P60                                               |  |

| RW                                            | RW                                                      | RW                                                        | RW                                                                                   | RW                                                                  | RW                                       | RW                              | RW                                                |  |

|                                               |                                                         |                                                           |                                                                                      |                                                                     |                                          | I                               | Initial value : 00H                               |  |

|                                               | P6[                                                     | 7:0]                                                      | I/O Data                                                                             |                                                                     |                                          |                                 |                                                   |  |

| 96IO (P6 Dire                                 | ection Regist                                           | er) : C1H                                                 |                                                                                      |                                                                     |                                          |                                 |                                                   |  |

| 7                                             | 6                                                       | 5                                                         | 4                                                                                    | 3                                                                   | 2                                        | 1                               | 0                                                 |  |

| P6710                                         | P66IO                                                   | P6510                                                     | P64IO                                                                                | P63IO                                                               | P6210                                    | P611O                           | P60IO                                             |  |

| RW                                            | RW                                                      | RW                                                        | RW                                                                                   | RW                                                                  | RW                                       | RW                              | RW                                                |  |

|                                               |                                                         |                                                           |                                                                                      |                                                                     |                                          | I                               | Initial value : 00H                               |  |

|                                               | P6l                                                     | O[7:0]                                                    | P6 Data I/O D                                                                        | irection                                                            |                                          |                                 |                                                   |  |

|                                               |                                                         |                                                           | 0 Input                                                                              |                                                                     |                                          |                                 |                                                   |  |

|                                               |                                                         |                                                           | 1 Output                                                                             |                                                                     |                                          |                                 |                                                   |  |

|                                               |                                                         |                                                           | ·                                                                                    |                                                                     |                                          |                                 |                                                   |  |

|                                               |                                                         |                                                           |                                                                                      |                                                                     |                                          |                                 |                                                   |  |

|                                               | II un Posisto                                           | · Salaction I                                             |                                                                                      |                                                                     |                                          |                                 |                                                   |  |

| •                                             | -                                                       |                                                           | Register) : DCI                                                                      |                                                                     | 2                                        | 1                               | 0                                                 |  |

| 7                                             | 6                                                       | 5                                                         | 4                                                                                    | 3                                                                   | 2                                        | 1                               |                                                   |  |

| <b>7</b><br>P67PU                             | <b>6</b><br>P66PU                                       | <b>5</b><br>P65PU                                         | <b>4</b><br>P64PU                                                                    | <b>3</b><br>P63PU                                                   | P62PU                                    | P61PU                           | P60PU                                             |  |

| 7                                             | 6                                                       | 5                                                         | 4                                                                                    | 3                                                                   | r                                        | P61PU<br>RW                     | P60PU<br>RW                                       |  |

| <b>7</b><br>P67PU                             | 6<br>P66PU<br>RW                                        | 5<br>P65PU<br>RW                                          | 4<br>P64PU<br>RW                                                                     | 3<br>P63PU<br>RW                                                    | P62PU<br>RW                              | P61PU<br>RW                     | P60PU                                             |  |

| <b>7</b><br>P67PU                             | 6<br>P66PU<br>RW                                        | <b>5</b><br>P65PU                                         | 4<br>P64PU<br>RW<br>Configure Pull                                                   | 3<br>P63PU<br>RW<br>-up Resistor c                                  | P62PU<br>RW                              | P61PU<br>RW                     | P60PU<br>RW                                       |  |

| 7<br>P67PU                                    | 6<br>P66PU<br>RW                                        | 5<br>P65PU<br>RW                                          | 4<br>P64PU<br>RW<br>Configure Pull<br>0 Disab                                        | 3<br>P63PU<br>RW<br>-up Resistor c                                  | P62PU<br>RW                              | P61PU<br>RW                     | P60PU<br>RW                                       |  |

| 7<br>P67PU                                    | 6<br>P66PU<br>RW                                        | 5<br>P65PU<br>RW                                          | 4<br>P64PU<br>RW<br>Configure Pull                                                   | 3<br>P63PU<br>RW<br>-up Resistor c                                  | P62PU<br>RW                              | P61PU<br>RW                     | P60PU<br>RW                                       |  |

| 7<br>P67PU                                    | 6<br>P66PU<br>RW                                        | 5<br>P65PU<br>RW                                          | 4<br>P64PU<br>RW<br>Configure Pull<br>0 Disab                                        | 3<br>P63PU<br>RW<br>-up Resistor c                                  | P62PU<br>RW                              | P61PU<br>RW                     | P60PU<br>RW                                       |  |

| 7<br>P67PU<br>RW                              | 6<br>P66PU<br>RW                                        | 5<br>P65PU<br>RW<br>PU[7:0]                               | 4<br>P64PU<br>RW<br>Configure Pull<br>0 Disat<br>1 Enab                              | 3<br>P63PU<br>RW<br>-up Resistor c                                  | P62PU<br>RW                              | P61PU<br>RW                     | P60PU<br>RW                                       |  |

| 7<br>P67PU<br>RW                              | 6<br>P66PU<br>RW<br>P6F                                 | 5<br>P65PU<br>RW<br>PU[7:0]                               | 4<br>P64PU<br>RW<br>Configure Pull<br>0 Disat<br>1 Enab                              | 3<br>P63PU<br>RW<br>-up Resistor c                                  | P62PU<br>RW                              | P61PU<br>RW                     | P60PU<br>RW                                       |  |

| 7<br>P67PU<br>RW                              | 6<br>P66PU<br>RW<br>P6F                                 | 5<br>P65PU<br>RW<br>PU[7:0]                               | 4<br>P64PU<br>RW<br>Configure Pull<br>0 Disat<br>1 Enab                              | 3<br>P63PU<br>RW<br>-up Resistor c<br>ble<br>le                     | P62PU<br>RW<br>of P6 Port                | P61PU<br>RW                     | P60PU<br>RW<br>Initial value : 00H                |  |

| 7<br>P67PU<br>RW<br>P60D (P6 Op<br>7          | 6<br>P66PU<br>RW<br>P6F<br>pen-drain Sele               | 5<br>P65PU<br>RW<br>PU[7:0]<br>ection Regis               | 4<br>P64PU<br>RW<br>Configure Pull<br>0 Disat<br>1 Enab                              | 3<br>P63PU<br>RW<br>-up Resistor c<br>ble<br>le<br>3                | P62PU<br>RW<br>of P6 Port                | P61PU<br>RW                     | P60PU<br>RW<br>Initial value : 00H                |  |

| 7<br>P67PU<br>RW<br>P60D (P6 Op<br>7<br>P670D | 6<br>P66PU<br>RW<br>P6F<br>pen-drain Sele<br>6<br>P66OD | 5<br>P65PU<br>RW<br>PU[7:0]<br>ection Regis<br>5<br>P65OD | 4<br>P64PU<br>RW<br>Configure Pull<br>0 Disat<br>1 Enab<br>ster) : BBH<br>4<br>P64OD | 3<br>P63PU<br>RW<br>-up Resistor c<br>ble<br>le<br>3<br>P63OD       | P62PU<br>RW<br>of P6 Port<br>2<br>P62OD  | P61PU<br>RW<br>I<br>P61OD<br>RW | P60PU<br>RW<br>Initial value : 00H                |  |

| 7<br>P67PU<br>RW<br>P60D (P6 Op<br>7<br>P670D | 6<br>P66PU<br>RW<br>P6F<br>P66OD<br>RW                  | 5<br>P65PU<br>RW<br>PU[7:0]<br>ection Regis<br>5<br>P65OD | 4<br>P64PU<br>RW<br>Configure Pull<br>0 Disat<br>1 Enab<br>ster) : BBH<br>4<br>P64OD | 3<br>P63PU<br>RW<br>-up Resistor c<br>ble<br>le<br>3<br>P63OD<br>RW | P62PU<br>RW<br>of P6 Port<br>P62OD<br>RW | P61PU<br>RW<br>I<br>P61OD<br>RW | P60PU<br>RW<br>Initial value : 00H<br>P60OD<br>RW |  |

- 0 Push-pull output

- 1 Open-drain output

# Z51F3221 **Product Specification**

zilog

| PFSR4 (Port Fu | unction Selection | Register 4) : F2H |

|----------------|-------------------|-------------------|

|----------------|-------------------|-------------------|

| 7      | 6      | 5      | 4            | 3            | 2      | 1      | 0                 |

|--------|--------|--------|--------------|--------------|--------|--------|-------------------|

| PFSR47 | PFSR46 | PFSR45 | PFSR44       | PFSR43       | PFSR42 | PFSR41 | PFSR40            |

| RW     | RW     | RW     | RW           | RW           | RW     | RW     | RW                |

|        |        |        |              |              |        |        | Initial value : 0 |

|        | PFS    | SR47   | P63 Function | select       |        |        |                   |

|        |        |        | 0 Por        | t            |        |        |                   |

|        |        |        | 1 SE         | G19 Function |        |        |                   |

|        | PFS    | SR46   | P62 Function | Select       |        |        |                   |

|        |        |        | 0 Por        | t            |        |        |                   |

|        |        |        | 1 SE         | G18 Function |        |        |                   |

|        | PFS    | SR45   | P61 Function | select       |        |        |                   |

|        |        |        | 0 Por        | t            |        |        |                   |

|        |        |        | 1 SE         | G17 Function |        |        |                   |

|        | PFS    | PFSR44 |              | Select       |        |        |                   |

|        |        |        | 0 Por        | t            |        |        |                   |

|        |        |        | 1 SE         | G16 Function |        |        |                   |

|        | PFS    | SR43   | P57 Function | select       |        |        |                   |

|        |        |        | 0 Por        | t            |        |        |                   |

|        |        |        | 1 SE         | G15 Function |        |        |                   |

|        | PFS    | SR42   | P56 Function | Select       |        |        |                   |

|        |        |        | 0 Por        | t            |        |        |                   |

|        |        |        | 1 SE         | G14 Function |        |        |                   |

|        | PFS    | SR41   | P55 Function | select       |        |        |                   |

|        |        |        | 0 Por        | t            |        |        |                   |

|        |        |        | 1 SE         | G13 Function |        |        |                   |

|        | PFS    | SR40   | P54 Function | Select       |        |        |                   |

|        |        |        | 0 Por        | t            |        |        |                   |

|        |        |        | 1 SE         | G12 Function |        |        |                   |

# 11.3.6 Register Description for Watch Dog Timer

| WDTCNT (Wa | WDTCNT (Watch Dog Timer Counter Register: Read Case) : 8EH |           |             |         |          |          |                  |  |  |  |

|------------|------------------------------------------------------------|-----------|-------------|---------|----------|----------|------------------|--|--|--|

| 7          | 6                                                          | 5         | 4           | 3       | 2        | 1        | 0                |  |  |  |

| WDTCNT7    | WDTCNT6                                                    | WDTCNT 5  | WDTCNT4     | WDTCNT3 | WDTCNT 2 | WDTCNT 1 | WDTCNT 0         |  |  |  |

| R          | R                                                          | R         | R           | R       | R        | R        | R                |  |  |  |

|            | WD                                                         | TCNT[7:0] | WDT Counter |         |          | I        | nitial value : 0 |  |  |  |

#### WDTDR (Watch Dog Timer Data Register: Write Case) : 8EH

| 7      | 6      | 5      | 4      | 3      | 2      | 1       | 0                 |   |

|--------|--------|--------|--------|--------|--------|---------|-------------------|---|

| WDTDR7 | WDTDR6 | WDTDR5 | WDTDR4 | WDTDR3 | WDTDR2 | WDTDR 1 | WDTDR0            |   |

| W      | W      | W      | W      | W      | W      | W       | W                 |   |

|        |        |        |        |        |        | I       | nitial value : FF | Ή |

WDTDR[7:0] Set a period

WDT Interrupt Interval=(BIT Interrupt Interval) x(WDTDR Value+1) NOTE) Do not write "0" in the WDTDR register.

#### WDTCR (Watch Dog Timer Control Register) : 8DH

| 7     | 6       | 5     | 4                                                                                                                     | 3                | 2               | 1           | 0      |  |

|-------|---------|-------|-----------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------------|--------|--|

| WDTEN | WDTRSON | WDTCL | -                                                                                                                     | -                | -               | -           | WDTIFR |  |

| RW    | RW      | RW    | -                                                                                                                     | -                | -               | -           | RW     |  |

|       |         |       | Initial valu                                                                                                          |                  |                 |             |        |  |

|       | WD      | TEN   | Control WDT                                                                                                           | Operation        |                 |             |        |  |

|       |         |       | 0 Disa                                                                                                                | ble              |                 |             |        |  |

|       |         |       | 1 Enat                                                                                                                | le               |                 |             |        |  |

|       | WD      | TRSON | Control WDT                                                                                                           | RESET Operat     | tion            |             |        |  |

|       |         |       | 0 Free                                                                                                                | Running 8-bit ti | imer            |             |        |  |

|       |         |       | 1 Wate                                                                                                                | h Dog Timer Rl   | ESET ON         |             |        |  |

|       | WD      | TCL   | Clear WDT C                                                                                                           | ounter           |                 |             |        |  |

|       |         |       | 0 Free                                                                                                                | Run              |                 |             |        |  |

|       |         |       | 1 Clea                                                                                                                | WDT Counter      | (auto clear aft | er 1 Cycle) |        |  |

|       | WD      | TIFR  | When WDT Interrupt occurs, this bit becomes '1'. For clearing bit, w '0' to this bit or auto clear by INT_ACK signal. |                  |                 |             |        |  |

|       |         |       | 0 WDT Interrupt no generation                                                                                         |                  |                 |             |        |  |

|       |         |       | 1 WDT                                                                                                                 | Interrupt gener  | ration          |             |        |  |

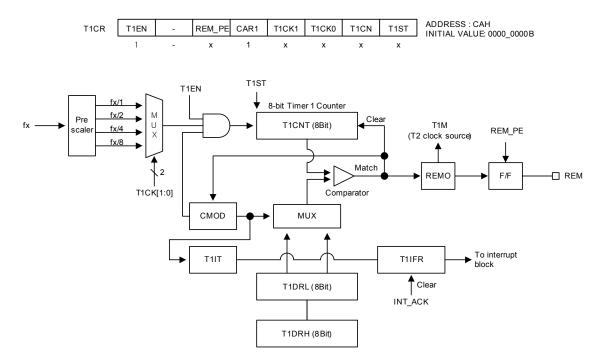

# 11.6.3 8-Bit Timer 1 Carrier Frequency Mode.

The carrier frequency and the pulse of data are calculated by the formula in the following sheet .The Figure 11.16 shows the block diagram of Timer 1 for carrier frequency mode.

#### Figure 11.17 Carrier Mode for Timer 1

NOTE) When one of T1DRH and T1DRL values is "00H", the carrier frequency generator (REM) output always becomes a "High" or "Low". At that time, Timer 1 Interrupt Flag Bit (T1IFR) is not set.

Z51F3221 Product Specification

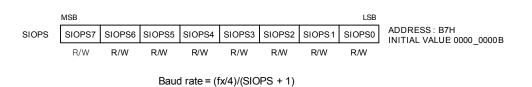

# 11.10.3 SIO Pre-Scaler Register (SIOPS)

SIOPS contains the SIO pre-scaler value. The SIO clock rate (baud rate) is calculated by the following fomula. Baud rate = Input clock (fx/4)/(Pre-scaler value + 1) or SCK input clock, where the input clock is fx/4

Figure 11.27 SIO Pre-Scaler Register (SIOPS)

#### 11.10.4 The usage of SIO

- 1. Select transmitter/receiver mode.

- 2. In transmitter mode, write data to be sent to SIODR.

- 3. Set CCLR to "1" to clear SIO counter and start shifting.

- 4. If Tx or Rx is completed, the SiO interrupt is generated and SIOIFR is set to "1".

- 5. In receiver mode, the received data can be acquired by reading SIODR.

# 11.12.8 UART Transmitter

The UART transmitter is enabled by setting the TXE bit in UARTCR2 register. When the Transmitter is enabled, the TXD pin should be set to TXD function for the serial output pin of UART by the PFSR6[7:6] or PFSR8[5:4]. The baud-rate, operation mode and frame format must be setup once before doing any transmission. In synchronous operation mode, the ACK pin is used as transmission clock, so it should be selected to do ACK function by PFSR6[5:4] or PFSR8[3:2].

# 11.12.8.1 Sending Tx data

A data transmission is initiated by loading the transmit buffer (UARTDR register I/O location) with the data to be transmitted. The data written in transmit buffer is moved to the shift register when the shift register is ready to send a new frame. The shift register is loaded with the new data if it is in idle state or immediately after the last stop bit of the previous frame is transmitted. When the shift register is loaded with new data, it will transfer one complete frame according to the settings of control registers. If the 9-bit characters are used in asynchronous or synchronous operation mode, the ninth bit must be written to the TX8 bit in UARTCR3 register before it is loaded to the transmit buffer (UARTDR register).

# 11.12.8.2 Transmitter flag and interrupt

The UART transmitter has 2 flags which indicate its state. One is UART data register empty flag (UDRE) and the other is transmit complete flag (TXC). Both flags can be interrupt sources.

UDRE flag indicates whether the transmit buffer is ready to receive new data. This bit is set when the transmit buffer is empty and cleared when the transmit buffer contains data to be transmitted but has not yet been moved into the shift register. And also this flag can be cleared by writing '0' to this bit position. Writing '1' to this bit position is prevented.

When the data register empty interrupt enable (UDRIE) bit in UARTCR2 register is set and the global interrupt is enabled, UARTST data register empty interrupt is generated while UDRE flag is set.

The transmit complete (TXC) flag bit is set when the entire frame in the transmit shift register has been shifted out and there is no more data in the transmit buffer. The TXC flag is automatically cleared when the transmit complete interrupt service routine is executed, or it can be cleared by writing '0' to TXC bit in UARTST register.

When the transmit complete interrupt enable (TXCIE) bit in UARTCR2 register is set and the global interrupt is enabled, UART transmit complete interrupt is generated while TXC flag is set.

# 11.12.9.5 Asynchronous Data Reception

To receive asynchronous data frame, the UART includes a clock and data recovery unit. The clock recovery logic is used for synchronizing the internally generated baud-rate clock to the incoming asynchronous serial frame on the RXD pin.

The data recovery logic samples and low pass filters the incoming bits, and this removes the noise of RXD pin.

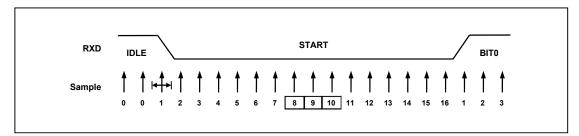

The next figure illustrates the sampling process of the start bit of an incoming frame. The sampling rate is 16 times of the baud-rate in normal mode. The horizontal arrows show the synchronization variation due to the asynchronous sampling process.

#### Figure 11.39 Start Bit Sampling

When the receiver is enabled (RXE=1), the clock recovery logic tries to find a high-to-low transition on the RXD line, the start bit condition. After detecting high to low transition on RXD line, the clock recovery logic uses samples 8,9, and 10 for normal mode to decide if a valid start bit is received. If more than 2 samples have logical low level, it is considered that a valid start bit is detected and the internally generated clock is synchronized to the incoming data frame. And the data recovery can begin. The synchronization process is repeated for each start bit.

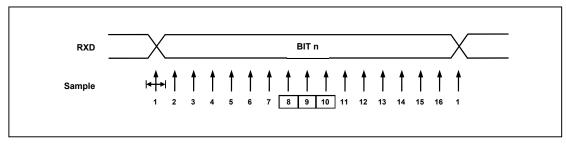

As described above, when the receiver clock is synchronized to the start bit, the data recovery can begin. Data recovery process is almost similar to the clock recovery process. The data recovery logic samples 16 times for each incoming bits, and uses sample 8, 9, and 10 to decide data value. If more than 2 samples have low levels, the received bit is considered to a logic '0' and if more than 2 samples have high levels, the received bit is considered to a logic '1'. The data recovery process is then repeated until a complete frame is received including the first stop bit. The decided bit value is stored in the receive shift register in order. Note that the Receiver only uses the first stop bit of a frame. Internally, after receiving the first stop bit, the Receiver is in idle state and waiting to find start bit.

Figure 11.40 Sampling of Data and Parity Bit

# 11.12.13 Baud Rate setting (example)

| Baud   | fx=1.00MHz |        | fx=1.84 | 32MHz  | fx=2.00MHz |        |

|--------|------------|--------|---------|--------|------------|--------|

| Rate   | UARTBD     | ERROR  | UARTBD  | ERROR  | UARTBD     | ERROR  |

| 2400   | 25         | 0.2%   | 47      | 0.0%   | 51         | 0.2%   |

| 4800   | 12         | 0.2%   | 23      | 0.0%   | 25         | 0.2%   |

| 9600   | 6          | -7.0%  | 11      | 0.0%   | 12         | 0.2%   |

| 14.4k  | 3          | 8.5%   | 7       | 0.0%   | 8          | -3.5%  |

| 19.2k  | 2          | 8.5%   | 5       | 0.0%   | 6          | -7.0%  |

| 28.8k  | 1          | 8.5%   | 3       | 0.0%   | 3          | 8.5%   |

| 38.4k  | 1          | -18.6% | 2       | 0.0%   | 2          | 8.5%   |

| 57.6k  | -          | -      | 1       | -25.0% | 1          | 8.5%   |

| 76.8k  | -          | -      | 1       | 0.0%   | 1          | -18.6% |

| 115.2k | -          | -      | -       | -      | -          | _      |

| 230.4k | -          | -      | -       | -      | _          | -      |

#### Table 11-18 Examples of UARTBD Settings for Commonly Used Oscillator Frequencies

#### (continued)

| Baud   | fx=3.68 | 64MHz | fx=4.0 | 0MHz  | fx=7.37 | 28MHz |

|--------|---------|-------|--------|-------|---------|-------|

| Rate   | UARTBD  | ERROR | UARTBD | ERROR | UARTBD  | ERROR |

| 2400   | 95      | 0.0%  | 103    | 0.2%  | 191     | 0.0%  |

| 4800   | 47      | 0.0%  | 51     | 0.2%  | 95      | 0.0%  |

| 9600   | 23      | 0.0%  | 25     | 0.2%  | 47      | 0.0%  |

| 14.4k  | 15      | 0.0%  | 16     | 2.1%  | 31      | 0.0%  |

| 19.2k  | 11      | 0.0%  | 12     | 0.2%  | 23      | 0.0%  |

| 28.8k  | 7       | 0.0%  | 8      | -3.5% | 15      | 0.0%  |

| 38.4k  | 5       | 0.0%  | 6      | -7.0% | 11      | 0.0%  |

| 57.6k  | 3       | 0.0%  | 3      | 8.5%  | 7       | 0.0%  |

| 76.8k  | 2       | 0.0%  | 2      | 8.5%  | 5       | 0.0%  |

| 115.2k | 1       | 0.0%  | 1      | 8.5%  | 3       | 0.0%  |

| 230.4k | -       | -     | -      | -     | 1       | 0.0%  |

| 250k   | -       | -     | -      | -     | 1       | -7.8% |

| 0.5M   | -       | -     | -      | -     | -       | -     |

#### (continued)

| Baud   | fx=8.0 | 0MHz  | fx=11.0 | 592MHz |

|--------|--------|-------|---------|--------|

| Rate   | UARTBD | ERROR | UARTBD  | ERROR  |

| 2400   | 207    | 0.2%  | -       | -      |

| 4800   | 103    | 0.2%  | 143     | 0.0%   |

| 9600   | 51     | 0.2%  | 71      | 0.0%   |

| 14.4k  | 34     | -0.8% | 47      | 0.0%   |

| 19.2k  | 25     | 0.2%  | 35      | 0.0%   |

| 28.8k  | 16     | 2.1%  | 23      | 0.0%   |

| 38.4k  | 12     | 0.2%  | 17      | 0.0%   |

| 57.6k  | 8      | -3.5% | 11      | 0.0%   |

| 76.8k  | 6      | -7.0% | 8       | 0.0%   |

| 115.2k | 3      | 8.5%  | 5       | 0.0%   |

| 230.4k | 1      | 8.5%  | 2       | 0.0%   |

| 250k   | 1      | 0.0%  | 2       | -7.8%  |

| 0.5M   | -      | -     | -       | -      |

| 1M     | -      | -     | -       | -      |

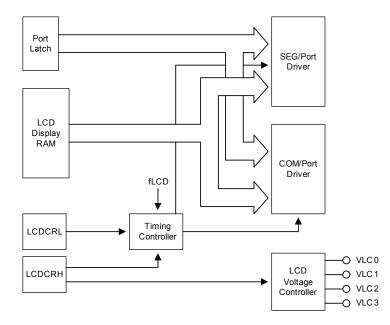

# 11.13 LCD Driver

#### 11.13.1 Overview

The LCD driver is controlled by the LCD Control Register (LCDCRH/L). The LCLK[1:0] determines the frequency of COM signal scanning of each segment output. A RESET clears the LCD control register LCDCRH and LCDCRL values to logic '0'.

The LCD display can continue operating during IDLE and STOP modes if a sub-frequency clock is used as system clock source.

The clock and duty for LCD driver is automatically initialized by hardware, whenever LCDCRH register data value is rewritten. So, don't rewrite LCDCRH frequently.

# 11.13.5 Block Diagram

#### Figure 11.49 LCD Circuit Block Diagram

NOTE) The clock and duty for LCD driver is automatically initialized by hardware, whenever LCDCRH register data value is rewritten. So, don't rewrite LCDCRH frequently

#### 11.13.6 Register Map

#### Table 11-19 LCD Register Map

| Name   | Address | Dir | Default | Description                      |

|--------|---------|-----|---------|----------------------------------|

| LCDCRH | ECH     | R/W | 00H     | LCD Driver Control High Register |

| LCDCRL | EBH     | R/W | 00H     | LCD Driver Control Low Register  |

## 11.13.7 LCD Driver Register Description

LCD driver register has two control registers, LCD driver control high register (LCDCRH) and LCD driver control low register (LCDCRL).

# Z51F3221 Product Specification

# 11.13.8 Register Description for LCD Driver

| 7         | 6                | 5             | 4                                         | 4         | 3                    |                        | 2          | 1               | 0                                              |

|-----------|------------------|---------------|-------------------------------------------|-----------|----------------------|------------------------|------------|-----------------|------------------------------------------------|

| LCDDR     | LD_B3            | LD_B2         | LD                                        | _B1       | LD_B0                | LC                     | LK1        | LCLK0           | DISP                                           |

| RW        | RW               | RW            | R                                         | W         | RW                   | F                      | Ŵ          | RW              | RW                                             |

|           |                  |               |                                           |           |                      |                        |            | I               | nitial value : 00                              |

|           | LCI              | DDR           | LCD Dri                                   | ving Res  | istor for E          | Bias Seleo             | ct         |                 |                                                |

|           |                  |               | 0 Internal LCD driving resistors for bias |           |                      |                        |            |                 |                                                |

|           |                  |               | 1                                         | Externa   | al LCD dr            | iving resis            | stor for l | bias            |                                                |

|           | LD               | _B[3:0]       | LCD Du                                    | ty and Bi | as Selec             | t (NOTE)               |            |                 |                                                |

|           | _                |               | LD_B3                                     | LD_B2     | LD_B1                | LD_B0                  | Descri     | iption          |                                                |

|           |                  |               | 0                                         | 0         | 0                    | 0                      | 1/2Du      | ty, 1/2Bias (10 | )0k ohm)                                       |

|           |                  |               | 0                                         | 0         | 0                    | 1                      | 1/2Du      | ty, 1/2Bias (50 | )k ohm)                                        |

|           |                  |               | 0                                         | 0         | 1                    | 0                      | 1/2Du      | ty, 1/3Bias (50 | )k ohm)                                        |

|           |                  |               | 0                                         | 0         | 1                    | 1                      | 1/3Du      | ty, 1/2Bias (10 | )0k ohm)                                       |

|           |                  |               | 0                                         | 1         | 0                    | 0                      | 1/3Du      | ty, 1/2Bias (50 | )k ohm)                                        |

|           |                  |               | 0                                         | 1         | 0                    | 1                      | 1/3Du      | ty, 1/3Bias (50 | )k ohm)                                        |

|           |                  |               | 0                                         | 1         | 1                    | 0                      | 1/4Du      | ty, 1/2Bias (10 | )0k ohm)                                       |

|           |                  |               | 0                                         | 1         | 1                    | 1                      | 1/4Du      | ty, 1/2Bias (50 | )k ohm)                                        |

|           |                  |               | 1                                         | 0         | 0                    | 0                      | 1/4Du      | ty, 1/3Bias (50 | )k ohm)                                        |

|           |                  |               | 1                                         | 0         | 0                    | 1                      | Not av     | vailable        |                                                |

|           |                  |               | 1                                         | 0         | 1                    | 0                      | Not av     | vailable        |                                                |

|           |                  |               | 1                                         | 0         | 1                    | 1                      | 1/5Du      | ty, 1/3Bias (50 | )k ohm)                                        |

|           |                  |               | 1                                         | 1         | 0                    | 0                      | 1/6Du      | ty, 1/3Bias (50 | )k ohm)                                        |

|           |                  |               | 1                                         | 1         | 0                    | 1                      | 1/6Du      | ty, 1/4Bias (50 | )k ohm)                                        |

|           |                  |               | 1                                         | 1         | 1                    | 0                      | 1/8Du      | ty, 1/3Bias (50 | )k ohm)                                        |

|           |                  |               | 1                                         | 1         | 1                    | 1                      | 1/8Du      | ty, 1/4Bias (50 | )k ohm)                                        |

|           | LCI              | LK[1:0]       | LCD Clo                                   | ock Selec | t (When              | f <sub>wcк</sub> (Wate | ch timer   | · clock)= 32.76 | 68 kHz)                                        |

|           |                  |               | LCLK1                                     | LCLK0     | Descrip              | otion                  |            |                 |                                                |

|           |                  |               | 0                                         | 0         | f <sub>LCD</sub> = 1 | 28Hz                   |            |                 |                                                |

|           |                  |               | 0                                         | 1         | $f_{LCD} = 2$        | 256Hz                  |            |                 |                                                |

|           |                  |               | 1                                         | 0         | $f_{LCD} = 5$        | 512Hz                  |            |                 |                                                |

|           |                  |               | 1                                         | 1         | $f_{LCD} = 1$        | 024Hz                  |            |                 |                                                |

|           |                  |               | ,                                         |           |                      | 0                      |            |                 | ock (f <sub>WCK</sub> ). So<br>y is turned on. |

|           | DIS              | P             | LCD Dis                                   | splay Cor | ntrol                |                        |            |                 |                                                |

|           |                  |               | 0                                         | Display   | off                  |                        |            |                 |                                                |

|           |                  |               | 1                                         | Normal    | display o            | on                     |            |                 |                                                |

| TES) 1. W | /hen 1/2 bias is | s selected, t | he bias le                                | evels are | set as VI            | _C0, VLC               | 2, and \   | /SS             |                                                |

#### LCDCRH (LCD Driver Control High Register) : ECH

2. When 1/3 bias is selected, the bias levels are set as VLC0, VLC1, VLC2 (=VLC3), and VSS

3. When 1/4 bias is selected, the bias levels are set as VLC0, VLC1, VLC2, VLC3, and VSS  $\,$

4. The bias levels are automatically set with appropriate bias circuit when internal bias resistors are used.

5. A bias circuit is connected like the "11.13.4 LCD Voltage Dividing Resistor Connection" and should be selected as an appropriate value for "LD\_B[3:0]".

# 12. Power Down Operation

#### 12.1 Overview

The Z51F3221 MCU features two power-down modes to minimize the power consumption of the device. In power down mode, power consumption is reduced considerably. The device provides three kinds of power saving functions, Main-IDLE, Sub-IDLE and STOP mode. In three modes, program is stopped.

# 12.2 Peripheral Operation in IDLE/STOP Mode

#### Table 12-1 Peripheral Operation during Power Down Mode

| Peripheral             | IDLE Mode                     | STOP Mode                                                                                                             |  |  |

|------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| CPU                    | ALL CPU Operation are Disable | ALL CPU Operation are Disable                                                                                         |  |  |

| RAM                    | Retain                        | Retain                                                                                                                |  |  |

| Basic Interval Timer   | Operates Continuously         | Stop                                                                                                                  |  |  |

| Watch Dog Timer        | Operates Continuously         | Stop (Can be operated with WDTRC OSC)                                                                                 |  |  |

| Watch Timer            | Operates Continuously         | Stop (Can be operated with sub clock)                                                                                 |  |  |

| Timer0~3               | Operates Continuously         | Halted (Only when the Event Counter Mode is<br>Enabled, Timer operates Normally)                                      |  |  |

| ADC                    | Operates Continuously         | Stop                                                                                                                  |  |  |

| BUZ                    | Operates Continuously         | Stop                                                                                                                  |  |  |

| SIO                    | Operates Continuously         | Only operate with external clock                                                                                      |  |  |

| UART                   | Operates Continuously         | Stop                                                                                                                  |  |  |

| LCD Controller         | Operates Continuously         | Stop (Can be operated with sub clock)                                                                                 |  |  |

| Internal OSC<br>(8MHz) | Oscillation                   | Stop when the system clock (fx) is fire                                                                               |  |  |

| WDTRC OSC<br>(6kHz)    | Stop                          | Can be operated with setting value                                                                                    |  |  |

| Main OSC<br>(1~12MHz)  | Oscillation                   | Stop when fx = fxiN                                                                                                   |  |  |

| Sub OSC<br>(32.768kHz) | Oscillation                   | Stop when fx = fsuB                                                                                                   |  |  |

| I/O Port               | Retain                        | Retain                                                                                                                |  |  |

| Control Register       | Retain                        | Retain                                                                                                                |  |  |

| Address Data Bus       | Retain                        | Retain                                                                                                                |  |  |

| Release Method         | By RESET, all Interrupts      | By RESET, Timer Interrupt (EC0,EC3),<br>SIO (External clock), External Interrupt,<br>UART by ACK, WT (sub clock), WDT |  |  |

# 12.5.1 Register Map

| Table 12-2 Power Down | Operation Register Map |

|-----------------------|------------------------|

|-----------------------|------------------------|

| Name | Address | Dir | Default | Description            |

|------|---------|-----|---------|------------------------|

| PCON | 87H     | R/W | 00H     | Power Control Register |

# 12.5.2 Power Down Operation Register Description

The power down operation register consists of the power control register (PCON).

## 12.5.3 Register Description for Power Down Operation

| PCON  | (Power C                 | Control Reg | jister) : 87H |                                   |                |                               |                 |                   |

|-------|--------------------------|-------------|---------------|-----------------------------------|----------------|-------------------------------|-----------------|-------------------|

| 7     | ,                        | 6           | 5             | 4                                 | 3              | 2                             | 1               | 0                 |

| PCC   | DN7                      | -           | _             | -                                 | PCON3          | PCON2                         | PCON1           | PCON0             |

| R     | W                        | -           | _             | -                                 | RW             | RW                            | RW              | RW                |

|       |                          |             |               |                                   |                |                               | I               | nitial value : 00 |

|       |                          | PCO         | ON[7:0]       | Power Control                     |                |                               |                 |                   |

|       |                          |             |               | 01H IDLE r                        | node enable    |                               |                 |                   |

|       |                          |             |               | 03H STOP                          | mode enable    |                               |                 |                   |

| NOTES | 6) 1. To e               | nter IDLE m | ode, PCON     | must be set to                    | '01H'.         |                               |                 |                   |

|       | 2. To e                  | nter STOP i | mode, PCON    | I must be set to                  | ʻ03H'.         |                               |                 |                   |

|       | 3. The                   | PCON regis  | ter is autom  | atically cleared                  | by a release s | ignal in STO                  | P/IDLE mode.    |                   |

|       |                          |             |               | ons must imme<br>he following exa |                | he instructior                | n that make the | e device enter    |

| Ex1)  | MOV<br>NOP<br>NOP<br>NOP | PCON, #0    | )1H ; IDI     | .E mode                           | Ex2)           | MOV F<br>NOP<br>NOP<br>•<br>• | PCON, #03H      | ; STOP moo        |

| Process                  | Description                                                                    | Remarks                                       |  |

|--------------------------|--------------------------------------------------------------------------------|-----------------------------------------------|--|

| 1                        | -No Operation                                                                  |                                               |  |

| 2                        | -1st POR level Detection                                                       | -about 1.4V                                   |  |

|                          | - (INT-OSC 8MHz/8)x256x28h Delay section (=10ms)                               |                                               |  |

| 3                        | -VDD input voltage must rise over than flash operating voltage for Config read | -Slew Rate >= 0.15V/ms                        |  |

|                          |                                                                                | -about 1.5V ~ 1.6V                            |  |

| 4                        | - Config read point                                                            | -Config Value is determined by Writing Option |  |

| (5)                      | - Rising section to Reset Release Level                                        | -16ms point after POR or Ext_reset release    |  |

|                          | - Reset Release section (BIT overflow)                                         |                                               |  |

| 6                        | i) after16ms, after External Reset Release (External reset)                    | - BIT is used for Peripheral stability        |  |

| ļ                        | ii) 16ms point after POR (POR only)                                            |                                               |  |

| $\overline{\mathcal{O}}$ | -Normal operation                                                              |                                               |  |

#### Table 13-2 Boot Process Description