Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | FR60 RISC                                                                       |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 100MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, UART/USART                                    |

| Peripherals                | DMA, LVD, WDT                                                                   |

| Number of I/O              | 104                                                                             |

| Program Memory Size        | 544KB (544K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 40K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 30x10b                                                                      |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f465capmc-gsk5e2 |

# 3. Pin Description

## 3.1 MB91F463CA, MB91F465CA, MB91F467Cx

| Pin no.  | Pin name          | I/O | I/O circuit<br>type* | Function                                     |

|----------|-------------------|-----|----------------------|----------------------------------------------|

| 2 to 9   | P02_0 to P02_7    | I/O | А                    | General-purpose input/output ports           |

|          | P14_0 to P14_7    |     |                      | General-purpose input/output ports           |

| 10 to 17 | ICU0 to ICU7      | I/O | А                    | Input capture input pins                     |

| 10 to 17 | TIN0 to TIN7      | 1/0 | ^                    | External trigger input pins of reload timer  |

|          | TTG8/0 to TTG15/7 |     |                      | External trigger input pins of PPG timer     |

|          | P15_0 to P15_3    |     |                      | General-purpose input/output ports           |

| 20 to 23 | OCU0 to OCU3      | I/O | Α                    | Output compare output pins                   |

|          | TOT0 to TOT3      |     |                      | Reload timer output pins                     |

| 24 to 27 | P17_4 to P17_7    | I/O | А                    | General-purpose input/output ports           |

| 24 10 27 | PPG4 to PPG7      | 1/0 |                      | Output pins of PPG timer                     |

| 28 to 31 | P16_0 to P16_3    | I/O | ۸                    | General-purpose input/output ports           |

| 20 10 31 | PPG8 to PPG11     | 1/0 | A                    | Output pins of PPG timer                     |

|          | P16_4             |     |                      | General-purpose input/output ports           |

| 32       | PPG12             | I/O | Α                    | Output pins of PPG timer                     |

|          | SGA               |     |                      | SGA output pin of sound generator            |

|          | P16_5             |     |                      | General-purpose input/output ports           |

| 33       | PPG13             | I/O | Α                    | Output pins of PPG timer                     |

|          | SGO               |     |                      | SGO output pin of sound generator            |

|          | P16_6             |     |                      | General-purpose input/output ports           |

| 34       | PPG14             | I/O | Α                    | Output pins of PPG timer                     |

|          | PFM               |     |                      | Pulse frequency modulator output pin         |

|          | P16_7             |     |                      | General-purpose input/output ports           |

| 35       | PPG15             | I/O | Α                    | Output pins of PPG timer                     |

|          | ATGX              |     |                      | A/D converter external trigger input pin     |

|          | P20_0             |     |                      | General-purpose input/output ports           |

| 38       | SIN2              | I/O | Α                    | Data input pin of USART2                     |

|          | AIN0              |     |                      | Up/down counter input pin                    |

|          | P20_1             |     |                      | General-purpose input/output ports           |

| 39       | SOT2              | I/O | Α                    | Data output pin of USART2                    |

|          | BIN0              |     |                      | Up/down counter input pin                    |

|          | P20_2             |     |                      | General-purpose input/output ports           |

| 40       | SCK2              | 1/0 | ^                    | Clock input/output pin of USART2             |

| 40       | ZIN0              | I/O | Α                    | Up/down counter input pin                    |

|          | CK2               |     |                      | External clock input pin of free-run timer 2 |

Document Number: 002-04609 Rev. \*A Page 7 of 106

| Туре | Circuit                                                                                                                                                              | Remarks                                                                                                                                                                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С    | pull-up control  pull-down control  R  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  standby control for input shutdown                           | CMOS level output ( $I_{OL}$ = 3mA, $I_{OH}$ = -3mA) 2 different CMOS hysteresis inputs with input shutdown function Automotive input with input shutdown function TTL input with input shutdown function Programmable pull-up resistor: $50k\Omega$ approx.              |

| D    | pull-up control  pull- down control  R  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  TTL input  standby control for input shutdown  analog input | CMOS level output ( $I_{OL}$ = 3mA, $I_{OH}$ = -3mA) 2 different CMOS hysteresis inputs with input shutdown function Automotive input with input shutdown function TTL input with input shutdown function Programmable pull-up resistor: $50k\Omega$ approx. Analog input |

| Туре | Circuit                                                                                                                                                                                   | Remarks                                                                                                                                                                                                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E    | pull-up control  driver strength control  data line  pull- down control  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  TTL input standby control for input shutdown    | CMOS level output (programmable $I_{OL}$ = 5mA, $I_{OH}$ = -5mA and $I_{OL}$ = 2mA, $I_{OH}$ = -2mA, and $I_{OL}$ = 30mA, $I_{OH}$ = -30mA) 2 different CMOS hysteresis inputs with input shutdown function Automotive input with input shutdown function TTL input with input shutdown function Programmable pull-up resistor: $50k\Omega$ approx.              |

| F    | pull-up control driver strength control data line  pull- down control  R CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  standby control for input shutdown analog input | CMOS level output (programmable $I_{OL}$ = 5mA, $I_{OH}$ = -5mA and $I_{OL}$ = 2mA, $I_{OH}$ = -2mA, and $I_{OL}$ = 30mA, $I_{OH}$ = -30mA) 2 different CMOS hysteresis inputs with input shutdown function Automotive input with input shutdown function TTL input with input shutdown function Programmable pull-up resistor: $50k\Omega$ approx. Analog input |

## 5. Handling Devices

#### 5.1 Preventing Latch-up

Latch-up may occur in a CMOS IC if a voltage higher than  $(V_{DD}5, V_{DD}35 \text{ or } HV_{DD}5^{*1})$  or less than  $(V_{SS}5 \text{ or } HV_{SS}5^{*1})$  is applied to an input or output pin or if a voltage exceeding the rating is applied between the power supply pins and ground pins. If latch-up occurs, the power supply current increases rapidly, sometimes resulting in thermal breakdown of the device. Therefore, be very careful not to apply voltages in excess of the absolute maximum ratings.

Note \*1: HV<sub>DD</sub>5, HV<sub>SS</sub>5 are available only on devices having Stepper Motor Controller.

#### 5.2 Handling of unused input pins

If unused input pins are left open, abnormal operation may result. Any unused input pins should be connected to pull-up or pull-down resistor ( $2K\Omega$  to  $10K\Omega$ ) or enable internal pullup or pulldown resisters (PPER/PPCR) before the input enable (PORTEN) is activated by software. The mode pins MD\_x can be connected to  $V_{SS}$ 5 or  $V_{DD}$ 5 directly. Unused ALARM input pins can be connected to  $AV_{SS}$ 5 directly.

#### 5.3 Power supply pins

In MB91460 series, devices including multiple power supply pins and ground pins are designed as follows; pins necessary to be at the same potential are interconnected internally to prevent malfunctions such as latch-up. All of the power supply pins and ground pins must be externally connected to the power supply and ground respectively in order to reduce unnecessary radiation, to prevent strobe signal malfunctions due to the ground level rising and to follow the total output current ratings. Furthermore, the power supply pins and ground pins of the MB91460 series must be connected to the current supply source via a low impedance.

It is also recommended to connect a ceramic capacitor of approximately 0.1  $\mu$ F as a bypass capacitor between power supply pin and ground pin near this device.

This series has a built-in step-down regulator. Connect a bypass capacitor of 4.7  $\mu$ F (use a X7R ceramic capacitor) to VCC18C pin for the regulator.

#### 5.4 Crystal oscillator circuit

Noise in proximity to the X0 (X0A) and X1 (X1A) pins can cause the device to operate abnormally. Printed circuit boards should be designed so that the X0 (X0A) and X1 (X1A) pins, and crystal oscillator, as well as bypass capacitors connected to ground, are located near the device and ground.

It is recommended that the printed circuit board layout be designed such that the X0 and X1 pins or X0A and X1A pins are surrounded by ground plane for the stable operation.

Please request the oscillator manufacturer to evaluate the oscillational characteristics of the crystal and this device.

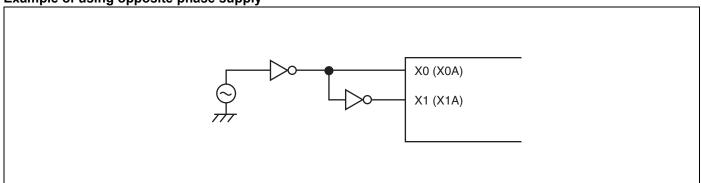

#### 5.5 Notes on using external clock

When using the external clock, it is necessary to simultaneously supply the X0 (X0A) and the X1 (X1A) pins. In the described combination, X1 (X1A) should be supplied with a clock signal which has the opposite phase to the X0 (X0A) pins. At X0 and X1, a frequency up to 16 MHz is possible.

Example of using opposite phase supply

(Continued)

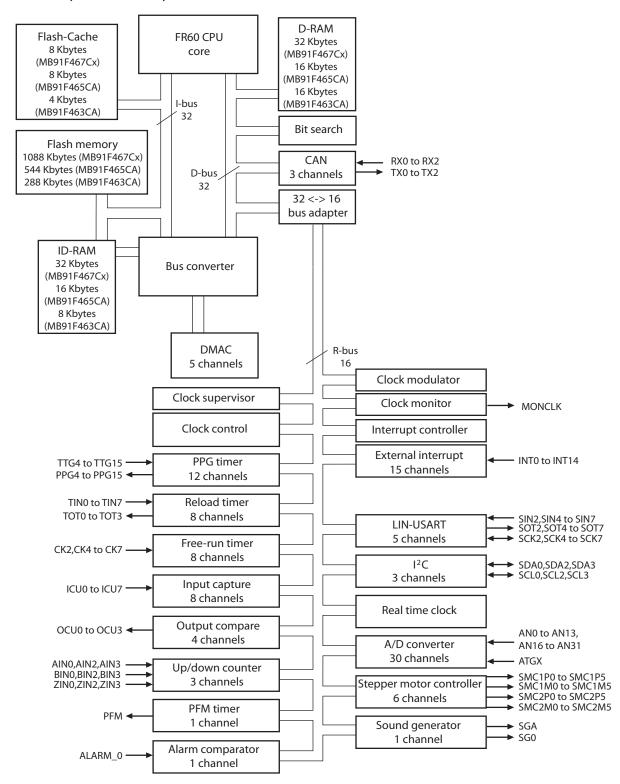

## 7. Block Diagram

#### 7.1 MB91F463CA, MB91F465CA, MB91F467Cx

## 8.3 Programming model

## 8.3.1 Basic programming model

|                                       |          | 32 bits         |               |

|---------------------------------------|----------|-----------------|---------------|

|                                       |          | <del> </del>    | Initial value |

| (                                     | R0       |                 | XXXX XXXXH    |

|                                       | R1       |                 |               |

|                                       | :::      | :::             |               |

| General-purpose registers <           | R12      |                 | • • •         |

|                                       | R13      | AC              | •••           |

|                                       | R14      | FP              | XXXX XXXXH    |

|                                       | R15      | SP              | 0000 0000н    |

| Program counter Program status        | PC<br>RS | — ILM — SCR CCR |               |

| Program status<br>Table base register |          | — ILM — SCR CCR |               |

| Tuble base register                   | TBR      |                 |               |

| Return pointer                        | RP       |                 |               |

| System stack pointer                  | SSP      |                 |               |

| User stack pointer                    | USP      |                 |               |

| Multiply & divide registers           | MDH      |                 |               |

|                                       |          |                 |               |

### 9.3 Flash access in CPU mode

## 9.3.1 Flash configuration

Flash memory map MB91F467Cx

| Address                  |             |             |        |        |                      |           |        |        |         |

|--------------------------|-------------|-------------|--------|--------|----------------------|-----------|--------|--------|---------|

| 0014:FFFFh<br>0014:C000h |             | SA6         | (8KB)  |        |                      | SA7 (     | (8KB)  |        |         |

| 0014:BFFFh<br>0014:8000h |             | SA4         | (8KB)  |        |                      | SA5 (     | (8KB)  |        | ROMS7   |

| 0014:7FFFh<br>0014:4000h |             | SA2         | (8KB)  |        |                      | SA3 (     | (8KB)  |        | HOIVIS7 |

| 0014:3FFFh<br>0014:0000h |             | SA0         | (8KB)  |        | SA1 (8KB)            |           |        |        |         |

| 0013:FFFFh<br>0012:0000h |             | SA22 (64KB) |        |        | SA23 (64KB)          |           |        |        | ROMS6   |

| 0011:FFFFh<br>0010:0000h |             | SA20        | (64KB) |        | SA21 (64KB)          |           |        |        | HOIVIS6 |

| 000F:FFFFh<br>000E:0000h | SA18 (64KB) |             |        |        | SA19 (64KB)          |           |        |        | ROMS5   |

| 000D:FFFFh<br>000C:0000h |             | SA16        | (64KB) |        | SA17 (64KB)          |           |        |        | ROMS4   |

| 000B:FFFFh<br>000A:0000h |             | SA14        | (64KB) |        | SA15 (64KB)          |           |        |        | ROMS3   |

| 0009:FFFFh<br>0008:0000h |             | SA12        | (64KB) |        | SA13 (64KB)          |           |        |        | ROMS2   |

| 0007:FFFFh<br>0006:0000h |             | SA10        | (64KB) |        | SA11 (64KB)          |           |        |        | ROMS1   |

| 0005:FFFFh<br>0004:0000h | SA8 (64KB)  |             |        |        | SA9 (64KB)           |           |        |        | ROMS0   |

| Ÿ                        | addr+0      | addr+1      | addr+2 | addr+3 | addr+4               | addr+5    | addr+6 | addr+7 |         |

| 16bit read/write         | dat[3       | 1:16]       | dat[1  | 5:0]   | dat[31:16] dat[15:0] |           |        |        |         |

| 32bit read/write         |             | dat[3       | 31:0]  |        |                      | dat[31:0] |        |        |         |

| 64bit read               |             |             |        | dat[   | 63:0]                |           |        |        |         |

#### 9.4.2 Pin connections in parallel programming mode

Resetting after setting the MD[2:0] pins to [111] will halt CPU functioning. At this time, the Flash memory's interface circuit enables direct control of the Flash memory unit from external pins by directly linking some of the signals to GP-Ports. Please see table below for signal mapping.

In this mode, the Flash memory appears to the external pins as a stand-alone unit. This mode is generally set when writing/erasing using the parallel Flash programmer. In this mode, all operations of the 8.5 Mbits Flash memory's Auto Algorithms are available.

Correspondence between MBM29LV400TC and Flash Memory Control Signals

| MBM29LV400TC<br>External pins | FR-CPU mode                                     | MB91F46              | Comment          |            |                                           |

|-------------------------------|-------------------------------------------------|----------------------|------------------|------------|-------------------------------------------|

|                               |                                                 | Flash memory<br>mode | Normal function  | Pin number |                                           |

| <del>_</del>                  | INITX                                           | _                    | INITX            | 84         |                                           |

| RESET                         | _                                               | FRSTX                | NMIX             | 85         |                                           |

| _                             | _                                               | MD_2                 | MD_2             | 76         | Set to '1'                                |

| _                             | _                                               | MD_1                 | MD_1             | 75         | Set to '1'                                |

| <del>_</del>                  | _                                               | MD_0                 | MD_0             | 74         | Set to '1'                                |

| RY/BY                         | FMCS:RDY bit                                    | RY/BYX               | GP28_0           | 100        |                                           |

| BYTE                          | Internally fixed to 'H'                         | BYTEX                | GP28_2           | 102        |                                           |

| WE                            |                                                 | WEX                  | GP28_5           | 111        |                                           |

| OE                            | Internal control signal + control via interface | OEX                  | GP28_4           | 110        |                                           |

| CE                            |                                                 | CEX                  | GP20_0           | 38         |                                           |

| <del>_</del>                  |                                                 | ATDIN                | GP17_7           | 27         | Set to '0'                                |

| <del>_</del>                  | circuit                                         | EQIN                 | GP17_6           | 26         | Set to '0'                                |

| <del>_</del>                  |                                                 | TESTX                | GP28_3           | 103        | Set to '1'                                |

| _                             |                                                 | RDYI                 | GP28_1           | 101        | Set to '0'                                |

| A-1                           |                                                 | FA0                  | GP17_5           | 25         | Set to '0'                                |

| A0 to A3                      |                                                 | FA1 to FA4           | GP29_0 to GP29_3 | 92 to 95   |                                           |

| A4 to A7                      |                                                 | FA5 to FA8           | GP29_4 to GP29_7 | 96 to 99   |                                           |

| A8 to A11                     |                                                 | FA9 to FA12          | GP16_0 to GP16_3 | 28 to 31   |                                           |

| A12 to A15                    | Internal address bus                            | FA13 to FA16         | GP16_4 to GP16_7 | 32 to 35   |                                           |

| A16 to A18                    |                                                 | FA17 to FA19         | GP15_0 to GP15_2 | 20 to 22   |                                           |

| A19                           |                                                 | FA20                 | GP15_3           | 23         | Set to '1' on<br>MB91F463CA<br>MB91F465CA |

| _                             |                                                 | FA21                 | GP17_4           | 24         | Set to '1'                                |

| DQ0 to DQ7                    | Internal data bus                               | DQ0 to DQ7           | GP14_0 to GP14_7 | 10 to 17   |                                           |

| DQ8 to DQ15                   |                                                 | DQ8 to DQ15          | GP02_0 to GP02_7 | 2 to 9     |                                           |

## 10. Memory Space

The FR family has 4 Gbytes of logical address space (2<sup>32</sup> addresses) available to the CPU by linear access.

### Direct addressing area

The following address space area is used for I/O.

This area is called direct addressing area, and the address of an operand can be specified directly in an instruction.

The size of directly addressable area depends on the length of the data being accessed as shown below.

$\label{eq:byte} \begin{array}{ll} \text{Byte data access} & :000_H \text{ to } 0\text{FF}_H \\ \text{Half word access} & :000_H \text{ to } 1\text{FF}_H \\ \text{Word data access} & :000_H \text{ to } 3\text{FF}_H \\ \end{array}$

Document Number: 002-04609 Rev. \*A

| Address                                       | Address Register        |                         |                            |                            |                         |  |  |

|-----------------------------------------------|-------------------------|-------------------------|----------------------------|----------------------------|-------------------------|--|--|

|                                               | +0                      | +1                      | +2                         | +3                         |                         |  |  |

| 000D00 <sub>H</sub>                           | Reserved                | Reserved                | PDRD02 [R]<br>XXXXXXXX     | Reserved                   |                         |  |  |

| 000D04 <sub>H</sub>                           | Reserved                | Reserved                | Reserved                   | Reserved                   |                         |  |  |

| 000D08 <sub>H</sub>                           | Reserved                | Reserved                | Reserved                   | Reserved                   |                         |  |  |

| 000D0C <sub>H</sub>                           | Reserved                | Reserved                | PDRD14 [R]<br>XXXXXXXX     | PDRD15 [R]<br>XXXX         | R-bus                   |  |  |

| 000D10 <sub>H</sub>                           | PDRD16 [R]<br>XXXXXXXX  | PDRD17 [R]<br>XXXX      | PDRD18 [R]<br>- XXX - XXX  | PDRD19 [R]<br>- XXX - XXX  | Port Data Direct Read   |  |  |

| 000D14 <sub>H</sub>                           | PDRD20 [R]<br>XXX       | Reserved                | PDRD22 [R]<br>XX - X - X   | PDRD23 [R]<br>- XXXXXXX    | Register                |  |  |

| 000D18 <sub>H</sub>                           | PDRD24 [R]<br>XXXXXXXX  | PDRD25 [R]<br>XXXXXXXX  | PDRD26 [R]<br>XXXXXXXX     | PDRD27 [R]<br>XXXXXXXX     |                         |  |  |

| 000D1C <sub>H</sub>                           | PDRD28 [R]<br>XXXXX     | PDRD29 [R]<br>XXXXXXXX  |                            |                            |                         |  |  |

| 000D20 <sub>H</sub><br>to 000D3C <sub>H</sub> |                         | Res                     | erved                      |                            | Reserved                |  |  |

| 000D40 <sub>H</sub>                           | Reserved                | Reserved                | DDR02 [R/W]<br>00000000    | Reserved                   |                         |  |  |

| 000D44 <sub>H</sub>                           | Reserved                | Reserved                | Reserved                   | Reserved                   |                         |  |  |

| 000D48 <sub>H</sub>                           | Reserved                | Reserved                | Reserved                   | Reserved                   |                         |  |  |

| 000D4C <sub>H</sub>                           | Reserved                | Reserved                | DDR14 [R/W]<br>00000000    | DDR15 [R/W]<br>0000        | R-bus                   |  |  |

| 000D50 <sub>H</sub>                           | DDR16 [R/W]<br>00000000 | DDR17 [R/W]<br>0000     | DDR18 [R/W]<br>- 000 - 000 | DDR19 [R/W]<br>- 000 - 000 | Port Direction Register |  |  |

| 000D54 <sub>H</sub>                           | DDR20 [R/W]<br>000      | Reserved                | DDR22 [R/W]<br>00-0-0      | DDR23 [R/W]<br>- 0000000   | _                       |  |  |

| 000D58 <sub>H</sub>                           | DDR24 [R/W]<br>00000000 | DDR25 [R/W]<br>00000000 | DDR26 [R/W]<br>00000000    | DDR27 [R/W]<br>00000000    |                         |  |  |

| 000D5C <sub>H</sub>                           | DDR28 [R/W]<br>00000    | DDR29 [R/W]<br>00000000 | Reserved                   | Reserved                   |                         |  |  |

| 000D60 <sub>H</sub><br>to 000D7C <sub>H</sub> |                         | Res                     | erved                      |                            | Reserved                |  |  |

| Address                                       |                           | Block                     |                              |                              |                                     |

|-----------------------------------------------|---------------------------|---------------------------|------------------------------|------------------------------|-------------------------------------|

|                                               | +0                        | +0 +1 +2 +3               |                              |                              |                                     |

| 000E80 <sub>H</sub>                           | Reserved                  | Reserved                  | EPILR02 [R/W]<br>00000000    | Reserved                     |                                     |

| 000E84 <sub>H</sub>                           | Reserved                  | Reserved                  | Reserved                     | Reserved                     |                                     |

| 000E88 <sub>H</sub>                           | Reserved                  | Reserved                  | Reserved                     | Reserved                     |                                     |

| 000E8C <sub>H</sub>                           | Reserved                  | Reserved                  | EPILR14 [R/W]<br>00000000    | EPILR15 [R/W]<br>0000        | R-bus Extra                         |

| 000E90 <sub>H</sub>                           | EPILR16 [R/W]<br>00000000 | EPILR17 [R/W]<br>0000     | EPILR18 [R/W]<br>- 000 - 000 | EPILR19 [R/W]<br>- 000 - 000 | Port Input Level<br>Select Register |

| 000E94 <sub>H</sub>                           | EPILR20 [R/W]<br>000      | Reserved                  | EPILR22 [R/W]<br>00-0-0      | EPILR23 [R/W]<br>- 0000000   |                                     |

| 000E98 <sub>H</sub>                           | EPILR24 [R/W]<br>00000000 | EPILR25 [R/W]<br>00000000 | EPILR26 [R/W]<br>00000000    | EPILR27 [R/W]<br>00000000    |                                     |

| 000E9C <sub>H</sub>                           | EPILR28 [R/W]<br>00000    | EPILR29 [R/W]<br>00000000 |                              |                              |                                     |

| 000EA0 <sub>H</sub><br>to 000EBC <sub>H</sub> |                           | Rese                      |                              | Reserved                     |                                     |

| 000EC0 <sub>H</sub>                           | Reserved                  | Reserved                  | PPER02 [R/W]<br>00000000     | Reserved                     |                                     |

| 000EC4 <sub>H</sub>                           | Reserved                  | Reserved                  | Reserved                     | Reserved                     |                                     |

| 000EC8 <sub>H</sub>                           | Reserved                  | Reserved                  | Reserved                     | Reserved                     |                                     |

| 000ECC <sub>H</sub>                           | Reserved                  | Reserved                  | PPER14 [R/W]<br>00000000     | PPER15 [R/W]<br>0000         | R-bus Port                          |

| 000ED0 <sub>H</sub>                           | PPER16 [R/W]<br>00000000  | PPER17 [R/W]<br>0000      | PPER18 [R/W]<br>- 000 - 000  | PPER19 [R/W]<br>- 000 - 000  | Pull-Up/Down Enable<br>Register     |

| 000ED4 <sub>H</sub>                           | PPER20 [R/W]<br>000       | Reserved                  | PPER22 [R/W]<br>00-0-0       | PPER23 [R/W]<br>- 0000000    | _                                   |

| 000ED8 <sub>H</sub>                           | PPER24 [R/W]<br>00000000  | PPER25 [R/W]<br>00000000  | PPER26 [R/W]<br>00000000     | PPER27 [R/W]<br>00000000     |                                     |

| 000EDC <sub>H</sub>                           | PPER28 [R/W]<br>00000     | PPER29 [R/W]<br>00000000  | Reserved                     | Reserved                     |                                     |

| 000EE0 <sub>H</sub><br>to 000EFC <sub>H</sub> |                           | Rese                      | erved                        |                              | Reserved                            |

| Address                                       |                                                          | Register             |                           |                           |                       |  |  |  |  |

|-----------------------------------------------|----------------------------------------------------------|----------------------|---------------------------|---------------------------|-----------------------|--|--|--|--|

|                                               | +0                                                       | +1                   | +2                        | +3                        |                       |  |  |  |  |

| 00C038 <sub>H</sub><br>to 00C03C <sub>H</sub> |                                                          |                      |                           |                           |                       |  |  |  |  |

| 00C040 <sub>H</sub>                           |                                                          | Q0 [R/W]<br>00000001 |                           | MSK0 [R/W]<br>00 00000000 |                       |  |  |  |  |

| 00C044 <sub>H</sub>                           |                                                          | 20 [R/W]<br>11111111 |                           | SK10 [R/W]<br>11 11111111 |                       |  |  |  |  |

| 00C048 <sub>H</sub>                           |                                                          | 20 [R/W]<br>00000000 |                           | RB10 [R/W]<br>00 00000000 |                       |  |  |  |  |

| 00C04C <sub>H</sub>                           |                                                          | R0 [R/W]<br>00000000 | R                         | eserved                   |                       |  |  |  |  |

| 00C050 <sub>H</sub>                           |                                                          | 10 [R/W]<br>00000000 |                           | TA20 [R/W]<br>00 00000000 | CAN 0                 |  |  |  |  |

| 00C054 <sub>H</sub>                           |                                                          | 10 [R/W]<br>00000000 |                           | TB20 [R/W]<br>00 00000000 | IF 2 Register         |  |  |  |  |

| 00C058 <sub>H</sub><br>to 00C05C <sub>H</sub> |                                                          | Res                  | erved                     |                           |                       |  |  |  |  |

| 00C060 <sub>H</sub>                           | IF2DTA20 [R/W] IF2DTA10 [R/W] 00000000 00000000 00000000 |                      |                           |                           |                       |  |  |  |  |

| 00C064 <sub>H</sub>                           |                                                          | 20 [R/W]<br>00000000 |                           | TB10 [R/W]<br>00 00000000 |                       |  |  |  |  |

| 00C068 <sub>H</sub><br>to 00C07C <sub>H</sub> |                                                          | Res                  | erved                     |                           |                       |  |  |  |  |

| 00C080 <sub>H</sub>                           |                                                          | R20 [R]<br>00000000  |                           | EQR10 [R]<br>00 00000000  |                       |  |  |  |  |

| 00C084 <sub>H</sub><br>to 00C08C <sub>H</sub> |                                                          | Res                  | erved                     |                           |                       |  |  |  |  |

| 00C090 <sub>H</sub>                           |                                                          | T20 [R]<br>00000000  |                           | VDT10 [R]<br>00 00000000  |                       |  |  |  |  |

| 00C094 <sub>H</sub><br>to 00C09C <sub>H</sub> |                                                          | Res                  | erved                     |                           | CAN 0<br>Status Flags |  |  |  |  |

| 00C0A0 <sub>H</sub>                           | 00C0A0 <sub>H</sub> INTPND20 [R] 00000000 00000000       |                      |                           | PND10 [R]<br>00 00000000  |                       |  |  |  |  |

| 00C0A4 <sub>H</sub><br>to 00C0AC <sub>H</sub> |                                                          |                      |                           |                           |                       |  |  |  |  |

| 00C0B0 <sub>H</sub>                           |                                                          | AL20 [R]<br>00000000 | 6VAL10 [R]<br>00 00000000 |                           |                       |  |  |  |  |

| 00C0B4 <sub>H</sub><br>to 00C0FC <sub>H</sub> |                                                          | Res                  |                           | Reserved                  |                       |  |  |  |  |

# 13. Interrupt Vector Table

| Intownunt                                   | Inte<br>nu | errupt<br>mber   | Interrup            | ot level *1        | Interr | rupt vector *2         | DMA<br>Resource |

|---------------------------------------------|------------|------------------|---------------------|--------------------|--------|------------------------|-----------------|

| Interrupt                                   | Decimal    | Hexa-<br>decimal | Setting<br>Register | Register address   | Offset | Default Vector address | number          |

| Reset                                       | 0          | 00               | -                   | -                  | 0x3FC  | 0x000FFFFC             |                 |

| Mode vector                                 | 1          | 01               | -                   | -                  | 0x3F8  | 0x000FFFF8             |                 |

| System reserved                             | 2          | 02               | -                   | -                  | 0x3F4  | 0x000FFFF4             |                 |

| System reserved                             | 3          | 03               | -                   | -                  | 0x3F0  | 0x000FFFF0             |                 |

| System reserved                             | 4          | 04               | -                   | -                  | 0x3EC  | 0x000FFFEC             |                 |

| CPU supervisor mode (INT #5 instruction) *6 | 5          | 05               | -                   | -                  | 0x3E8  | 0x000FFFE8             |                 |

| Memory Protection exception *6              | 6          | 06               | -                   | -                  | 0x3E4  | 0x000FFFE4             |                 |

| Co-processor fault trap *5                  | 7          | 07               | -                   | -                  | 0x3E0  | 0x000FFFE0             |                 |

| Co-processor<br>error trap *5               | 8          | 08               | -                   | -                  | 0x3DC  | 0x000FFFDC             |                 |

| INTE instruction *5                         | 9          | 09               | -                   | -                  | 0x3D8  | 0x000FFFD8             |                 |

| Instruction break exception *5              | 10         | 0A               | -                   | -                  | 0x3D4  | 0x000FFFD4             |                 |

| Operand break trap *5                       | 11         | 0B               | -                   | -                  | 0x3D0  | 0x000FFFD0             |                 |

| Step trace trap *5                          | 12         | 0C               | -                   | -                  | 0x3CC  | 0x000FFFCC             |                 |

| NMI interrupt (tool)*5                      | 13         | 0D               | -                   | -                  | 0x3C8  | 0x000FFFC8             |                 |

| Undefined instruction exception             | 14         | 0E               | -                   | -                  | 0x3C4  | 0x000FFFC4             |                 |

| NMI request                                 | 15         | 0F               | F <sub>H</sub>      | fixed              | 0x3C0  | 0x000FFFC0             |                 |

| External Interrupt 0                        | 16         | 10               | ICDOO               | 0×440              | 0x3BC  | 0x000FFFBC             | 0, 16           |

| External Interrupt 1                        | 17         | 11               | ICR00               | 0x440              | 0x3B8  | 0x000FFFB8             | 1, 17           |

| External Interrupt 2                        | 18         | 12               | ICR01               | 0x441              | 0x3B4  | 0x000FFFB4             | 2, 18           |

| External Interrupt 3                        | 19         | 13               | ICKUI               | UX <del>44</del> I | 0x3B0  | 0x000FFFB0             | 3, 19           |

| External Interrupt 4                        | 20         | 14               | ICB02               | 0v442              | 0x3AC  | 0x000FFFAC             | 20              |

| External Interrupt 5                        | 21         | 15               | ICR02               | 0x442              | 0x3A8  | 0x000FFFA8             | 21              |

| External Interrupt 6                        | 22         | 16               | ICDO2               | 0.440              | 0x3A4  | 0x000FFFA4             | 22              |

| External Interrupt 7                        | 23         | 17               | ICR03               | 0x443              | 0x3A0  | 0x000FFFA0             | 23              |

| External Interrupt 8                        | 24         | 18               | ICR04               | 0v444              | 0x39C  | 0x000FFF9C             |                 |

| External Interrupt 9                        | 25         | 19               | 10KU4               | 0x444              | 0x398  | 0x000FFF98             |                 |

| External Interrupt 10                       | 26         | 1A               | ICR05               | 0x445              | 0x394  | 0x000FFF94             |                 |

| External Interrupt 11                       | 27         | 1B               | ICKUS               | UX <del>+4</del> 0 | 0x390  | 0x000FFF90             |                 |

| External Interrupt 12                       | 28         | 1C               | ICR06               | 0x446              | 0x38C  | 0x000FFF8C             |                 |

| External Interrupt 13                       | 29         | 1D               | ICKUU               | UX <del>44</del> 0 | 0x388  | 0x000FFF88             |                 |

Document Number: 002-04609 Rev. \*A

| Interrupt                               |         | errupt<br>mber   | Interrupt level *1  |                    | Interrupt vector *2 |                        | DMA<br>Resource |

|-----------------------------------------|---------|------------------|---------------------|--------------------|---------------------|------------------------|-----------------|

| Interrupt                               | Decimal | Hexa-<br>decimal | Setting<br>Register | Register address   | Offset              | Default Vector address | number          |

| USART (LIN, FIFO) 4 RX                  | 66      | 42               | ICR25               | 0×450              | 0x2F4               | 0x000FFEF4             | 10, 56          |

| USART (LIN, FIFO) 4 TX                  | 67      | 43               | ICR25               | 0x459              | 0x2F0               | 0x000FFEF0             | 11, 57          |

| USART (LIN, FIFO) 5 RX                  | 68      | 44               | ICDOC               | 0.454              | 0x2EC               | 0x000FFEEC             | 12, 58          |

| USART (LIN, FIFO) 5 TX                  | 69      | 45               | ICR26               | 0x45A              | 0x2E8               | 0x000FFEE8             | 13, 59          |

| USART (LIN, FIFO) 6 RX                  | 70      | 46               | 10007               | 0450               | 0x2E4               | 0x000FFEE4             | 60              |

| USART (LIN, FIFO) 6 TX                  | 71      | 47               | ICR27               | 0x45B              | 0x2E0               | 0x000FFEE0             | 61              |

| USART (LIN, FIFO) 7 RX                  | 72      | 48               | IODOO               | 0450               | 0x2DC               | 0x000FFEDC             | 62              |

| USART (LIN, FIFO) 7 TX                  | 73      | 49               | ICR28               | 0x45C              | 0x2D8               | 0x000FFED8             | 63              |

| I <sup>2</sup> C 0 / I <sup>2</sup> C 2 | 74      | 4A               | ICDOO               | 0.450              | 0x2D4               | 0x000FFED4             |                 |

| I <sup>2</sup> C 3                      | 75      | 4B               | ICR29               | 0x45D              | 0x2D0               | 0x000FFED0             |                 |

| Reserved                                | 76      | 4C               | IODOO               | 0455               | 0x2CC               | 0x000FFECC             | 64              |

| Reserved                                | 77      | 4D               | ICR30               | 0x45E              | 0x2C8               | 0x000FFEC8             | 65              |

| Reserved                                | 78      | 4E               | 10001               | 0.455              | 0x2C4               | 0x000FFEC4             | 66              |

| Reserved                                | 79      | 4F               | ICR31               | 0x45F              | 0x2C0               | 0x000FFEC0             | 67              |

| Reserved                                | 80      | 50               | IODOO               | 0x460              | 0x2BC               | 0x000FFEBC             | 68              |

| Reserved                                | 81      | 51               | ICR32               | UX <del>4</del> 60 | 0x2B8               | 0x000FFEB8             | 69              |

| Reserved                                | 82      | 52               | ICD22               | 0.404              | 0x2B4               | 0x000FFEB4             | 70              |

| Reserved                                | 83      | 53               | ICR33               | 0x461              | 0x2B0               | 0x000FFEB0             | 71              |

| Reserved                                | 84      | 54               | ICD24               | 0.400              | 0x2AC               | 0x000FFEAC             | 72              |

| Reserved                                | 85      | 55               | ICR34               | 0x462              | 0x2A8               | 0x000FFEA8             | 73              |

| Reserved                                | 86      | 56               | ICD25               | 0v462              | 0x2A4               | 0x000FFEA4             | 74              |

| Reserved                                | 87      | 57               | ICR35               | 0x463              | 0x2A0               | 0x000FFEA0             | 75              |

| Reserved                                | 88      | 58               | ICDac               | 0×404              | 0x29C               | 0x000FFE9C             | 76              |

| Reserved                                | 89      | 59               | ICR36               | 0x464              | 0x298               | 0x000FFE98             | 77              |

| Reserved                                | 90      | 5A               | ICD27               | 0×465              | 0x294               | 0x000FFE94             | 78              |

| Reserved                                | 91      | 5B               | ICR37               | 0x465              | 0x290               | 0x000FFE90             | 79              |

| Input Capture 0                         | 92      | 5C               | ICD20               | 0×466              | 0x28C               | 0x000FFE8C             | 80              |

| Input Capture 1                         | 93      | 5D               | - ICR38             | 0x466              | 0x288               | 0x000FFE88             | 81              |

| Input Capture 2                         | 94      | 5E               | ICD20               | 0.467              | 0x284               | 0x000FFE84             | 82              |

| Input Capture 3                         | 95      | 5F               | ICR39               | 0x467              | 0x280               | 0x000FFE80             | 83              |

| Input Capture 4                         | 96      | 60               | ICD40               | 0v400              | 0x27C               | 0x000FFE7C             | 84              |

| Input Capture 5                         | 97      | 61               | ICR40               | 0x468              | 0x278               | 0x000FFE78             | 85              |

| Input Capture 6                         | 98      | 62               | ICD44               | 0v460              | 0x274               | 0x000FFE74             | 86              |

| Input Capture 7                         | 99      | 63               | ICR41               | 0x469              | 0x270               | 0x000FFE70             | 87              |

| Output Compare 0                        | 100     | 64               | 100.40              | 0.404              | 0x26C               | 0x000FFE6C             | 88              |

| Output Compare 1                        | 101     | 65               | ICR42               | 0x46A              | 0x268               | 0x000FFE68             | 89              |

| Modulation<br>Degree<br>(k)           | Random No<br>(N) | CMPR<br>[hex]                         | Basecik<br>[MHz] | Fmin<br>[MHz] | Fmax<br>[MHz]                         |

|---------------------------------------|------------------|---------------------------------------|------------------|---------------|---------------------------------------|

| 1                                     | 3                | 026F                                  | 60               | 54.9          | 66.1                                  |

| 1                                     | 5                | 02AE                                  | 60               | 51.9          | 71                                    |

| 1                                     | 7                | 02ED                                  | 60               | 49.3          | 76.7                                  |

| 1                                     | 9                | 032C                                  | 60               | 46.9          | 83.3                                  |

| 1                                     | 11               | 036B                                  | 60               | 44.7          | 91.3                                  |

| 2                                     | 3                | 046E                                  | 60               | 51.9          | 71                                    |

| 2                                     | 5                | 04AC                                  | 60               | 46.9          | 83.3                                  |

| 3                                     | 3                | 066D                                  | 60               | 49.3          | 76.7                                  |

| 4                                     | 3                | 086C                                  | 60               | 46.9          | 83.3                                  |

| 5                                     | 3                | 0A6B                                  | 60               | 44.7          | 91.3                                  |

| 1                                     | 3                | 026F                                  | 56               | 51.4          | 61.6                                  |

| 1                                     | 5                | 02AE                                  | 56               | 48.6          | 66.1                                  |

| 1                                     | 7                | 02ED                                  | 56               | 46.1          | 71.4                                  |

| 1                                     | 9                | 032C                                  | 56               | 43.8          | 77.6                                  |

| 1                                     | 11               | 036B                                  | 56               | 41.8          | 84.9                                  |

| 1                                     | 13               | 03AA                                  | 56               | 39.9          | 93.8                                  |

| 2                                     | 3                | 046E                                  | 56               | 48.6          | 66.1                                  |

| 2                                     | 5                | 04AC                                  | 56               | 43.8          | 77.6                                  |

| 2                                     | 7                | 04EA                                  | 56               | 39.9          | 93.8                                  |

| 3                                     | 3                | 066D                                  | 56               | 46.1          | 71.4                                  |

| 3                                     | 5                | 06AA                                  | 56               | 39.9          | 93.8                                  |

| 4                                     | 3                | 086C                                  | 56               | 43.8          | 77.6                                  |

| 5                                     | 3                | 0A6B                                  | 56               | 41.8          | 84.9                                  |

| 6                                     | 3                | 0C6A                                  | 56               | 39.9          | 93.8                                  |

| 1                                     | 3                | 026F                                  | 52               | 47.8          | 57                                    |

| 1                                     | 5                | 02AE                                  | 52               | 45.2          | 61.2                                  |

| 1                                     | 7                | 02ED                                  | 52               | 42.9          | 66.1                                  |

| 1                                     | 9                | 032C                                  | 52               | 40.8          | 71.8                                  |

| 1                                     | 11               | 036B                                  | 52               | 38.8          | 78.6                                  |

| 1                                     | 13               | 03AA                                  | 52               | 37.1          | 86.8                                  |

| 1                                     | 15               | 03E9                                  | 52               | 35.5          | 96.9                                  |

| 2                                     | 3                | 046E                                  | 52               | 45.2          | 61.2                                  |

| 2                                     | 5                | 04AC                                  | 52               | 40.8          | 71.8                                  |

| 2                                     | 7                | 04EA                                  | 52               | 37.1          | 86.8                                  |

| 3                                     | 3                | 066D                                  | 52               | 42.9          | 66.1                                  |

| 3                                     | 5                | 06AA                                  | 52               | 37.1          | 86.8                                  |

| 4                                     | 3                | 086C                                  | 52               | 40.8          | 71.8                                  |

| · · · · · · · · · · · · · · · · · · · | ·                | · · · · · · · · · · · · · · · · · · · | ·                |               | · · · · · · · · · · · · · · · · · · · |

| Modulation<br>Degree<br>(k) | Random No<br>(N) | CMPR<br>[hex] | Basecik<br>[MHz] | Fmin<br>[MHz] | Fmax<br>[MHz] |

|-----------------------------|------------------|---------------|------------------|---------------|---------------|

| 5                           | 3                | 0A6B          | 52               | 38.8          | 78.6          |

| 6                           | 3                | 0C6A          | 52               | 37.1          | 86.8          |

| 7                           | 3                | 0E69          | 52               | 35.5          | 96.9          |

| 1                           | 3                | 026F          | 48               | 44.2          | 52.5          |

| 1                           | 5                | 02AE          | 48               | 41.8          | 56.4          |

| 1                           | 7                | 02ED          | 48               | 39.6          | 60.9          |

| 1                           | 9                | 032C          | 48               | 37.7          | 66.1          |

| 1                           | 11               | 036B          | 48               | 35.9          | 72.3          |

| 1                           | 13               | 03AA          | 48               | 34.3          | 79.9          |

| 1                           | 15               | 03E9          | 48               | 32.8          | 89.1          |

| 2                           | 3                | 046E          | 48               | 41.8          | 56.4          |

| 2                           | 5                | 04AC          | 48               | 37.7          | 66.1          |

| 2                           | 7                | 04EA          | 48               | 34.3          | 79.9          |

| 3                           | 3                | 066D          | 48               | 39.6          | 60.9          |

| 3                           | 5                | 06AA          | 48               | 34.3          | 79.9          |

| 4                           | 3                | 086C          | 48               | 37.7          | 66.1          |

| 5                           | 3                | 0A6B          | 48               | 35.9          | 72.3          |

| 6                           | 3                | 0C6A          | 48               | 34.3          | 79.9          |

| 7                           | 3                | 0E69          | 48               | 32.8          | 89.1          |

| 1                           | 3                | 026F          | 44               | 40.6          | 48.1          |

| 1                           | 5                | 02AE          | 44               | 38.4          | 51.6          |

| 1                           | 7                | 02ED          | 44               | 36.4          | 55.7          |

| 1                           | 9                | 032C          | 44               | 34.6          | 60.4          |

| 1                           | 11               | 036B          | 44               | 33            | 66.1          |

| 1                           | 13               | 03AA          | 44               | 31.5          | 73            |

| 1                           | 15               | 03E9          | 44               | 30.1          | 81.4          |

| 2                           | 3                | 046E          | 44               | 38.4          | 51.6          |

| 2                           | 5                | 04AC          | 44               | 34.6          | 60.4          |

| 2                           | 7                | 04EA          | 44               | 31.5          | 73            |

| 2                           | 9                | 0528          | 44               | 28.9          | 92.1          |

| 3                           | 3                | 066D          | 44               | 36.4          | 55.7          |

| 3                           | 5                | 06AA          | 44               | 31.5          | 73            |

| 4                           | 3                | 086C          | 44               | 34.6          | 60.4          |

| 4                           | 5                | 08A8          | 44               | 28.9          | 92.1          |

| 5                           | 3                | 0A6B          | 44               | 33            | 66.1          |

| 6                           | 3                | 0C6A          | 44               | 31.5          | 73            |

| 7                           | 3                | 0E69          | 44               | 30.1          | 81.4          |

|                             |                  |               |                  |               |               |

(V<sub>DD</sub>5 = AV<sub>CC</sub>5 = 3.0 V to 5.5 V, V<sub>SS</sub>5 = AV<sub>SS</sub>5 = 0 V, T<sub>A</sub> = -40 °C to + 105 °C)

| _                     | Symbol             | Pin<br>name                 |                                                                                                                                                                                            |                       | Value   |                     | Remarks |                                              |

|-----------------------|--------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------|---------------------|---------|----------------------------------------------|

| Parameter             |                    |                             | Condition                                                                                                                                                                                  | Min                   | Min Typ |                     |         |                                              |

| Input "L" voltage     | V <sub>ILXDF</sub> | X0                          | _                                                                                                                                                                                          | V <sub>SS</sub> - 0.3 | _       | $0.2 \times V_{DD}$ | V       | External clock in<br>"Fast Clock Input mode" |

|                       | V <sub>OH2</sub>   | Normal<br>outputs           | $\begin{aligned} &4.5\text{V} \leq \text{V}_{DD} \leq 5.5\text{V}, \\ &I_{OH} = -2\text{mA} \\ &3.0\text{V} \leq \text{V}_{DD} \leq 4.5\text{V}, \\ &I_{OH} = -1.6\text{mA} \end{aligned}$ | V <sub>DD</sub> — 0.5 |         |                     | V       | Driving strength set to 2 mA                 |

|                       | V <sub>OH5</sub>   | Normal<br>outputs           | $\begin{aligned} &4.5\text{V} \leq \text{V}_{DD} \leq 5.5\text{V}, \\ &I_{OH} = -5\text{mA} \\ &3.0\text{V} \leq \text{V}_{DD} \leq 4.5\text{V}, \\ &I_{OH} = -3\text{mA} \end{aligned}$   | V <sub>DD</sub> — 0.5 |         |                     | V       | Driving strength set to 5 mA                 |

| Output "H" voltage    | V <sub>OH3</sub>   | I <sup>2</sup> C<br>outputs | $\begin{array}{l} 3.0V \leq V_{DD} \leq 5.5V, \\ I_{OH} =  -3\text{mA} \end{array}$                                                                                                        | V <sub>DD</sub> - 0.5 |         | _                   | V       |                                              |

|                       | V <sub>OH30</sub>  | High<br>current<br>outputs  | $\begin{aligned} 4.5 \text{V} &\leq \text{V}_{DD} \leq 5.5 \text{V}, \\ \text{T}_{A} &= -40 ^{\circ} \text{C}, \\ \text{I}_{OH} &= -40 \text{mA} \end{aligned}$                            | V <sub>DD</sub> - 0.5 |         |                     | ٧       | Driving strength set to 30mA                 |

|                       |                    |                             | $4.5V \le V_{DD} \le 5.5V,$ $I_{OH} = -30\text{mA}$                                                                                                                                        |                       |         |                     |         |                                              |

|                       |                    |                             | $3.0V \le V_{DD} \le 4.5V$ , $I_{OH} = -20mA$                                                                                                                                              |                       |         |                     |         |                                              |

|                       | V <sub>OL2</sub>   | Normal<br>outputs           | $\begin{array}{l} 4.5V \leq V_{DD} \leq 5.5V, \\ I_{OH} = \ + \ 2mA \end{array}$                                                                                                           |                       | _       | 0.4                 | V       | Driving strength set                         |

|                       |                    |                             | $\begin{array}{l} 3.0 \text{V} \leq \text{V}_{DD} \leq 4.5 \text{V}, \\ \text{I}_{OH} = \ + \ 1.6 \text{mA} \end{array}$                                                                   |                       |         |                     |         | to 2 mA                                      |

| Output "L" -voltage   | $V_{OL5}$          | Normal<br>outputs           | $\begin{array}{l} 4.5V \leq V_{DD} \leq 5.5V, \\ I_{OH} = \ + \ 5mA \end{array}$                                                                                                           |                       | _       | 0.4                 | V       | Driving strength set                         |

|                       |                    |                             | $\begin{array}{l} 3.0 \text{V} \leq \text{V}_{DD} \leq 4.5 \text{V}, \\ \text{I}_{OH} = \ + \ 3 \text{mA} \end{array}$                                                                     |                       |         |                     |         | to 5 mA                                      |

|                       | V <sub>OL3</sub>   | I <sup>2</sup> C<br>outputs | $\begin{array}{l} 3.0 \text{V} \leq \text{V}_{DD} \leq 5.5 \text{V}, \\ \text{I}_{OH} = \ + \ 3 \text{mA} \end{array}$                                                                     | —                     | _       | 0.4                 | V       |                                              |

|                       | V <sub>OL30</sub>  | High<br>current<br>outputs  | $4.5V \le V_{DD} \le 5.5V$ ,<br>$T_A = -40^{\circ}C$ ,<br>$I_{OH} = +40mA$                                                                                                                 |                       |         | 0.5                 | V       | Deixing atreaugh and                         |

|                       |                    |                             | $4.5V \le V_{DD} \le 5.5V,$ $I_{OH} = +30\text{mA}$                                                                                                                                        |                       |         |                     |         | Driving strength set<br>to 30mA              |

|                       |                    |                             | $3.0V \le V_{DD} \le 4.5V,$<br>$I_{OH} = +20mA$                                                                                                                                            |                       |         |                     |         |                                              |

| Input leakage current | I <sub>IL</sub>    | Pnn_m                       | $3.0V \le V_{DD} \le 5.5V$<br>$V_{SS}5 < V_{I} < V_{DD}$<br>$T_A = 25 °C$                                                                                                                  | <b>—</b> 1            | _       | + 1                 | μA      |                                              |

|                       |                    | *1                          | $3.0V \le V_{DD} \le 5.5V$<br>$V_{SS}5 < V_{I} < V_{DD}$<br>$T_A = 105 ^{\circ}C$                                                                                                          | -3                    |         | + 3                 | μ/ \    |                                              |

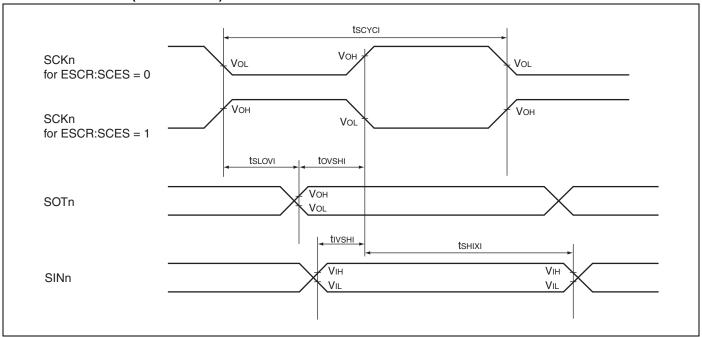

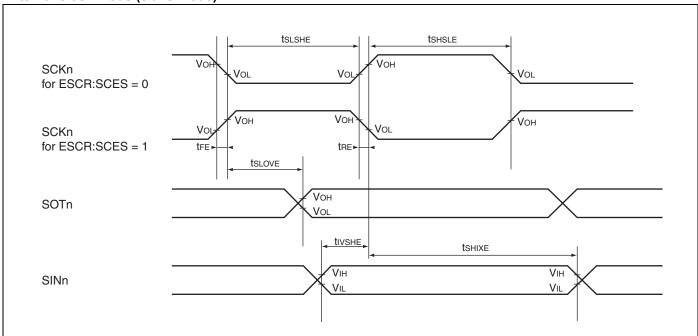

### 15.7.3 LIN-USART Timings at $V_{DD}$ 5 = 3.0 to 5.5 V

- Conditions during AC measurements

- All AC tests were measured under the following conditions:

- IO<sub>drive</sub> = 5 mA

- $-V_{DD}5 = 3.0 \text{ V to } 5.5 \text{ V}, I_{load} = 3 \text{ mA}$

- $-V_{SS}5 = 0 V$

- $-T_a = -40^{\circ}C \text{ to } +105^{\circ}C$

- - C<sub>I</sub> = 50 pF (load capacity value of pins when testing)

- -  $VOL = 0.2 \times V_{DD}5$

- - VOH =  $0.8 \times V_{DD}5$

- - EPILR = 0, PILR = 1 (Automotive Level = worst case)

(V<sub>DD</sub>5 = 3.0 V to 5.5 V, V<sub>SS</sub>5 = AV<sub>SS</sub>5 = 0 V,  $T_A = -40$  °C to + 105 °C)

| B                                                                            | 0 1                | <b>D</b> .   | Condition                                          | $V_{DD}5 = 3.0$                         | V to 4.5 V               | $V_{DD}5 = 4.5 \text{ V} \text{ to } 5.5 \text{ V}$ |                          | 11.24 |

|------------------------------------------------------------------------------|--------------------|--------------|----------------------------------------------------|-----------------------------------------|--------------------------|-----------------------------------------------------|--------------------------|-------|

| Parameter                                                                    | Symbol             | Pin name     |                                                    | Min                                     | Max                      | Min                                                 | Max                      | Unit  |

| Serial clock cycle time                                                      | t <sub>scyci</sub> | SCKn         | Internal<br>clock<br>operation<br>(master<br>mode) | 4 t <sub>CLKP</sub>                     | _                        | 4 t <sub>CLKP</sub>                                 | _                        | ns    |

| SCK ↓ → SOT delay time                                                       | t <sub>SLOVI</sub> | SCKn<br>SOTn |                                                    | - 30                                    | 30                       | <b>- 20</b>                                         | 20                       | ns    |

| $\begin{array}{c} SOT \to SCK \downarrow \\ delay\ time \end{array}$         | t <sub>ovshi</sub> | SCKn<br>SOTn |                                                    | $m \times t_{\text{CLKP}} - 30^{\star}$ | _                        | $m \times t_{CLKP} - 20*$                           | _                        | ns    |

| Valid SIN $\rightarrow$ SCK ↑ setup time                                     | t <sub>IVSHI</sub> | SCKn<br>SINn |                                                    | t <sub>CLKP</sub> + 55                  | _                        | t <sub>CLKP</sub> + 45                              | _                        | ns    |

| $\begin{array}{c} SCK \uparrow \to valid \; SIN \\ hold \; time \end{array}$ | t <sub>SHIXI</sub> | SCKn<br>SINn |                                                    | 0                                       | _                        | 0                                                   | _                        | ns    |

| Serial clock "H" pulse width                                                 | t <sub>SHSLE</sub> | SCKn         |                                                    | t <sub>CLKP</sub> + 10                  | _                        | t <sub>CLKP</sub> + 10                              | _                        | ns    |

| Serial clock "L" pulse width                                                 | t <sub>SLSHE</sub> | SCKn         |                                                    | t <sub>CLKP</sub> + 10                  | _                        | t <sub>CLKP</sub> + 10                              | _                        | ns    |

| SCK ↓ → SOT delay time                                                       | t <sub>SLOVE</sub> | SCKn<br>SOTn | External<br>clock<br>operation<br>(slave mode)     | _                                       | 2 t <sub>CLKP</sub> + 55 | _                                                   | 2 t <sub>CLKP</sub> + 45 | ns    |

| Valid SIN → SCK ↑ setup time                                                 | t <sub>IVSHE</sub> | SCKn<br>SINn |                                                    | 10                                      | _                        | 10                                                  | _                        | ns    |

| $\begin{array}{c} SCK \uparrow \to valid \; SIN \\ hold \; time \end{array}$ | t <sub>SHIXE</sub> | SCKn<br>SINn |                                                    | t <sub>CLKP</sub> + 10                  | _                        | t <sub>CLKP</sub> + 10                              | _                        | ns    |

| SCK rising time                                                              | t <sub>FE</sub>    | SCKn         |                                                    |                                         | 20                       |                                                     | 20                       | ns    |

| SCK falling time                                                             | t <sub>RE</sub>    | SCKn         |                                                    | _                                       | 20                       |                                                     | 20                       | ns    |

<sup>\*:</sup> Parameter m depends on t<sub>SCYCI</sub> and can be calculated as:

- if  $t_{SCYCI} = 2*k*t_{CLKP}$ , then m = k, where k is an integer > 2

- if  $t_{SCYCI} = (2*k + 1)*t_{CLKP}$ , then m = k + 1, where k is an integer > 1

Notes: • The above values are AC characteristics for CLK synchronous mode.

• t<sub>CLKP</sub> is the cycle time of the peripheral clock.

Document Number: 002-04609 Rev. \*A

### Internal clock mode (master mode)

### External clock mode (slave mode)

### Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

**USB Controllers**

Wireless/RF

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers Interface Lighting & Power Control Memory **PSoC** Touch Sensing

cypress.com/clocks cypress.com/interface cypress.com/powerpsoc cypress.com/memory cypress.com/psoc cypress.com/touch cypress.com/usb cypress.com/wireless

## PSoC® Solutions

cypress.com/psoc PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

**Technical Support** cypress.com/support