Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

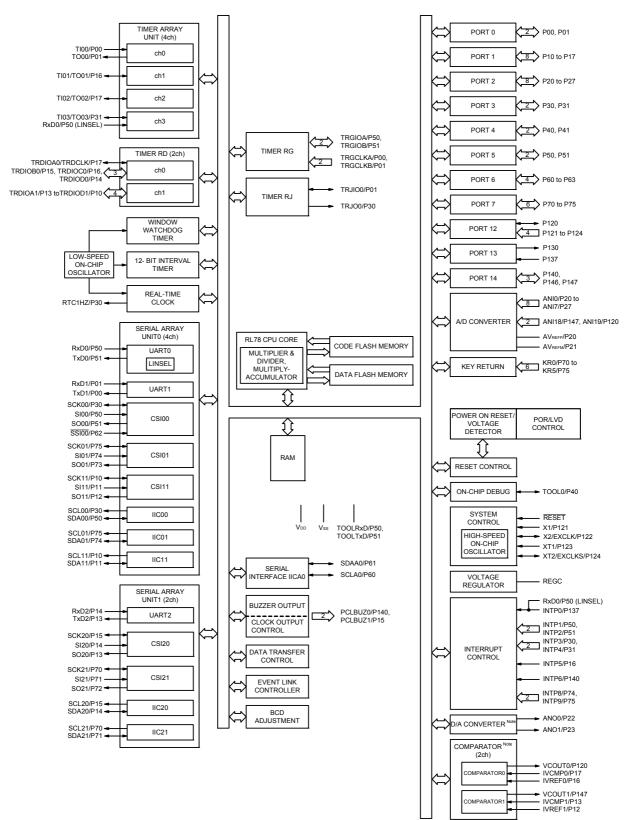

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFl

| 2 010                      |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 256КВ (256К х 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 8K x 8                                                                          |

| RAM Size                   | 24K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 10x8/10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

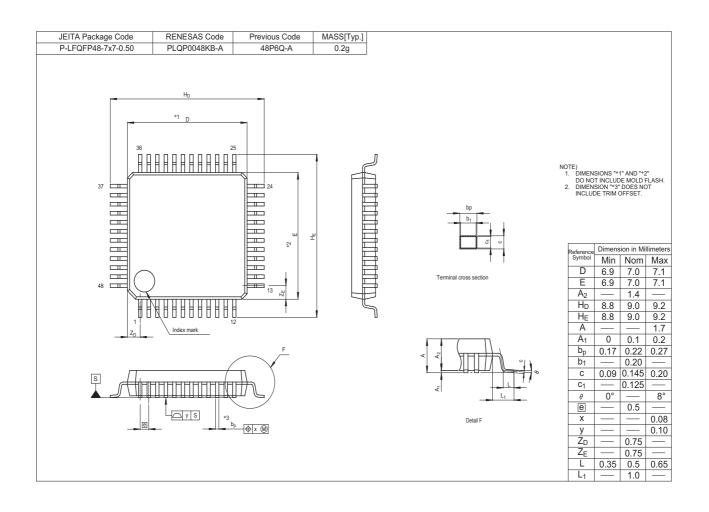

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | 48-LFQFP (7x7)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f104gjafb-x0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.3.2 32-pin products

• 32-pin plastic HWQFN (5 × 5 mm, 0.5 mm pitch)

Note Mounted on the 96 KB or more code flash memory products.

#### Caution Connect the REGC pin to Vss pin via a capacitor (0.47 to 1 $\mu\text{F}).$

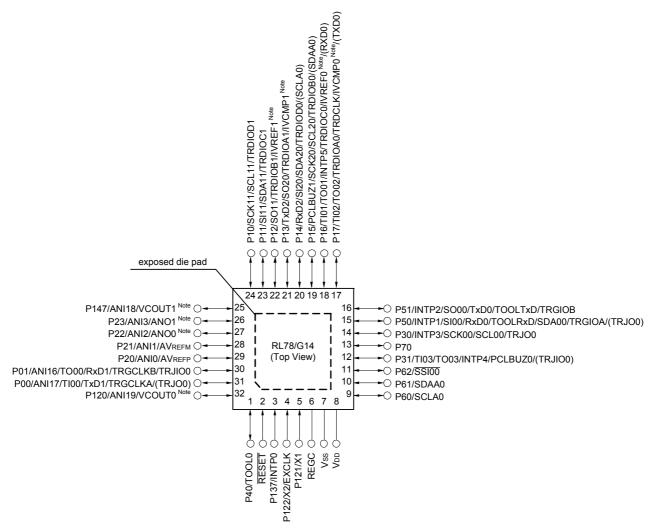

- Remark 1. For pin identification, see 1.4 Pin Identification.

- **Remark 2.** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register 0, 1 (PIOR0, 1).

- Remark 3. It is recommended to connect an exposed die pad to Vss.

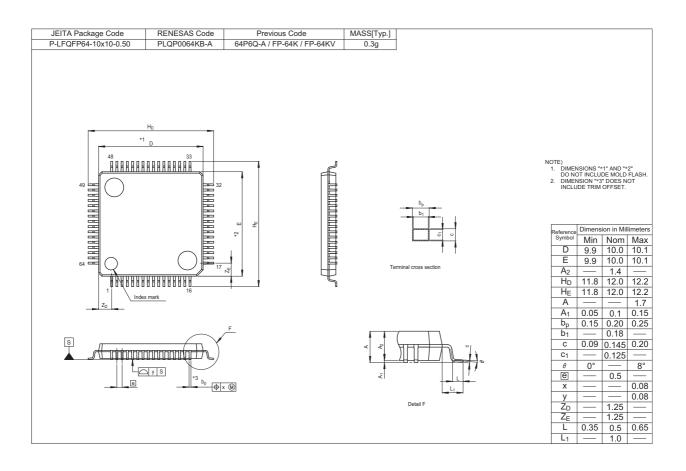

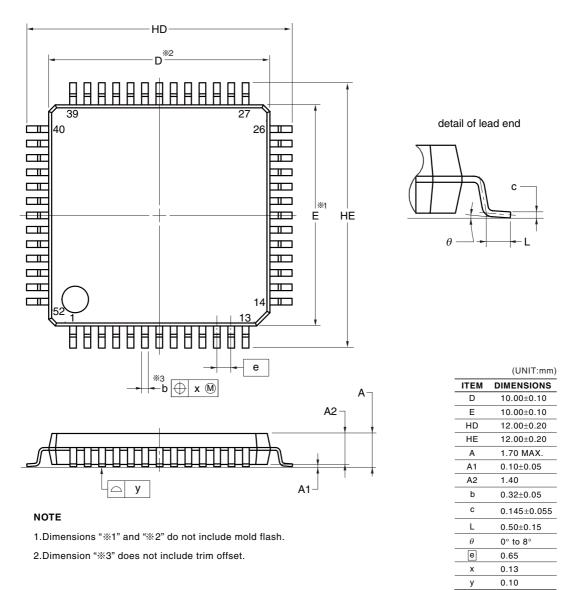

# 1.5.6 48-pin products

**Note** Mounted on the 96 KB or more code flash memory products.

| 1 | ი | in | i٦ |

|---|---|----|----|

| ( | 2 | 12 | .) |

|                        |                      | 80-pin                                                                                                                                                                                                                                                                     | (2/2)<br>100-pin               |  |  |  |

|------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|

| 1                      | tem                  | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                      | •                              |  |  |  |

| 1                      | lem                  | R5F104Mx<br>(x = K, L)                                                                                                                                                                                                                                                     | R5F104Px<br>(x = K, L)         |  |  |  |

| Clock output/buzz      | zer output           | 2                                                                                                                                                                                                                                                                          | 2                              |  |  |  |

|                        |                      | <ul> <li>2.44 kHz, 4.88 kHz, 9.76 kHz, 1.25 MHz, 2.</li> <li>(Main system clock: fMAIN = 20 MHz operati</li> <li>256 Hz, 512 Hz, 1.024 kHz, 2.048 kHz, 4.03</li> <li>(Subsystem clock: fsub = 32.768 kHz operation)</li> </ul>                                             | 1                              |  |  |  |

| 8/10-bit resolution    | n A/D converter      | 17 channels                                                                                                                                                                                                                                                                | 20 channels                    |  |  |  |

| D/A converter          |                      | 2 channels                                                                                                                                                                                                                                                                 | 2 channels                     |  |  |  |

| Comparator             |                      | 2 channels                                                                                                                                                                                                                                                                 | 2 channels                     |  |  |  |

| Serial interface       |                      | <ul> <li>[80-pin, 100-pin products]</li> <li>CSI: 2 channels/UART (UART supporting L</li> <li>CSI: 2 channels/UART: 1 channel/simplified</li> <li>CSI: 2 channels/UART: 1 channel/simplified</li> <li>CSI: 2 channels/UART: 1 channel/simplified</li> </ul>                | I I <sup>2</sup> C: 2 channels |  |  |  |

|                        | I <sup>2</sup> C bus | 2 channels                                                                                                                                                                                                                                                                 | 2 channels                     |  |  |  |

| Data transfer con      | troller (DTC)        | 39 sources                                                                                                                                                                                                                                                                 | 39 sources                     |  |  |  |

| Event link control     | ler (ELC)            | Event input: 26<br>Event trigger output: 9                                                                                                                                                                                                                                 |                                |  |  |  |

| Vectored inter-        | Internal             | 32                                                                                                                                                                                                                                                                         | 32                             |  |  |  |

| rupt sources           | External             | 13                                                                                                                                                                                                                                                                         | 13                             |  |  |  |

| Key interrupt          |                      | 8                                                                                                                                                                                                                                                                          | 8                              |  |  |  |

| Reset                  |                      | Reset by RESET pin     Internal reset by watchdog timer     Internal reset by power-on-reset     Internal reset by voltage detector     Internal reset by illegal instruction execution     Internal reset by RAM parity error     Internal reset by illegal-memory access | ן Note                         |  |  |  |

| Power-on-reset circuit |                      | • Power-on-reset: $1.51 \pm 0.04 \text{ V}$ (TA = -40 to +85°C)<br>$1.51 \pm 0.06 \text{ V}$ (TA = -40 to +105°C)<br>• Power-down-reset: $1.50 \pm 0.04 \text{ V}$ (TA = -40 to +85°C)<br>$1.50 \pm 0.06 \text{ V}$ (TA = -40 to +105°C)                                   |                                |  |  |  |

| Voltage detector       |                      | 1.63 V to 4.06 V (14 stages)                                                                                                                                                                                                                                               |                                |  |  |  |

| On-chip debug fu       | nction               | Provided                                                                                                                                                                                                                                                                   |                                |  |  |  |

| Power supply vol       | tage                 | V <sub>DD</sub> = 1.6 to 5.5 V (T <sub>A</sub> = -40 to +85°C)<br>V <sub>DD</sub> = 2.4 to 5.5 V (T <sub>A</sub> = -40 to +105°C)                                                                                                                                          |                                |  |  |  |

| Operating ambier       | nt temperature       | $ T_A = -40 \text{ to } +85^{\circ}\text{C} \text{ (A: Consumer applications, D: Industrial applications),} $<br>$ T_A = -40 \text{ to } +105^{\circ}\text{C} \text{ (G: Industrial applications)} $                                                                       |                                |  |  |  |

Note

The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution is not issued by emulation with the in-circuit emulator or onchip debug emulator.

- Note 1. Total current flowing into VDD, EVDDD, and EVDD1, including the input leakage current flowing when the level of the input pin is fixed to VDD, EVDDD, and EVDD1, or Vss, EVss0, and EVss1. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, D/A converter, comparator, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

Note 2. When high-speed on-chip oscillator and subsystem clock are stopped.

- Note 3. When high-speed system clock and subsystem clock are stopped.

- **Note 4.** When high-speed on-chip oscillator and high-speed system clock are stopped. When AMPHS1 = 1 (Ultra-low power consumption oscillation). However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- Note 5. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

HS (high-speed main) mode:  $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}_{\text{@1}} \text{ MHz to } 32 \text{ MHz}$

2.4 V  $\leq$  VDD  $\leq$  5.5 V@1 MHz to 16 MHz

LS (low-speed main) mode:  $$1.8~V \le V \mbox{DD} \le 5.5~V \ensuremath{\textcircled{@}1}$  MHz to 8 MHz

LV (low-voltage main) mode:  $1.6 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}_{@}1 \text{ MHz}$  to 4 MHz

- Remark 1. fMX: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- Remark 2. fHoco: High-speed on-chip oscillator clock frequency (64 MHz max.)

- **Remark 3.** fin: High-speed on-chip oscillator clock frequency (32 MHz max.)

- **Remark 4.** fsuB: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 5. Except subsystem clock operation, temperature condition of the TYP. value is TA = 25°C

- Note 1. Total current flowing into VDD, EVDD0, and EVDD1, including the input leakage current flowing when the level of the input pin is fixed to VDD, EVDD0, and EVDD1, or Vss, EVss0, and EVss1. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, D/A converter, comparator, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

Note 2. During HALT instruction execution by flash memory.

- Note 3. When high-speed on-chip oscillator and subsystem clock are stopped.

- **Note 4.** When high-speed system clock and subsystem clock are stopped.

- **Note 5.** When high-speed on-chip oscillator and high-speed system clock are stopped. When RTCLPC = 1 and setting ultra-low current consumption (AMPHS1 = 1). The current flowing into the RTC is included. However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- Note 6. Not including the current flowing into the RTC, 12-bit interval timer, and watchdog timer.

- Note 7. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

- HS (high-speed main) mode:  $2.7 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}_{@}1 \text{ MHz}$  to 32 MHz

- 2.4 V  $\leq$  VDD  $\leq$  5.5 V@1 MHz to 16 MHz

- LS (low-speed main) mode:  $1.8 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ @1 MHz to 8 MHz

- LV (low-voltage main) mode:  $1.6 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ @1 MHz to 4 MHz

- Note 8. Regarding the value for current to operate the subsystem clock in STOP mode, refer to that in HALT mode.

- Remark 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- Remark 2. fHOCO: High-speed on-chip oscillator clock frequency (64 MHz max.)

- **Remark 3.** file: High-speed on-chip oscillator clock frequency (32 MHz max.)

- **Remark 4.** fsuB: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 5. Except subsystem clock operation and STOP mode, temperature condition of the TYP. value is TA = 25°C

# 2.4 AC Characteristics

| Items                                                                    | Symbol          |                                         | Conditions                    |                                                                | MIN.                | TYP. | MAX. | Unit |

|--------------------------------------------------------------------------|-----------------|-----------------------------------------|-------------------------------|----------------------------------------------------------------|---------------------|------|------|------|

| Instruction cycle (min-                                                  | Тсү             | Main system                             | HS (high-speed main)          | $2.7~V \leq V \text{DD} \leq 5.5~V$                            | 0.03125             |      | 1    | μs   |

| imum instruction exe-                                                    |                 | clock (fmain)                           | mode                          | $2.4 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$     | 0.0625              |      | 1    | μs   |

| cution time)                                                             |                 | operation                               | LS (low-speed main)<br>mode   | $1.8 \text{ V} \leq \text{V}\text{DD} \leq 5.5 \text{ V}$      | 0.125               |      | 1    | μs   |

|                                                                          |                 |                                         | LV (low-voltage main)<br>mode | $1.6 \text{ V} \leq \text{V}\text{DD} \leq 5.5 \text{ V}$      | 0.25                |      | 1    | μs   |

|                                                                          |                 | Subsystem clo                           | ock (fsuв) operation          | $1.8~V \le V_{DD} \le 5.5~V$                                   | 28.5                | 30.5 | 31.3 | μs   |

|                                                                          |                 | In the self-                            | HS (high-speed main)          | $2.7~V \leq V \text{DD} \leq 5.5~V$                            | 0.03125             |      | 1    | μs   |

|                                                                          |                 | program-                                | mode                          | $2.4 \text{ V} \leq \text{V}_{DD} < 2.7 \text{ V}$             | 0.0625              |      | 1    | μs   |

|                                                                          |                 | ming mode                               | LS (low-speed main) mode      | $1.8 \text{ V} \leq \text{V}\text{DD} \leq 5.5 \text{ V}$      | 0.125               |      | 1    | μs   |

|                                                                          |                 |                                         | LV (low-voltage main)<br>mode | $1.8 \text{ V} \leq \text{V}\text{DD} \leq 5.5 \text{ V}$      | 0.25                |      | 1    | μs   |

| External system clock                                                    | fEX             | $2.7 \text{ V} \leq \text{V}_{DD} \leq$ | 5.5 V                         |                                                                | 1.0                 |      | 20.0 | MHz  |

| frequency                                                                |                 | $2.4~V \leq V_{DD} \leq$                | 2.7 V                         |                                                                | 1.0                 |      | 16.0 | MHz  |

|                                                                          |                 | $1.8 \text{ V} \leq \text{V}_{DD} <$    | 2.4 V                         |                                                                | 1.0                 |      | 8.0  | MHz  |

|                                                                          |                 | $1.6 V \le V_{DD} <$                    | 1.8 V                         |                                                                | 1.0                 |      | 4.0  | MHz  |

|                                                                          | fexs            |                                         |                               |                                                                | 32                  |      | 35   | kHz  |

| External system clock                                                    | texн,           | $2.7~V \leq V_{DD} \leq$                | 5.5 V                         |                                                                | 24                  |      |      | ns   |

| input high-level width,                                                  | tEXL            | $2.4~V \leq V_{DD} \leq$                | 2.7 V                         |                                                                | 30                  |      |      | ns   |

| low-level width                                                          |                 | $1.8 \text{ V} \leq \text{V}_{DD} <$    | 2.4 V                         |                                                                | 60                  |      |      | ns   |

|                                                                          |                 | $1.6 \text{ V} \leq \text{V}_{DD} <$    | 1.8 V                         |                                                                | 120                 |      |      | ns   |

|                                                                          | texhs,<br>texls |                                         |                               |                                                                | 13.7                |      |      | μs   |

| TI00 to TI03, TI10 to<br>TI13 input high-level<br>width, low-level width | ttiH, tti∟      |                                         |                               |                                                                | 1/fмск + 10<br>Note |      |      | ns   |

| Timer RJ input cycle                                                     | fc              | TRJIO                                   |                               | $2.7 \text{ V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \text{ V}$ | 100                 |      |      | ns   |

|                                                                          |                 |                                         |                               | $1.8 \text{ V} \le \text{EV}_{\text{DD0}} < 2.7 \text{ V}$     | 300                 |      |      | ns   |

|                                                                          |                 |                                         |                               | $1.6 \text{ V} \le \text{EV}_{\text{DD0}} < 1.8 \text{ V}$     | 500                 |      |      | ns   |

| Timer RJ input high-                                                     | tтjiн,          | TRJIO                                   |                               | $2.7 \text{ V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \text{ V}$ | 40                  |      |      | ns   |

| level width, low-level                                                   | t⊤ji∟           |                                         |                               | $1.8 \text{ V} \le \text{EV}_{\text{DD0}} < 2.7 \text{ V}$     | 120                 |      |      | ns   |

| width                                                                    |                 |                                         |                               | 1.6 V ≤ EVDD0 < 1.8 V                                          | 200                 |      |      | ns   |

### (TA = -40 to +85°C, 1.6 V $\leq$ EVDD0 = EVDD1 $\leq$ VDD $\leq$ 5.5 V, VSS = EVSS0 = EVSS1 = 0 V)

NoteThe following conditions are required for low voltage interface when EVDD0 < VDD $1.8 V \le EVDD0 < 2.7 V$ : MIN. 125 ns $1.6 V \le EVDD0 < 1.8 V$ : MIN. 250 ns

Remark fMCK: Timer array unit operation clock frequency (Operation clock to be set by the CKSmn bit of timer mode register mn (TMRmn). m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3))

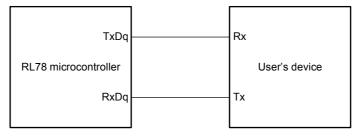

### UART mode connection diagram (during communication at same potential)

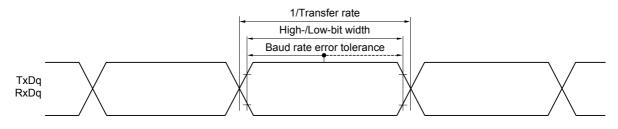

#### UART mode bit width (during communication at same potential) (reference)

Remark 1. q: UART number (q = 0 to 3), g: PIM and POM number (g = 0, 1, 5, 14)

Remark 2. fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00 to 03, 10 to 13))

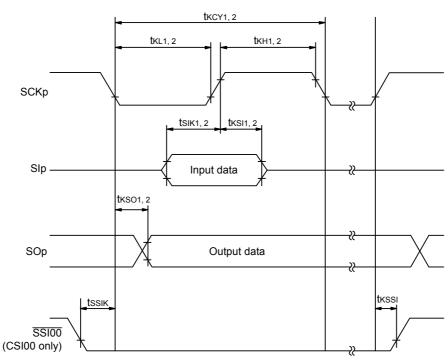

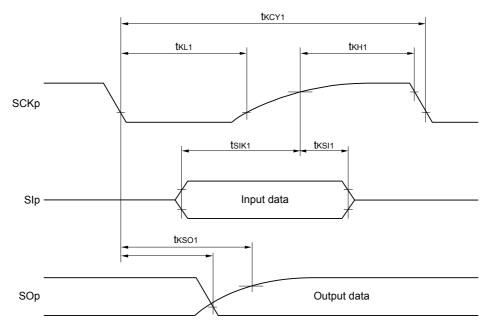

## CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

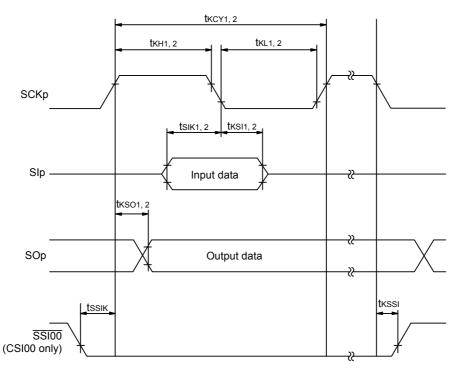

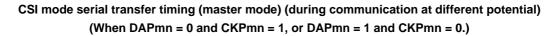

CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

Remark 1. p: CSI number (p = 00, 01, 10, 11, 20, 21, 30, 31) Remark 2. m: Unit number, n: Channel number (mn = 00 to 03, 10 to 13)

CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

- Remark 1. p: CSI number (p = 00, 01, 10, 20, 30, 31), m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), g: PIM and POM number (g = 0, 1, 3 to 5, 14)

- Remark 2. CSI01 of 48-, 52-, 64-pin products, and CSI11 and CSI21 cannot communicate at different potential. Use other CSI for communication at different potential.

(3) When reference voltage (+) = VDD (ADREFP1 = 0, ADREFP0 = 0), reference voltage (-) = Vss (ADREFM = 0), target pin: ANI0 to ANI14, ANI16 to ANI20, internal reference voltage, and temperature sensor output voltage

(TA = -40 to +85°C, 1.6 V  $\leq$  EVDD0 = EVDD1  $\leq$  VDD  $\leq$  5.5 V, Vss = EVss0 = EVss1 = 0 V, Reference voltage (+) = VDD, Reference voltage (-) = Vss)

| Parameter                       | Symbol | Conditions                                                                               |                                                                   | MIN.   | TYP.                  | MAX.              | Unit |

|---------------------------------|--------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------|-----------------------|-------------------|------|

| Resolution                      | RES    |                                                                                          |                                                                   | 8      |                       | 10                | bit  |

| Overall error Note 1            | AINL   | 10-bit resolution                                                                        | $1.8 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      |        | 1.2                   | ±7.0              | LSB  |

|                                 |        |                                                                                          | 1.6 V $\leq$ VDD $\leq$ 5.5 V Note 3                              |        | 1.2                   | ±10.5             | LSB  |

| Conversion time                 | tconv  | 10-bit resolution                                                                        | $3.6 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      | 2.125  |                       | 39                | μs   |

|                                 |        | Target pin: ANI0 to ANI14, ANI16 to ANI20                                                | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      | 3.1875 |                       | 39                | μs   |

|                                 |        |                                                                                          | $1.8 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      | 17     |                       | 39                | μs   |

|                                 |        |                                                                                          | $1.6 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      | 57     |                       | 95                | μs   |

|                                 |        | 10-bit resolution                                                                        | $3.6 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      | 2.375  |                       | 39                | μs   |

|                                 |        | Target pin: internal reference voltage, and temperature sensor output voltage            | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      | 3.5625 |                       | 39                | μs   |

|                                 |        | (HS (high-speed main) mode)                                                              | $2.4~V \leq V_{DD} \leq 5.5~V$                                    | 17     |                       | 39                | μs   |

| Zero-scale error Notes 1, 2     | Ezs    | 10-bit resolution                                                                        | $1.8~V \leq V_{DD} \leq 5.5~V$                                    |        |                       | ±0.60             | %FSR |

|                                 |        |                                                                                          | 1.6 V $\leq$ VDD $\leq$ 5.5 V Note 3                              |        |                       | ±0.85             | %FSR |

| Full-scale error Notes 1, 2     | Efs    | 10-bit resolution                                                                        | $1.8~V \leq V_{DD} \leq 5.5~V$                                    |        |                       | ±0.60             | %FSR |

|                                 |        |                                                                                          | $1.6~V \leq V_{DD} \leq 5.5~V$ Note 3                             |        |                       | ±0.85             | %FSR |

| Integral linearity error Note 1 | ILE    | 10-bit resolution                                                                        | $1.8 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      |        |                       | ±4.0              | LSB  |

|                                 |        |                                                                                          | $1.6 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ Note 3 |        |                       | ±6.5              | LSB  |

| Differential linearity error    | DLE    | 10-bit resolution                                                                        | $1.8~\text{V} \leq \text{V}_\text{DD} \leq 5.5~\text{V}$          |        |                       | ±2.0              | LSB  |

| Note 1                          |        |                                                                                          | $1.6 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ Note 3 |        |                       | ±2.5              | LSB  |

| Analog input voltage            | VAIN   | ANI0 to ANI14                                                                            |                                                                   | 0      |                       | Vdd               | V    |

|                                 |        | ANI16 to ANI20                                                                           |                                                                   | 0      |                       | EV <sub>DD0</sub> | V    |

|                                 |        | Internal reference voltage (2.4 V $\leq$ VDD $\leq$ 5.5 V, HS (high-speed main) mode)    |                                                                   | ١      | / <sub>BGR</sub> Note | 4                 | V    |

|                                 |        | Temperature sensor output voltage (2.4 V $\leq$ VDD $\leq$ 5.5 V, HS (high-speed main) r | node)                                                             | ۲V     | MPS25 Not             | te 4              | V    |

**Note 1.** Excludes quantization error (±1/2 LSB).

**Note 2.** This value is indicated as a ratio (% FSR) to the full-scale value.

Note 3. When the conversion time is set to 57  $\mu$ s (min.) and 95  $\mu$ s (max.).

Note 4. Refer to 2.6.2 Temperature sensor characteristics/internal reference voltage characteristic.

|                      |                                                                                                                | $\mathbf{E}\mathbf{V}\mathbf{D}\mathbf{D}0 = \mathbf{E}\mathbf{V}\mathbf{D}\mathbf{D}1 \leq \mathbf{V}\mathbf{D}\mathbf{D} \leq 5.5 \mathbf{V},$ |                                                                                                                                              | ,           |      |      | (4/: |

|----------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|------|------|

| Items                | Symbol                                                                                                         | Condition                                                                                                                                        | IS                                                                                                                                           | MIN.        | TYP. | MAX. | Unit |

| Output voltage, high | Voh1                                                                                                           | P00 to P06, P10 to P17, P30,<br>P31, P40 to P47, P50 to P57,                                                                                     | $\begin{array}{l} 4.0 \text{ V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \text{ V}, \\ \\ \text{IOH1} = -3.0 \text{ mA} \end{array}$             | EVDD0 - 0.7 |      |      | V    |

|                      |                                                                                                                | P80 to P87, P100 to P102, P110,                                                                                                                  | 2.7 V ≤ EVDD0 ≤ 5.5 V,<br>Іон1 = -2.0 mA                                                                                                     | EVDD0 - 0.6 |      |      | V    |

|                      |                                                                                                                | P111, P120, P130, P140 to P147                                                                                                                   | 2.4 V ≤ EVDD0 ≤ 5.5 V,<br>Іон1 = -1.5 mA                                                                                                     | EVDD0 - 0.5 |      |      | V    |

|                      | Voh2                                                                                                           | P20 to P27, P150 to P156                                                                                                                         | 2.4 V ≤ Vdd ≤ 5.5 V,<br>Ioh2 = -100 μA                                                                                                       | VDD - 0.5   |      |      | V    |

| Output voltage, low  | P31, P40 to P47, P50 to P57,<br>P64 to P67, P70 to P77,<br>P80 to P87, P100 to P102, P110,<br>P111, P120, P130 | P31, P40 to P47, P50 to P57,                                                                                                                     | $\begin{array}{l} 4.0 \ \text{V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \ \text{V}, \\ \\ \text{I}_{\text{OL1}} = 8.5 \ \text{mA} \end{array}$ |             |      | 0.7  | V    |

|                      |                                                                                                                | $\begin{array}{l} 2.7 \ \text{V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \ \text{V}, \\ \\ \text{I}_{\text{OL1}} = 3.0 \ \text{mA} \end{array}$     |                                                                                                                                              |             | 0.6  | V    |      |

|                      |                                                                                                                | P140 to P147                                                                                                                                     | $2.7 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V},$<br>IOL1 = 1.5 mA                                                               |             |      | 0.4  | V    |

|                      |                                                                                                                |                                                                                                                                                  | $\begin{array}{l} 2.4 \ \text{V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \ \text{V}, \\ \\ \text{I}_{\text{OL1}} = 0.6 \ \text{mA} \end{array}$ |             |      | 0.4  | V    |

|                      | VOL2                                                                                                           | P20 to P27, P150 to P156                                                                                                                         | $\begin{array}{l} 2.4 \ V \leq V \text{dd} \leq 5.5 \ V, \\ I \text{OL2} = 400 \ \mu A \end{array}$                                          |             |      | 0.4  | V    |

|                      | Vol3                                                                                                           | P60 to P63                                                                                                                                       | $4.0 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V},$<br>IOL3 = 15.0 mA                                                              |             |      | 2.0  | V    |

|                      | $4.0 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V},$<br>IOL3 = 5.0 mA                                 | $\begin{array}{l} 4.0 \text{ V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \text{ V}, \\ \text{IOL3} = 5.0 \text{ mA} \end{array}$                     |                                                                                                                                              |             | 0.4  | V    |      |

|                      |                                                                                                                |                                                                                                                                                  | $\begin{array}{l} 2.7 \ \text{V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \ \text{V}, \\ \\ \text{IOL3} = 3.0 \ \text{mA} \end{array}$           |             |      | 0.4  | V    |

|                      |                                                                                                                |                                                                                                                                                  | $2.4 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V},$<br>IOL3 = 2.0 mA                                                               |             |      | 0.4  | V    |

(TA = -40 to +105°C, 2.4 V  $\leq$  EVDD0 = EVDD1  $\leq$  VDD  $\leq$  5.5 V, VSS = EVSS0 = EVSS1 = 0 V)

(4/5)

Caution P00, P02 to P04, P10, P11, P13 to P15, P17, P30, P43 to P45, P50 to P55, P71, P74, P80 to P82, P142 to P144 do not output high level in N-ch open-drain mode.

Remark Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

# 3.3.2 Supply current characteristics

#### (1) Flash ROM: 16 to 64 KB of 30- to 64-pin products

#### (TA = -40 to +105°C, 2.4 V $\leq$ EVDD0 $\leq$ VDD $\leq$ 5.5 V, Vss = EVsso = 0 V)

| Parameter | Symbol |          |                      | Conditions                                   |                      |                         | MIN. | TYP. | MAX. | Unit |

|-----------|--------|----------|----------------------|----------------------------------------------|----------------------|-------------------------|------|------|------|------|

| Supply    | IDD1   | Operat-  | HS (high-speed main) | fносо = 64 MHz,                              | Basic                | V <sub>DD</sub> = 5.0 V |      | 2.4  |      | mA   |

| current   |        | ing mode | mode Note 5          | fiH = 32 MHz Note 3                          | operation            | VDD = 3.0 V             |      | 2.4  |      |      |

| Note 1    |        |          |                      | fносо = 32 MHz,                              | Basic                | VDD = 5.0 V             |      | 2.1  |      |      |

|           |        |          |                      | fiH = 32 MHz Note 3                          | operation            | VDD = 3.0 V             |      | 2.1  |      |      |

|           |        |          | HS (high-speed main) | fносо = 64 MHz,                              | Normal               | VDD = 5.0 V             |      | 5.1  | 9.3  | mA   |

|           |        |          | mode Note 5          | fiH = 32 MHz Note 3                          | operation            | VDD = 3.0 V             |      | 5.1  | 9.3  |      |

|           |        |          |                      | fносо = 32 MHz,                              | Normal               | VDD = 5.0 V             |      | 4.8  | 8.7  |      |

|           |        |          |                      | fiH = 32 MHz Note 3                          |                      | VDD = 3.0 V             |      | 4.8  | 8.7  |      |

|           |        |          |                      | fносо = 48 MHz,                              |                      | VDD = 5.0 V             |      | 4.0  | 7.3  |      |

|           |        |          |                      | fiH = 24 MHz Note 3                          | operation            | VDD = 3.0 V             |      | 4.0  | 7.3  |      |

|           |        |          |                      | fносо = 24 MHz,                              | Normal               | VDD = 5.0 V             |      | 3.8  | 6.7  |      |

|           |        |          |                      | fiH = 24 MHz Note 3                          | operation            | VDD = 3.0 V             |      | 3.8  | 6.7  |      |

|           |        |          |                      | fносо = 16 MHz,                              | Normal               | VDD = 5.0 V             |      | 2.8  | 4.9  |      |

|           |        |          |                      | fiH = 16 MHz Note 3                          | operation            | VDD = 3.0 V             |      | 2.8  | 4.9  |      |

|           |        |          | HS (high-speed main) | f <sub>MX</sub> = 20 MHz <sup>Note 2</sup> , | Normal               | Square wave input       |      | 3.3  | 5.7  | mA   |

|           |        |          | mode Note 5          | VDD = 5.0 V                                  | operation            | Resonator connection    |      | 3.4  | 5.8  |      |

|           |        |          |                      | f <sub>MX</sub> = 20 MHz <sup>Note 2</sup> , | Normal               | Square wave input       |      | 3.3  | 5.7  | 5.7  |

|           |        |          |                      | VDD = 3.0 V                                  | operation            | Resonator connection    |      | 3.4  | 5.8  |      |

|           |        |          |                      | f <sub>MX</sub> = 10 MHz <sup>Note 2</sup> , | Normal               | Square wave input       |      | 2.0  | 3.4  |      |

|           |        |          |                      | VDD = 5.0 V                                  | operation            | Resonator connection    |      | 2.1  | 3.5  |      |

|           |        |          |                      | f <sub>MX</sub> = 10 MHz <sup>Note 2</sup> , | Normal               | Square wave input       |      | 2.0  | 3.4  |      |

|           |        |          |                      | VDD = 3.0 V                                  | operation            | Resonator connection    |      | 2.1  | 3.5  |      |

|           |        |          | Subsystem clock      | fsub = 32.768 kHz Note 4                     | Normal               | Square wave input       |      | 4.7  | 6.1  | μA   |

|           |        |          | operation            | TA = -40°C                                   | operation            | Resonator connection    |      | 4.7  | 6.1  |      |

|           |        |          |                      | fsue = 32.768 kHz Note 4                     | Normal               | Square wave input       |      | 4.7  | 6.1  |      |

|           |        |          |                      | TA = +25°C                                   | operation            | Resonator connection    |      | 4.7  | 6.1  |      |

|           |        |          |                      | fsub = 32.768 kHz Note 4                     | Normal               | Square wave input       |      | 4.8  | 6.7  |      |

|           |        |          |                      | TA = +50°C                                   | operation            | Resonator connection    |      | 4.8  | 6.7  |      |

|           |        |          |                      | fsub = 32.768 kHz Note 4                     | Normal               | Square wave input       |      | 4.8  | 7.5  |      |

|           |        |          |                      | TA = +70°C                                   | operation            | Resonator connection    |      | 4.8  | 7.5  |      |

|           |        |          |                      | fsue = 32.768 kHz Note 4                     | Normal               | Square wave input       |      | 5.4  | 8.9  | 1    |

|           |        |          |                      | T <sub>A</sub> = +85°C operation             | Resonator connection |                         | 5.4  | 8.9  |      |      |

|           |        |          |                      | fsub = 32.768 kHz Note 4                     | Normal               | Square wave input       |      | 7.2  | 21.0 |      |

|           |        |          |                      | TA = +105°C                                  | operation            | Resonator connection    |      | 7.3  | 21.1 |      |

(Notes and Remarks are listed on the next page.)

#### RL78/G14

- Note 1. Total current flowing into VDD, EVDD0, and EVDD1, including the input leakage current flowing when the level of the input pin is fixed to VDD, EVDD0, and EVDD1, or Vss, EVss0, and EVss1. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, D/A converter, comparator, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- **Note 2.** When high-speed on-chip oscillator and subsystem clock are stopped.

- **Note 3.** When high-speed system clock and subsystem clock are stopped.

- **Note 4.** When high-speed on-chip oscillator and high-speed system clock are stopped. When AMPHS1 = 1 (Ultra-low power consumption oscillation). However, not including the current flowing into the 12-bit interval timer and watchdog timer.

Note 5.Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.<br/>HS (high-speed main) mode:  $2.7 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V} @1 \text{ MHz}$  to 32 MHz

$2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}_{@}1 \text{ MHz}$  to 16 MHz

Remark 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- Remark 2. fHOCO: High-speed on-chip oscillator clock frequency (64 MHz max.)

- Remark 3. fill: High-speed on-chip oscillator clock frequency (32 MHz max.)

- Remark 4. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 5. Except subsystem clock operation, temperature condition of the TYP. value is TA = 25°C

- Note 1. Total current flowing into VDD, EVDD0, and EVDD1, including the input leakage current flowing when the level of the input pin is fixed to VDD, EVDD0, and EVDD1, or Vss, EVss0, and EVss1. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, D/A converter, comparator, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

Note 2. During HALT instruction execution by flash memory.

- Note 3. When high-speed on-chip oscillator and subsystem clock are stopped.

- **Note 4.** When high-speed system clock and subsystem clock are stopped.

- **Note 5.** When high-speed on-chip oscillator and high-speed system clock are stopped. When RTCLPC = 1 and setting ultra-low current consumption (AMPHS1 = 1). The current flowing into the RTC is included. However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- Note 6. Not including the current flowing into the RTC, 12-bit interval timer, and watchdog timer.

- Note 7.Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.<br/>HS (high-speed main) mode:  $2.7 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ @1 MHz to 32 MHz

- 2.4 V  $\leq$  VDD  $\leq$  5.5 V@1 MHz to 16 MHz

- Note 8. Regarding the value for current to operate the subsystem clock in STOP mode, refer to that in HALT mode.

- Remark 1. fMX: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- Remark 2. fHOCO: High-speed on-chip oscillator clock frequency (64 MHz max.)

- Remark 3. fin: High-speed on-chip oscillator clock frequency (32 MHz max.)

- Remark 4. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 5. Except subsystem clock operation and STOP mode, temperature condition of the TYP. value is TA = 25°C

<R> <R>

<R> <R>

<R> <R>

## (3) Flash ROM: 384 to 512 KB of 48- to 100-pin products

#### (TA = -40 to +105°C, 2.4 V $\leq$ EVDD0 = EVDD1 $\leq$ VDD $\leq$ 5.5 V, VSS = EVSS0 = EVSS1 = 0 V)

| Parameter | Symbol                            |           |                      | Conditions                                   |                                |                      | MIN.        | TYP. | MAX. | Uni  |   |

|-----------|-----------------------------------|-----------|----------------------|----------------------------------------------|--------------------------------|----------------------|-------------|------|------|------|---|

| Supply    | IDD1                              | Operat-   | HS (high-speed main) | fносо = 64 MHz,                              | Basic                          | VDD = 5.0 V          |             | 2.9  |      | mA   |   |

| current   |                                   | ing mode  | mode Note 5          | fiH = 32 MHz Note 3                          | operation                      | VDD = 3.0 V          |             | 2.9  |      | 1    |   |

| Note 1    |                                   |           |                      | fносо = 32 MHz,                              | Basic                          | VDD = 5.0 V          |             | 2.5  |      | 1    |   |

|           |                                   |           |                      | fiH = 32 MHz Note 3                          | operation                      | VDD = 3.0 V          |             | 2.5  |      | 1    |   |

|           |                                   |           | HS (high-speed main) | fносо = 64 MHz,                              | Normal                         | VDD = 5.0 V          |             | 6.0  | 11.2 | m/   |   |

|           |                                   |           | mode Note 5          | fiH = 32 MHz Note 3                          | operation                      | VDD = 3.0 V          |             | 6.0  | 11.2 |      |   |

|           |                                   |           |                      |                                              | fносо = 32 MHz,                | Normal               | VDD = 5.0 V |      | 5.5  | 10.6 | 1 |

|           |                                   |           |                      | fiH = 32 MHz Note 3                          | operation                      | VDD = 3.0 V          |             | 5.5  | 10.6 |      |   |

|           |                                   |           |                      | fносо = 48 MHz,                              | Normal                         | VDD = 5.0 V          |             | 4.7  | 8.6  |      |   |

|           |                                   |           |                      | fiH = 24 MHz Note 3                          | operation                      | VDD = 3.0 V          |             | 4.7  | 8.6  |      |   |

|           |                                   |           |                      | fносо = 24 MHz,                              | Normal                         | VDD = 5.0 V          |             | 4.4  | 8.2  |      |   |

|           |                                   |           |                      | fiH = 24 MHz Note 3                          | operation                      | VDD = 3.0 V          |             | 4.4  | 8.2  | 2    |   |

|           |                                   |           |                      | fносо = 16 MHz,                              | Normal                         | VDD = 5.0 V          |             | 3.3  | 5.9  |      |   |

|           |                                   |           |                      | fiH = 16 MHz Note 3                          | operation                      | VDD = 3.0 V          |             | 3.3  | 5.9  | 1    |   |

|           |                                   |           | HS (high-speed main) | fmx = 20 MHz Note 2,                         | Normal                         | Square wave input    |             | 3.7  | 6.8  | m    |   |

|           | mode Note 5 VDD = 5.0 V operation | operation | Resonator connection |                                              | 3.9                            | 7.0                  | 1           |      |      |      |   |

|           |                                   |           |                      | fmx = 20 MHz Note 2,                         | Normal                         | Square wave input    |             | 3.7  | 6.8  | 1    |   |

|           |                                   |           |                      | VDD = 3.0 V                                  | operation                      | Resonator connection |             | 3.9  | 7.0  | 1    |   |

|           |                                   |           |                      | fmx = 10 MHz Note 2,                         | Normal                         | Square wave input    |             | 2.3  | 4.1  |      |   |

|           |                                   |           |                      | VDD = 5.0 V                                  | operation                      | Resonator connection |             | 2.3  | 4.2  |      |   |

|           |                                   |           |                      | f <sub>MX</sub> = 10 MHz <sup>Note 2</sup> , | Normal                         | Square wave input    |             | 2.3  | 4.1  |      |   |

|           |                                   |           |                      | VDD = 3.0 V                                  | operation                      | Resonator connection |             | 2.3  | 4.2  | 1    |   |

|           |                                   |           | Subsystem clock      | fsub = 32.768 kHz Note 4                     | Normal                         | Square wave input    |             | 5.2  | 7.7  | μ    |   |

|           |                                   |           | operation            | TA = -40°C                                   | operation                      | Resonator connection |             | 5.2  | 7.7  | 1    |   |

|           |                                   |           |                      | fsub = 32.768 kHz Note 4                     | Normal                         | Square wave input    |             | 5.3  | 7.7  | 1    |   |

|           |                                   |           |                      | TA = +25°C                                   | operation                      | Resonator connection |             | 5.3  | 7.7  | 1    |   |

|           |                                   |           |                      | fsub = 32.768 kHz Note 4                     | Normal                         | Square wave input    |             | 5.5  | 10.6 | 1    |   |

|           |                                   |           |                      | TA = +50°C                                   | operation                      | Resonator connection |             | 5.5  | 10.6 | 1    |   |

|           |                                   |           |                      | fsue = 32.768 kHz Note 4                     | Normal                         | Square wave input    |             | 5.9  | 13.2 |      |   |

|           |                                   |           |                      | TA = +70°C                                   | operation Resonator connection |                      | 6.0         | 13.2 | 1    |      |   |

|           |                                   |           |                      | fsuв = 32.768 kHz <sup>Note 4</sup>          | Normal                         | Square wave input    |             | 6.8  | 17.5 | 1    |   |

|           |                                   |           |                      | $T_A = +85^{\circ}C$                         | operation                      | Resonator connection |             | 6.9  | 17.5 | 1    |   |

|           |                                   |           |                      | fsue = 32.768 kHz <sup>Note 4</sup>          | Normal                         | Square wave input    |             | 15.5 | 77.8 | 1    |   |

|           |                                   |           |                      | $T_A = +105^{\circ}C$                        | operation                      |                      |             |      | -    | -    |   |

|           |                                   |           |                      |                                              |                                | Resonator connection |             | 15.5 | 77.8 | L    |   |

(Notes and Remarks are listed on the next page.)

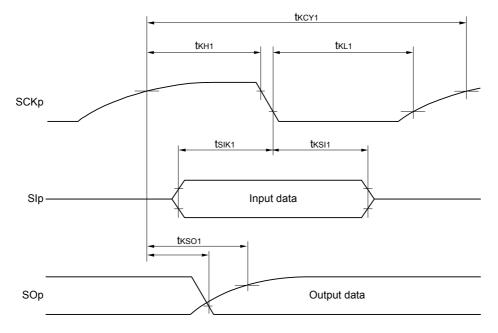

#### CSI mode connection diagram (during communication at different potential

- **Remark 5.** Rb[Ω]: Communication line (SCKp, SOp) pull-up resistance, Cb[F]: Communication line (SCKp, SOp) load capacitance, Vb[V]: Communication line voltage

- **Remark 6.** p: CSI number (p = 00, 01, 10, 20, 30, 31), m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), g: PIM and POM number (g = 0, 1, 3 to 5, 14)

- Remark 7. fmck: Serial array unit operation clock frequency (Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00))

- Remark 8. CSI01 of 48-, 52-, 64-pin products, and CSI11 and CSI21 cannot communicate at different potential. Use other CSI for communication at different potential.

| Parameter         | Symbol | Con                              | Conditions                                        |      |      |      | Unit |

|-------------------|--------|----------------------------------|---------------------------------------------------|------|------|------|------|

| Voltage detection | VLVDD0 | VPOC2, VPOC1, VPOC0 = 0, 1, 1, f | C2, VPOC1, VPOC0 = 0, 1, 1, falling reset voltage |      |      |      | V    |

| threshold         | VLVDD1 | LVIS1, LVIS0 = 1, 0              | LVIS1, LVIS0 = 1, 0 Rising release reset voltage  |      |      |      | V    |

|                   |        |                                  | Falling interrupt voltage                         | 2.75 | 2.86 | 2.97 | V    |

|                   | VLVDD2 | LVIS1, LVIS0 = 0, 1              | Rising release reset voltage                      | 2.90 | 3.02 | 3.14 | V    |

|                   |        |                                  | Falling interrupt voltage                         | 2.85 | 2.96 | 3.07 | V    |

|                   | VLVDD3 | LVIS1, LVIS0 = 0, 0              | Rising release reset voltage                      | 3.90 | 4.06 | 4.22 | V    |

|                   |        |                                  | Falling interrupt voltage                         | 3.83 | 3.98 | 4.13 | V    |

# (2) Interrupt & Reset Mode

(TA = -40 to +105°C, VPDR  $\leq$  VDD  $\leq$  5.5 V, VSS = 0 V)

# 3.6.7 Power supply voltage rising slope characteristics

#### (TA = -40 to +105°C, Vss = 0 V)

| Parameter                         | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|-----------------------------------|--------|------------|------|------|------|------|

| Power supply voltage rising slope | SVDD   |            |      |      | 54   | V/ms |

Caution Make sure to keep the internal reset state by the LVD circuit or an external reset until VDD reaches the operating voltage range shown in 3.4 AC Characteristics.

#### R5F104GKAFB, R5F104GLAFB R5F104GKGFB, R5F104GLGFB

# 4.7 52-pin products

R5F104JCAFA, R5F104JDAFA, R5F104JEAFA, R5F104JFAFA, R5F104JGAFA, R5F104JHAFA, R5F104JJAFA R5F104JCDFA, R5F104JDDFA, R5F104JEDFA, R5F104JFDFA, R5F104JGDFA, R5F104JHDFA, R5F104JJDFA R5F104JCGFA, R5F104JDGFA, R5F104JEGFA, R5F104JFGFA, R5F104JGGFA, R5F104JHGFA, R5F104JJGFA

| JEITA Package Code  | RENESAS Code | Previous Code  | MASS (TYP.) [g] |

|---------------------|--------------|----------------|-----------------|

| P-LQFP52-10x10-0.65 | PLQP0052JA-A | P52GB-65-GBS-1 | 0.3             |

© 2012 Renesas Electronics Corporation. All rights reserved.

#### R5F104LKAFB, R5F104LLAFB R5F104LKGFB, R5F104LLGFB