Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 48                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 12x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f104lcdfp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

RL78/G14 1. OUTLINE

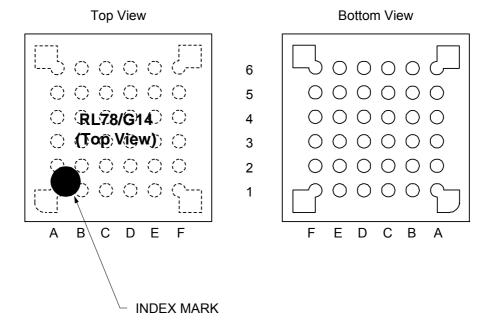

## **1.3.3 36-pin products**

• 36-pin plastic WFLGA (4 × 4 mm, 0.5 mm pitch)

|   | Α                                                                | В                                                               | С                                                   | D                                            | E                                     | F                                    |   |

|---|------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------|---------------------------------------|--------------------------------------|---|

| 6 | P60/SCLA0                                                        | VDD                                                             | P121/X1                                             | P122/X2/EXCLK                                | P137/INTP0                            | P40/TOOL0                            | 6 |

| 5 | P62/SSI00                                                        | P61/SDAA0                                                       | Vss                                                 | REGC                                         | RESET                                 | P120/ANI19/<br>VCOUT0 Note           | 5 |

| 4 | P72/SO21                                                         | P71/SI21/<br>SDA21                                              | P14/RxD2/SI20/<br>SDA20/TRDIOD0/<br>(SCLA0)         | P31/TI03/TO03/<br>INTP4/PCLBUZ0/<br>(TRJIO0) | P00/TI00/TxD1/<br>TRGCLKA/<br>(TRJO0) | P01/TO00/<br>RxD1/TRGCLKB/<br>TRJIO0 | 4 |

| 3 | P50/INTP1/<br>SI00/RxD0/<br>TOOLRxD/<br>SDA00/TRGIOA/<br>(TRJO0) | P70/SCK21/<br>SCL21                                             | P15/PCLBUZ1/<br>SCK20/SCL20/<br>TRDIOB0/<br>(SDAA0) | P22/ANI2/<br>ANO0 Note                       | P20/ANI0/<br>AVREFP                   | P21/ANI1/<br>AVREFM                  | 3 |

| 2 | P30/INTP3/<br>SCK00/SCL00/<br>TRJO0                              | P16/TI01/TO01/<br>INTP5/TRDIOC0/<br>IVREF0 Note/<br>(RXD0)      | P12/SO11/<br>TRDIOB1/<br>IVREF1 Note                | P11/SI11/<br>SDA11/<br>TRDIOC1               | P24/ANI4                              | P23/ANI3/<br>ANO1 <sup>Note</sup>    | 2 |

| 1 | P51/INTP2/<br>SO00/TxD0/<br>TOOLTxD/<br>TRGIOB                   | P17/TI02/TO02/<br>TRDIOA0/<br>TRDCLK/<br>IVCMP0 Note/<br>(TXD0) | P13/TxD2/<br>SO20/TRDIOA1/<br>IVCMP1 Note           | P10/SCK11/<br>SCL11/<br>TRDIOD1              | P147/ANI18/<br>VCOUT1 Note            | P25/ANI5                             | 1 |

| • | Δ                                                                | R                                                               | C.                                                  | n                                            | F                                     | F                                    |   |

**Note** Mounted on the 96 KB or more code flash memory products.

Caution Connect the REGC pin to Vss pin via a capacitor (0.47 to 1  $\mu$ F).

Remark 1. For pin identification, see 1.4 Pin Identification.

Remark 2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register 0, 1 (PIOR0, 1).

RL78/G14 1. OUTLINE

## 1.5.2 32-pin products

**Note** Mounted on the 96 KB or more code flash memory products.

RL78/G14 1. OUTLINE

[30-pin, 32-pin, 36-pin, 40-pin products (code flash memory 96 KB to 256 KB)]

Caution This outline describes the functions at the time when Peripheral I/O redirection register 0, 1 (PIOR0, 1) are set to 00H.

(1/2)

|                      |                                                                    | 30-pin                                                                                                                                                                                                                                                                                                                                                                                             | 32-pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36-pin                                                                                        | 40-pin                                                                                 |  |  |  |  |

|----------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| ı                    | Item                                                               | R5F104Ax<br>(x = F, G)                                                                                                                                                                                                                                                                                                                                                                             | R5F104Bx $(x = F, G)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R5F104Cx<br>(x = F, G)                                                                        | R5F104Ex<br>(x = F to H)                                                               |  |  |  |  |

| Code flash mem       | nory (KB)                                                          | 96 to 128                                                                                                                                                                                                                                                                                                                                                                                          | 96 to 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96 to 128                                                                                     | 96 to 192                                                                              |  |  |  |  |

| Data flash mem       | ory (KB)                                                           | 8                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                                                             | 8                                                                                      |  |  |  |  |

| RAM (KB)             |                                                                    | 12 to 16 Note                                                                                                                                                                                                                                                                                                                                                                                      | 12 to 16 Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12 to 16 Note                                                                                 | 12 to 20 Note                                                                          |  |  |  |  |

| Address space        |                                                                    | 1 MB                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                        |  |  |  |  |

| Main system<br>clock | High-speed system clock  High-speed on-chip oscillator clock (fiн) | HS (high-speed main) mo<br>HS (high-speed main) mo<br>LS (low-speed main) mod<br>LV (low-voltage main) mod<br>HS (high-speed main) mod<br>HS (high-speed main) mod<br>LS (low-speed main) mod                                                                                                                                                                                                      | ation, external main system de: 1 to 20 MHz (VDD = 2 de: 1 to 16 MHz (VDD = 1.4 de: 1 to 4 MHz (VDD = 1.4 de: 1 to 32 MHz (VDD = 1.4 de: 1 to 32 MHz (VDD = 2 de: 1 to 16 MHz (VDD = 2 de: 1 to 16 MHz (VDD = 1.6 de: 1 to 4 MHz ( | 7 to 5.5 V),<br>.4 to 5.5 V),<br>3 to 5.5 V),<br>6 to 5.5 V),<br>7 to 5.5 V),<br>4 to 5.5 V), |                                                                                        |  |  |  |  |

| Subsystem cloc       | k                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                               | XT1 (crystal) oscillation,<br>external subsystem<br>clock input (EXCLKS)<br>32.768 kHz |  |  |  |  |

| Low-speed on-c       | chip oscillator clock                                              | 15 kHz (TYP.): V <sub>DD</sub> = 1.6 to 5.5 V                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                        |  |  |  |  |

| General-purpose      | e register                                                         | 8 bits × 32 registers (8 bits                                                                                                                                                                                                                                                                                                                                                                      | s × 8 registers × 4 banks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                               |                                                                                        |  |  |  |  |

| Minimum instruc      | ction execution time                                               | 0.03125 μs (High-speed o                                                                                                                                                                                                                                                                                                                                                                           | on-chip oscillator clock: fiн                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | = 32 MHz operation)                                                                           |                                                                                        |  |  |  |  |

|                      |                                                                    | 0.05 μs (High-speed syste                                                                                                                                                                                                                                                                                                                                                                          | em clock: f <sub>M</sub> x = 20 MHz op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | eration)                                                                                      |                                                                                        |  |  |  |  |

|                      |                                                                    | — 30.5 μs (Subsystem clock: fsuβ = 32.768 kHz operation)                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                        |  |  |  |  |

| Instruction set      |                                                                    | <ul> <li>Data transfer (8/16 bits)</li> <li>Adder and subtractor/logical operation (8/16 bits)</li> <li>Multiplication (8 bits × 8 bits, 16 bits × 16 bits), Division (16 bits ÷ 16 bits, 32 bits ÷ 32 bits)</li> <li>Multiplication and Accumulation (16 bits × 16 bits + 32 bits)</li> <li>Rotate, barrel shift, and bit manipulation (Set, reset, test, and Boolean operation), etc.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                        |  |  |  |  |

| I/O port             | Total                                                              | 26                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32                                                                                            | 36                                                                                     |  |  |  |  |

|                      | CMOS I/O                                                           | 21                                                                                                                                                                                                                                                                                                                                                                                                 | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26                                                                                            | 28                                                                                     |  |  |  |  |

|                      | CMOS input                                                         | 3                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                                                             | 5                                                                                      |  |  |  |  |

|                      | CMOS output                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                                             | _                                                                                      |  |  |  |  |

|                      | N-ch open-drain I/O (6<br>V tolerance)                             | 2                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                                                             | 3                                                                                      |  |  |  |  |

| Timer                | 16-bit timer                                                       | 8 channels<br>(TAU: 4 channels, Timer F                                                                                                                                                                                                                                                                                                                                                            | RJ: 1 channel, Timer RD: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | channels, Timer RG: 1 cl                                                                      | hannel)                                                                                |  |  |  |  |

|                      | Watchdog timer                                                     | 1 channel                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                        |  |  |  |  |

|                      | Real-time clock (RTC)                                              | 1 channel                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                        |  |  |  |  |

|                      | 12-bit interval timer                                              | 1 channel                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                        |  |  |  |  |

|                      | Timer output                                                       | Timer outputs: 13 channe PWM outputs: 9 channels                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                        |  |  |  |  |

|                      | RTC output                                                         |                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                               | 1 • 1 Hz (subsystem clock: fsub = 32.768 kHz)                                          |  |  |  |  |

(Note is listed on the next page.)

# (2) Flash ROM: 96 to 256 KB of 30- to 100-pin products (TA = -40 to +85°C, 1.6 V $\leq$ EVDD0 = EVDD1 $\leq$ VDD $\leq$ 5.5 V, Vss = EVss0 = EVss1 = 0 V)

| Parameter         | Symbol      | Conditions                    |                         |                                                 |                         |                         |                      | TYP. | MAX. | Unit |  |

|-------------------|-------------|-------------------------------|-------------------------|-------------------------------------------------|-------------------------|-------------------------|----------------------|------|------|------|--|

| Supply            | IDD1        | Operat-                       | HS (high-speed main)    | fHOCO = 64 MHz,                                 | Basic                   | V <sub>DD</sub> = 5.0 V |                      | 2.6  |      | mA   |  |

| current<br>Note 1 |             | ing mode                      | mode Note 5             | f <sub>IH</sub> = 32 MHz Note 3                 | operation               | V <sub>DD</sub> = 3.0 V |                      | 2.6  |      |      |  |

| Note 1            |             |                               |                         | fHOCO = 32 MHz,                                 | Basic                   | V <sub>DD</sub> = 5.0 V |                      | 2.3  |      |      |  |

|                   |             |                               |                         | fih = 32 MHz Note 3                             | operation               | V <sub>DD</sub> = 3.0 V |                      | 2.3  |      |      |  |

|                   |             |                               | HS (high-speed main)    | fHOCO = 64 MHz,                                 | Normal                  | V <sub>DD</sub> = 5.0 V |                      | 5.4  | 10.2 | mA   |  |

|                   |             |                               | mode Note 5             | fih = 32 MHz Note 3                             | operation               | V <sub>DD</sub> = 3.0 V |                      | 5.4  | 10.2 |      |  |

|                   |             |                               |                         | fHOCO = 32 MHz,                                 | Normal                  | V <sub>DD</sub> = 5.0 V |                      | 5.0  | 9.6  |      |  |

|                   |             |                               |                         | fih = 32 MHz Note 3                             | operation               | V <sub>DD</sub> = 3.0 V |                      | 5.0  | 9.6  |      |  |

|                   |             |                               |                         | fHOCO = 48 MHz,                                 | Normal                  | V <sub>DD</sub> = 5.0 V |                      | 4.2  | 7.8  |      |  |

|                   |             |                               | fih = 24 MHz Note 3     | operation                                       | V <sub>DD</sub> = 3.0 V |                         | 4.2                  | 7.8  |      |      |  |

|                   |             |                               |                         | fhoco = 24 MHz,                                 | Normal                  | V <sub>DD</sub> = 5.0 V |                      | 4.0  | 7.4  |      |  |