#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                     |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 48MHz                                                                |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, TSI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT    |

| Number of I/O              | 54                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 4K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D - 16bit; D/A - 12bit                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | 64-LQFP (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl16z32vlh4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Ratings** 1

#### **Thermal handling ratings** 1.1

#### Table 1. Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _    | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

#### Moisture handling ratings 1.2

#### Table 2. Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level |      | 3    |      | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 1.3 ESD handling ratings

Table 3. ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | -2000 | +2000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 105 °C     | -100  | +100  | mA   | 3     |

1. Determined according to JEDEC Standard JESD22-A114, Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM).

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

| Symbol             | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>LVW1H</sub> | Level 1 falling (LVWV = 00)                                 | 2.62 | 2.70 | 2.78 | V    |       |

| $V_{LVW2H}$        | <ul> <li>Level 2 falling (LVWV = 01)</li> </ul>             | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | <ul> <li>Level 3 falling (LVWV = 10)</li> </ul>             | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{LVW4H}$        | • Level 4 falling (LVWV = 11)                               | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range   | _    | ±60  | _    | mV   | _     |

| V <sub>LVDL</sub>  | Falling low-voltage detect threshold — low range (LVDV=00)  | 1.54 | 1.60 | 1.66 | V    | _     |

|                    | Low-voltage warning thresholds — low range                  |      |      |      |      | 1     |

| V <sub>LVW1L</sub> | <ul> <li>Level 1 falling (LVWV = 00)</li> </ul>             | 1.74 | 1.80 | 1.86 | v    |       |

| V <sub>LVW2L</sub> | <ul> <li>Level 2 falling (LVWV = 01)</li> </ul>             | 1.84 | 1.90 | 1.96 | v    |       |

| V <sub>LVW3L</sub> | <ul> <li>Level 3 falling (LVWV = 10)</li> </ul>             | 1.94 | 2.00 | 2.06 | v    |       |

| V <sub>LVW4L</sub> | • Level 4 falling (LVWV = 11)                               | 2.04 | 2.10 | 2.16 | v    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis —<br>low range | —    | ±40  | —    | mV   | _     |

| V <sub>BG</sub>    | Bandgap voltage reference                                   | 0.97 | 1.00 | 1.03 | V    | —     |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed      | 900  | 1000 | 1100 | μs   | —     |

Table 6.

V<sub>DD</sub> supply LVD and POR operating requirements (continued)

1. Rising thresholds are falling threshold + hysteresis voltage

### 2.2.3 Voltage and current operating behaviors Table 7. Voltage and current operating behaviors

| Symbol           | Description                                                                                                                                                                                              | Min.                             | Max.       | Unit   | Notes |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|--------|-------|

| V <sub>OH</sub>  | Output high voltage — Normal drive pad (except<br>RESET_b)<br>• 2.7 V ≤ V <sub>DD</sub> ≤ 3.6 V, I <sub>OH</sub> = -5 mA                                                                                 | V <sub>DD</sub> – 0.5            | _          | V      | 1, 2  |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -2.5 \text{ mA}$                                                                                                   | V <sub>DD</sub> – 0.5            | —          | V      |       |

| V <sub>OH</sub>  | Output high voltage — High drive pad (except RESET_b)<br>• 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -20 mA<br>• 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -10 mA | $V_{DD} - 0.5$<br>$V_{DD} - 0.5$ |            | V<br>V | 1, 2  |

| I <sub>OHT</sub> | Output high current total for all ports                                                                                                                                                                  | —                                | 100        | mA     |       |

| V <sub>OL</sub>  | Output low voltage — Normal drive pad<br>• 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 5 mA<br>• 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 2.5 mA                   |                                  | 0.5<br>0.5 | V<br>V | 1     |

| Symbol           | Description                                                                                          | Min. | Max.  | Unit | Notes |

|------------------|------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| V <sub>OL</sub>  | Output low voltage — High drive pad                                                                  |      |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 20 mA                                 | _    | 0.5   | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 10 \text{ mA}$ | _    | 0.5   | V    |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                               | _    | 100   | mA   |       |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range                                           | _    | 1     | μA   | 3     |

| I <sub>IN</sub>  | Input leakage current (per pin) at 25 °C                                                             | _    | 0.025 | μA   | 3     |

| I <sub>IN</sub>  | Input leakage current (total all pins) for full temperature range                                    | _    | 65    | μA   | 3     |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                                           | —    | 1     | μA   |       |

| R <sub>PU</sub>  | Internal pullup resistors                                                                            | 20   | 50    | kΩ   | 4     |

Table 7. Voltage and current operating behaviors (continued)

1. PTB0, PTB1, PTD6, and PTD7 I/O have both high drive and normal drive capability selected by the associated PTx\_PCRn[DSE] control bit. All other GPIOs are normal drive only.

2. The reset pin only contains an active pull down device when configured as the RESET signal or as a GPIO. When configured as a GPIO output, it acts as a pseudo open drain output.

3. Measured at  $V_{DD} = 3.6 V$

4. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{SS}$

### 2.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$  and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 48 MHz

- Bus and flash clock = 24 MHz

- FEI clock mode

POR and VLLSx $\rightarrow$ RUN recovery use FEI clock mode at the default CPU and system frequency of 21 MHz, and a bus and flash clock frequency of 10.5 MHz.

| Symbol           | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.8 V to execution of the first instruction across the operating temperature range of the chip. |      |      | 300  | μs   | 1     |

|                  | • VLLS0 $\rightarrow$ RUN                                                                                                                                         | _    | 106  | 120  | μs   |       |

|                  |                                                                                                                                                                   |      |      |      |      |       |

| Symbol | Description               | Min. | Тур. | Max. | Unit | Notes |

|--------|---------------------------|------|------|------|------|-------|

|        | • VLLS1 → RUN             | —    | 105  | 117  | μs   |       |

|        | • VLLS3 $\rightarrow$ RUN | _    | 47   | 54   | μs   |       |

|        | • LLS $\rightarrow$ RUN   | _    | 4.5  | 5.0  | μs   |       |

|        | • VLPS → RUN              |      | 4.5  | 5.0  | μs   |       |

|        | • STOP → RUN              |      | 4.5  | 5.0  | μs   |       |

Table 8. Power mode transition operating behaviors (continued)

1. Normal boot (FTFA\_FOPT[LPBOOT]=11).

### 2.2.5 Power consumption operating behaviors

The maximum values stated in the following table represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

| Symbol                | Description                                                                                                                                                                                                  | Temp.     | Тур. | Max      | Unit | Note |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|----------|------|------|

| I <sub>DDA</sub>      | Analog supply current                                                                                                                                                                                        | —         | _    | See note | mA   | 1    |

| IDD_RUNCO_ CM         | Run mode current in compute<br>operation - 48 MHz core / 24 MHz<br>flash/ bus disabled, LPTMR running<br>using 4 MHz internal reference clock,<br>CoreMark® benchmark code<br>executing from flash, at 3.0 V |           | 6.1  | _        | mA   | 2    |

| I <sub>DD_RUNCO</sub> | Run mode current in compute<br>operation - 48 MHz core / 24 MHz<br>flash / bus clock disabled, code of<br>while(1) loop executing from flash, at<br>3.0 V                                                    | _         | 3.8  | 4.4      | mA   | 3    |

| I <sub>DD_RUN</sub>   | Run mode current - 48 MHz core / 24<br>MHz bus and flash, all peripheral<br>clocks disabled, code executing from<br>flash, at 3.0 V                                                                          | -         | 4.6  | 5.2      | mA   | 3    |

| I <sub>DD_RUN</sub>   | MHz bus and flash, all peripheral a clocks enabled, code executing from                                                                                                                                      | at 25 °C  | 6.0  | 6.2      | mA   | 3, 4 |

|                       |                                                                                                                                                                                                              | at 70 °C  | 6.2  | 6.4      | mA   |      |

|                       |                                                                                                                                                                                                              | at 125 °C | 6.2  | 6.5      | mA   |      |

Table 9. Power consumption operating behaviors

Table continues on the next page...

The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

- 2.  $V_{DD}$  = 3.3 V,  $T_A$  = 25 °C,  $f_{OSC}$  = 8 MHz (crystal),  $f_{SYS}$  = 48 MHz,  $f_{BUS}$  = 24 MHz

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method

## 2.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

### 2.2.8 Capacitance attributes

#### Table 12. Capacitance attributes

| Symbol          | Description       | Min. | Max. | Unit |

|-----------------|-------------------|------|------|------|

| C <sub>IN</sub> | Input capacitance | —    | 7    | pF   |

## 2.3 Switching specifications

### 2.3.1 Device clock specifications

#### Table 13. Device clock specifications

| Symbol             | Description                      | Min. | Max. | Unit |

|--------------------|----------------------------------|------|------|------|

|                    | Normal run mode                  | •    | •    | •    |

| f <sub>SYS</sub>   | System and core clock            | _    | 48   | MHz  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 24   | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 24   | MHz  |

| f <sub>LPTMR</sub> | LPTMR clock                      | _    | 24   | MHz  |

|                    | VLPR and VLPS modes <sup>1</sup> | •    | •    |      |

| f <sub>SYS</sub>   | System and core clock            | _    | 4    | MHz  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 1    | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 1    | MHz  |

| f <sub>LPTMR</sub> | LPTMR clock <sup>2</sup>         | _    | 24   | MHz  |

| f <sub>ERCLK</sub> | External reference clock         | _    | 16   | MHz  |

| Symbol | Description                                     | Min. | Max. | Unit |

|--------|-------------------------------------------------|------|------|------|

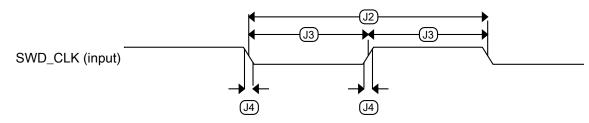

| J1     | SWD_CLK frequency of operation                  |      |      |      |

|        | Serial wire debug                               | 0    | 25   | MHz  |

| J2     | SWD_CLK cycle period                            | 1/J1 | _    | ns   |

| J3     | SWD_CLK clock pulse width                       |      |      |      |

|        | Serial wire debug                               | 20   |      | ns   |

| J4     | SWD_CLK rise and fall times                     | —    | 3    | ns   |

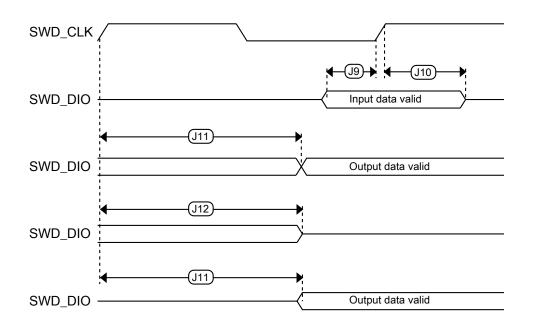

| J9     | SWD_DIO input data setup time to SWD_CLK rise   | 10   | _    | ns   |

| J10    | SWD_DIO input data hold time after SWD_CLK rise | 0    | _    | ns   |

| J11    | SWD_CLK high to SWD_DIO data valid              | —    | 32   | ns   |

| J12    | SWD_CLK high to SWD_DIO high-Z                  | 5    | _    | ns   |

| Table 17. | SWD full voltage range electricals ( | (continued) |

|-----------|--------------------------------------|-------------|

|-----------|--------------------------------------|-------------|

Figure 4. Serial wire clock input timing

## 3.2 System modules

There are no specifications necessary for the device's system modules.

## 3.3 Clock modules

## 3.3.1 MCG specifications

| Symbol                       | Description                                                                                                                               |                                                                           | Min.                            | Тур.      | Max.    | Unit                  | Notes |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------|-----------|---------|-----------------------|-------|

| f <sub>ints_ft</sub>         |                                                                                                                                           | frequency (slow clock) —<br>t nominal V <sub>DD</sub> and 25 °C           | —                               | 32.768    | —       | kHz                   |       |

| f <sub>ints_t</sub>          | Internal reference<br>user trimmed                                                                                                        | frequency (slow clock) —                                                  | 31.25                           | _         | 39.0625 | kHz                   |       |

| $\Delta_{fdco\_res\_t}$      | frequency at fixed                                                                                                                        | med average DCO output<br>voltage and temperature —<br>I] and C4[SCFTRIM] | _                               | ± 0.3     | ± 0.6   | %f <sub>dco</sub>     | 1     |

| $\Delta f_{dco\_t}$          |                                                                                                                                           | trimmed average DCO output<br>Itage and temperature                       | _                               | +0.5/-0.7 | ± 3     | %f <sub>dco</sub>     | 1, 2  |

| $\Delta f_{dco_t}$           |                                                                                                                                           | •                                                                         |                                 | ± 0.4     | ± 1.5   | %f <sub>dco</sub>     | 1, 2  |

| f <sub>intf_ft</sub>         | Internal reference frequency (fast clock) — factory trimmed at nominal $V_{\text{DD}}$ and 25 $^{\circ}\text{C}$                          |                                                                           | —                               | 4         | —       | MHz                   |       |

| ∆f <sub>intf_ft</sub>        | Frequency deviation of internal reference clock (fast clock) over temperature and voltage — factory trimmed at nominal $V_{DD}$ and 25 °C |                                                                           | _                               | +1/-2     | ± 3     | %f <sub>intf_ft</sub> | 2     |

| f <sub>intf_t</sub>          |                                                                                                                                           | frequency (fast clock) —<br>ominal V <sub>DD</sub> and 25 °C              | 3                               | —         | 5       | MHz                   |       |

| f <sub>loc_low</sub>         | Loss of external c<br>RANGE = 00                                                                                                          | lock minimum frequency —                                                  | (3/5) x<br>f <sub>ints_t</sub>  | —         | —       | kHz                   |       |

| f <sub>loc_high</sub>        | Loss of external c<br>RANGE = 01, 10,                                                                                                     | lock minimum frequency —<br>or 11                                         | (16/5) x<br>f <sub>ints_t</sub> | —         | _       | kHz                   |       |

|                              |                                                                                                                                           | FL                                                                        | L                               |           |         |                       |       |

| f <sub>fll_ref</sub>         | FLL reference free                                                                                                                        | quency range                                                              | 31.25                           | _         | 39.0625 | kHz                   |       |

| f <sub>dco</sub>             | DCO output<br>frequency range                                                                                                             | Low range (DRS = 00)<br>640 × f <sub>fll_ref</sub>                        | 20                              | 20.97     | 25      | MHz                   | 3, 4  |

|                              |                                                                                                                                           | Mid range (DRS = 01)<br>$1280 \times f_{fll_ref}$                         | 40                              | 41.94     | 48      | MHz                   |       |

| f <sub>dco_t_DMX3</sub><br>2 | DCO output<br>frequency                                                                                                                   | Low range (DRS = 00)                                                      | _                               | 23.99     |         | MHz                   | 5, 6  |

#### Table 18. MCG specifications

Table continues on the next page...

Kinetis KL16 Sub-Family, Rev5 08/2014.

| Symbol                   | Description                |                                                                                            | Min.   | Тур.  | Max.                                                          | Unit | Notes |

|--------------------------|----------------------------|--------------------------------------------------------------------------------------------|--------|-------|---------------------------------------------------------------|------|-------|

|                          |                            | $732 \times f_{fll\_ref}$                                                                  |        |       |                                                               |      |       |

|                          |                            | Mid range (DRS = 01)                                                                       | —      | 47.97 | —                                                             | MHz  | ]     |

|                          |                            | $1464 \times f_{fll\_ref}$                                                                 |        |       |                                                               |      |       |

| J <sub>cyc_fll</sub>     | FLL period jitter          |                                                                                            | _      | 180   | —                                                             | ps   | 7     |

|                          | • f <sub>VCO</sub> = 48 M  | 1Hz                                                                                        |        |       |                                                               |      |       |

| t <sub>fll_acquire</sub> | FLL target freque          | ncy acquisition time                                                                       |        | _     | 1                                                             | ms   | 8     |

|                          |                            | PL                                                                                         | L      |       |                                                               |      | 1     |

| f <sub>vco</sub>         | VCO operating fre          | equency                                                                                    | 48.0   | _     | 100                                                           | MHz  |       |

| I <sub>pli</sub>         |                            | rrent<br>/Hz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =<br>V multiplier = 48)  | _      | 1060  | —                                                             | μΑ   | 9     |

| I <sub>pli</sub>         |                            | rrent<br>/Hz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =<br> V multiplier = 24) | _      | 600   | _                                                             | μΑ   | 9     |

| f <sub>pll_ref</sub>     | PLL reference fre          | quency range                                                                               | 2.0    | _     | 4.0                                                           | MHz  |       |

| J <sub>cyc_pll</sub>     | PLL period jitter (        | RMS)                                                                                       |        |       |                                                               |      | 10    |

|                          | • f <sub>vco</sub> = 48 Mł | Hz                                                                                         | —      | 120   | _                                                             | ps   |       |

|                          | • f <sub>vco</sub> = 100 N | ЛНz                                                                                        | —      | 50    | _                                                             | ps   |       |

| J <sub>acc_pll</sub>     | PLL accumulated            | jitter over 1µs (RMS)                                                                      |        |       |                                                               |      | 10    |

|                          | • f <sub>vco</sub> = 48 MI | Hz                                                                                         | —      | 1350  | _                                                             | ps   |       |

|                          | • f <sub>vco</sub> = 100 M | ЛНz                                                                                        | —      | 600   | _                                                             | ps   |       |

| D <sub>lock</sub>        | Lock entry freque          | ncy tolerance                                                                              | ± 1.49 |       | ± 2.98                                                        | %    |       |

| D <sub>unl</sub>         | Lock exit frequen          | cy tolerance                                                                               | ± 4.47 | _     | ± 5.97                                                        | %    |       |

| t <sub>pll_lock</sub>    | Lock detector det          | ection time                                                                                | _      | _     | 150 × 10 <sup>-6</sup><br>+ 1075(1/<br>f <sub>pll_ref</sub> ) | S    | 11    |

### Table 18. MCG specifications (continued)

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. The deviation is relative to the factory trimmed frequency at nominal  $V_{DD}$  and 25 °C,  $f_{ints_{ft}}$ .

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32 = 0.

- The resulting system clock frequencies must not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco t</sub>) over voltage and temperature must be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32 = 1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 7. This specification is based on standard deviation (RMS) of period or frequency.

- 8. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 9. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 10. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- 11. This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 1. Assumes 25 MHz flash clock frequency.

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

#### 3.4.1.3 Flash high voltage current behaviors Table 23. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation | —    | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       | —    | 1.5  | 4.0  | mA   |

## 3.4.1.4 Reliability specifications

#### Table 24. NVM reliability specifications

| Symbol                  | Description                            | Min.    | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|---------|-------------------|------|--------|-------|

|                         | Program                                | n Flash |                   |      |        |       |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | _    | years  | —     |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | —    | years  | —     |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K    | 50 K              | _    | cycles | 2     |

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25 °C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40 °C  $\leq$  T<sub>i</sub>  $\leq$  125 °C.

## 3.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

# 3.6 Analog

### 3.6.1 ADC electrical specifications

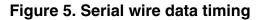

The 16-bit accuracy specifications listed in Table 25 and Table 26 are achievable on the differential pins ADCx\_DP0, ADCx\_DM0.

All other ADC channels meet the 13-bit differential/12-bit single-ended accuracy specifications.

| Symbol            | Description                               | Conditions                                                       | Min.             | Typ. <sup>1</sup> | Max.             | Unit | Notes |

|-------------------|-------------------------------------------|------------------------------------------------------------------|------------------|-------------------|------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage                            | Absolute                                                         | 1.71             |                   | 3.6              | V    |       |

| $\Delta V_{DDA}$  | Supply voltage                            | Delta to V <sub>DD</sub> (V <sub>DD</sub> – V <sub>DDA</sub> )   | -100             | 0                 | +100             | mV   | 2     |

| $\Delta V_{SSA}$  | Ground voltage                            | Delta to $V_{SS}$ ( $V_{SS} - V_{SSA}$ )                         | -100             | 0                 | +100             | mV   | 2     |

| $V_{REFH}$        | ADC reference voltage high                |                                                                  | 1.13             | V <sub>DDA</sub>  | V <sub>DDA</sub> | V    | 3     |

| V <sub>REFL</sub> | ADC reference voltage low                 |                                                                  | V <sub>SSA</sub> | V <sub>SSA</sub>  | V <sub>SSA</sub> | V    | 3     |

| V <sub>ADIN</sub> | Input voltage                             | 16-bit differential mode                                         | VREFL            |                   | 31/32 *<br>VREFH | V    |       |

|                   |                                           | All other modes                                                  | VREFL            | _                 | VREFH            |      |       |

| C <sub>ADIN</sub> | Input                                     | 16-bit mode                                                      | _                | 8                 | 10               | pF   |       |

|                   | capacitance                               | <ul> <li>8-bit / 10-bit / 12-bit<br/>modes</li> </ul>            | —                | 4                 | 5                |      |       |

| R <sub>ADIN</sub> | Input series resistance                   |                                                                  | _                | 2                 | 5                | kΩ   | _     |

| R <sub>AS</sub>   | Analog source<br>resistance<br>(external) | 13-bit / 12-bit modes<br>f <sub>ADCK</sub> < 4 MHz               |                  | _                 | 5                | kΩ   | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | ≤ 13-bit mode                                                    | 1.0              |                   | 18.0             | MHz  | 5     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | 16-bit mode                                                      | 2.0              |                   | 12.0             | MHz  | 5     |

| C <sub>rate</sub> | ADC conversion                            | ≤ 13-bit modes                                                   |                  |                   |                  |      | 6     |

|                   | rate                                      | No ADC hardware averaging                                        | 20.000           | _                 | 818.330          | Ksps |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |                  |                   |                  |      |       |

| C <sub>rate</sub> | ADC conversion                            | 16-bit mode                                                      |                  |                   |                  |      | 6     |

|                   | rate                                      | No ADC hardware averaging                                        | 37.037           | _                 | 461.467          | Ksps |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |                  |                   |                  |      |       |

### 3.6.1.1 16-bit ADC operating conditions Table 25. 16-bit ADC operating conditions

- 1. Typical values assume  $V_{DDA}$  = 3.0 V, Temp = 25 °C,  $f_{ADCK}$  = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- For packages without dedicated VREFH and VREFL pins, V<sub>REFH</sub> is internally tied to V<sub>DDA</sub>, and V<sub>REFL</sub> is internally tied to V<sub>SSA</sub>.

- 4. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 5. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

Kinetis KL16 Sub-Family, Rev5 08/2014.

6. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

Figure 6. ADC input impedance equivalency diagram

### 3.6.1.2 16-bit ADC electrical characteristics

| Symbol               | Description                  | Conditions <sup>1</sup>                           | Min.         | Typ. <sup>2</sup> | Max. | Unit             | Notes                |

|----------------------|------------------------------|---------------------------------------------------|--------------|-------------------|------|------------------|----------------------|

| I <sub>DDA_ADC</sub> | Supply current               |                                                   | 0.215        | —                 | 1.7  | mA               | 3                    |

|                      | ADC                          | • ADLPC = 1, ADHSC =                              | 1.2          | 2.4               | 3.9  | MHz              | t <sub>ADACK</sub> = |

|                      | asynchronous<br>clock source | 0                                                 | 2.4          | 4.0               | 6.1  | MHz              | 1/f <sub>ADACK</sub> |

|                      |                              | <ul> <li>ADLPC = 1, ADHSC =</li> <li>1</li> </ul> | 3.0          | 5.2               | 7.3  | MHz              |                      |

| f <sub>ADACK</sub>   |                              | • ADLPC = 0, ADHSC = 0                            | 4.4          | 6.2               | 9.5  | MHz              |                      |

|                      |                              | <ul> <li>ADLPC = 0, ADHSC =<br/>1</li> </ul>      |              |                   |      |                  |                      |

|                      | Sample Time                  | See Reference Manual chapte                       | r for sample | times             |      | 1                |                      |

| TUE                  | Total unadjusted             | 12-bit modes                                      | _            | ±4                | ±6.8 | LSB <sup>4</sup> | 5                    |

|                      | error                        | • <12-bit modes                                   | —            | ±1.4              | ±2.1 |                  |                      |

Table 26. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ )

| Symbol          | Description                     | Conditions <sup>1</sup>              | Min. | Typ. <sup>2</sup>      | Max.            | Unit             | Notes                                                                        |

|-----------------|---------------------------------|--------------------------------------|------|------------------------|-----------------|------------------|------------------------------------------------------------------------------|

| DNL             | Differential non-<br>linearity  | 12-bit modes                         | _    | ±0.7                   | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                                                                            |

|                 |                                 | 12-bit modes                         | _    | ±0.2                   | -0.3 to 0.5     |                  |                                                                              |

| INL             | Integral non-<br>linearity      | 12-bit modes                         | _    | ±1.0                   | -2.7 to<br>+1.9 | LSB <sup>4</sup> | 5                                                                            |

|                 |                                 | <ul> <li>&lt;12-bit modes</li> </ul> | _    | ±0.5                   | -0.7 to<br>+0.5 |                  |                                                                              |

| E <sub>FS</sub> | Full-scale error                | 12-bit modes                         | —    | -4                     | -5.4            | LSB <sup>4</sup> | V <sub>ADIN</sub> =                                                          |

|                 |                                 | <ul> <li>&lt;12-bit modes</li> </ul> | _    | -1.4                   | -1.8            |                  | V <sub>DDA</sub> <sup>5</sup>                                                |

| EQ              | Quantization                    | 16-bit modes                         | _    | -1 to 0                | —               | LSB <sup>4</sup> |                                                                              |

|                 | error                           | • ≤13-bit modes                      | _    | —                      | ±0.5            |                  |                                                                              |

| ENOB            | Effective number of bits        | 16-bit differential mode             | 12.8 | 14.5                   | _               | bits             | 6                                                                            |

|                 |                                 | • Avg = 32                           | 11.9 | 13.8                   |                 | bits             |                                                                              |

|                 |                                 | • Avg = 4                            |      |                        |                 |                  |                                                                              |

|                 |                                 | 16-bit single-ended mode             | 12.2 | 13.9                   | -               | bits             |                                                                              |

|                 |                                 | • Avg = 32                           | 11.4 | 13.1                   | -               | bits             |                                                                              |

|                 |                                 | • Avg = 4                            |      |                        |                 |                  |                                                                              |

| SINAD           | Signal-to-noise plus distortion | See ENOB                             | 6.02 | 2 × ENOB +             | 1.76            | dB               |                                                                              |

| THD             | Total harmonic distortion       | 16-bit differential mode             | _    | -94                    | _               | dB               | 7                                                                            |

|                 |                                 | • Avg = 32                           | _    | -85                    | _               | dB               |                                                                              |

|                 |                                 | 16-bit single-ended mode             |      |                        |                 |                  |                                                                              |

|                 |                                 | • Avg = 32                           |      |                        |                 |                  |                                                                              |

| SFDR            | Spurious free<br>dynamic range  | 16-bit differential mode             | 82   | 95                     |                 | dB               | 7                                                                            |

|                 | aynamic range                   | • Avg = 32                           | 78   | 90                     |                 | dB               |                                                                              |

|                 |                                 | 16-bit single-ended mode             | 10   | 30                     |                 | чD               |                                                                              |

|                 |                                 | <ul> <li>Avg = 32</li> </ul>         |      |                        |                 |                  |                                                                              |

| -               |                                 | ,                                    |      |                        |                 |                  |                                                                              |

| E <sub>IL</sub> | Input leakage<br>error          |                                      |      | $I_{ln} \times R_{AS}$ |                 | mV               | I <sub>In</sub> =<br>leakage<br>current                                      |

|                 |                                 |                                      |      |                        |                 |                  | (refer to<br>the MCU's<br>voltage<br>and<br>current<br>operating<br>ratings) |

| Table 26. | 16-bit ADC characteristics | $(V_{REFH} = V)$ | V <sub>DDA</sub> , V <sub>REFL</sub> : | = V <sub>SSA</sub> ) (continued) |

|-----------|----------------------------|------------------|----------------------------------------|----------------------------------|

|-----------|----------------------------|------------------|----------------------------------------|----------------------------------|

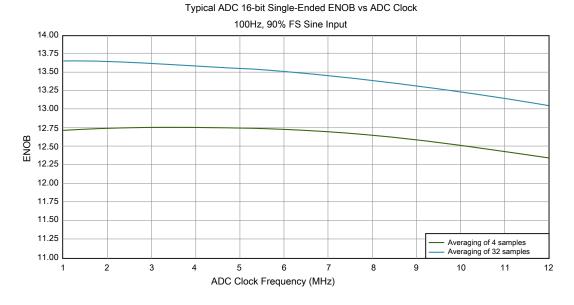

Figure 8. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

### 3.6.2 CMP and 6-bit DAC electrical specifications Table 27. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------|

| V <sub>DD</sub>    | Supply voltage                                      | 1.71                  | _    | 3.6             | V    |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)     | —                     | —    | 200             | μA   |

| IDDLS              | Supply current, low-speed mode (EN=1, PMODE=0)      | —                     | _    | 20              | μA   |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> – 0.3 |      | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>   | Analog input offset voltage                         | —                     | —    | 20              | mV   |

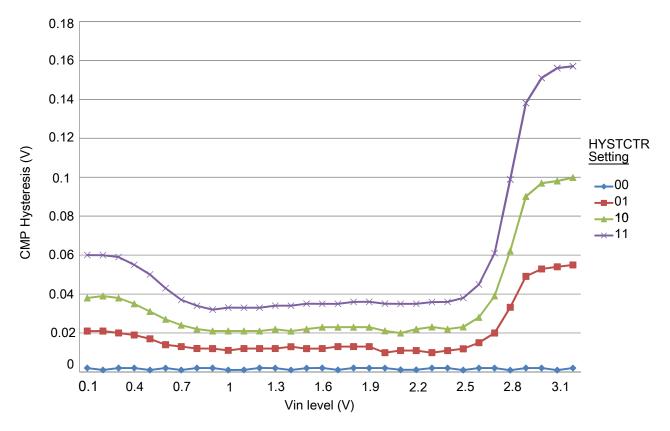

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |      |

|                    | • CR0[HYSTCTR] = 00                                 | —                     | 5    | _               | mV   |

|                    | • CR0[HYSTCTR] = 01                                 | _                     | 10   | _               | mV   |

|                    | • CR0[HYSTCTR] = 10                                 | —                     | 20   | _               | mV   |

|                    | <ul> <li>CR0[HYSTCTR] = 11</li> </ul>               | —                     | 30   | _               | mV   |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 | _    | _               | V    |

| V <sub>CMPOI</sub> | Output low                                          | —                     |      | 0.5             | V    |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns   |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns   |

|                    | Analog comparator initialization delay <sup>2</sup> | _                     |      | 40              | μs   |

Figure 10. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

### 3.6.3 12-bit DAC electrical characteristics

#### 3.6.3.1 12-bit DAC operating requirements Table 28. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min. | Max. | Unit | Notes |

|-------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71 | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| CL                | Output load capacitance | _    | 100  | pF   | 2     |

| ١L                | Output load current     | —    | 1    | mA   |       |

1. The DAC reference can be selected to be  $V_{DDA}$  or VREFH.

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

### 3.6.3.2 12-bit DAC operating behaviors Table 29. 12-bit DAC operating behaviors

| Symbol                     | Description                                                                            | Min.                      | Тур.     | Max.              | Unit   | Notes |

|----------------------------|----------------------------------------------------------------------------------------|---------------------------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub><br>P | Supply current — low-power mode                                                        |                           | —        | 250               | μΑ     |       |

| I <sub>DDA_DACH</sub><br>P | Supply current — high-speed mode                                                       | —                         | —        | 900               | μA     |       |

| t <sub>DACLP</sub>         | Full-scale settling time (0x080 to 0xF7F) — low-power mode                             | _                         | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>         | Full-scale settling time (0x080 to 0xF7F) — high-power mode                            | —                         | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>       | Code-to-code settling time (0xBF8 to<br>0xC08) — low-power mode and high-speed<br>mode | _                         | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>       | DAC output voltage range low — high-<br>speed mode, no load, DAC set to 0x000          | _                         | —        | 100               | mV     |       |

| V <sub>dacouth</sub>       | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF         | V <sub>DACR</sub><br>-100 | —        | V <sub>DACR</sub> | mV     |       |

| INL                        | Integral non-linearity error — high speed mode                                         | —                         | —        | ±8                | LSB    | 2     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> > 2<br>V                          | —                         | —        | ±1                | LSB    | 3     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                        | _                         | —        | ±1                | LSB    | 4     |

| V <sub>OFFSET</sub>        | Offset error                                                                           | _                         | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>             | Gain error                                                                             | _                         | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                       | Power supply rejection ratio, $V_{DDA} \ge 2.4 V$                                      | 60                        | —        | 90                | dB     |       |

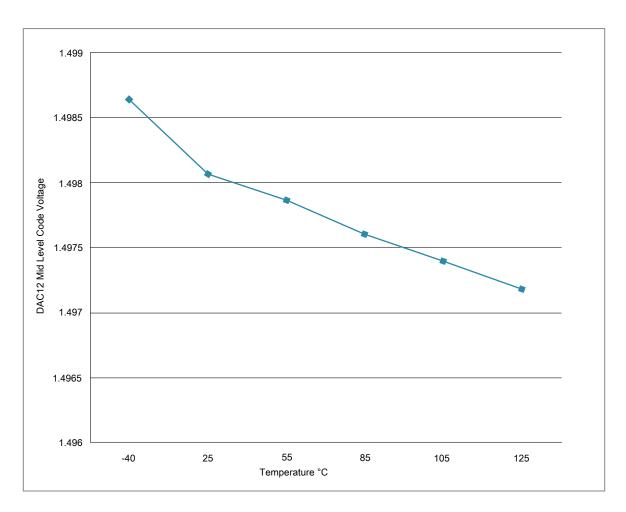

| T <sub>CO</sub>            | Temperature coefficient offset voltage                                                 | —                         | 3.7      | —                 | μV/C   | 6     |

| $T_{GE}$                   | Temperature coefficient gain error                                                     | —                         | 0.000421 | —                 | %FSR/C |       |

| Rop                        | Output resistance (load = $3 \text{ k}\Omega$ )                                        | —                         | —        | 250               | Ω      |       |

| SR                         | Slew rate -80h→ F7Fh→ 80h                                                              |                           |          |                   | V/µs   |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                       | 1.2                       | 1.7      | —                 |        |       |

|                            | <ul> <li>Low power (SP<sub>LP</sub>)</li> </ul>                                        | 0.05                      | 0.12     | —                 |        |       |

| BW                         | 3dB bandwidth                                                                          |                           |          |                   | kHz    |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                       | 550                       |          | _                 |        |       |

|                            | • Low power (SP <sub>LP</sub> )                                                        | 40                        |          | _                 |        |       |

1. Settling within  $\pm 1$  LSB

2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

3. The DNL is measured for 0 + 100 mV to  $V_{\text{DACR}}$  –100 mV

4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  – 100 mV

6. V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

Figure 12. Offset at half scale vs. temperature

# 3.7 Timers

See General switching specifications.

# 3.8 Communication interfaces

### 3.8.1 SPI switching specifications

The Serial Peripheral Interface (SPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic SPI timing modes. See the SPI chapter of the chip's Reference Manual for information about the modified transfer formats used for communicating with slower peripheral devices.

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all SPI pins.

| Num. | Symbol              | Description                    | Min.                      | Max.                     | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|--------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2   | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x                   | ns                 | 2    |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |      |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       |                          | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | —                        | t <sub>SPSCK</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x                   | ns                 | —    |

|      |                     |                                |                           | t <sub>periph</sub>      |                    |      |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 18                        | —                        | ns                 | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | —                        | ns                 | —    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                         | 15                       | ns                 | —    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | _                        | ns                 | —    |

| 10   | t <sub>RI</sub>     | Rise time input                | —                         | t <sub>periph</sub> - 25 | ns                 | _    |

|      | t <sub>FI</sub>     | Fall time input                |                           |                          |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | —                         | 25                       | ns                 | -    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                          |                    |      |

Table 30. SPI master mode timing on slew rate disabled pads

1. For SPI0  $f_{periph}$  is the bus clock (f\_{BUS}). For SPI1  $f_{periph}$  is the system clock (f\_{SYS}).

2.  $t_{periph} = 1/f_{periph}$

| Num. | Symbol             | Description                    | Min.                      | Max.                          | Unit               | Note |

|------|--------------------|--------------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>    | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub> | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>  | Enable lead time               | 1/2                       |                               | t <sub>SPSCK</sub> |      |

| 4    | t <sub>Lag</sub>   | Enable lag time                | 1/2                       | _                             | t <sub>SPSCK</sub> |      |

| 5    | twspsck            | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x<br>t <sub>periph</sub> | ns                 | _    |

| 6    | t <sub>SU</sub>    | Data setup time (inputs)       | 96                        | _                             | ns                 | _    |

| 7    | t <sub>HI</sub>    | Data hold time (inputs)        | 0                         | _                             | ns                 | _    |

# 7.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

# 7.2 Format

Part numbers for this device have the following format:

Q KL## A FFF R T PP CC N

# 7.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                 | Values                                                                                                                 |

|-------|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status        | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>                             |

| KL##  | Kinetis family              | • KL16                                                                                                                 |

| A     | Key attribute               | • Z = Cortex-M0+                                                                                                       |

| FFF   | Program flash memory size   | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> <li>128 = 128 KB</li> </ul>                                               |

| R     | Silicon revision            | <ul> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                    |

| Т     | Temperature range (°C)      | • V = -40 to 105                                                                                                       |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | • 4 = 48 MHz                                                                                                           |

| N     | Packaging type              | R = Tape and reel                                                                                                      |

# 7.4 Example

This is an example part number:

MKL16Z128VFM4

# 8 Terminology and guidelines

## 8.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

## 8.1.1 Example

This is an example of an operating requirement:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

## 8.2 Definition: Operating behavior

Unless otherwise specified, an *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

## 8.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

## 8.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | _    | 7    | pF   |

## 8.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol | Description                                    | Min. | Тур. | Max. | Unit |

|--------|------------------------------------------------|------|------|------|------|

| 1      | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

## 8.8.2 Example 2

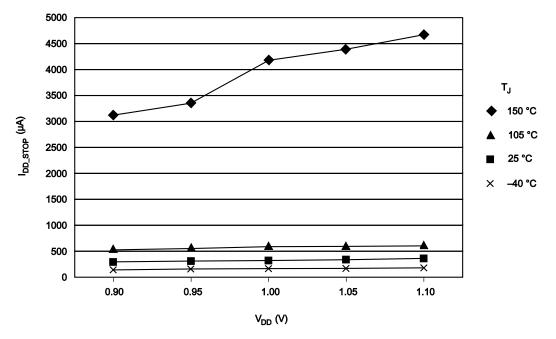

This is an example of a chart that shows typical values for various voltage and temperature conditions:

# 8.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):