Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 5                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                         |

| Supplier Device Package    | 8-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qt1acdwe |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MC68HC908QY4A MC68HC908QT4A MC68HC908QY2A MC68HC908QT2A MC68HC908QY1A MC68HC908QT1A

**Data Sheet**

M68HC08 Microcontrollers

MC68HC908QY4A Rev. 3 03/2010

freescale.com

# **List of Chapters**

\_\_\_\_\_

| Chapter 1 General Description                                 |

|---------------------------------------------------------------|

| Chapter 2 Memory                                              |

| Chapter 3 Analog-to-Digital Converter (ADC10) Module          |

| Chapter 4 Auto Wakeup Module (AWU)51                          |

| Chapter 5 Configuration Register (CONFIG)57                   |

| Chapter 6 Computer Operating Properly (COP)61                 |

| Chapter 7 Central Processor Unit (CPU)65                      |

| Chapter 8 External Interrupt (IRQ)77                          |

| Chapter 9 Keyboard Interrupt Module (KBI)                     |

| Chapter 10 Low-Voltage Inhibit (LVI)                          |

| Chapter 11 Oscillator (OSC) Module                            |

| Chapter 12 Input/Output Ports (PORTS)                         |

| Chapter 13 System Integration Module (SIM)109                 |

| Chapter 14 Timer Interface Module (TIM)125                    |

| Chapter 15 Development Support                                |

| Chapter 16 Electrical Specifications155                       |

| Chapter 17 Ordering Information and Mechanical Specifications |

| Appendix A 908QTA/QYxA Conversion Guidelines191               |

# Chapter 1 General Description

# 1.1 Introduction

The MC68HC908QY4A is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

| Device        | FLASH<br>Memory Size | ADC               | Pin<br>Count |

|---------------|----------------------|-------------------|--------------|

| MC68HC908QT1A | 1536 bytes           | —                 | 8 pins       |

| MC68HC908QT2A | 1536 bytes           | 6 channel, 10 bit | 8 pins       |

| MC68HC908QT4A | 4096 bytes           | 6 channel, 10 bit | 8 pins       |

| MC68HC908QY1A | 1536 bytes           | —                 | 16 pins      |

| MC68HC908QY2A | 1536 bytes           | 6 channel, 10 bit | 16 pins      |

| MC68HC908QY4A | 4096 bytes           | 6 channel, 10 bit | 16 pins      |

### Table 1-1. Summary of Device Variations

# 1.2 Features

Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- Software selectable 1 MHz, 2 MHz, or 3.2 MHz internal bus operation

- 8-bit trim capability

- ±25% untrimmed

- Trimmable to approximately 0.4%<sup>(1)</sup>

- Software selectable crystal oscillator range, 32–100 kHz, 1–8 MHz and 8–32 MHz

- Software configurable input clock from either internal or external source

- Auto wakeup from STOP capability using dedicated internal 32-kHz RC or bus clock source

- On-chip in-application programmable FLASH memory

- Internal program/erase voltage generation

- Monitor ROM containing user callable program/erase routines

- FLASH security<sup>(2)</sup>

<sup>1.</sup> See 16.11 Oscillator Characteristics for internal oscillator specifications

<sup>2.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

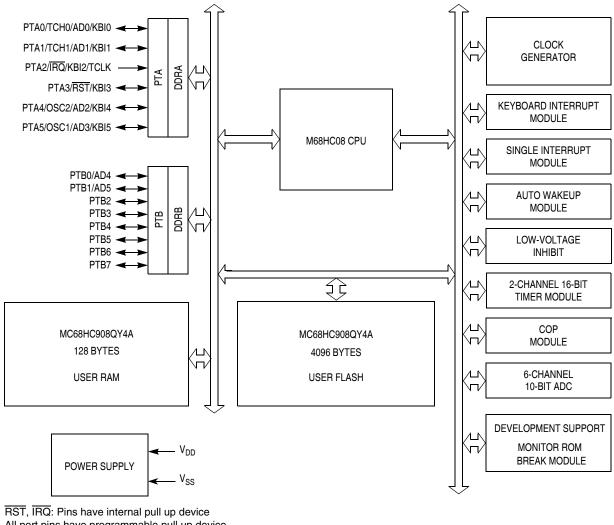

# 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HC908QY4A.

All port pins have internal pull up device All port pins have programmable pull up device PTA[0:5]: Higher current sink and source capability PTB[0:7]: Not available on 8-pin devices

Figure 1-1. Block Diagram

# **1.5 Pin Functions**

Table 1-2 provides a description of the pin functions.

| Pin<br>Name                         | Description                                                                                                         | Input/Output     |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|

| V <sub>DD</sub>                     | Power supply                                                                                                        | Power            |

| V <sub>SS</sub>                     | Power supply ground                                                                                                 | Power            |

|                                     | PTA0 — General purpose I/O port                                                                                     | Input/Output     |

|                                     | TCH0 — Timer Channel 0 I/O                                                                                          | Input/Output     |

| PTA0                                | AD0 — A/D channel 0 input                                                                                           | Input            |

|                                     | KBI0 — Keyboard interrupt input 0                                                                                   | Input            |

|                                     | PTA1 — General purpose I/O port                                                                                     | Input/Output     |

| PTA1                                | TCH1 — Timer Channel 1 I/O                                                                                          | Input/Output     |

| PIAI                                | AD1 — A/D channel 1 input                                                                                           | Input            |

|                                     | KBI1 — Keyboard interrupt input 1                                                                                   | Input            |

|                                     | PTA2 — General purpose input-only port                                                                              | Input            |

| PTA2                                | IRQ — External interrupt with programmable pullup and Schmitt trigger input                                         | Input            |

| P IA2                               | KBI2 — Keyboard interrupt input 2                                                                                   | Input            |

|                                     | TCLK — Timer clock input                                                                                            | Input            |

|                                     | PTA3 — General purpose I/O port                                                                                     | Input/Output     |

| PTA3                                | RST — Reset input, active low with internal pullup and Schmitt trigger                                              | Input            |

|                                     | KBI3 — Keyboard interrupt input 3                                                                                   | Input            |

|                                     | PTA4 — General purpose I/O port                                                                                     | Input/Output     |

| PTA4                                | OSC2 —XTAL oscillator output (XTAL option only)<br>RC or internal oscillator output (OSC2EN = 1 in PTAPUE register) | Output<br>Output |

|                                     | AD2 — A/D channel 2 input                                                                                           | Input            |

|                                     | KBI4 — Keyboard interrupt input 4                                                                                   | Input            |

|                                     | PTA5 — General purpose I/O port                                                                                     | Input/Output     |

|                                     | OSC1 — XTAL, RC, or external oscillator input                                                                       | Input            |

| PTA5                                | AD3 — A/D channel 3 input                                                                                           | Input            |

|                                     | KBI5 — Keyboard interrupt input 5                                                                                   | Input            |

| <b></b> (1)                         | PTB0 — General-purpose I/O port                                                                                     | Input/Output     |

| PTB0 <sup>(1)</sup>                 | AD4 — A/D channel 4 input                                                                                           | Input            |

| $\mathbf{p} = \mathbf{r} \cdot (1)$ | PTB1 — General-purpose I/O port                                                                                     | Input/Output     |

| PTB1 <sup>(1)</sup>                 | AD5 — A/D channel 5 input                                                                                           | Input            |

| PTB2-<br>PTB7 <sup>(1)</sup>        | 6 General-purpose I/O port                                                                                          | Input/Output     |

#### Table 1-2. Pin Functions

1. The PTB pins are not available on the 8-pin packages.

#### Memory

| \$0000<br>↓ | IDIRECT PAGE REGISTERS  | ]     |              |             |

|-------------|-------------------------|-------|--------------|-------------|

| \$003F      | 64 BYTES                |       |              |             |

| \$0040<br>↓ | UNIMPLEMENTED           |       |              |             |

| \$007F      | 64 BYTES                |       |              |             |

| \$0080<br>↓ | RAM                     |       |              |             |

| \$00FF      | 128 BYTES               |       |              |             |

| \$0100<br>↓ | UNIMPLEMENTED           |       |              |             |

| \$27FF      | 9984 BYTES              |       |              |             |

| \$2800<br>↓ | AUXILIARY ROM           |       |              |             |

| \$2A1F      | 544 BYTES               |       |              |             |

| \$2A20<br>↓ | UNIMPLEMENTED           |       |              |             |

| \$2F7D      | 1374 BYTES              |       |              |             |

| \$2F7E<br>↓ | AUXILIARY ROM           |       |              |             |

| \$2FFF      | 130 BYTES               |       |              |             |

| \$3000<br>↓ | UNIMPLEMENTED           |       |              |             |

| ↓<br>\$EDFF | 48640 BYTES             |       |              |             |

| \$EE00<br>↓ | FLASH MEMORY            | ] [   | RESERVED     | \$EE00<br>↓ |

| \$FDFF      | 4096 BYTES              |       | 2560 BYTES   | \$F7FF      |

| \$FE00      | MISCELLANEOUS REGISTERS | Ì 丶 、 | FLASH MEMORY | \$F800      |

| ↓<br>\$FE1F | 32 BYTES                |       | 1536 BYTES   | ↓<br>\$FDFF |

| \$FE20      | MONITOR ROM             |       |              | _           |

| ↓<br>\$FF7D | 350 BYTES               |       |              |             |

| \$FF7E      | UNIMPLEMENTED           | -     |              |             |

| ↓<br>\$FFAF | 50BYTES                 |       |              |             |

| \$FFB0      | FLASH                   |       |              |             |

| ↓<br>\$FFBD | 14 BYTES                |       |              |             |

| \$FFBE      | MISCELLANEOUS REGISTERS | -     |              |             |

| ↓<br>\$FFC1 | 4 BYTES                 |       |              |             |

| \$FFC2      | FLASH                   | 1     |              |             |

| ↓<br>\$FFCF | 14 BYTES                |       |              |             |

| \$FFD0      | USER VECTORS            | 1     |              |             |

| ↓<br>\$FFFF | 48 BYTES                |       |              |             |

| L_          |                         | -     |              |             |

MC68HC908QY4A, MC68HC908QT4A Memory Map MC68HC908QT1A, MC68HC908QT2A, MC68HC908QY1A, and MC68HC908QY2A Memory Map

Figure 2-1. Memory Map

# 2.6 FLASH Memory (FLASH)

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire monitor mode interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths.

This subsection describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from the internal  $V_{DD}$  supply. The program and erase operations are enabled through the use of an internal charge pump.

The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section.

**NOTE** An erased bit reads as a 1 and a programmed bit reads as a 0. A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

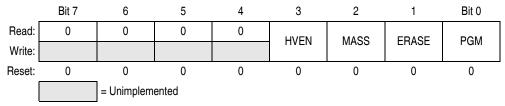

### 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

#### HVEN — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM =1 or ERASE =1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation.

- 1 = Mass erase operation selected

- 0 = Mass erase operation unselected

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

If the bus frequency is less than the ADCK frequency, precise sample time for continuous conversions cannot be guaranteed in short-sample mode (ADLSMP = 0). If the bus frequency is less than 1/11th of the ADCK frequency, precise sample time for continuous conversions cannot be guaranteed in long-sample mode (ADLSMP = 1).

When clear, the ADC10 will perform a single conversion (single conversion mode) each time ADSCR is written (assuming the ADCH[4:0] bits do not decode all 1s).

- 1 = Continuous conversion following a write to ADSCR

- 0 = One conversion following a write to ADSCR

#### ADCH[4:0] — Channel Select Bits

The ADCH[4:0] bits form a 5-bit field that is used to select one of the input channels. The input channels are detailed in Table 3-2. The successive approximation converter subsystem is turned off when the channel select bits are all set to 1. This feature allows explicit disabling of the ADC10 and isolation of the input channel from the I/O pad. Terminating continuous conversion mode this way will prevent an additional, single conversion from being performed. It is not necessary to set the channel select bits to all 1s to place the ADC10 in a low-power state, however, because the module is automatically placed in a low-power state when a conversion completes.

| ADCH4 | ADCH3 | ADCH2         | ADCH1 | ADCH0 | Input Select <sup>(1)</sup> |

|-------|-------|---------------|-------|-------|-----------------------------|

| 0     | 0     | 0             | 0     | 0     | AD0                         |

| 0     | 0     | 0             | 0     | 1     | AD1                         |

| 0     | 0     | 0             | 1     | 0     | AD2                         |

| 0     | 0     | 0             | 1     | 1     | AD3                         |

| 0     | 0     | 1             | 0     | 0     | AD4                         |

| 0     | 0     | 1             | 0     | 1     | AD5                         |

| 0     | 0     | 1             | 1     | 0     | Unused                      |

|       | Cor   | ntinuing thro | ugh   |       | Unused                      |

| 1     | 1     | 0             | 0     | 1     | Unused                      |

| 1     | 1     | 0             | 1     | 0     | BANDGAP REF <sup>(2)</sup>  |

| 1     | 1     | 0             | 1     | 1     | Reserved                    |

| 1     | 1     | 1             | 0     | 0     | Reserved                    |

| 1     | 1     | 1             | 0     | 1     | V <sub>REFH</sub>           |

| 1     | 1     | 1             | 1     | 0     | V <sub>REFL</sub>           |

| 1     | 1     | 1             | 1     | 1     | Low-power state             |

Table 3-2. Input Channel Select

1. If any unused or reserved channels are selected, the resulting conversion will be unknown.

2. Requires LVI to be powered (LVIPWRD =0, in CONFIG1)

### 3.8.2 ADC10 Result High Register (ADRH)

This register holds the MSBs of the result and is updated each time a conversion completes. All other bits read as 0s. Reading ADRH prevents the ADC10 from transferring subsequent conversion results into the result registers until ADRL is read. If ADRL is not read until the after next conversion is completed, then the intermediate conversion result will be lost. In 8-bit mode, this register contains no interlocking with ADRL.

# Chapter 6 Computer Operating Properly (COP)

# 6.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the configuration 1 (CONFIG1) register.

### SIM MODULE SIM RESET CIRCUIT BUSCLKX4 12-BIT SIM COUNTER RESET STATUS REGISTER **CLEAR STAGES 5-12 EARALL STAGES** COP TIMEOUT INTERNAL RESET SOURCES<sup>(1)</sup> STOP INSTRUCTION COPCTL WRITE COP CLOCK COP MODULE 6-BIT COP COUNTER COPEN (FROM SIM) COPD (FROM CONFIG1) CLEAR RESET COP COUNTER COPCTL WRITE COP RATE SELECT (COPRS FROM CONFIG1)

# 6.2 Functional Description

1. See Chapter 13 System Integration Module (SIM) for more details.

Figure 6-1. COP Block Diagram

**Central Processor Unit (CPU)**

# 7.7 Instruction Set Summary

Table 7-1 provides a summary of the M68HC08 instruction set.

| Source                                                                                                   | Operation                                               | Description                                                           |    |   | Effec<br>on CC |   |   |   | Address<br>Mode                                                                                          | Opcode                                           | Operand                                            | es                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------|----|---|----------------|---|---|---|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|--------------------------------------|

| Form                                                                                                     |                                                         |                                                                       | ۷  | н | -              | Ν | z | С | Add<br>Moc                                                                                               | Opc                                              | Ope                                                | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC ,X<br>ADC ,X<br>ADC opr,SP<br>ADC opr,SP | Add with Carry                                          | A ← (A) + (M) + (C)                                                   | ţ  | ţ | _              | ţ | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff          | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ADD #opr<br>ADD opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD opr,SP<br>ADD opr,SP                     | Add without Carry                                       | A ← (A) + (M)                                                         | ţ  | ţ |                | ţ | ţ | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB |                                                    | 23443245                             |

| AIS #opr                                                                                                 | Add Immediate Value (Signed) to SP                      | $SP \leftarrow (SP) + (16 \ \ensuremath{M})$                          | -  | - | -              | - | - | - | IMM                                                                                                      | A7                                               | ii                                                 | 2                                    |

| AIX #opr                                                                                                 | Add Immediate Value (Signed) to H:X                     | $H:X \leftarrow (H:X) + (16 \mathrel{\scriptstyle{\triangleleft}} M)$ | -  | - | Ι              | - | - | - | IMM                                                                                                      | AF                                               | ii                                                 | 2                                    |

| AND #opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND opr,X<br>AND ,X<br>AND opr,SP<br>AND opr,SP         | Logical AND                                             | A ← (A) & (M)                                                         | 0  | _ | _              | ţ | ţ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff    | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL ,X                                                 | Arithmetic Shift Left<br>(Same as LSL)                  |                                                                       | ţ  | _ | _              | ţ | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                     | 4<br>1<br>4<br>3<br>5                |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                          | Arithmetic Shift Right                                  |                                                                       | ţ  | _ | -              | ţ | ţ | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                     | 4<br>1<br>4<br>3<br>5                |

| BCC rel                                                                                                  | Branch if Carry Bit Clear                               | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                              | -  | - | -              | - | - | - | REL                                                                                                      | 24                                               | rr                                                 | 3                                    |

| BCLR n, opr                                                                                              | Clear Bit n in M                                        | Mn ← 0                                                                | _  | _ | _              | _ | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |

| BCS rel                                                                                                  | Branch if Carry Bit Set (Same as BLO)                   | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                     | -  | - | I              | - | - | - | REL                                                                                                      | 25                                               | rr                                                 | 3                                    |

| BEQ rel                                                                                                  | Branch if Equal                                         | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) = 1$                     | -  | - | -              | _ | - | - | REL                                                                                                      | 27                                               | rr                                                 | 3                                    |

| BGE opr                                                                                                  | Branch if Greater Than or Equal To<br>(Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 0$            | -  | - | -              | _ | - | - | REL                                                                                                      | 90                                               | rr                                                 | 3                                    |

| BGT <i>opr</i>                                                                                           | Branch if Greater Than (Signed<br>Operands)             | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 0$   | -  | - | _              | _ | - | - | REL                                                                                                      | 92                                               | rr                                                 | 3                                    |

| BHCC rel                                                                                                 | Branch if Half Carry Bit Clear                          | $PC \leftarrow (PC) + 2 + rel? (H) = 0$                               | -  | - | -              | _ | - | - | REL                                                                                                      | 28                                               | rr                                                 | 3                                    |

| BHCS rel                                                                                                 | Branch if Half Carry Bit Set                            | $PC \leftarrow (PC) + 2 + rel? (H) = 1$                               | -  | - | _              | - | - | - | REL                                                                                                      | 29                                               | rr                                                 | 3                                    |

| BHI <i>rel</i>                                                                                           | Branch if Higher                                        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 0$            | 1- | - | 1-             | - | - | - | REL                                                                                                      | 22                                               | rr                                                 | 3                                    |

### Table 7-1. Instruction Set Summary (Sheet 1 of 6)

External Interrupt (IRQ)

# Chapter 10 Low-Voltage Inhibit (LVI)

# **10.1 Introduction**

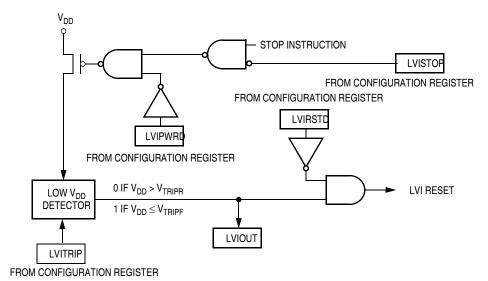

The low-voltage inhibit (LVI) module is provided as a system protection mechanism to prevent the MCU from operating below a certain operating supply voltage level. The module has several configuration options to allow functionality to be tailored to different system level demands.

The configuration registers (see Chapter 5 Configuration Register (CONFIG)) contain control bits for this module.

## **10.2 Features**

Features of the LVI module include:

- Programmable LVI reset

- Selectable LVI trip voltage

- Programmable stop mode operation

## **10.3 Functional Description**

Figure 10-1 shows the structure of the LVI module. LVISTOP, LVIPWRD, LVITRIP, and LVIRSTD are user selectable options found in the configuration register.

Figure 10-1. LVI Module Block Diagram

Low-Voltage Inhibit (LVI)

### 11.3.1.2 XTAL Oscillator Clock (XTALCLK)

XTALCLK is the XTAL oscillator output signal. It runs at the full speed of the crystal ( $f_{XCLK}$ ) and comes directly from the crystal oscillator circuit. Figure 11-2 shows only the logical relation of XTALCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of XTALCLK is unknown and may depend on the crystal and other external factors. The frequency of XTALCLK can be unstable at start up.

### 11.3.1.3 RC Oscillator Clock (RCCLK)

RCCLK is the RC oscillator output signal. Its frequency is directly proportional to the time constant of the external R ( $R_{EXT}$ ) and internal C. Figure 11-3 shows only the logical relation of RCCLK to OSC1 and may not represent the actual circuitry.

### 11.3.1.4 Internal Oscillator Clock (INTCLK)

INTCLK is the internal oscillator output signal. INTCLK is software selectable to be nominally 12.8 MHz, 8.0 MHz, or 4.0 MHz. INTCLK can be digitally adjusted using the oscillator trimming feature of the OSCTRIM register (see 11.3.2.1 Internal Oscillator Trimming).

#### 11.3.1.5 Bus Clock Times 4 (BUSCLKX4)

BUSCLKX4 is the same frequency as the input clock (XTALCLK, RCCLK, or INTCLK). This signal is driven to the SIM module and is used during recovery from reset and stop and is the clock source for the COP module.

### 11.3.1.6 Bus Clock Times 2 (BUSCLKX2)

The frequency of this signal is equal to half of the BUSCLKX4. This signal is driven to the SIM for generation of the bus clocks used by the CPU and other modules on the MCU. BUSCLKX2 will be divided by two in the SIM. The internal bus frequency is one fourth of the XTALCLK, RCCLK, or INTCLK frequency.

### 11.3.2 Internal Oscillator

The internal oscillator circuit is designed for use with no external components to provide a clock source with a tolerance of less than  $\pm 25\%$  untrimmed. An 8-bit register (OSCTRIM) allows the digital adjustment to a tolerance of ACC<sub>INT</sub>. See the oscillator characteristics in the Electrical section of this data sheet.

The internal oscillator is capable of generating clocks of 12.8 MHz, 8.0 MHz, or 4.0 MHz (INTCLK) resulting in a bus frequency (INTCLK divided by 4) of 3.2 MHz, 2.0 MHz, or 1.0 MHz respectively. The bus clock is software selectable and defaults to the 3.2-MHz bus out of reset. Users can increase the bus frequency based on the voltage range of their application.

Figure 11-3 shows how BUSCLKX4 is derived from INTCLK and OSC2 can output BUSCLKX4 by setting OSC2EN.

### 11.3.2.1 Internal Oscillator Trimming

OSCTRIM allows a clock period adjustment of +127 and -128 steps. Increasing the OSCTRIM value increases the clock period, which decreases the clock frequency. Trimming allows the internal clock frequency to be fine tuned to the target frequency.

All devices are factory programmed with trim values that are stored in FLASH memory at locations \$FFC0 and \$FFC1. The trim value is **not** automatically loaded into the OSCTRIM register. User software must

System Integration Module (SIM)

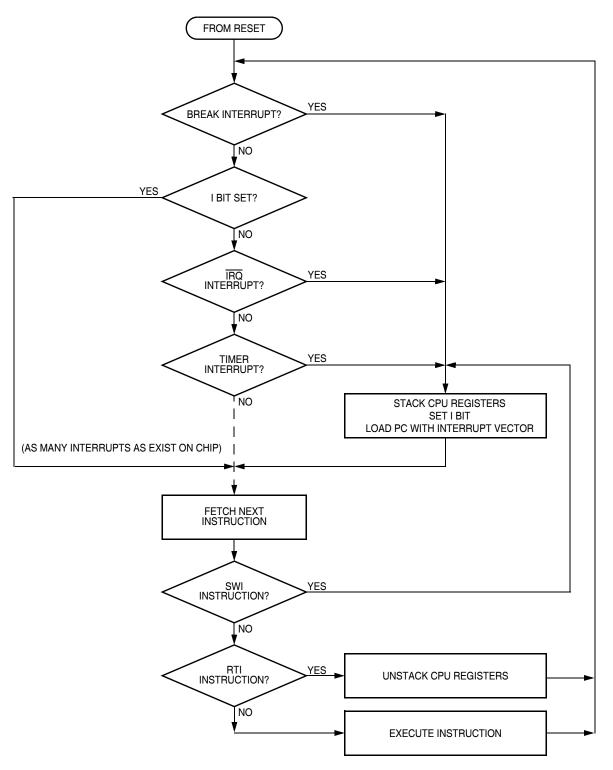

Figure 13-7. Interrupt Processing

# Chapter 15 Development Support

# **15.1 Introduction**

This section describes the break module, the monitor module (MON), and the monitor mode entry methods.

# 15.2 Break Module (BRK)

The break module can generate a break interrupt that stops normal program flow at a defined address to enter a background program.

Features include:

- Accessible input/output (I/O) registers during the break Interrupt

- Central processor unit (CPU) generated break interrupts

- Software-generated break interrupts

- Computer operating properly (COP) disabling during break interrupts

### 15.2.1 Functional Description

When the internal address bus matches the value written in the break address registers, the break module issues a breakpoint signal (BKPT) to the system integration module (SIM). The SIM then causes the CPU to load the instruction register with a software interrupt instruction (SWI). The program counter vectors to \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode).

The following events can cause a break interrupt to occur:

- A CPU generated address (the address in the program counter) matches the contents of the break address registers.

- Software writes a 1 to the BRKA bit in the break status and control register.

When a CPU generated address matches the contents of the break address registers, the break interrupt is generated. A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the microcontroller unit (MCU) to normal operation.

Figure 15-2 shows the structure of the break module.

When the internal address bus matches the value written in the break address registers or when software writes a 1 to the BRKA bit in the break status and control register, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode)

# Chapter 16 Electrical Specifications

## 16.1 Introduction

This section contains electrical and timing specifications.

# 16.2 Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the microcontroller unit (MCU) can be exposed without permanently damaging it.

NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 16.5 5-V DC Electrical Characteristics and 16.8 3-V DC Electrical Characteristics for guaranteed operating conditions.

| Characteristic <sup>(1)</sup>                                        | Symbol                               | Value                                  | Unit |

|----------------------------------------------------------------------|--------------------------------------|----------------------------------------|------|

| Supply voltage                                                       | V <sub>DD</sub>                      | -0.3 to +6.0                           | V    |

| Input voltage                                                        | V <sub>IN</sub>                      | $V_{\rm SS}$ –0.3 to $V_{\rm DD}$ +0.3 | V    |

| Mode entry voltage, IRQ pin                                          | V <sub>TST</sub>                     | V <sub>SS</sub> –0.3 to +9.1           | V    |

| Maximum current per pin excluding PTA0–PTA5, $V_{DD}$ , and $V_{SS}$ | I                                    | ±15                                    | mA   |

| Maximum current for pins PTA0-PTA5                                   | I <sub>PTA0</sub> _I <sub>PTA5</sub> | ±25                                    | mA   |

| Storage temperature                                                  | T <sub>STG</sub>                     | −55 to +150                            | °C   |

| Maximum current out of V <sub>SS</sub>                               | I <sub>MVSS</sub>                    | 100                                    | mA   |

| Maximum current into V <sub>DD</sub>                                 | I <sub>MVDD</sub>                    | 100                                    | mA   |

1. Voltages references to  $V_{SS}$ .

### NOTE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{IN}$  and  $V_{OUT}$  be constrained to the range  $V_{SS} \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ .)

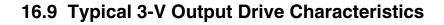

Figure 16-4. Typical 3-Volt Output High Voltage versus Output High Current (25°C)

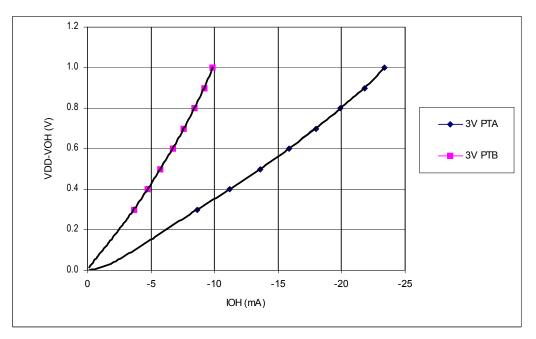

Figure 16-5. Typical 3-Volt Output Low Voltage versus Output Low Current (25°C)

**Ordering Information and Mechanical Specifications**

Case 948F page 1 of 3

## A.2.2 Enhanced Oscillator Module (OSC)

The QYxA contains a much enhanced oscillator module that allows more options than the QYx Classic.

- The ICFS bits in the Oscillator Status and Control Register (OSCSC) allow the Internal Oscillator to be configured for 1-, 2-, or 3.2-MHz operation. Also, the ECFS bits in the same register allow a low, medium, or high crystal frequency range to be selected for the source of the system clock. With this option you can choose to use a 32-kHz (low range) or a 16-MHz (high range) crystal.

- Another improvement to the Oscillator Module design is that you can switch between internal

oscillator and external oscillator options at any time. For example, if you wanted the low power

advantage of running from a 32-kHz crystal but still needed some processing power to perform

math calculations you could switch back and forth between internal and external clock. The same

is true for switching between 1-, 2-, and 3.2-MHz internal oscillator options.

### A.2.2.1 Registers Affected

|        | Bit 7           | 6       | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |  |  |

|--------|-----------------|---------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Read:  | OSCOPT1         | OSCOPT0 | ICFS1 | ICFS0 | ECFS1 | ECFS0 | ECGON | ECGST |  |  |  |  |

| Write: | 0300F11         | 0300F10 | 10131 | 10530 | LOFST | LOFSU | LOGON |       |  |  |  |  |

| Reset: | 0               | 0       | 1     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |

|        | = Unimplemented |         |       |       |       |       |       |       |  |  |  |  |

#### Figure A-4. Oscillator Status and Control Register (OSCSC)

The OSCOPT bits are no longer in the CONFIG2 register and now reside in the OSCSC register. Also, the ICFSx and ECFSx bits now reside in this register.

The IFS bits are used to select different Internal Oscillator speeds.

The ECFS bits are used to select the range of crystal that should be used to provide the reference clock.