Welcome to **E-XFL.COM**

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |  |  |  |

|----------------------------|------------------------------------------------------------------------|--|--|--|

| Product Status             | Obsolete                                                               |  |  |  |

| Core Processor             | HC08                                                                   |  |  |  |

| Core Size                  | 8-Bit                                                                  |  |  |  |

| Speed                      | 8MHz                                                                   |  |  |  |

| Connectivity               | -                                                                      |  |  |  |

| Peripherals                | LVD, POR, PWM                                                          |  |  |  |

| Number of I/O              | 5                                                                      |  |  |  |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |  |  |  |

| Program Memory Type        | FLASH                                                                  |  |  |  |

| EEPROM Size                | -                                                                      |  |  |  |

| RAM Size                   | 128 x 8                                                                |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |  |  |  |

| Data Converters            | -                                                                      |  |  |  |

| Oscillator Type            | Internal                                                               |  |  |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |  |  |  |

| Mounting Type              | Surface Mount                                                          |  |  |  |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                          |  |  |  |

| Supplier Device Package    | 8-SO                                                                   |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qt1acdwer |  |  |  |

| Purchase UKL               | https://www.e-xtl.com/product-detail/nxp-semiconductors/mc908qt1acdwer |  |  |  |

This page intentionally blank.

# **Chapter 1 General Description**

## 1.1 Introduction

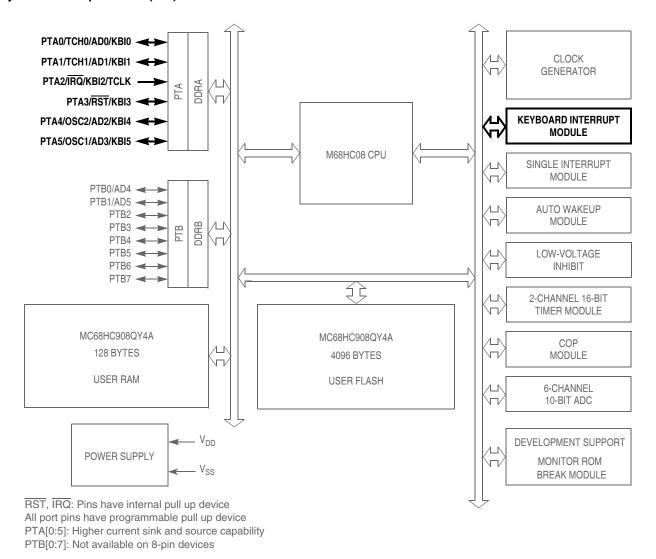

The MC68HC908QY4A is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

**FLASH** Pin Device ADC **Memory Size** Count 1536 bytes MC68HC908QT1A 8 pins MC68HC908QT2A 1536 bytes 6 channel, 10 bit 8 pins MC68HC908QT4A 6 channel, 10 bit 4096 bytes 8 pins MC68HC908QY1A 1536 bytes 16 pins MC68HC908QY2A 1536 bytes 6 channel, 10 bit 16 pins MC68HC908QY4A 4096 bytes 6 channel, 10 bit 16 pins

**Table 1-1. Summary of Device Variations**

## 1.2 Features

## Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- Software selectable 1 MHz, 2 MHz, or 3.2 MHz internal bus operation

- 8-bit trim capability

- ±25% untrimmed

- Trimmable to approximately 0.4%<sup>(1)</sup>

- Software selectable crystal oscillator range, 32–100 kHz, 1–8 MHz and 8–32 MHz

- Software configurable input clock from either internal or external source

- Auto wakeup from STOP capability using dedicated internal 32-kHz RC or bus clock source

- On-chip in-application programmable FLASH memory

- Internal program/erase voltage generation

- Monitor ROM containing user callable program/erase routines

- FLASH security<sup>(2)</sup>

<sup>1.</sup> See 16.11 Oscillator Characteristics for internal oscillator specifications

<sup>2.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Memory

Table 2-1. Vector Addresses

| Vector Priority | Vector             | Address               | Vector                         |

|-----------------|--------------------|-----------------------|--------------------------------|

| Lowest          | IF22-<br>IF16      | \$FFD0,1-<br>\$FFDC,D | Not used                       |

| Ţ               | IF15               | \$FFDE,F              | ADC conversion complete vector |

|                 | IF14               | \$FFE0,1              | Keyboard vector                |

|                 | IF13               | _                     | Not used                       |

|                 | IF12               | _                     | Not used                       |

|                 | IF11               | _                     | Not used                       |

|                 | IF10               | _                     | Not used                       |

|                 | IF9                | _                     | Not used                       |

|                 | IF8                | _                     | Not used                       |

|                 | IF7                | _                     | Not used                       |

|                 | IF6                | _                     | Not used                       |

|                 | IF5                | \$FFF2,3              | TIM overflow vector            |

|                 | IF4                | \$FFF4,5              | TIM channel 1 vector           |

|                 | IF3                | \$FFF6,7              | TIM channel 0 vector           |

|                 | IF2                | _                     | Not used                       |

|                 | IF1                | \$FFFA,B              | ĪRQ vector                     |

|                 | _                  | \$FFFC,D              | SWI vector                     |

| Highest         | Highest — \$FFFE,F |                       | Reset vector                   |

# 2.5 Random-Access Memory (RAM)

This MCU includes static RAM. The locations in RAM below \$0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait or stop mode. At power-on, the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention.

For compatibility with older M68HC05 MCUs, the HC08 resets the stack pointer to \$00FF. In the devices that have RAM above \$00FF, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM).

| 1 ;point one past RAM;SP<-(H:X-1) | LDHX #RamLast+1<br>TXS |

|-----------------------------------|------------------------|

|-----------------------------------|------------------------|

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

# 2.6 FLASH Memory (FLASH)

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire monitor mode interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths.

This subsection describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from the internal  $V_{DD}$  supply. The program and erase operations are enabled through the use of an internal charge pump.

The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section.

#### NOTE

An erased bit reads as a 1 and a programmed bit reads as a 0. A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

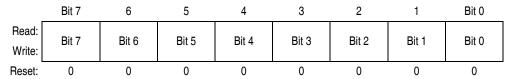

# 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

#### **HVEN** — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM =1 or ERASE =1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

## MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation.

- 1 = Mass erase operation selected

- 0 = Mass erase operation unselected

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Memory

- 6. Wait for a time, t<sub>PGS</sub>.

- 7. Write data to the FLASH address being programmed<sup>(1)</sup>.

- 8. Wait for time, t<sub>PROG</sub>.

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM bit (1).

- 11. Wait for time, t<sub>NVH</sub>.

- 12. Clear the HVEN bit.

- 13. After time, t<sub>RCV</sub>, the memory can be accessed in read mode again.

## **NOTE**

The COP register at location \$FFFF should not be written between steps 5-12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 16.15 Memory Characteristics.

## 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

## **NOTE**

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than \$FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF). The FLBPR itself can be erased or programmed only with an external voltage, V<sub>TST</sub>, present on the  $\overline{\text{IRQ}}$  pin. This voltage also allows entry from reset into the monitor mode.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

<sup>1.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

Memory

**Configuration Register (CONFIG)**

#### **Computer Operating Properly (COP)**

The COP counter is a free-running 6-bit counter preceded by the 12-bit system integration module (SIM) counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 BUSCLKX4 cycles; depending on the state of the COP rate select bit, COPRS, in configuration register 1. With a 262,128 BUSCLKX4 cycle overflow option, the internal 12.8-MHz oscillator gives a COP timeout period of 20.48 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the  $\overline{RST}$  pin low (if the RSTEN bit is set in the CONFIG1 register) for  $32 \times BUSCLKX4$  cycles and sets the COP bit in the reset status register (RSR). See 13.8.1 SIM Reset Status Register.

#### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

# 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

## 6.3.1 BUSCLKX4

BUSCLKX4 is the oscillator output signal. BUSCLKX4 frequency is equal to the crystal frequency or the RC-oscillator frequency.

## 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

## 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see Figure 6-2) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector.

#### 6.3.4 Power-On Reset

The power-on reset (POR) circuit in the SIM clears the SIM counter  $4096 \times BUSCLKX4$  cycles after power up.

## 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

# 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register (CONFIG). See Chapter 5 Configuration Register (CONFIG).

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

## **Central Processor Unit (CPU)**

# 7.7 Instruction Set Summary

Table 7-1 provides a summary of the M68HC08 instruction set.

Table 7-1. Instruction Set Summary (Sheet 1 of 6)

| Source                                                                                          | Operation                                            | Description                                              | Effect on CCR |   |   |          |    |   | Address<br>Mode                                                                              | Opcode                                           | Operand                                         | les                                  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------|---------------|---|---|----------|----|---|----------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            | - Political                                          |                                                          | ٧             | Н | I | N        | Z  | С | Add                                                                                          | Opc                                              | Ope                                             | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC, X<br>ADC opr,SP<br>ADC opr,SP  | Add with Carry                                       | A ← (A) + (M) + (C)                                      | 1             | ‡ | - | 1        | 1  | ţ | IMM DIR EXT IX2 IX1 IX SP1 SP2                                                               | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2 3 4 4 3 2 4 5                      |

| ADD #opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD opr,X<br>ADD opr,SP<br>ADD opr,SP          | Add without Carry                                    | $A \leftarrow (A) + (M)$                                 | 1             | Î | _ | 1        | Î  | Î | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| AIS #opr                                                                                        | Add Immediate Value (Signed) to SP                   | SP ← (SP) + (16 « M)                                     | -             | _ | _ | _        | _  | - | IMM                                                                                          | A7                                               | ii                                              | 2                                    |

| AIX #opr                                                                                        | Add Immediate Value (Signed) to H:X                  | H:X ← (H:X) + (16 « M)                                   | -             | _ | _ | _        | -  | _ | IMM                                                                                          | AF                                               | ii                                              | 2                                    |

| AND #opr<br>AND opr<br>AND opr,<br>AND opr,X<br>AND opr,X<br>AND, X<br>AND opr,SP<br>AND opr,SP | Logical AND                                          | A ← (A) & (M)                                            | 0             | _ | _ | ‡        | ‡  | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                    | Arithmetic Shift Left<br>(Same as LSL)               | © <b>→</b>                                               | 1             | _ | - | ‡        | Į. | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                 | Arithmetic Shift Right                               | b7 b0                                                    | ţ             | _ | ı | <b>‡</b> | ‡  | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| BCC rel                                                                                         | Branch if Carry Bit Clear                            | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                 | _             | _ | _ | _        | -  | - | REL                                                                                          | 24                                               | rr                                              | 3                                    |

| BCLR n, opr                                                                                     | Clear Bit n in M                                     | Mn ← 0                                                   | _             | _ | _ | _        | _  | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd    | 4<br>4<br>4<br>4<br>4<br>4           |

| BCS rel                                                                                         | Branch if Carry Bit Set (Same as BLO)                | PC ← (PC) + 2 + rel? (C) = 1                             | -             | - | - | _        | -  | - | REL                                                                                          | 25                                               | rr                                              | 3                                    |

| BEQ rel                                                                                         | Branch if Equal                                      | $PC \leftarrow (PC) + 2 + rel? (Z) = 1$                  | _             | _ | _ | _        | -  | _ | REL                                                                                          | 27                                               | rr                                              | 3                                    |

| BGE opr                                                                                         | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 0$         | _             | - | _ | _        | _  | _ | REL                                                                                          | 90                                               | rr                                              | 3                                    |

| BGT opr                                                                                         | Branch if Greater Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel?(Z) \mid (N \oplus V) = 0$ | _             | - | - | _        | -  | _ | REL                                                                                          | 92                                               | rr                                              | 3                                    |

| BHCC rel                                                                                        | Branch if Half Carry Bit Clear                       | $PC \leftarrow (PC) + 2 + rel? (H) = 0$                  | _             | _ | _ | _        | _  | _ | REL                                                                                          | 28                                               | rr                                              | 3                                    |

| BHCS rel                                                                                        | Branch if Half Carry Bit Set                         | PC ← (PC) + 2 + <i>rel</i> ? (H) = 1                     | <u> -</u>     | _ | _ | _        | _  | _ | REL                                                                                          | 29                                               | rr                                              | 3                                    |

| BHI rel                                                                                         | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + rel? (C) \mid (Z) = 0$         | -             | - | - | _        | -  | _ | REL                                                                                          | 22                                               | rr                                              | 3                                    |

#### **Keyboard Interrupt Module (KBI)**

Figure 9-1. Block Diagram Highlighting KBI Block and Pins

#### $9.3.1.1 \; MODEK = 1$

If the MODEK bit is set, the keyboard interrupt inputs are both edge and level sensitive. The KBIPx bit will determine whether a edge sensitive pin detects rising or falling edges and on level sensitive pins whether the pin detects low or high levels. With MODEK set, both of the following actions must occur to clear a keyboard interrupt request:

- Return of all enabled keyboard interrupt inputs to a deasserted level. As long as any enabled keyboard interrupt pin is asserted, the keyboard interrupt remains active.

- Vector fetch or software clear. A KBI vector fetch generates an interrupt acknowledge signal to clear the KBI latch. Software generates the interrupt acknowledge signal by writing a 1 to ACKK in KBSCR. The ACKK bit is useful in applications that poll the keyboard interrupt inputs and require software to clear the KBI latch. Writing to ACKK prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt inputs. An edge detect that occurs after writing to ACKK latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the CPU loads the program counter with the KBI vector address.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

**Keyboard Interrupt Module (KBI)**

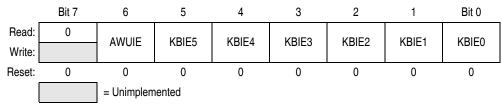

## 9.8.2 Keyboard Interrupt Enable Register (KBIER)

KBIER enables or disables each keyboard interrupt pin.

Figure 9-4. Keyboard Interrupt Enable Register (KBIER)

## KBIE5-KBIE0 — Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch KBI interrupt requests.

- 1 = KBIx pin enabled as keyboard interrupt pin

- 0 = KBIx pin not enabled as keyboard interrupt pin

#### NOTE

AWUIE bit is not used in conjunction with the keyboard interrupt feature. To see a description of this bit, see Chapter 4 Auto Wakeup Module (AWU).

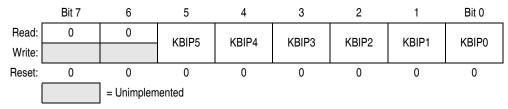

## 9.8.3 Keyboard Interrupt Polarity Register (KBIPR)

KBIPR determines the polarity of the enabled keyboard interrupt pin and enables the appropriate pullup or pulldown device.

Figure 9-5. Keyboard Interrupt Polarity Register (KBIPR)

#### KBIP5-KBIP0 — Keyboard Interrupt Polarity Bits

Each of these read/write bits enables the polarity of the keyboard interrupt detection.

- 1 = Keyboard polarity is high level and/or rising edge

- 0 = Keyboard polarity is low level and/or falling edge

Low-Voltage Inhibit (LVI)

## ECFS1:ECFS0 — External Crystal Frequency Select Bits

These read/write bits enable the specific amplifier for the crystal frequency range. Refer to oscillator characteristics table in the Electricals section for information on maximum external clock frequency versus supply voltage.

| ECFS1 | ECFS0 | External Crystal Frequency |

|-------|-------|----------------------------|

| 0     | 0     | 8 MHz – 32 MHz             |

| 0     | 1     | 1 MHz – 8 MHz              |

| 1     | 0     | 32 kHz – 100 kHz           |

| 1     | 1     | Reserved                   |

#### ECGON — External Clock Generator On Bit

This read/write bit enables the OSC1 pin as the clock input to the MCU, so that the switching process can be initiated. This bit is cleared by reset. This bit is ignored in monitor mode with the internal oscillator bypassed.

- 1 = External clock enabled

- 0 = External clock disabled

#### **ECGST** — External Clock Status Bit

This read-only bit indicates whether an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

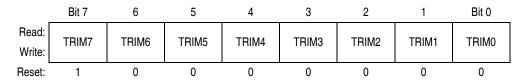

# 11.8.2 Oscillator Trim Register (OSCTRIM)

Figure 11-5. Oscillator Trim Register (OSCTRIM)

## TRIM7-TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the internal capacitance used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed oscillator period. The oscillator period is based on the oscillator frequency selected by the ICFS bits in OSCSC.

Applications using the internal oscillator should copy the internal oscillator trim value at location \$FFC0 or \$FFC1 into this register to trim the clock source.

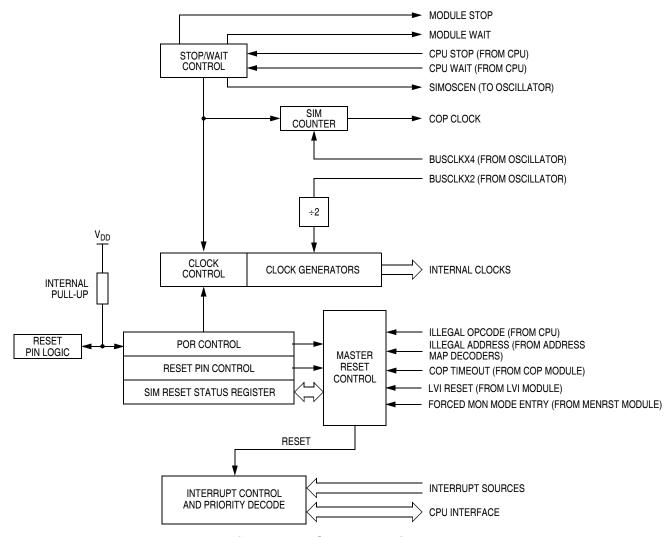

#### **System Integration Module (SIM)**

Figure 13-1. SIM Block Diagram

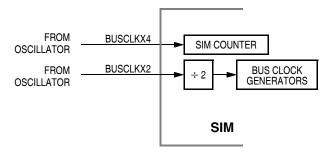

## 13.3 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 13-2.

Figure 13-2. SIM Clock Signals

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

#### **Timer Interface Module (TIM)**

channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

#### 14.3.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use the following initialization procedure:

- 1. In the TIM status and control register (TSC):

- a. Stop the counter by setting the TIM stop bit, TSTOP.

- b. Reset the counter and prescaler by setting the TIM reset bit, TRST.

- 2. In the TIM counter modulo registers (TMODH:TMODL), write the value for the required PWM period.

- 3. In the TIM channel x registers (TCHxH:TCHxL), write the value for the required pulse width.

- 4. In TIM channel x status and control register (TSCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB:MSxA. See Table 14-2.

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (polarity 1 to clear output on compare) or 1:1 (polarity 0 to set output on compare) to the edge/level select bits, ELSxB:ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 14-2.

## NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIM status control register (TSC), clear the TIM stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM status control register 0 (TSCR0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

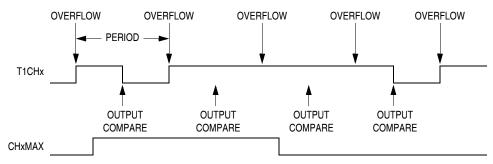

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 14.8.1 TIM Status and Control Register.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

## TOVx — Toggle-On-Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the counter overflows. When channel x is an input capture channel, TOVx has no effect.

- 1 = Channel x pin toggles on TIM counter overflow.

- 0 = Channel x pin does not toggle on TIM counter overflow.

#### NOTE

When TOVx is set, a counter overflow takes precedence over a channel x output compare if both occur at the same time.

## CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 14-11 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 14-11. CHxMAX Latency

# 14.8.5 TIM Channel Registers

These read/write registers contain the captured counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

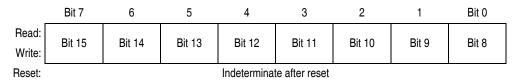

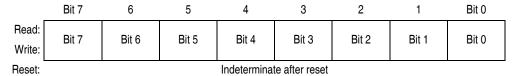

Figure 14-12. TIM Channel x Register High (TCHxH)

Figure 14-13. TIM Channel Register Low (TCHxL)

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

#### **Development Support**

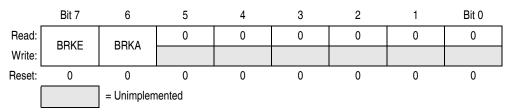

## 15.2.2.1 Break Status and Control Register

The break status and control register (BRKSCR) contains break module enable and status bits.

Figure 15-3. Break Status and Control Register (BRKSCR)

### **BRKE** — Break Enable Bit

This read/write bit enables breaks on break address register matches. Clear BRKE by writing a 0 to bit 7. Reset clears the BRKE bit.

- 1 = Breaks enabled on 16-bit address match

- 0 = Breaks disabled

#### **BRKA** — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a 1 to BRKA generates a break interrupt. Clear BRKA by writing a 0 to it before exiting the break routine. Reset clears the BRKA bit.

- 1 = Break address match

- 0 = No break address match

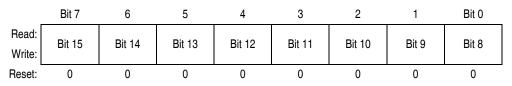

### 15.2.2.2 Break Address Registers

The break address registers (BRKH and BRKL) contain the high and low bytes of the desired breakpoint address. Reset clears the break address registers.

Figure 15-4. Break Address Register High (BRKH)

Figure 15-5. Break Address Register Low (BRKL)

#### **Development Support**

## 15.3.2 Security

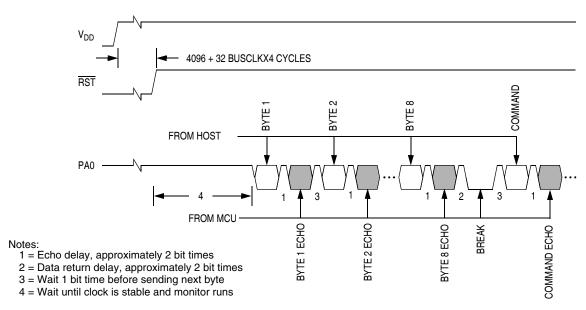

A security feature discourages unauthorized reading of FLASH locations while in monitor mode. The host can bypass the security feature at monitor mode entry by sending eight security bytes that match the bytes at locations \$FFF6\_\$FFFD. Locations \$FFF6\_\$FFFD contain user-defined data.

#### NOTE

Do not leave locations \$FFF6-\$FFFD blank. For security reasons, program locations \$FFF6-\$FFFD even if they are not used for vectors.

During monitor mode entry, the MCU waits after the power-on reset for the host to send the eight security bytes on pin PTA0. If the received bytes match those at locations \$FFF6—\$FFFD, the host bypasses the security feature and can read all FLASH locations and execute code from FLASH. Security remains bypassed until a power-on reset occurs. If the reset was not a power-on reset, security remains bypassed and security code entry is not required. See Figure 15-18.

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6—\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a FLASH location returns an invalid value and trying to execute code from FLASH causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

#### NOTE

The MCU does not transmit a break character until after the host sends the eight security bytes.

Figure 15-18. Monitor Mode Entry Timing

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$80 is set. If it is, then the correct security code has been entered and FLASH can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the FLASH module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

## **Ordering Information and Mechanical Specifications**

Case 1452 page 4 of 4

Case 648 page 3 of 3