Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | -                                                          |

| Peripherals                | LVD, POR, PWM                                              |

| Number of I/O              | 13                                                         |

| Program Memory Size        | 1.5KB (1.5K x 8)                                           |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 128 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                              |

| Supplier Device Package    | 8-SO                                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908qt1amdwe |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

General Description

# 1.4 Pin Assignments

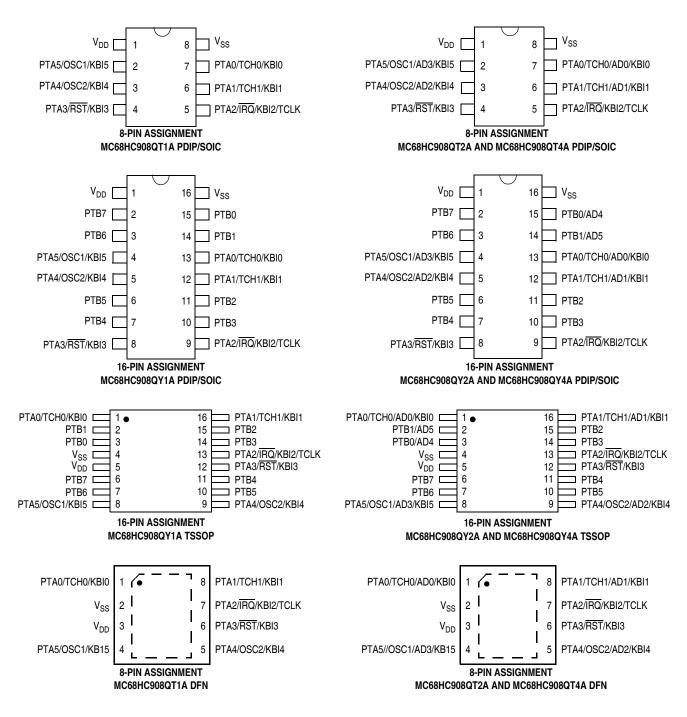

The MC68HC908QT4A, MC68H908QT2A, and MC68HC098QT1A are available in 8-pin packages. The MC68HC908QY4A, MC68HC908QY2A, and MC68HC908QY1A are available in 16-pin packages. Figure 1-2 shows the pin assignment for these packages.

Figure 1-2. MCU Pin Assignments

#### **Direct Page Registers**

| Addr.                         | Register Name                                     |                 | Bit 7   | 6                         | 5      | 4           | 3              | 2        | 1      | Bit 0  |  |  |

|-------------------------------|---------------------------------------------------|-----------------|---------|---------------------------|--------|-------------|----------------|----------|--------|--------|--|--|

|                               | TIM Channel 1 Status and                          | Read:           | CH1F    | CH1IE                     | 0      | MS1A        | ELS1B          | ELS1A    | TOV1   | CH1MAX |  |  |

| \$0028                        | Control Register (TSC1)                           | Write:          | 0       |                           |        |             |                |          |        | •••••  |  |  |

|                               | See page 135.                                     | Reset:<br>Read: | 0       | 0                         | 0      | 0           | 0              | 0        | 0      | 0      |  |  |

| \$0029                        | TIM Channel 1<br>\$0029 Register High (TCH1H)     |                 | Bit 15  | Bit 14                    | Bit 13 | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8  |  |  |

|                               | See page 137.                                     | Reset:          |         | Indeterminate after reset |        |             |                |          |        |        |  |  |

| \$002A                        | TIM Channel 1<br>Register Low (TCH1L)             | Read:<br>Write: | Bit 7   | Bit 6                     | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0  |  |  |

|                               | See page 137.                                     | Reset:          |         |                           |        | Indetermina | te after reset |          | •      |        |  |  |

| \$002B<br>↓<br>\$0035         | Reserved                                          |                 |         |                           |        |             |                |          |        |        |  |  |

| \$0036 Control Register (OSCS | Oscillator Status and<br>Control Register (OSCSC) | Read:<br>Write: | OSCOPT1 | OSCOPT0                   | ICFS1  | ICFS0       | ECFS1          | ECFS0    | ECGON  | ECGST  |  |  |

|                               | See page 100.                                     | Reset:          | 0       | 0                         | 1      | 0           | 0              | 0        | 0      | 0      |  |  |

| \$0037                        | Reserved                                          |                 |         |                           |        |             |                |          |        |        |  |  |

| \$0038                        | Oscillator Trim Register<br>(OSCTRIM)             | Read:<br>Write: | TRIM7   | TRIM6                     | TRIM5  | TRIM4       | TRIM3          | TRIM2    | TRIM1  | TRIM0  |  |  |

|                               | See page 101.                                     | Reset:          | 1       | 0                         | 0      | 0           | 0              | 0        | 0      | 0      |  |  |

| \$0039<br>↓<br>\$003B         | Reserved                                          |                 |         |                           |        |             |                |          |        |        |  |  |

| \$003C                        | ADC10 Status and Control<br>Register (ADSCR)      | Read:<br>Write: | COCO    | AIEN                      | ADCO   | ADCH4       | ADCH3          | ADCH2    | ADCH1  | ADCH0  |  |  |

|                               | See page 46.                                      | Reset:          | 0       | 0                         | 0      | 1           | 1              | 1        | 1      | 1      |  |  |

|                               | ADC10 Data Register High                          | Read:           | 0       | 0                         | 0      | 0           | 0              | 0        | AD9    | AD8    |  |  |

| \$003D                        | (ADRH)                                            | Write:          | R       | R                         | R      | R           | R              | R        | R      | R      |  |  |

|                               | See page 48.                                      | Reset:          | 0       | 0                         | 0      | 0           | 0              | 0        | 0      | 0      |  |  |

|                               | ADC10 Data Register Low                           | Read:           | AD7     | AD6                       | AD5    | AD4         | AD3            | AD2      | AD1    | AD0    |  |  |

| \$003E                        | (ADRL)<br>See page 48.                            | Write:          | R       | R                         | R      | R           | R              | R        | R      | R      |  |  |

|                               | See paye 40.                                      | Reset:          | 0       | 0                         | 0      | 0           | 0              | 0        | 0      | 0      |  |  |

| \$003F                        | ADC10 Clock Register<br>(ADCLK)                   | Read:<br>Write: | ADLPC   | ADIV1                     | ADIV0  | ADICLK      | MODE1          | MODE0    | ADLSMP | ACLKEN |  |  |

|                               | See page 48.                                      | Reset:          | 0       | 0                         | 0      | 0           | 0              | 0        | 0      | 0      |  |  |

|                               |                                                   |                 |         | = Unimplem                | ented  | R           | = Reserved     | U = Unaf | fected |        |  |  |

#### Analog-to-Digital Converter (ADC10) Module

charging. If externally available, connect the  $V_{\text{REFL}}$  pin to the same potential as  $V_{\text{SSA}}$  at the single point ground location.

## 3.7.5 ADC10 Channel Pins (ADn)

The ADC10 has multiple input channels. Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. 0.01  $\mu$ F capacitors with good high-frequency characteristics are sufficient. These capacitors are not necessary in all cases, but when used they must be placed as close as possible to the package pins and be referenced to V<sub>SSA</sub>.

# 3.8 Registers

These registers control and monitor operation of the ADC10:

- ADC10 status and control register, ADSCR

- ADC10 data registers, ADRH and ADRL

- ADC10 clock register, ADCLK

## 3.8.1 ADC10 Status and Control Register

This section describes the function of the ADC10 status and control register (ADSCR). Writing ADSCR aborts the current conversion and initiates a new conversion (if the ADCH[4:0] bits are equal to a value other than all 1s).

|                 | Bit 7 | 6    | 5    | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|------|------|-------|-------|-------|-------|-------|

| Read:<br>Write: | 0000  | AIEN | ADCO | ADCH4 | ADCH3 | ADCH2 | ADCH1 | ADCH0 |

| Reset:          | 0     | 0    | 0    | 1     | 1     | 1     | 1     | 1     |

#### Figure 3-3. ADC10 Status and Control Register (ADSCR)

#### COCO — Conversion Complete Bit

COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the status and control register is written or whenever the data register (low) is read.

- 1 = Conversion completed

- 0 = Conversion not completed

#### AIEN — ADC10 Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of a conversion. The interrupt signal is cleared when the data register is read or the status/control register is written.

1 = ADC10 interrupt enabled

0 = ADC10 interrupt disabled

#### ADCO — ADC10 Continuous Conversion Bit

When this bit is set, the ADC10 will begin to convert samples continuously (continuous conversion mode) and update the result registers at the end of each conversion, provided the ADCH[4:0] bits do not decode to all 1s. The ADC10 will continue to convert until the MCU enters reset, the MCU enters stop mode (if ACLKEN is clear), ADCLK is written, or until ADSCR is written again. If stop is entered (with ACLKEN low), continuous conversions will cease and can be restarted only with a write to ADSCR. Any write to ADSCR with ADCO set and the ADCH bits not all 1s will abort the current conversion and begin continuous conversions.

#### ADIV[1:0] — ADC10 Clock Divider Bits

ADIV1 and ADIV0 select the divide ratio used by the ADC10 to generate the internal clock ADCK. Table 3-3 shows the available clock configurations.

| ADIV1 | ADIV0 | Divide Ratio (ADIV) | Clock Rate      |

|-------|-------|---------------------|-----------------|

| 0     | 0     | 1                   | Input clock ÷ 1 |

| 0     | 1     | 2                   | Input clock ÷ 2 |

| 1     | 0     | 4                   | Input clock ÷ 4 |

| 1     | 1     | 8                   | Input clock ÷ 8 |

#### Table 3-3. ADC10 Clock Divide Ratio

## ADICLK — Input Clock Select Bit

If ACLKEN is clear, ADICLK selects either the bus clock or an alternate clock source as the input clock source to generate the internal clock ADCK. If the alternate clock source is less than the minimum clock speed, use the internally-generated bus clock as the clock source. As long as the internal clock ADCK, which is equal to the selected input clock divided by ADIV, is at a frequency (f<sub>ADCK</sub>) between the minimum and maximum clock speeds (considering ALPC), correct operation can be guaranteed.

1 = The internal bus clock is selected as the input clock source

0 = The alternate clock source IS SELECTED

#### MODE[1:0] — 10- or 8-Bit or Hardware Triggered Mode Selection

These bits select 10- or 8-bit operation. The successive approximation converter generates a result that is rounded to 8- or 10-bit value based on the mode selection. This rounding process sets the transfer function to transition at the midpoint between the ideal code voltages, causing a quantization error of  $\pm 1/2$ LSB.

Reset returns 8-bit mode.

00 = 8-bit, right-justified, ADSCR software triggered mode enabled

01 = 10-bit, right-justified, ADSCR software triggered mode enabled

10 = Reserved

11 = 10-bit, right-justified, hardware triggered mode enabled

#### ADLSMP — Long Sample Time Configuration

This bit configures the sample time of the ADC10 to either 3.5 or 23.5 ADCK clock cycles. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption in continuous conversion mode if high conversion rates are not required.

- 1 = Long sample time (23.5 cycles)

- 0 = Short sample time (3.5 cycles)

#### ACLKEN — Asynchronous Clock Source Enable

This bit enables the asynchronous clock source as the input clock to generate the internal clock ADCK, and allows operation in stop mode. The asynchronous clock source will operate between 1 MHz and 2 MHz if ADLPC is clear, and between 0.5 MHz and 1 MHz if ADLPC is set.

- 1 = The asynchronous clock is selected as the input clock source (the clock generator is only enabled during the conversion)

- 0 = ADICLK specifies the input clock source and conversions will not continue in stop mode

# Chapter 5 Configuration Register (CONFIG)

# 5.1 Introduction

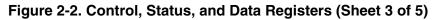

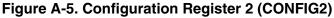

This section describes the configuration registers (CONFIG1 and CONFIG2). The configuration registers enable or disable the following options:

- Stop mode recovery time (32 × BUSCLKX4 cycles or 4096 × BUSCLKX4 cycles)

- STOP instruction

- Computer operating properly module (COP)

- COP reset period (COPRS): 8176 × BUSCLKX4 or 262,128 × BUSCLKX4

- Low-voltage inhibit (LVI) enable and trip voltage selection

- Auto wakeup timeout period

- Allow clock source to remain enabled in STOP

- Enable IRQ pin

- Disable IRQ pin pullup device

- Enable RST pin

# 5.2 Functional Description

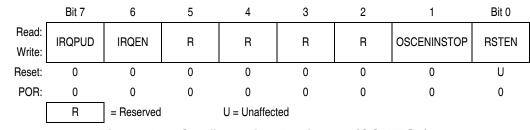

The configuration registers are used in the initialization of various options. The configuration registers can be written once after each reset. Most of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU) it is recommended that this register be written immediately after reset. The configuration registers are located at \$001E and \$001F, and may be read at anytime.

**NOTE** The CONFIG registers are one-time writable by the user after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in Figure 5-1 and Figure 5-2.

Figure 5-1. Configuration Register 2 (CONFIG2)

**Central Processor Unit (CPU)**

| Source                                                                                          | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   | ec<br>CC |   |    | Address<br>Mode                                     | Opcode                                           | Operand                                         | es                                   |

|-------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|----------|---|----|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            | operation                        | Becomption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | v | Н | I | Ν        | z | С  | Add<br>Mod                                          | Opc                                              | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR opr,X<br>CLR X<br>CLR opr,SP                | Clear                            | $\begin{array}{c} M \leftarrow \$00 \\ A \leftarrow \$00 \\ X \leftarrow \$00 \\ H \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \end{array}$                                                                                                                                                                                                                                                                                                                                           | 0 | _ | _ | 0        | 1 | _  | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F                 | dd<br>ff<br>ff                                  | 3<br>1<br>1<br>3<br>2<br>4           |

| CMP #opr<br>CMP opr<br>CMP opr,<br>CMP opr,X<br>CMP opr,X<br>CMP ,X<br>CMP opr,SP<br>CMP opr,SP | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t | _ | _ | ţ        | ţ | ţ  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>E1<br>F1<br>9EE1<br>9ED1       | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                    | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                                                                           | 0 | _ | _ | ţ        | ţ | 1  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

| CPHX #opr<br>CPHX opr                                                                           | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ţ | - | - | \$       | ţ | ţ  | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3<br>4                               |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX ,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ţ | _ | _ | ţ        | ţ | ţ  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| DAA                                                                                             | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U | - | - | 1        | 1 | \$ | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel       | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 4 + \mathit{rel} ? (\mathit{result}) \neq 0 \end{array}$ | _ | _ | _ | _        | _ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 5<br>3<br>3<br>5<br>4<br>6           |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                    | Decrement                        | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                   | ţ | - | _ | ţ        | ţ | -  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

| DIV                                                                                             | Divide                           | $A \leftarrow (H:A)/(X)$<br>H $\leftarrow$ Remainder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - | - | - | -        | t | ţ  | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR ,X<br>EOR opr,SP<br>EOR opr,SP  | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 | _ | _ | ţ        | ţ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                    | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                   | ţ | _ | _ | ţ        | ţ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

#### External Interrupt (IRQ)

# 8.4 Interrupts

The following IRQ source can generate interrupt requests:

• Interrupt flag (IRQF) — The IRQF bit is set when the IRQ pin is asserted based on the IRQ mode. The IRQ interrupt mask bit, IMASK, is used to enable or disable IRQ interrupt requests.

# 8.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 8.5.1 Wait Mode

The IRQ module remains active in wait mode. Clearing IMASK in INTSCR enables IRQ interrupt requests to bring the MCU out of wait mode.

## 8.5.2 Stop Mode

The IRQ module remains active in stop mode. Clearing IMASK in INTSCR enables IRQ interrupt requests to bring the MCU out of stop mode.

# 8.6 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

# 8.7 I/O Signals

The IRQ module does not share its pin with any module on this MCU.

## 8.7.1 IRQ Input Pins (IRQ)

The IRQ pin provides a maskable external interrupt source. The IRQ pin contains an internal pullup device.

Oscillator (OSC) Module

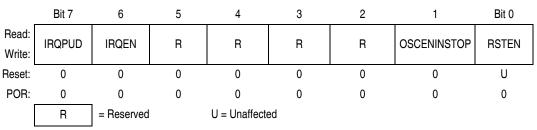

# 11.8 Registers

The oscillator module contains two registers:

- Oscillator status and control register (OSCSC)

- Oscillator trim register (OSCTRIM)

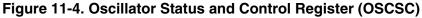

## 11.8.1 Oscillator Status and Control Register

The oscillator status and control register (OSCSC) contains the bits for switching between internal and external clock sources. If the application uses an external crystal, bits in this register are used to select the crystal oscillator amplifier necessary for the desired crystal. While running off the internal clock source, the user can use bits in this register to select the internal clock source frequency.

#### OSCOPT1:OSCOPT0 — OSC Option Bits

These read/write bits allow the user to change the clock source for the MCU. The default reset condition has the bus clock being derived from the internal oscillator. See 11.3.2.2 Internal to External Clock Switching for information on changing clock sources.

| OSCOPT1 | OSCOPT0 | Oscillator Modes                                          |

|---------|---------|-----------------------------------------------------------|

| 0       | 0       | Internal oscillator (frequency selected using ICFSx bits) |

| 0       | 1       | External oscillator clock                                 |

| 1       | 0       | External RC                                               |

| 1       | 1       | External crystal (range selected using ECFSx bits)        |

#### ICFS1:ICFS0 — Internal Clock Frequency Select Bits

These read/write bits enable the frequency to be increased for applications requiring a faster bus clock when running off the internal oscillator. The WAIT instruction has no effect on the oscillator logic. BUSCLKX2 and BUSCLKX4 continue to drive to the SIM module.

| ICFS1 | ICFS0 | Internal Clock Frequency           |

|-------|-------|------------------------------------|

| 0     | 0     | 4.0 MHz                            |

| 0     | 1     | 8.0 MHz                            |

| 1     | 0     | 12.8 MHz — default reset condition |

| 1     | 1     | Reserved                           |

**Oscillator (OSC) Module**

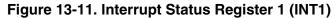

#### 13.6.2.1 Interrupt Status Register 1

|        | Bit 7 | 6          | 5   | 4   | 3   | 2   | 1 | Bit 0 |

|--------|-------|------------|-----|-----|-----|-----|---|-------|

| Read:  | IF6   | IF5        | IF4 | IF3 | IF2 | IF1 | 0 | 0     |

| Write: | R     | R          | R   | R   | R   | R   | R | R     |

| Reset: | 0     | 0          | 0   | 0   | 0   | 0   | 0 | 0     |

|        | R     | = Reserved |     |     |     |     |   |       |

#### IF1–IF6 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

1 = Interrupt request present

0 = No interrupt request present

#### Bit 0, 1 — Always read 0

#### 13.6.2.2 Interrupt Status Register 2

|        | Bit 7 | 6          | 5    | 4    | 3    | 2   | 1   | Bit 0 |

|--------|-------|------------|------|------|------|-----|-----|-------|

| Read:  | IF14  | IF13       | IF12 | IF11 | IF10 | IF9 | IF8 | IF7   |

| Write: | R     | R          | R    | R    | R    | R   | R   | R     |

| Reset: | 0     | 0          | 0    | 0    | 0    | 0   | 0   | 0     |

| [      | R     | = Reserved |      |      |      |     |     |       |

Figure 13-12. Interrupt Status Register 2 (INT2)

#### IF7–IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3.

1 = Interrupt request present

0 = No interrupt request present

#### 13.6.2.3 Interrupt Status Register 3

|        | Bit 7 | 6          | 5    | 4    | 3    | 2    | 1    | Bit 0 |  |  |  |

|--------|-------|------------|------|------|------|------|------|-------|--|--|--|

| Read:  | IF22  | IF21       | IF20 | IF19 | IF18 | IF17 | IF16 | IF15  |  |  |  |

| Write: | R     | R          | R    | R    | R    | R    | R    | R     |  |  |  |

| Reset: | 0     | 0          | 0    | 0    | 0    | 0    | 0    | 0     |  |  |  |

|        | R     | = Reserved |      |      |      |      |      |       |  |  |  |

|        |       |            |      |      |      |      |      |       |  |  |  |

#### Figure 13-13. Interrupt Status Register 3 (INT3)

#### IF15–IF22 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

1 = Interrupt request present

0 = No interrupt request present

Timer Interface Module (TIM)

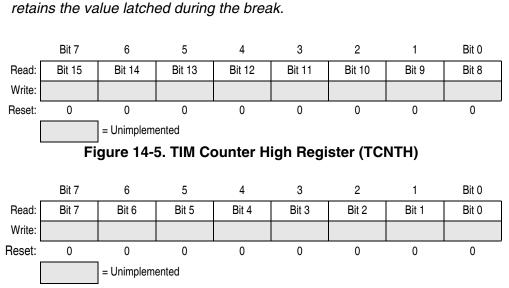

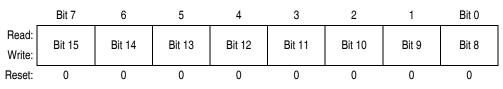

## 14.8.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

> **NOTE** If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL

## Figure 14-6. TIM Counter Low Register (TCNTL)

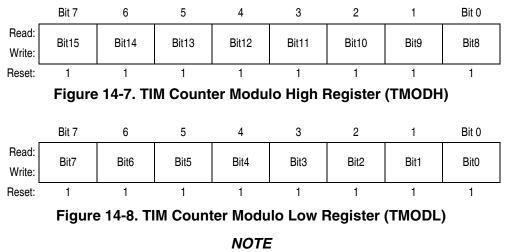

## 14.8.3 TIM Counter Modulo Registers

The read/write TIM modulo registers contain the modulo value for the counter. When the counter reaches the modulo value, the overflow flag (TOF) becomes set, and the counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIM counter modulo registers.

Reset the counter before writing to the TIM counter modulo registers.

#### TOVx — Toggle-On-Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the counter overflows. When channel x is an input capture channel, TOVx has no effect.

- 1 = Channel x pin toggles on TIM counter overflow.

- 0 = Channel x pin does not toggle on TIM counter overflow.

#### NOTE

When TOVx is set, a counter overflow takes precedence over a channel x output compare if both occur at the same time.

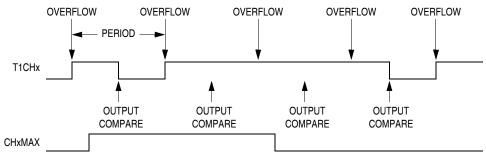

#### CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 14-11 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 14-11. CHxMAX Latency

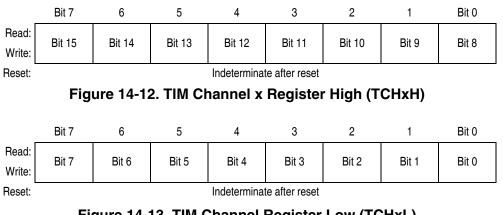

#### 14.8.5 TIM Channel Registers

These read/write registers contain the captured counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Development Support

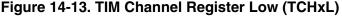

## 15.2.2.1 Break Status and Control Register

The break status and control register (BRKSCR) contains break module enable and status bits.

Figure 15-3. Break Status and Control Register (BRKSCR)

#### BRKE — Break Enable Bit

This read/write bit enables breaks on break address register matches. Clear BRKE by writing a 0 to bit 7. Reset clears the BRKE bit.

- 1 = Breaks enabled on 16-bit address match

- 0 = Breaks disabled

### BRKA — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a 1 to BRKA generates a break interrupt. Clear BRKA by writing a 0 to it before exiting the break routine. Reset clears the BRKA bit.

1 = Break address match

0 = No break address match

### 15.2.2.2 Break Address Registers

The break address registers (BRKH and BRKL) contain the high and low bytes of the desired breakpoint address. Reset clears the break address registers.

Figure 15-4. Break Address Register High (BRKH)

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Read:<br>Write: | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

Figure 15-5. Break Address Register Low (BRKL)

Development Support

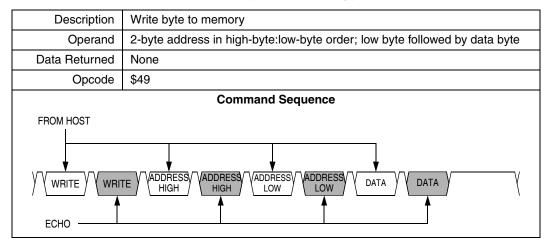

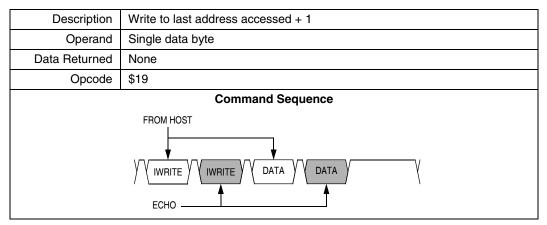

#### Table 15-4. WRITE (Write Memory) Command

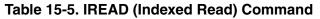

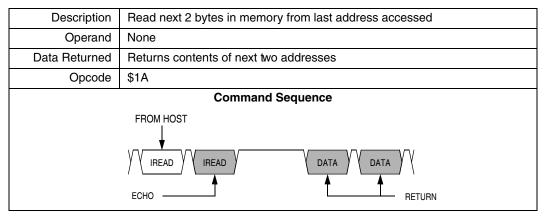

#### Table 15-6. IWRITE (Indexed Write) Command

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

#### **Electrical Specifications**

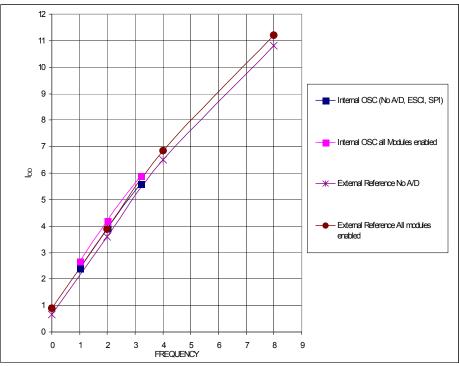

Figure 16-9. Typical 5-Volt Run Current versus Bus Frequency (25•C)

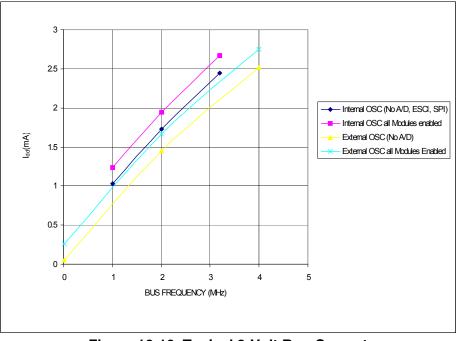

Figure 16-10. Typical 3-Volt Run Current versus Bus Frequency (25•C)

**Electrical Specifications**

# **16.15 Memory Characteristics**

| Characteristic                                      | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage (1)                      | V <sub>RDR</sub>                 | 1.3        | —      | _          | V      |

| FLASH program bus clock frequency                   | _                                | 1          | —      |            | MHz    |

| FLASH PGM/ERASE supply voltage (V <sub>DD</sub> )   | V <sub>PGM/ERASE</sub>           | 2.7        | —      | 5.5        | V      |

| FLASH read bus clock frequency                      | f <sub>Read</sub> <sup>(2)</sup> | 0          | _      | 8 M        | Hz     |

| FLASH page erase time<br><1 K cycles<br>>1 K cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                               | t <sub>MErase</sub>              | 4          | —      |            | ms     |

| FLASH PGM/ERASE to HVEN setup time                  | t <sub>NVS</sub>                 | 10         | —      | _          | μs     |

| FLASH high-voltage hold time                        | t <sub>NVH</sub>                 | 5          | —      |            | μs     |

| FLASH high-voltage hold time (mass erase)           | t <sub>NVHL</sub>                | 100        | —      | _          | μs     |

| FLASH program hold time                             | t <sub>PGS</sub>                 | 5          | —      | _          | μs     |

| FLASH program time                                  | t <sub>PROG</sub>                | 30         | —      | 40         | μs     |

| FLASH return to read time                           | t <sub>RCV</sub> <sup>(3)</sup>  | 1          | —      | _          | μs     |

| FLASH cumulative program hv period                  | t <sub>HV</sub> <sup>(4)</sup>   | —          | —      | 4          | ms     |

| FLASH endurance <sup>(5)</sup>                      | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(6)</sup>            | _                                | 15         | 100    | _          | Years  |

1. Values are based on characterization results, not tested in production.

2. f<sub>Read</sub> is defined as the frequency range for which the FLASH memory can be read.

3. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

4. t<sub>HV</sub> is defined as the cumulative high voltage programming time to the same row before next erase.

t<sub>HV</sub> must satisfy this condition: t<sub>NVS</sub> + t<sub>NVH</sub> + t<sub>PGS</sub> + (t<sub>PROG</sub> x 32) ≤ t<sub>HV</sub> maximum.

Typical endurance was evaluated for this product family. For additional information on how Freescale Semiconductor defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

6. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines Typical Data Retention, please refer to Engineering Bulletin EB618.

Ordering Information and Mechanical Specifications

Case 626 page 2 of 3

**Ordering Information and Mechanical Specifications**

Case 648 page 2 of 3

## A.2.3 Improved Auto Wakeup Module (AWU)

The QYxA contains an AWU that has improved accuracy across voltage and temperature for typical testing.

- A new feature provides ability to run the AWU from an alternate source (internal oscillator or external crystal). This is an advantage for an application that needs more accurate AWU operation.

- On the QYxA AWU approximate time out will be 16 ms for short time out and 512 ms for long time out when running from the internal 32-kHz RC source.

- Finally, at lower voltages typical measurements have shown lower power consumption by the QYxA AWU.

A.2.3.1 Registers Affected

Setting the OSCENINSTOP bit forces the AWU to use BUSCLKX2 as the source to this timeout.

## A.2.4 New Power-on Reset Module (POR)

The QYxA POR re-arm voltage will have a minimum specification of 0.7 V while the QYx Classic POR re-arm was 0.1 V. The higher POR re-arm voltage provides added protection against brown out conditions.

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007–2010. All rights reserved.

MC68HC908QY4A Rev. 3, 03/2010