Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 5                                                                      |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 8-SO                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qt2amdwer |

#### Memory

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

# **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

# 2.6.2 FLASH Page Erase Operation

Use the following procedure to erase a page of FLASH memory. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80, or \$XXC0. The user interrupt vector area resides in the \$FFC0–\$FFFF page. Any FLASH memory page can be erased alone.

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub>.

- 7. Clear the ERASE bit.

- 8. Wait for a time, t<sub>NVH</sub>.

- 9. Clear the HVEN bit.

- After time, t<sub>RCV</sub>, the memory can be accessed in read mode again.

### NOTE

The COP register at location \$FFFF should not be written between steps 5-9, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, other unrelated operations may occur between the steps.

### **CAUTION**

A page erase of the vector page will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

Analog-to-Digital Converter (ADC10) Module

# **AWUIE** — Auto Wakeup Interrupt Enable Bit

This read/write bit enables the auto wakeup interrupt input to latch interrupt requests. Reset clears AWUIE.

- 1 = Auto wakeup enabled as interrupt input

- 0 = Auto wakeup not enabled as interrupt input

#### NOTE

KBIE5–KBIE0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 9.8.2 Keyboard Interrupt Enable Register (KBIER).

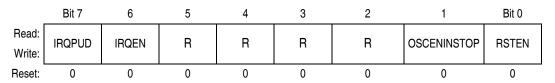

# 4.6.4 Configuration Register 2

The configuration register 2 (CONFIG2), is used to allow the bus clock source to run in STOP. In this case, the clock, BUSCLKX2 will be used to drive the AWU request generator.

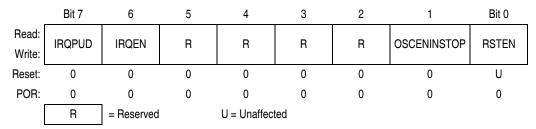

Figure 4-5. Configuration Register 2 (CONFIG2)

# OSCENINSTOP — Oscillator Enable in Stop Mode Bit

OSCENINSTOP, when set, will allow the bus clock source (BUSCLKX2) to generate clocks for the AWU in stop mode. See 11.8.1 Oscillator Status and Control Register for information on enabling the external clock sources.

- 1 = Oscillator enabled to operate during stop mode

- 0 = Oscillator disabled during stop mode

### NOTE

IRQPUD, IRQEN, and RSTEN bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see Chapter 5 Configuration Register (CONFIG).

# 4.6.5 Configuration Register 1

The configuration register 1 (CONFIG1), is used to select the period for the AWU. The timeout will be based on the COPRS bit along with the clock source for the AWU.

Figure 4-6. Configuration Register 1 (CONFIG1)

**Configuration Register (CONFIG)**

# Table 7-1. Instruction Set Summary (Sheet 2 of 6)

| Source                                                                                                | Operation                                         | Description                                                                                                                                                                                                                                                                                                                                   |   |   | Effect<br>on CCR |   |   |   | Address<br>Mode                                                                              | Opcode                                           | Operand                                                              | les                             |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------------------|---|---|---|----------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------|---------------------------------|

| Form                                                                                                  | Operation                                         | Becomplien                                                                                                                                                                                                                                                                                                                                    | ٧ | Н | I                | N | Z | С | Add<br>Mod                                                                                   | Орс                                              | Ope                                                                  | Cycles                          |

| BHS rel                                                                                               | Branch if Higher or Same (Same as BCC)            | $PC \leftarrow (PC) + 2 + rel? (C) = 0$                                                                                                                                                                                                                                                                                                       | _ | - | -                | - | _ | - | REL                                                                                          | 24                                               | rr                                                                   | 3                               |

| BIH rel                                                                                               | Branch if IRQ Pin High                            | PC ← (PC) + 2 + <i>rel</i> ? IRQ = 1                                                                                                                                                                                                                                                                                                          | _ | - | _                | - | _ | _ | REL                                                                                          | 2F                                               | rr                                                                   | 3                               |

| BIL rel                                                                                               | Branch if IRQ Pin Low                             | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 0$                                                                                                                                                                                                                                                                                           | _ | - | -                | - | - | _ | REL                                                                                          | 2E                                               | rr                                                                   | 3                               |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT,X<br>BIT opr,SP<br>BIT opr,SP         | Bit Test                                          | (A) & (M)                                                                                                                                                                                                                                                                                                                                     | 0 | _ | 1                | 1 | ‡ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9EE5<br>9ED5 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff                      | 23443245                        |

| BLE opr                                                                                               | Branch if Less Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (Z)   (N \oplus V) = 1$                                                                                                                                                                                                                                                                                        | _ | - | -                | - | - | - | REL                                                                                          | 93                                               | rr                                                                   | 3                               |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                     | $PC \leftarrow (PC) + 2 + rel? (C) = 1$                                                                                                                                                                                                                                                                                                       | _ | - | _                | - | _ | _ | REL                                                                                          | 25                                               | rr                                                                   | 3                               |

| BLS rel                                                                                               | Branch if Lower or Same                           | $PC \leftarrow (PC) + 2 + rel? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                              | _ | - | _                | - | - | - | REL                                                                                          | 23                                               | rr                                                                   | 3                               |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                              | - | - | -                | - | - | _ | REL                                                                                          | 91                                               | rr                                                                   | 3                               |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                    | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                       | _ | - | -                | - | - | - | REL                                                                                          | 2C                                               | rr                                                                   | 3                               |

| BMI rel                                                                                               | Branch if Minus                                   | PC ← (PC) + 2 + rel? (N) = 1                                                                                                                                                                                                                                                                                                                  | _ | - | -                | - | - | - | REL                                                                                          | 2B                                               | rr                                                                   | 3                               |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                      | PC ← (PC) + 2 + <i>rel</i> ? (I) = 1                                                                                                                                                                                                                                                                                                          | _ | - | _                | - | _ | _ | REL                                                                                          | 2D                                               | rr                                                                   | 3                               |

| BNE rel                                                                                               | Branch if Not Equal                               | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                       | _ | - | _                | - | _ | _ | REL                                                                                          | 26                                               | rr                                                                   | 3                               |

| BPL rel                                                                                               | Branch if Plus                                    | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                       | _ | - | -                | - | - | - | REL                                                                                          | 2A                                               | rr                                                                   | 3                               |

| BRA rel                                                                                               | Branch Always                                     | PC ← (PC) + 2 + <i>rel</i>                                                                                                                                                                                                                                                                                                                    | _ | - | -                | - | - | _ | REL                                                                                          | 20                                               | rr                                                                   | 3                               |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                 | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                         | _ | _ | _                | _ | - | 1 | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555                        |

| BRN rel                                                                                               | Branch Never                                      | PC ← (PC) + 2                                                                                                                                                                                                                                                                                                                                 | _ | _ | _                | _ | _ | _ | REL                                                                                          | 21                                               | rr                                                                   | 3                               |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                   | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                         | _ | _ | ı                | _ | ı | ‡ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555                        |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                             | Mn ← 1                                                                                                                                                                                                                                                                                                                                        | _ | _ | _                | _ | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                         | 4<br>4<br>4<br>4<br>4<br>4<br>4 |

| BSR rel                                                                                               | Branch to Subroutine                              | $\begin{array}{c} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                                    | _ | - | -                | _ | - | _ | REL                                                                                          | AD                                               | rr                                                                   | 4                               |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                       | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel~?~(A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel~?~(A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel~?~(X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel~?~(A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel~?~(A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel~?~(A) - (M) = \$00 \end{array}$ | _ | _ | -                | _ | - | _ | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 31<br>41<br>51<br>61<br>71<br>9E61               | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                      | 5<br>4<br>4<br>5<br>4<br>6      |

| CLC                                                                                                   | Clear Carry Bit                                   | C ← 0                                                                                                                                                                                                                                                                                                                                         | _ | _ | _                | _ | _ | 0 | INH                                                                                          | 98                                               |                                                                      | 1                               |

| CLI                                                                                                   | Clear Interrupt Mask                              | I ← 0                                                                                                                                                                                                                                                                                                                                         | _ | - | 0                | _ | _ | _ | INH                                                                                          | 9A                                               |                                                                      | 2                               |

# Table 7-1. Instruction Set Summary (Sheet 6 of 6)

| Source                                                       | Operation                             | Description                                                                                                                                                                                                                                                                                                                                                                  |                                                  | Effect<br>on CCR |   |          |     |     |                                       | Address<br>Mode                    | Opcode         | Operand | es |

|--------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|---|----------|-----|-----|---------------------------------------|------------------------------------|----------------|---------|----|

| Form                                                         | operation.                            | Boompton                                                                                                                                                                                                                                                                                                                                                                     | on CCR V H I N Z O  1  1 1 1 1 1 1 1 1 1 1 1 1 1 |                  |   | С        | Add | Opc | Ope                                   | Cycles                             |                |         |    |

| SWI                                                          | Software Interrupt                    | $\begin{array}{c} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  I \leftarrow 1 \\ PCH \leftarrow Interrupt  Vector  High  Byte \\ PCL \leftarrow Interrupt  Vector  Low  Byte \\ \end{array}$ | _                                                | _                | 1 | _        | _   | _   | INH                                   | 83                                 |                | 9       |    |

| TAP                                                          | Transfer A to CCR                     | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                    | 1                                                | 1                | ‡ | ‡        | 1   | 1   | INH                                   | 84                                 |                | 2       |    |

| TAX                                                          | Transfer A to X                       | X ← (A)                                                                                                                                                                                                                                                                                                                                                                      | -                                                | -                | _ | -        | -   | -   | INH                                   | 97                                 |                | 1       |    |

| TPA                                                          | Transfer CCR to A                     | $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                         | -                                                | -                | _ | -        | -   | -   | INH                                   | 85                                 |                | 1       |    |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP | Test for Negative or Zero             | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                       | 0                                                | _                | _ | <b>‡</b> | 1   | ı   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D | dd<br>ff<br>ff | 311324  |    |

| TSX                                                          | Transfer SP to H:X                    | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                               | -                                                | -                | - | -        | -   | -   | INH                                   | 95                                 |                | 2       |    |

| TXA                                                          | Transfer X to A                       | A ← (X)                                                                                                                                                                                                                                                                                                                                                                      | -                                                | -                | _ | -        | -   | -   | INH                                   | 9F                                 |                | 1       |    |

| TXS                                                          | Transfer H:X to SP                    | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                             | -                                                | -                | _ | _        | _   | -   | INH                                   | 94                                 |                | 2       |    |

| WAIT                                                         | Enable Interrupts; Wait for Interrupt | I bit ← 0; Inhibit CPU clocking until interrupted                                                                                                                                                                                                                                                                                                                            | -                                                | -                | 0 | -        | -   | _   | INH                                   | 8F                                 |                | 1       |    |

| Α     | Accumulator                                                         | n               | Any bit                                     |

|-------|---------------------------------------------------------------------|-----------------|---------------------------------------------|

| С     | Carry/borrow bit                                                    | opr             | Operand (one or two bytes)                  |

| CCR   | Condition code register                                             | PC              | Program counter                             |

| dd    | Direct address of operand                                           | PCH             | Program counter high byte                   |

| dd rr | Direct address of operand and relative offset of branch instruction | PCL             | Program counter low byte                    |

| DD    | Direct to direct addressing mode                                    | REL             | Relative addressing mode                    |

| DIR   | Direct addressing mode                                              | rel             | Relative program counter offset byte        |

| DIX+  | Direct to indexed with post increment addressing mode               | rr              | Relative program counter offset byte        |

| ee ff | High and low bytes of offset in indexed, 16-bit offset addressing   | SP1             | Stack pointer, 8-bit offset addressing mode |

| EXT   | Extended addressing mode                                            | SP2             | Stack pointer 16-bit offset addressing mode |

| ff    | Offset byte in indexed, 8-bit offset addressing                     | SP              | Stack pointer                               |

| Н     | Half-carry bit                                                      | U               | Undefined                                   |

| Н     | Index register high byte                                            | V               | Overflow bit                                |

| hh II | High and low bytes of operand address in extended addressing        | Χ               | Index register low byte                     |

| I     | Interrupt mask                                                      | Z               | Zero bit                                    |

| ii    | Immediate operand byte                                              | &               | Logical AND                                 |

| IMD   | Immediate source to direct destination addressing mode              | 1               | Logical OR                                  |

| IMM   | Immediate addressing mode                                           | $\oplus$        | Logical EXCLUSIVE OR                        |

| INH   | Inherent addressing mode                                            | ()              | Contents of                                 |

| IX    | Indexed, no offset addressing mode                                  | <del>-</del> () | Negation (two's complement)                 |

| IX+   | Indexed, no offset, post increment addressing mode                  | #`´             | Immediate value                             |

| IX+D  | Indexed with post increment to direct addressing mode               | **              | Sign extend                                 |

| IX1   | Indexed, 8-bit offset addressing mode                               | $\leftarrow$    | Loaded with                                 |

| IX1+  | Indexed, 8-bit offset, post increment addressing mode               | ?               | If                                          |

| IX2   | Indexed, 16-bit offset addressing mode                              | :               | Concatenated with                           |

| M     | Memory location                                                     | ‡               | Set or cleared                              |

| N     | Negative bit                                                        | _               | Not affected                                |

|       |                                                                     |                 |                                             |

# 7.8 Opcode Map

See Table 7-2.

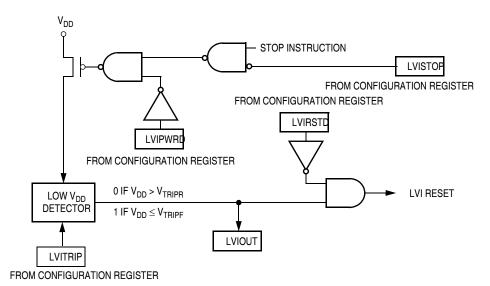

# Chapter 10 Low-Voltage Inhibit (LVI)

# 10.1 Introduction

The low-voltage inhibit (LVI) module is provided as a system protection mechanism to prevent the MCU from operating below a certain operating supply voltage level. The module has several configuration options to allow functionality to be tailored to different system level demands.

The configuration registers (see Chapter 5 Configuration Register (CONFIG)) contain control bits for this module.

# 10.2 Features

Features of the LVI module include:

- Programmable LVI reset

- Selectable LVI trip voltage

- Programmable stop mode operation

# 10.3 Functional Description

Figure 10-1 shows the structure of the LVI module. LVISTOP, LVIPWRD, LVITRIP, and LVIRSTD are user selectable options found in the configuration register.

Figure 10-1. LVI Module Block Diagram

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

Input/Output Ports (PORTS)

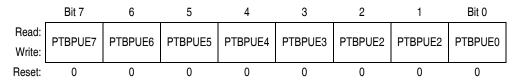

# 12.4.3 Port B Input Pullup Enable Register

The port B input pullup enable register (PTBPUE) contains a software configurable pullup device for each of the eight port B pins. Each bit is individually configurable and requires the corresponding data direction register, DDRBx, be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRBx bit is configured as output.

Figure 12-8. Port B Input Pullup Enable Register (PTBPUE)

### PTBPUE[7:0] — Port B Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port B pins

- 1 = Corresponding port B pin configured to have internal pull if its DDRB bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port B pin regardless of the state of its DDRB bit.

# 12.4.4 Port B Summary Table

**PTB**

Bit

$X^{(1)}$

Χ

Table 12-2 summarizes the operation of the port A pins when used as a general-purpose input/output pins.

| I/O Pin                    | Accesses to DDRB | A    | ccesses to PTB           |

|----------------------------|------------------|------|--------------------------|

| Mode                       | Read/Write       | Read | Write                    |

| Input, Hi-Z <sup>(2)</sup> | DDRB7-DDRB0      | Pin  | PTB7-PTB0 <sup>(3)</sup> |

Pin

PTB7-PTB0

**Table 12-2. Port B Pin Functions**

DDRB7-DDRB0

1. X = don't care

DDRB Bit

0

1

- 2. Hi-Z = high impedance

- 3. Writing affects data register, but does not affect the input.

Output

In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset (or break in emulation mode). A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the break status register (BSR). If the COP disable bit, COPD, in the configuration register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

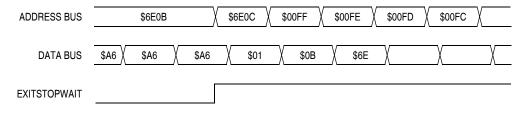

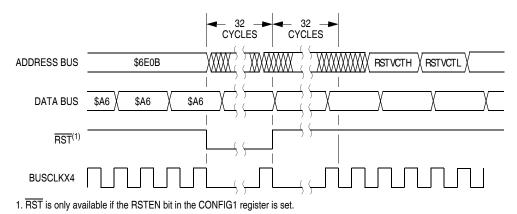

Figure 13-15 and Figure 13-16 show the timing for wait recovery.

NOTE: EXITSTOPWAIT =  $\overline{RST}$  pin OR CPU interrupt

Figure 13-15. Wait Recovery from Interrupt

Figure 13-16. Wait Recovery from Internal Reset

# **13.7.2 Stop Mode**

In stop mode, the SIM counter is reset and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset or break also causes an exit from stop mode.

The SIM disables the oscillator signals (BUSCLKX2 and BUSCLKX4) in stop mode, stopping the CPU and peripherals. If OSCENINSTOP is set, BUSCLKX2 will remain running in STOP and can be used to run the AWU. Stop recovery time is selectable using the SSREC bit in the configuration register 1 (CONFIG1). If SSREC is set, stop recovery is reduced from the normal delay of 4096 BUSCLKX4 cycles down to 32. This is ideal for the internal oscillator, RC oscillator, and external oscillator options which do not require long start-up times from stop mode.

### NOTE

External crystal applications should use the full stop recovery time by clearing the SSREC bit.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

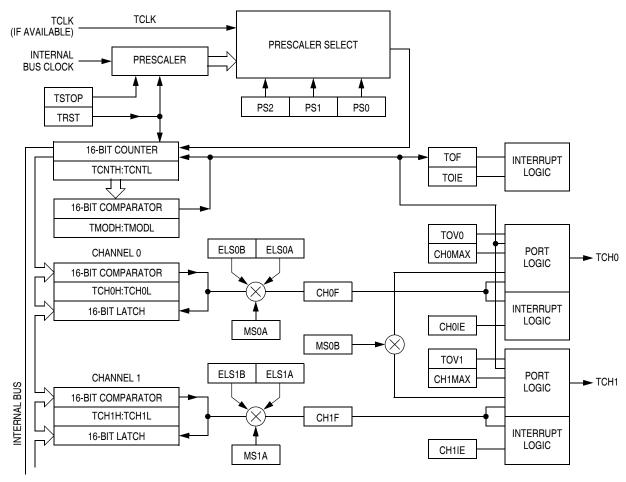

Figure 14-2. TIM Block Diagram

### 14.3.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 14.3.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new

value in the output compare interrupt routine. The output compare interrupt occurs at the end of

the current output compare pulse. The interrupt routine has until the end of the counter overflow

period to write the new value.

- When changing to a larger output compare value, enable TIM overflow interrupts and write the new

value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the

current counter overflow period. Writing a larger value in an output compare interrupt routine (at

**Timer Interface Module (TIM)**

# 14.7 I/O Signals

The TIM module can share its pins with the general-purpose I/O pins. See Figure 14-1 for the port pins that are shared.

# 14.7.1 TIM Channel I/O Pins (TCH1:TCH0)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. TCH0 can be configured as buffered output compare or buffered PWM pin.

# 14.7.2 TIM Clock Pin (TCLK)

TCLK is an external clock input that can be the clock source for the counter instead of the prescaled internal bus clock. Select the TCLK input by writing 1s to the three prescaler select bits, PS[2:0]. 14.8.1 TIM Status and Control Register The minimum TCLK pulse width is specified in the Timer Interface Module Characteristics table in the Electricals section. The maximum TCLK frequency is the least of 4 MHz or bus frequency ÷ 2.

# 14.8 Registers

The following registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM control registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

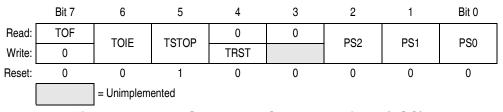

# 14.8.1 TIM Status and Control Register

The TIM status and control register (TSC) does the following:

- Enables TIM overflow interrupts

- Flags TIM overflows

- · Stops the counter

- · Resets the counter

- Prescales the counter clock

Figure 14-4. TIM Status and Control Register (TSC)

### **TOF** — TIM Overflow Flag Bit

This read/write flag is set when the counter reaches the modulo value programmed in the TIM counter modulo registers. Clear TOF by reading the TSC register when TOF is set and then writing a 0 to TOF.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

#### **Timer Interface Module (TIM)**

Setting MS0B causes the contents of TSC1 to be ignored by the TIM and reverts TCH1 to general-purpose I/O.

- 1 = Buffered output compare/PWM operation enabled

- 0 = Buffered output compare/PWM operation disabled

### MSxA — Mode Select Bit A

When ELSxB:A  $\neq$  00, this read/write bit selects either input capture operation or unbuffered output compare/PWM operation. See Table 14-2.

- 1 = Unbuffered output compare/PWM operation

- 0 = Input capture operation

When ELSxB:A = 00, this read/write bit selects the initial output level of the TCHx pin (see Table 14-2).

- 1 = Initial output level low

- 0 = Initial output level high

### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

# ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to an I/O port, and pin TCHx is available as a general-purpose I/O pin. Table 14-2 shows how ELSxB and ELSxA work.

| MSxB | MSxA | ELSxB | ELSxA | Mode            | Configuration                                     |

|------|------|-------|-------|-----------------|---------------------------------------------------|

| Х    | 0    | 0     | 0     | Output proof    | Pin under port control; initial output level high |

| Х    | 1    | 0     | 0     | Output preset   | Pin under port control; initial output level low  |

| 0    | 0    | 0     | 1     |                 | Capture on rising edge only                       |

| 0    | 0    | 1     | 0     | Input capture   | Capture on falling edge only                      |

| 0    | 0    | 1     | 1     |                 | Capture on rising or falling edge                 |

| 0    | 1    | 0     | 0     |                 | Software compare only                             |

| 0    | 1    | 0     | 1     | Output compare  | Toggle output on compare                          |

| 0    | 1    | 1     | 0     | or PWM          | Clear output on compare                           |

| 0    | 1    | 1     | 1     |                 | Set output on compare                             |

| 1    | Х    | 0     | 1     | Buffered output | Toggle output on compare                          |

| 1    | Х    | 1     | 0     | compare or      | Clear output on compare                           |

| 1    | Х    | 1     | 1     | buffered PWM    | Set output on compare                             |

Table 14-2. Mode, Edge, and Level Selection

### NOTE

After initially enabling a TIM channel register for input capture operation and selecting the edge sensitivity, clear CHxF to ignore any erroneous edge detection flags.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

# TOVx — Toggle-On-Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the counter overflows. When channel x is an input capture channel, TOVx has no effect.

- 1 = Channel x pin toggles on TIM counter overflow.

- 0 = Channel x pin does not toggle on TIM counter overflow.

#### NOTE

When TOVx is set, a counter overflow takes precedence over a channel x output compare if both occur at the same time.

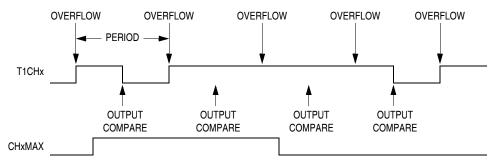

# CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 14-11 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 14-11. CHxMAX Latency

# 14.8.5 TIM Channel Registers

These read/write registers contain the captured counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

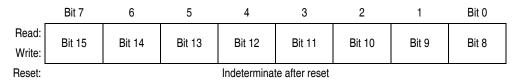

Figure 14-12. TIM Channel x Register High (TCHxH)

Figure 14-13. TIM Channel Register Low (TCHxL)

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

### NOTE

If the reset vector is blank and monitor mode is entered, the chip will see an additional reset cycle after the initial power-on reset (POR). Once the reset vector has been programmed, the traditional method of applying a voltage,  $V_{TST}$ , to  $\overline{IRQ}$  must be used to enter monitor mode.

If monitor mode was entered as a result of the reset vector being blank, the COP is always disabled regardless of the state of  $\overline{IRQ}$ .

If the voltage applied to the  $\overline{IRQ}$  is less than  $V_{TST}$ , the MCU will come out of reset in user mode. Internal circuitry monitors the reset vector fetches and will assert an internal reset if it detects that the reset vectors are erased (\$FF). When the MCU comes out of reset, it is forced into monitor mode without requiring high voltage on the  $\overline{IRQ}$  pin. Once out of reset, the monitor code is initially executing with the internal clock at its default frequency.

If  $\overline{\text{IRQ}}$  is held high, all pins will default to regular input port functions except for PTA0 and PTA5 which will operate as a serial communication port and OSC1 input respectively (refer to Figure 15-11). That will allow the clock to be driven from an external source through OSC1 pin.

If IRQ is held low, all pins will default to regular input port function except for PTA0 which will operate as serial communication port. Refer to Figure 15-12.

Regardless of the state of the  $\overline{IRQ}$  pin, it will not function as a port input pin in monitor mode. Bit 2 of the Port A data register will always read 0. The BIH and BIL instructions will behave as if the  $\overline{IRQ}$  pin is enabled, regardless of the settings in the configuration register. See Chapter 5 Configuration Register (CONFIG).

The COP module is disabled in forced monitor mode. Any reset other than a power-on reset (POR) will automatically force the MCU to come back to the forced monitor mode.

### 15.3.1.3 Monitor Vectors

In monitor mode, the MCU uses different vectors for reset, SWI (software interrupt), and break interrupt than those for user mode. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

### NOTE

Exiting monitor mode after it has been initiated by having a blank reset vector requires a power-on reset (POR). Pulling RST (when RST pin available) low will not exit monitor mode in this situation.

Table 15-2 summarizes the differences between user mode and monitor mode regarding vectors.

|         | Functions            |                     |                      |                     |                    |                   |  |  |  |

|---------|----------------------|---------------------|----------------------|---------------------|--------------------|-------------------|--|--|--|

| Modes   | Reset<br>Vector High | Reset<br>Vector Low | Break<br>Vector High | Break<br>Vector Low | SWI<br>Vector High | SWI<br>Vector Low |  |  |  |

| User    | \$FFFE               | \$FFFF              | \$FFFC               | \$FFFD              | \$FFFC             | \$FFFD            |  |  |  |

| Monitor | \$FEFE               | \$FEFF              | \$FEFC               | \$FEFD              | \$FEFC             | \$FEFD            |  |  |  |

**Table 15-2. Mode Difference**

# **Development Support**

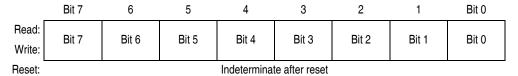

# Table 15-4. WRITE (Write Memory) Command

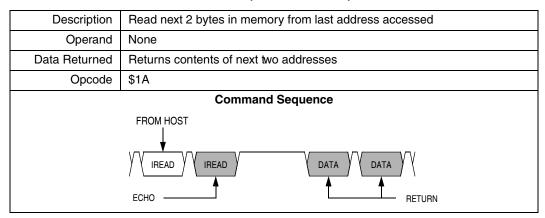

Table 15-5. IREAD (Indexed Read) Command

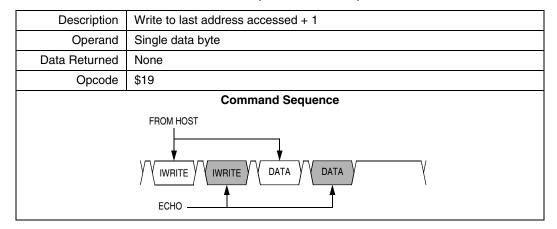

Table 15-6. IWRITE (Indexed Write) Command

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

### MC68HC908QYA/QTA Family Data Sheet, Rev. 3

# 16.5 5-V DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                        | Symbol              | Min                                                                  | Typ <sup>(2)</sup> | Max                   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------|--------------------|-----------------------|------|

| Output high voltage  I <sub>Load</sub> = -2.0 mA, all I/O pins  I <sub>Load</sub> = -10.0 mA, all I/O pins  I <sub>Load</sub> = -15.0 mA, PTA0, PTA1, PTA3-PTA5 only | V <sub>OH</sub>     | V <sub>DD</sub> -0.4<br>V <sub>DD</sub> -1.5<br>V <sub>DD</sub> -0.8 | _<br>_<br>_        | _<br>_<br>_           | V    |

| Maximum combined I <sub>OH</sub> (all I/O pins)                                                                                                                      | I <sub>OHT</sub>    | _                                                                    | _                  | 50                    | mA   |

| Output low voltage  I <sub>Load</sub> = 1.6 mA, all I/O pins  I <sub>Load</sub> = 10.0 mA, all I/O pins  I <sub>Load</sub> = 15.0 mA, PTA0, PTA1, PTA3—PTA5 only     | V <sub>OL</sub>     | _<br>_<br>_                                                          | _<br>_<br>_        | 0.4<br>1.5<br>0.8     | V    |

| Maximum combined I <sub>OL</sub> (all I/O pins)                                                                                                                      | I <sub>OHL</sub>    | _                                                                    | _                  | 50                    | mA   |

| Input high voltage<br>PTA0-PTA5, PTB0-PTB7                                                                                                                           | V <sub>IH</sub>     | 0.7 x V <sub>DD</sub>                                                |                    | V <sub>DD</sub>       | ٧    |

| Input low voltage PTA0-PTA5, PTB0-PTB7                                                                                                                               | V <sub>IL</sub>     | V <sub>SS</sub>                                                      | _                  | 0.3 x V <sub>DD</sub> | V    |

| Input hysteresis <sup>(3)</sup>                                                                                                                                      | V <sub>HYS</sub>    | 0.06 x V <sub>DD</sub>                                               | _                  | _                     | V    |

| DC injection current, all ports <sup>(4)</sup>                                                                                                                       | I <sub>INJ</sub>    | -2                                                                   | _                  | +2                    | mA   |

| Total dc current injection (sum of all I/O) <sup>(4)</sup>                                                                                                           | I <sub>INJTOT</sub> | -25                                                                  | _                  | +25                   | mA   |

| Ports Hi-Z leakage current                                                                                                                                           | I <sub>IL</sub>     | -1                                                                   | ±0.1               | +1                    | μА   |

| Capacitance Ports (as input) <sup>(3)</sup>                                                                                                                          | C <sub>IN</sub>     | _                                                                    |                    | 8                     | pF   |

| POR rearm voltage                                                                                                                                                    | V <sub>POR</sub>    | 750                                                                  | _                  | _                     | mV   |

| POR rise time ramp rate <sup>(3)(5)</sup>                                                                                                                            | R <sub>POR</sub>    | 0.035                                                                | _                  | _                     | V/ms |

| Monitor mode entry voltage (3)                                                                                                                                       | V <sub>TST</sub>    | V <sub>DD + 2.5</sub>                                                | _                  | 9.1                   | V    |

| Pullup resistors <sup>(6)</sup> PTA0–PTA5, PTB0–PTB7                                                                                                                 | R <sub>PU</sub>     | 16                                                                   | 26                 | 36                    | kΩ   |

| Pulldown resistors <sup>(7)</sup><br>PTA0–PTA5                                                                                                                       | R <sub>PD</sub>     | 16                                                                   | 26                 | 36                    | kΩ   |

| Low-voltage inhibit reset, trip falling voltage                                                                                                                      | V <sub>TRIPF</sub>  | 3.90                                                                 | 4.20               | 4.50                  | V    |

| Low-voltage inhibit reset, trip rising voltage                                                                                                                       | V <sub>TRIPR</sub>  | 4.00                                                                 | 4.30               | 4.60                  | V    |

| Low-voltage inhibit reset/recover hysteresis                                                                                                                         | V <sub>HYS</sub>    | _                                                                    | 100                | _                     | mV   |

- 1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted. 2. Typical values reflect average measurements at midpoint of voltage range, 25•C only.

- 3. Values are based on characterization results, not tested in production.

- Guaranteed by design, not tested in production.

If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, the LVI will hold the part in reset until minimum V<sub>DD</sub> is reached.

R<sub>PU</sub> is measured at V<sub>DD</sub> = 5.0 V.

R<sub>PD</sub> is measured at V<sub>DD</sub> = 5.0 V, Pulldown resistors only available when KBIx is enabled with KBIxPOL =1.

### **Electrical Specifications**

| Characteristic                       | Conditions  | Symbol          | Min  | Typ <sup>(1)</sup> | Max  | Unit | Comment                    |

|--------------------------------------|-------------|-----------------|------|--------------------|------|------|----------------------------|

| Integral pen linearity               | 10-bit mode | INL             | 0    | ±0.5               | _    | LSB  |                            |

| Integral non-linearity               | 8-bit mode  | IINL            | 0    | ±0.3               | _    | LOD  |                            |

| Zero-scale error                     | 10-bit mode | E <sub>ZS</sub> | 0    | ±0.5               | _    | LSB  | $V_{ADIN} = V_{SS}$        |

| Zero-scale error                     | 8-bit mode  | ∟ZS             | 0    | ±0.3               | _    | LOD  | VADIN - VSS                |

| Full-scale error                     | 10-bit mode | E <sub>FS</sub> | 0    | ±0.5               | _    | LSB  | $V_{ADIN} = V_{DD}$        |

| Full-Scale error                     | 8-bit mode  | -FS             | 0    | ±0.3               | 1    | LOD  | VADIN - VDD                |

| Quantization error                   | 10-bit mode | EQ              |      |                    | ±0.5 | LSB  | 8-bit mode is              |

| Quantization enoi                    | 8-bit mode  | <u>-</u> Q      | 1    | _                  | ±0.5 | LOD  | not truncated              |

| Input leakage error                  | 10-bit mode | E <sub>IL</sub> | 0    | ±0.2               | ±5   | LSB  | Pad leakage <sup>(5)</sup> |

| iliput leakage elloi                 | 8-bit mode  | <u> </u>        | 0    | ±0.1               | ±1.2 | LOD  | * R <sub>AS</sub>          |

| Bandgap voltage input <sup>(6)</sup> |             | $V_{BG}$        | 1.17 | 1.245              | 1.32 | V    |                            |

- Typical values assume V<sub>DD</sub> = 5.0 V, temperature = 25•C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

Incremental I<sub>DD</sub> added to MCU mode current.

- 3. Values are based on characterization results, not tested in production.

- 4. Reference the ADC module specification for more information on calculating conversion times.

- 5. Based on typical input pad leakage current.

- 6. LVI must be enabled, (LVIPWRD = 0, in CONFIG1). Voltage input to ADCH4:0 = \$1A, an ADC conversion on this channel allows user to determine supply voltage.

Case 1452 page 3 of 4

# A.2.3 Improved Auto Wakeup Module (AWU)

The QYxA contains an AWU that has improved accuracy across voltage and temperature for typical testing.

- A new feature provides ability to run the AWU from an alternate source (internal oscillator or external crystal). This is an advantage for an application that needs more accurate AWU operation.

- On the QYxA AWU approximate time out will be 16 ms for short time out and 512 ms for long time out when running from the internal 32-kHz RC source.

- Finally, at lower voltages typical measurements have shown lower power consumption by the QYxA AWU.

# A.2.3.1 Registers Affected

Figure A-5. Configuration Register 2 (CONFIG2)

Setting the OSCENINSTOP bit forces the AWU to use BUSCLKX2 as the source to this timeout.

# A.2.4 New Power-on Reset Module (POR)

The QYxA POR re-arm voltage will have a minimum specification of 0.7 V while the QYx Classic POR re-arm was 0.1 V. The higher POR re-arm voltage provides added protection against brown out conditions.