Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 5                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 8-SO                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qt4acdwer |

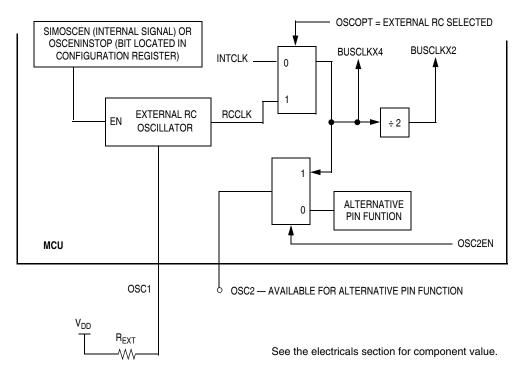

# Chapter 11 Oscillator (OSC) Module

| 11.1    | Introduction                            | 93   |

|---------|-----------------------------------------|------|

| 11.2    | Features                                | . 93 |

| 11.3    | Functional Description                  | . 93 |

| 11.3.1  | Internal Signal Definitions             |      |

| 11.3.1. |                                         |      |

| 11.3.1. |                                         |      |

| 11.3.1. | 3 RC Oscillator Clock (RCCLK)           | . 95 |

| 11.3.1. | 4 Internal Oscillator Clock (INTCLK)    | . 95 |

| 11.3.1. | 5 Bus Clock Times 4 (BUSCLKX4)          | . 95 |

| 11.3.1. |                                         |      |

| 11.3.2  | Internal Oscillator                     |      |

| 11.3.2. | 3 · · · · · · · · · · · · · · · · · · · |      |

| 11.3.2. | 3                                       |      |

| 11.3.2. | $oldsymbol{arphi}$                      |      |

| 11.3.3  | External Oscillator                     |      |

| 11.3.4  | XTAL Oscillator                         |      |

| 11.3.5  | RC Oscillator                           |      |

| 11.4    | Interrupts                              | . 98 |

| 11.5    | Low-Power Modes                         | . 98 |

| 11.5.1  | Wait Mode                               |      |

| 11.5.2  | Stop Mode                               | . 98 |

| 11.6    | OSC During Break Interrupts             | . 99 |

| 11.7    | I/O Signals                             | . 99 |

| 11.7.1  | Oscillator Input Pin (OSC1)             | . 99 |

| 11.7.2  | Oscillator Output Pin (OSC2)            | . 99 |

| 11.8    | Registers                               | 100  |

| 11.8.1  | Oscillator Status and Control Register  | 100  |

| 11.8.2  | Oscillator Trim Register (OSCTRIM)      | 101  |

|         | Observation 40                          |      |

|         | Chapter 12                              |      |

|         | Input/Output Ports (PORTS)              |      |

| 12.1    | Introduction                            |      |

| 12.2    | Unused Pin Termination                  | 103  |

| 12.3    | Port A                                  | 103  |

| 12.3.1  | Port A Data Register                    | 104  |

| 12.3.2  | Data Direction Register A               |      |

| 12.3.3  | Port A Input Pullup Enable Register     |      |

| 12.3.4  | Port A Summary Table                    |      |

| 12.4    | Port B                                  |      |

| 12.4.1  | Port B Data Register                    | 106  |

| 12.4.2  | Data Direction Register B               |      |

| 12.4.3  | Port B Input Pullup Enable Register     |      |

| 12.4.4  | Port B Summary Table                    | 108  |

| Output Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unbuffered Output Compare                                                                                                                                                                                                                                                                                                                                                                                                                                       | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Buffered Output Compare                                                                                                                                                                                                                                                                                                                                                                                                                                         | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pulse Width Modulation (PWM)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Unbuffered PWM Signal Generation                                                                                                                                                                                                                                                                                                                                                                                                                                | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I During Break Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                       | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

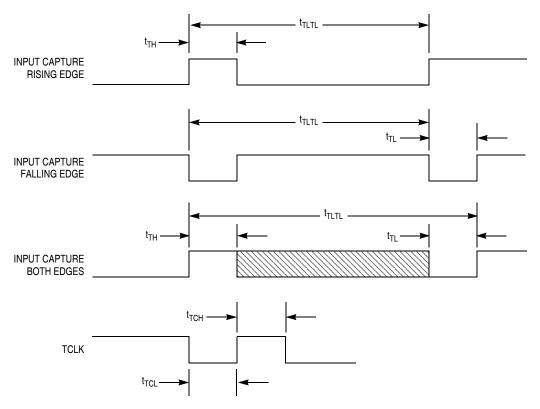

| TIM Channel I/O Pins (TCH1:TCH0)                                                                                                                                                                                                                                                                                                                                                                                                                                | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TIM Clock Pin (TCLK)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

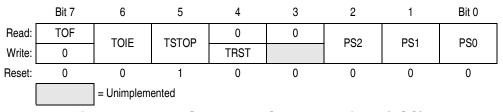

| nisters                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| This charmer registers                                                                                                                                                                                                                                                                                                                                                                                                                                          | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 15                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Development Support                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Development Support                                                                                                                                                                                                                                                                                                                                                                                                                                             | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

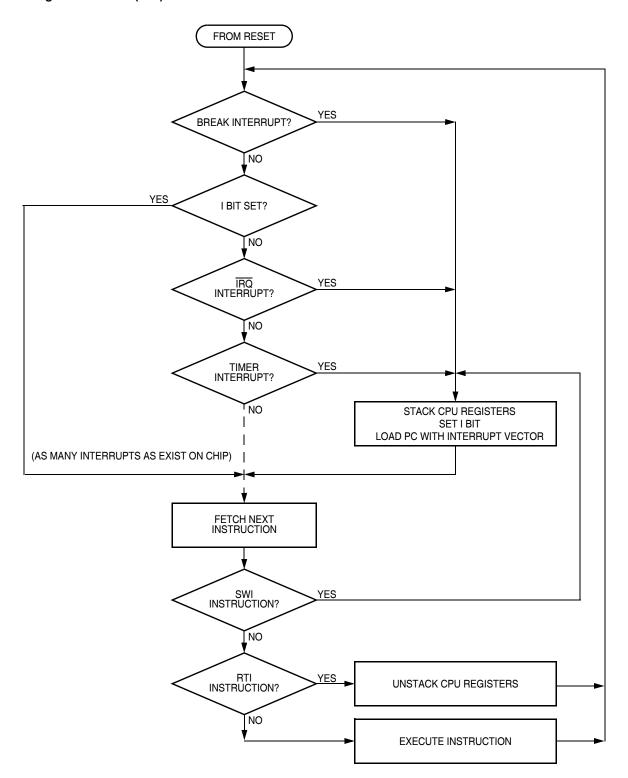

| oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 139<br>139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 139<br>139<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| oduction  ak Module (BRK)  Functional Description  Flag Protection During Break Interrupts  TIM During Break Interrupts                                                                                                                                                                                                                                                                                                                                         | 139<br>139<br>141<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts                                                                                                                                                                                                                                                                                                                 | 139<br>139<br>141<br>141<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

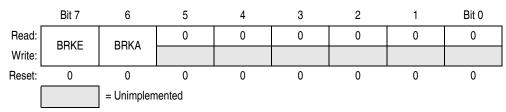

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers                                                                                                                                                                                                                                                                                          | 139<br>139<br>141<br>141<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register                                                                                                                                                                                                                                                                 | 139<br>139<br>141<br>141<br>141<br>142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

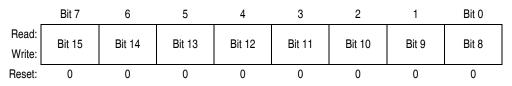

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers                                                                                                                                                                                                                                         | 139<br>141<br>141<br>141<br>141<br>142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register                                                                                                                                                                                                                | 139<br>139<br>141<br>141<br>141<br>142<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register                                                                                                                                                                                          | 139<br>141<br>141<br>141<br>142<br>142<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register                                                                                                                                        | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register                                                                                                                                                                                          | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register                                                                                                                                        | 139<br>141<br>141<br>141<br>142<br>143<br>143<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register Low-Power Modes                                                                                                                        | 139<br>141<br>141<br>141<br>142<br>143<br>143<br>144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON)                                                                                                                           | 139<br>139<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description                                                                                                    | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Flag Control Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode                                           | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers. Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode Forced Monitor Mode                                     | 139<br>139<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>148<br>148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode Forced Monitor Mode Monitor Vectors                      | 139<br>139<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>148<br>148<br>150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode Forced Monitor Mode Monitor Vectors Data Format | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>148<br>1148<br>1150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Flag Control Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode Forced Monitor Mode Monitor Vectors Data Format Break Signal    | 139<br>139<br>141<br>141<br>141<br>142<br>143<br>144<br>144<br>148<br>148<br>150<br>150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Unbuffered Output Compare Buffered Output Compare Pulse Width Modulation (PWM) Unbuffered PWM Signal Generation Buffered PWM Signal Generation PWM Initialization errupts errupts V-Power Modes Wait Mode Stop Mode I During Break Interrupts. Signals TIM Channel I/O Pins (TCH1:TCH0) TIM Clock Pin (TCLK) gisters TIM Status and Control Register TIM Counter Registers TIM Counter Registers TIM Counter Modulo Registers TIM Channel Status and Control Registers TIM Channel Status and Control Registers TIM Channel Registers |

# **Chapter 1 General Description**

## 1.1 Introduction

The MC68HC908QY4A is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

**FLASH** Pin Device ADC **Memory Size** Count 1536 bytes MC68HC908QT1A 8 pins MC68HC908QT2A 1536 bytes 6 channel, 10 bit 8 pins MC68HC908QT4A 6 channel, 10 bit 4096 bytes 8 pins MC68HC908QY1A 1536 bytes 16 pins MC68HC908QY2A 1536 bytes 6 channel, 10 bit 16 pins MC68HC908QY4A 4096 bytes 6 channel, 10 bit 16 pins

**Table 1-1. Summary of Device Variations**

## 1.2 Features

#### Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

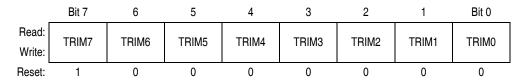

- Trimmable internal oscillator

- Software selectable 1 MHz, 2 MHz, or 3.2 MHz internal bus operation

- 8-bit trim capability

- ±25% untrimmed

- Trimmable to approximately 0.4%<sup>(1)</sup>

- Software selectable crystal oscillator range, 32–100 kHz, 1–8 MHz and 8–32 MHz

- Software configurable input clock from either internal or external source

- Auto wakeup from STOP capability using dedicated internal 32-kHz RC or bus clock source

- On-chip in-application programmable FLASH memory

- Internal program/erase voltage generation

- Monitor ROM containing user callable program/erase routines

- FLASH security<sup>(2)</sup>

<sup>1.</sup> See 16.11 Oscillator Characteristics for internal oscillator specifications

<sup>2.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

# 2.6 FLASH Memory (FLASH)

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire monitor mode interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths.

This subsection describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from the internal  $V_{DD}$  supply. The program and erase operations are enabled through the use of an internal charge pump.

The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section.

#### NOTE

An erased bit reads as a 1 and a programmed bit reads as a 0. A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

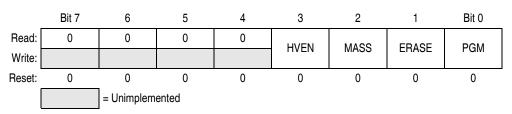

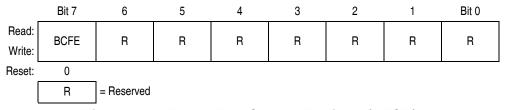

# 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

#### **HVEN** — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM =1 or ERASE =1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation.

- 1 = Mass erase operation selected

- 0 = Mass erase operation unselected

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

# Central Processor Unit (CPU)

# Table 7-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation Description            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |   | Effect<br>on CCR |          |   |    |                                                     | Opcode                                           |                                           | les                                  |

|------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|------------------|----------|---|----|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| Form                                                                                           | оролино                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | Н | I                | Ν        | Z | С  | Add                                                 | Opc                                              | Ope                                       | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                           | Clear                            | $\begin{array}{l} M \leftarrow \$00 \\ A \leftarrow \$00 \\ X \leftarrow \$00 \\ X \leftarrow \$00 \\ H \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \end{array}$                                                                                                                                                                                                                                                                                                                                          | 0  | _ | ı                | 0        | 1 | _  | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff<br>ff                            | 3<br>1<br>1<br>3<br>2<br>4           |

| CMP #opr<br>CMP opr<br>CMP opr,<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ţ  | _ |                  | <b>‡</b> | ‡ | 1  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = SFF - (M) \\ A \leftarrow (\overline{A}) = SFF - (M) \\ X \leftarrow (\overline{X}) = SFF - (M) \\ M \leftarrow (\overline{M}) = SFF - (M) \end{array}$                                                                                                                                                                                                                          | 0  | _ | - 1              | 1        | ‡ | 1  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) - (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ţ  | - | _                | ‡        | ‡ | ‡  | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                             | 3                                    |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX ,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  | _ | _                | ‡        | 1 | Į. | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 |                                           | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U  | - | -                | 1        | 1 | 1  | INH                                                 | 72                                               |                                           | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A)-1 \text{ or } M \leftarrow (M)-1 \text{ or } X \leftarrow (X)-1 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+4+\mathit{rel}? \text{ (result)} \neq 0 \end{array}$ | _  | _ | ı                | -        | ı | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr | 533546                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{l} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                       | Į. | _ | -                | <b>1</b> | 1 | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                            | Divide                           | $A \leftarrow (H:A)/(X)$<br>$H \leftarrow Remainder$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _  | - | -                | -        | ‡ | ‡  | INH                                                 | 52                                               |                                           | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0  | _ | ı                | ‡        | ‡ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $M \leftarrow (M) + 1$<br>$A \leftarrow (A) + 1$<br>$X \leftarrow (X) + 1$<br>$M \leftarrow (M) + 1$<br>$M \leftarrow (M) + 1$<br>$M \leftarrow (M) + 1$                                                                                                                                                                                                                                                                                                                                                                                                          | Î  | _ | -                | 1        | ‡ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

81

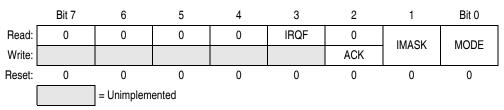

# 8.8 Registers

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. The INTSCR:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks the IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

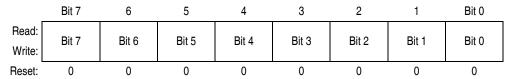

Figure 8-3. IRQ Status and Control Register (INTSCR)

# IRQF — IRQ Flag Bit

This read-only status bit is set when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- $0 = \overline{IRQ}$  interrupt not pending

# ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads 0.

## IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables the IRQ interrupt request.

- 1 = IRQ interrupt request disabled

- 0 = IRQ interrupt request enabled

#### MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin.

- $1 = \overline{IRQ}$  interrupt request on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt request on falling edges only

**Keyboard Interrupt Module (KBI)**

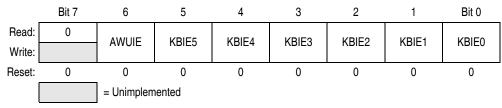

# 9.8.2 Keyboard Interrupt Enable Register (KBIER)

KBIER enables or disables each keyboard interrupt pin.

Figure 9-4. Keyboard Interrupt Enable Register (KBIER)

## KBIE5-KBIE0 — Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch KBI interrupt requests.

- 1 = KBIx pin enabled as keyboard interrupt pin

- 0 = KBIx pin not enabled as keyboard interrupt pin

#### NOTE

AWUIE bit is not used in conjunction with the keyboard interrupt feature. To see a description of this bit, see Chapter 4 Auto Wakeup Module (AWU).

## 9.8.3 Keyboard Interrupt Polarity Register (KBIPR)

KBIPR determines the polarity of the enabled keyboard interrupt pin and enables the appropriate pullup or pulldown device.

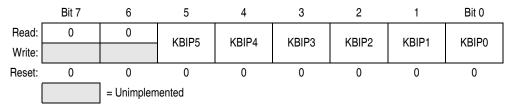

Figure 9-5. Keyboard Interrupt Polarity Register (KBIPR)

#### KBIP5-KBIP0 — Keyboard Interrupt Polarity Bits

Each of these read/write bits enables the polarity of the keyboard interrupt detection.

- 1 = Keyboard polarity is high level and/or rising edge

- 0 = Keyboard polarity is low level and/or falling edge

# 10.4 LVI Interrupts

The LVI module does not generate interrupt requests.

## 10.5 Low-Power Modes

The STOP and WAIT instructions put the MCU in low power-consumption standby modes.

#### 10.5.1 Wait Mode