Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 13                                                                    |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | - ·                                                                   |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 16-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qy1acdwe |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC908QY4A MC68HC908QY2A MC68HC908QY1A

# MC68HC908QT4A MC68HC908QT2A MC68HC908QT1A

Data Sheet

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2007–2010. All rights reserved.

#### Memory

- 6. Wait for a time, t<sub>PGS</sub>.

- 7. Write data to the FLASH address being  $programmed^{(1)}$ .

- 8. Wait for time, t<sub>PROG</sub>.

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM bit <sup>(1)</sup>.

- 11. Wait for time, t<sub>NVH</sub>.

- 12. Clear the HVEN bit.

- 13. After time, t<sub>RCV</sub>, the memory can be accessed in read mode again.

#### NOTE

The COP register at location \$FFFF should not be written between steps 5-12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed t<sub>PROG</sub> maximum, see 16.15 Memory Characteristics.

## 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

#### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal FF). The FLBPR itself can be erased or programmed only with an external voltage,  $V_{TST}$ , present on the IRQ pin. This voltage also allows entry from reset into the monitor mode.

<sup>1.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

**Functional Description**

Upon reset or when a conversion is otherwise aborted, the ADC10 module will enter a low power, inactive state. In this state, all internal clocks and references are disabled. This state is entered asynchronously and immediately upon aborting of a conversion.

#### 3.3.3.4 Total Conversion Time

The total conversion time depends on many factors such as sample time, bus frequency, whether ACLKEN is set, and synchronization time. The total conversion time is summarized in Table 3-1.

| Conversion Mode                                  | ACLKEN | Maximum Conversion Time      |

|--------------------------------------------------|--------|------------------------------|

| 8-Bit Mode (short sample — ADLSMP = 0):          |        |                              |

| Single or 1st continuous                         | 0      | 18 ADCK + 3 bus clock        |

| Single or 1st continuous                         | 1      | 18 ADCK + 3 bus clock + 5 μs |

| Subsequent continuous $(f_{Bus} \ge f_{ADCK})$   | Х      | 16 ADCK                      |

| 8-Bit Mode (long sample — ADLSMP = 1):           |        |                              |

| Single or 1st continuous                         | 0      | 38 ADCK + 3 bus clock        |

| Single or 1st continuous                         | 1      | 38 ADCK + 3 bus clock + 5 μs |

| Subsequent continuous ( $f_{Bus} \ge f_{ADCK}$ ) | Х      | 36 ADCK                      |

| 10-Bit Mode (short sample — ADLSMP = 0):         |        |                              |

| Single or 1st continuous                         | 0      | 21 ADCK + 3 bus clock        |

| Single or 1st continuous                         | 1      | 21 ADCK + 3 bus clock + 5 μs |

| Subsequent continuous ( $f_{Bus} \ge f_{ADCK}$ ) | Х      | 19 ADCK                      |

| 10-Bit Mode (long sample — ADLSMP = 1):          |        |                              |

| Single or 1st continuous                         | 0      | 41 ADCK + 3 bus clock        |

| Single or 1st continuous                         | 1      | 41 ADCK + 3 bus clock + 5 μs |

| Subsequent continuous $(f_{Bus} \ge f_{ADCK})$   | Х      | 39 ADCK                      |

Table 3-1. Total Conversion Time versus Control Conditions

The maximum total conversion time for a single conversion or the first conversion in continuous conversion mode is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by the ADICLK and ACLKEN bits, and the divide ratio is specified by the ADIV bits. For example, if the alternate clock source is 16 MHz and is selected as the input clock source, the input clock divide-by-8 ratio is selected and the bus frequency is 4 MHz, then the conversion time for a single 10-bit conversion is:

Maximum Conversion time =  $\frac{21 \text{ ADCK cycles}}{16 \text{ MHz/8}} + \frac{3 \text{ bus cycles}}{4 \text{ MHz}} = 11.25 \,\mu\text{s}$

Number of bus cycles = 11.25  $\mu$ s x 4 MHz = 45 cycles

NOTE

The ADCK frequency must be between  $f_{ADCK}$  minimum and  $f_{ADCK}$  maximum to meet A/D specifications.

#### Analog-to-Digital Converter (ADC10) Module

# 3.4 Interrupts

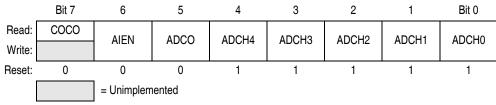

When AIEN is set, the ADC10 is capable of generating a CPU interrupt after each conversion. A CPU interrupt is generated when the conversion completes (indicated by COCO being set). COCO will set at the end of a conversion regardless of the state of AIEN.

## 3.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 3.5.1 Wait Mode

The ADC10 will continue the conversion process and will generate an interrupt following a conversion if AIEN is set. If the ADC10 is not required to bring the MCU out of wait mode, ensure that the ADC10 is not in continuous conversion mode by clearing ADCO in the ADC10 status and control register before executing the WAIT instruction. In single conversion mode the ADC10 automatically enters a low-power state when the conversion is complete. It is not necessary to set the channel select bits (ADCH[4:0]) to all 1s to enter a low power state.

## 3.5.2 Stop Mode

If ACLKEN is clear, executing a STOP instruction will abort the current conversion and place the ADC10 in a low-power state. Upon return from stop mode, a write to ADSCR is required to resume conversions, and the result stored in ADRH and ADRL will represent the last completed conversion until the new conversion completes.

If ACLKEN is set, the ADC10 continues normal operation during stop mode. The ADC10 will continue the conversion process and will generate an interrupt following a conversion if AIEN is set. If the ADC10 is not required to bring the MCU out of stop mode, ensure that the ADC10 is not in continuous conversion mode by clearing ADCO in the ADC10 status and control register before executing the STOP instruction. In single conversion mode the ADC10 automatically enters a low-power state when the conversion is complete. It is not necessary to set the channel select bits (ADCH[4:0]) to all 1s to enter a low-power state.

If ACLKEN is set, a conversion can be initiated while in stop using the external hardware trigger ADEXTCO when in external convert mode. The ADC10 will operate in a low-power mode until the trigger is asserted, at which point it will perform a conversion and assert the interrupt when complete (if AIEN is set).

# 3.6 ADC10 During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. BCFE in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the

If the bus frequency is less than the ADCK frequency, precise sample time for continuous conversions cannot be guaranteed in short-sample mode (ADLSMP = 0). If the bus frequency is less than 1/11th of the ADCK frequency, precise sample time for continuous conversions cannot be guaranteed in long-sample mode (ADLSMP = 1).

When clear, the ADC10 will perform a single conversion (single conversion mode) each time ADSCR is written (assuming the ADCH[4:0] bits do not decode all 1s).

- 1 = Continuous conversion following a write to ADSCR

- 0 = One conversion following a write to ADSCR

#### ADCH[4:0] — Channel Select Bits

The ADCH[4:0] bits form a 5-bit field that is used to select one of the input channels. The input channels are detailed in Table 3-2. The successive approximation converter subsystem is turned off when the channel select bits are all set to 1. This feature allows explicit disabling of the ADC10 and isolation of the input channel from the I/O pad. Terminating continuous conversion mode this way will prevent an additional, single conversion from being performed. It is not necessary to set the channel select bits to all 1s to place the ADC10 in a low-power state, however, because the module is automatically placed in a low-power state when a conversion completes.

| ADCH4 | ADCH3 | ADCH2         | ADCH1 | ADCH0 | Input Select <sup>(1)</sup> |

|-------|-------|---------------|-------|-------|-----------------------------|

| 0     | 0     | 0             | 0     | 0     | AD0                         |

| 0     | 0     | 0             | 0     | 1     | AD1                         |

| 0     | 0     | 0             | 1     | 0     | AD2                         |

| 0     | 0     | 0             | 1     | 1     | AD3                         |

| 0     | 0     | 1             | 0     | 0     | AD4                         |

| 0     | 0     | 1             | 0     | 1     | AD5                         |

| 0     | 0     | 1             | 1     | 0     | Unused                      |

|       | Cor   | ntinuing thro | ugh   |       | Unused                      |

| 1     | 1     | 0             | 0     | 1     | Unused                      |

| 1     | 1     | 0             | 1     | 0     | BANDGAP REF <sup>(2)</sup>  |

| 1     | 1     | 0             | 1     | 1     | Reserved                    |

| 1     | 1     | 1             | 0     | 0     | Reserved                    |

| 1     | 1     | 1             | 0     | 1     | V <sub>REFH</sub>           |

| 1     | 1     | 1             | 1     | 0     | V <sub>REFL</sub>           |

| 1     | 1     | 1             | 1     | 1     | Low-power state             |

Table 3-2. Input Channel Select

1. If any unused or reserved channels are selected, the resulting conversion will be unknown.

2. Requires LVI to be powered (LVIPWRD =0, in CONFIG1)

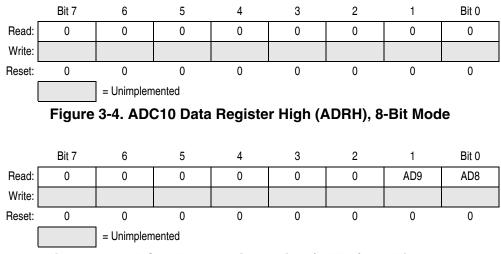

## 3.8.2 ADC10 Result High Register (ADRH)

This register holds the MSBs of the result and is updated each time a conversion completes. All other bits read as 0s. Reading ADRH prevents the ADC10 from transferring subsequent conversion results into the result registers until ADRL is read. If ADRL is not read until the after next conversion is completed, then the intermediate conversion result will be lost. In 8-bit mode, this register contains no interlocking with ADRL.

#### Analog-to-Digital Converter (ADC10) Module

## 3.8.3 ADC10 Result Low Register (ADRL)

This register holds the LSBs of the result. This register is updated each time a conversion completes. Reading ADRH prevents the ADC10 from transferring subsequent conversion results into the result registers until ADRL is read. If ADRL is not read until the after next conversion is completed, then the intermediate conversion result will be lost. In 8-bit mode, there is no interlocking with ADRH.

Figure 3-6. ADC10 Data Register Low (ADRL)

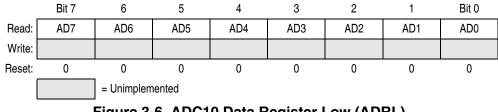

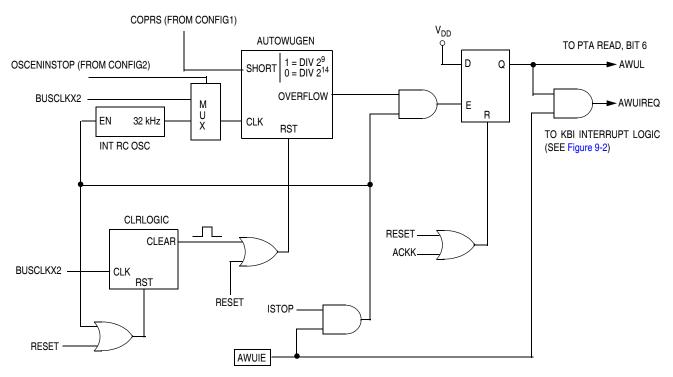

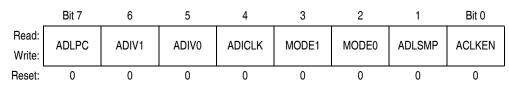

## 3.8.4 ADC10 Clock Register (ADCLK)

This register selects the clock frequency for the ADC10 and the modes of operation.

Figure 3-7. ADC10 Clock Register (ADCLK)

## ADLPC — ADC10 Low-Power Configuration Bit

ADLPC controls the speed and power configuration of the successive approximation converter. This is used to optimize power consumption when higher sample rates are not required.

1 = Low-power configuration: The power is reduced at the expense of maximum clock speed.

0 = High-speed configuration

Analog-to-Digital Converter (ADC10) Module

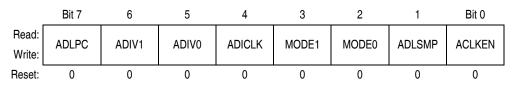

# Chapter 4 Auto Wakeup Module (AWU)

# 4.1 Introduction

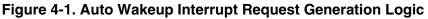

This section describes the auto wakeup module (AWU). The AWU generates a periodic interrupt during stop mode to wake the part up without requiring an external signal. Figure 4-1 is a block diagram of the AWU.

# 4.2 Features

Features of the auto wakeup module include:

- One internal interrupt with separate interrupt enable bit, sharing the same keyboard interrupt vector and keyboard interrupt mask bit

- Exit from low-power stop mode without external signals

- Selectable timeout periods

- Dedicated low-power internal oscillator separate from the main system clock sources

- Option to allow bus clock source to run the AWU if enabled in STOP

#### **Computer Operating Properly (COP)**

The COP counter is a free-running 6-bit counter preceded by the 12-bit system integration module (SIM) counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 BUSCLKX4 cycles; depending on the state of the COP rate select bit, COPRS, in configuration register 1. With a 262,128 BUSCLKX4 cycle overflow option, the internal 12.8-MHz oscillator gives a COP timeout period of 20.48 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the  $\overline{\text{RST}}$  pin low (if the RSTEN bit is set in the CONFIG1 register) for 32 × BUSCLKX4 cycles and sets the COP bit in the reset status register (RSR). See 13.8.1 SIM Reset Status Register.

#### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

# 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

## 6.3.1 BUSCLKX4

BUSCLKX4 is the oscillator output signal. BUSCLKX4 frequency is equal to the crystal frequency or the RC-oscillator frequency.

## 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

## 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see Figure 6-2) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector.

## 6.3.4 Power-On Reset

The power-on reset (POR) circuit in the SIM clears the SIM counter  $4096 \times BUSCLKX4$  cycles after power up.

## 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

## 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register (CONFIG). See Chapter 5 Configuration Register (CONFIG).

Computer Operating Properly (COP)

Keyboard Interrupt Module (KBI)

## 9.8.2 Keyboard Interrupt Enable Register (KBIER)

KBIER enables or disables each keyboard interrupt pin.

## Figure 9-4. Keyboard Interrupt Enable Register (KBIER)

#### KBIE5–KBIE0 — Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch KBI interrupt requests.

1 = KBIx pin enabled as keyboard interrupt pin

0 = KBIx pin not enabled as keyboard interrupt pin

#### NOTE

AWUIE bit is not used in conjunction with the keyboard interrupt feature. To see a description of this bit, see Chapter 4 Auto Wakeup Module (AWU).

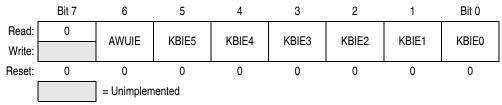

## 9.8.3 Keyboard Interrupt Polarity Register (KBIPR)

KBIPR determines the polarity of the enabled keyboard interrupt pin and enables the appropriate pullup or pulldown device.

#### Figure 9-5. Keyboard Interrupt Polarity Register (KBIPR)

#### KBIP5-KBIP0 — Keyboard Interrupt Polarity Bits

Each of these read/write bits enables the polarity of the keyboard interrupt detection.

1 = Keyboard polarity is high level and/or rising edge

0 = Keyboard polarity is low level and/or falling edge

#### Input/Output Ports (PORTS)

## 12.3.4 Port A Summary Table

The following table summarizes the operation of the port A pins when used as a general-purpose input/output pins.

| PTAPUE | PTAPUE DDRA PTA I/O Pin |                  | I/O Pin                               | Accesses to DDRA | Access    | ses to PTA               |

|--------|-------------------------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    | Bit                     | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0                       | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRA5-DDRA0      | Pin       | PTA5–PTA0 <sup>(3)</sup> |

| 0      | 0                       | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRA5-DDRA0      | Pin       | PTA5–PTA0 <sup>(3)</sup> |

| Х      | 1                       | х                | Output                                | DDRA5-DDRA0      | PTA5-PTA0 | PTA5–PTA0 <sup>(5)</sup> |

#### Table 12-1. Port A Pin Functions

1. X = don't care

2. I/O pin pulled to  $V_{DD}$  by internal pullup.

3. Writing affects data register, but does not affect input.

4. Hi-Z = high impedance

5. Output does not apply to PTA2

# 12.4 Port B

Port B is an 8-bit special function port that shares two of its pins with the 10-bit ADC (see Chapter 3 Analog-to-Digital Converter (ADC10) Module).

Each port B pin also has a software configurable pullup device if the corresponding port pin is configured as an input port.

## 12.4.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the port B pins.

Figure 12-5. Port B Data Register (PTB)

#### PTB[7:0] — Port B Data Bits

These read/write bits are software programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

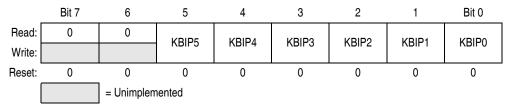

# Chapter 13 System Integration Module (SIM)

# **13.1 Introduction**

This section describes the system integration module (SIM), which supports up to 24 external and/or internal interrupts. Together with the central processor unit (CPU), the SIM controls all microcontroller unit (MCU) activities. A block diagram of the SIM is shown in Figure 13-1. The SIM is a system state controller that coordinates CPU and exception timing.

The SIM is responsible for:

- · Bus clock generation and control for CPU and peripherals

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and computer operating properly (COP) timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

## Table 13-1. Signal Name Conventions

| Signal Name | Description                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSCLKX4    | Buffered clock from the internal, RC or XTAL oscillator circuit.                                                                                           |

| BUSCLKX2    | The BUSCLKX4 frequency divided by two. This signal is again divided by two in the SIM to generate the internal bus clocks (bus clock = BUSCLKX4 $\div$ 4). |

| Address bus | Internal address bus                                                                                                                                       |

| Data bus    | Internal data bus                                                                                                                                          |

| PORRST      | Signal from the power-on reset module to the SIM                                                                                                           |

| IRST        | Internal reset signal                                                                                                                                      |

| R/W         | Read/write signal                                                                                                                                          |

# 13.2 RST and IRQ Pins Initialization

RST and IRQ pins come out of reset as PTA3 and PTA2 respectively. RST and IRQ functions can be activated by programing CONFIG2 accordingly. Refer to Chapter 5 Configuration Register (CONFIG).

#### System Integration Module (SIM)

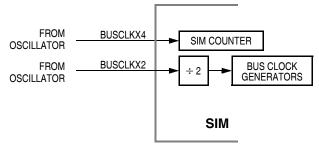

Figure 13-1. SIM Block Diagram

# **13.3 SIM Bus Clock Control and Generation**

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 13-2.

Timer Interface Module (TIM)

## 14.8.2 TIM Counter Registers

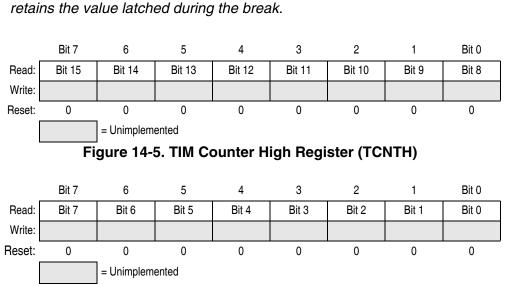

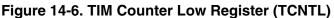

The two read-only TIM counter registers contain the high and low bytes of the value in the counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

> **NOTE** If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL

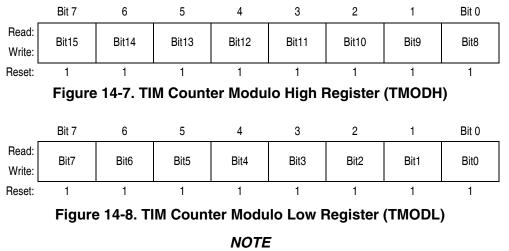

## 14.8.3 TIM Counter Modulo Registers

The read/write TIM modulo registers contain the modulo value for the counter. When the counter reaches the modulo value, the overflow flag (TOF) becomes set, and the counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIM counter modulo registers.

Reset the counter before writing to the TIM counter modulo registers.

**Electrical Specifications**

# 16.8 3-V DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                        | Symbol              | Min                                                                  | Typ <sup>(2)</sup> | Max                   | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------|--------------------|-----------------------|------|

| Output high voltage<br>$I_{Load} = -0.6$ mA, all I/O pins<br>$I_{Load} = -4.0$ mA, all I/O pins<br>$I_{Load} = -10.0$ mA, PTA0, PTA1, PTA3–PTA5 only | V <sub>OH</sub>     | V <sub>DD</sub> -0.3<br>V <sub>DD</sub> -1.0<br>V <sub>DD</sub> -0.8 |                    |                       | v    |

| Maximum combined I <sub>OH</sub> (all I/O pins)                                                                                                      | I <sub>OHT</sub>    | —                                                                    | —                  | 50                    | mA   |

| Output low voltage<br>$I_{Load} = 0.5$ mA, all I/O pins<br>$I_{Load} = 6.0$ mA, all I/O pins<br>$I_{Load} = 10.0$ mA, PTA0, PTA1, PTA3–PTA5 only     | V <sub>OL</sub>     |                                                                      |                    | 0.3<br>1.0<br>0.8     | v    |

| Maximum combined I <sub>OL</sub> (all I/O pins)                                                                                                      | I <sub>OHL</sub>    | —                                                                    | —                  | 50                    | mA   |

| Input high voltage<br>PTA0–PTA5, PTB0–PTB7                                                                                                           | V <sub>IH</sub>     | 0.7 x V <sub>DD</sub>                                                | _                  | V <sub>DD</sub>       | v    |

| Input low voltage<br>PTA0-PTA5, PTB0-PTB7                                                                                                            | V <sub>IL</sub>     | V <sub>SS</sub>                                                      | _                  | 0.3 x V <sub>DD</sub> | v    |

| Input hysteresis <sup>(3)</sup>                                                                                                                      | V <sub>HYS</sub>    | 0.06 x V <sub>DD</sub>                                               | —                  | —                     | V    |

| DC injection current, all ports <sup>(4)</sup>                                                                                                       | I <sub>INJ</sub>    | -2                                                                   | —                  | +2                    | mA   |

| Total dc current injection (sum of all I/O) <sup>(4)</sup>                                                                                           | I <sub>INJTOT</sub> | -25                                                                  | —                  | +25                   | mA   |

| Ports Hi-Z leakage current                                                                                                                           | ۱ <sub>IL</sub>     | -1                                                                   | ±0.1               | +1                    | μA   |

| Capacitance<br>Ports (as input) <sup>(3)</sup>                                                                                                       | C <sub>IN</sub>     | _                                                                    | _                  | 8                     | pF   |

| POR rearm voltage                                                                                                                                    | V <sub>POR</sub>    | 750                                                                  | —                  | —                     | mV   |

| POR rise time ramp rate <sup>(3)(5)</sup>                                                                                                            | R <sub>POR</sub>    | 0.035                                                                | —                  | —                     | V/ms |

| Monitor mode entry voltage <sup>(3)</sup>                                                                                                            | V <sub>TST</sub>    | V <sub>DD</sub> + 2.5                                                | —                  | V <sub>DD</sub> + 4.0 | V    |

| Pullup resistors <sup>(6)</sup><br>PTA0–PTA5, PTB0–PTB7                                                                                              | R <sub>PU</sub>     | 16                                                                   | 26                 | 36                    | kΩ   |

| Pulldown resistors <sup>(7)</sup><br>PTA0–PTA5                                                                                                       | R <sub>PD</sub>     | 16                                                                   | 26                 | 36                    | kΩ   |

| Low-voltage inhibit reset, trip falling voltage                                                                                                      | V <sub>TRIPF</sub>  | 2.40                                                                 | 2.55               | 2.70                  | V    |

| Low-voltage inhibit reset, trip rising voltage <sup>(6)</sup>                                                                                        | V <sub>TRIPR</sub>  | 2.475                                                                | 2.625              | 2.775                 | V    |

| Low-voltage inhibit reset/recover hysteresis                                                                                                         | V <sub>HYS</sub>    |                                                                      | 75                 | _                     | mV   |

1.  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted. 2. Typical values reflect average measurements at midpoint of voltage range, 25•C only.

3. Values are based on characterization results, not tested in production.

4. Guaranteed by design, not tested in production.

If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, the LVI will hold the part in reset until minimum V<sub>DD</sub> is reached.

6.  $R_{PU}$  is measured at  $V_{DD}$  = 3.0 V 7.  $R_{PD}$  is measured at  $V_{DD}$  = 3.0 V, Pulldown resistors only available when KBIx is enabled with KBIxPOL =1.

**Electrical Specifications**

# **16.15 Memory Characteristics**

| Characteristic                                      | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage (1)                      | V <sub>RDR</sub>                 | 1.3        | _      | _          | V      |

| FLASH program bus clock frequency                   | _                                | 1          | _      |            | MHz    |

| FLASH PGM/ERASE supply voltage (V <sub>DD</sub> )   | V <sub>PGM/ERASE</sub>           | 2.7        | —      | 5.5        | V      |

| FLASH read bus clock frequency                      | f <sub>Read</sub> <sup>(2)</sup> | 0          | _      | 8 M        | Hz     |

| FLASH page erase time<br><1 K cycles<br>>1 K cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                               | t <sub>MErase</sub>              | 4          | —      |            | ms     |

| FLASH PGM/ERASE to HVEN setup time                  | t <sub>NVS</sub>                 | 10         | _      | _          | μs     |

| FLASH high-voltage hold time                        | t <sub>NVH</sub>                 | 5          | _      |            | μs     |

| FLASH high-voltage hold time (mass erase)           | t <sub>NVHL</sub>                | 100        | —      | _          | μs     |

| FLASH program hold time                             | t <sub>PGS</sub>                 | 5          | _      | _          | μs     |

| FLASH program time                                  | t <sub>PROG</sub>                | 30         | _      | 40         | μs     |

| FLASH return to read time                           | t <sub>RCV</sub> <sup>(3)</sup>  | 1          | _      | _          | μs     |

| FLASH cumulative program hv period                  | t <sub>HV</sub> <sup>(4)</sup>   | —          | —      | 4          | ms     |

| FLASH endurance <sup>(5)</sup>                      | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(6)</sup>            | _                                | 15         | 100    | _          | Years  |

1. Values are based on characterization results, not tested in production.

2. f<sub>Read</sub> is defined as the frequency range for which the FLASH memory can be read.

3. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

4. t<sub>HV</sub> is defined as the cumulative high voltage programming time to the same row before next erase.

t<sub>HV</sub> must satisfy this condition: t<sub>NVS</sub> + t<sub>NVH</sub> + t<sub>PGS</sub> + (t<sub>PROG</sub> x 32) ≤ t<sub>HV</sub> maximum.

Typical endurance was evaluated for this product family. For additional information on how Freescale Semiconductor defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

6. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines Typical Data Retention, please refer to Engineering Bulletin EB618.

**Mechanical Drawings**

Case 968 page 2 of 3

\_\_\_\_\_

**Mechanical Drawings**

Case 648 page 1 of 3

- The ADC that is on the QYxA can operate while the MCU is in stop mode allowing lower power operation. This also adds a lower noise environment for precise ADC results.

- Enabling an ADC channel no longer overrides the digital I/O function of the associated pin. To prevent the digital I/O from interfering with the ADC read of the pin, the data direction bit associated with the port pin must be set as input.

- Finally, the new ADC can be configured to select two different reference clock sources:

- The internal bus x 4

- An internal asynchronous source

The internal asynchronous clock source allows the ADC to be clocked for operation in stop mode.

#### A.2.1.1 Registers Affected

Figure A-1. ADC10 Status and Control Register (ADSCR)

The ADCHx bits can be used to select additional ADC channels or bandgap measurement.

|        | Bit 7           | 6 | 5 | 4 | 3 | 2 | 1   | Bit 0 |  |

|--------|-----------------|---|---|---|---|---|-----|-------|--|

| Read:  | 0               | 0 | 0 | 0 | 0 | 0 | AD9 | AD8   |  |

| Write: |                 |   |   |   |   |   |     |       |  |

| Reset: | 0               | 0 | 0 | 0 | 0 | 0 | 0   | 0     |  |

|        | = Unimplemented |   |   |   |   |   |     |       |  |

Figure A-2. ADC10 Data Register High (ADRH), 10-Bit Mode

10-bit ADC uses the new ADRH register for the upper 2 bits.

Figure A-3. ADC10 Clock Register (ADCLK)

A long sample time option has been added to conserve power at the expense of longer conversion times. This option is selected using the new ADLSMP bit in the ADCLK register. (The bit location was previously reserved.)

The ADC will now run in stop mode if the ACLKEN bit is set to enable the asynchronous clock inside the ADC module. Utilizing stop mode for an ADC conversion gives the quietest operating mode to get extremely accurate ADC readings. (This bit location now used by ACLKEN was reserved — it always read as a 0 and writes to that location had no affect.)