Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | HC08                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | -                                                                    |

| Peripherals                | LVD, POR, PWM                                                        |

| Number of I/O              | 13                                                                   |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                     |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 128 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                              |

| Supplier Device Package    | 16-PDIP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qy1acpe |

MC68HC908QY4A MC68HC908QY2A MC68HC908QY1A MC68HC908QT4A MC68HC908QT2A MC68HC908QT1A

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2007–2010. All rights reserved.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

# **Revision History**

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History**

| Date Revision<br>Level |                                                                                             | Description                                                                                                                                                                                                                                                   | Page<br>Number(s)               |  |

|------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

| December,<br>2005      | N/A                                                                                         | Initial release                                                                                                                                                                                                                                               | N/A                             |  |

|                        |                                                                                             | Added 1.7 Unused Pin Termination.                                                                                                                                                                                                                             | 20                              |  |

|                        | Figure 4-1. Auto Wakeup Interrupt Request Generation Logic — Corrected clock source.        |                                                                                                                                                                                                                                                               | 51                              |  |

|                        |                                                                                             | 4.3 Functional Description — Clarified operation.                                                                                                                                                                                                             | 52                              |  |

|                        |                                                                                             | 4.5.1 Wait Mode — Corrected operation details.                                                                                                                                                                                                                | 53                              |  |

|                        |                                                                                             | 4.6.4 Configuration Register 2 — Corrected clock source.                                                                                                                                                                                                      | 55                              |  |

| August,<br>2006        | 1                                                                                           | 4.6.5 Configuration Register 1 — Added SSREC bit description.                                                                                                                                                                                                 | 55                              |  |

| 2000                   |                                                                                             | 5.2 Functional Description — Corrected clock source.                                                                                                                                                                                                          | 58                              |  |

|                        |                                                                                             | 12.1 Introduction — Replaced note.                                                                                                                                                                                                                            | 103                             |  |

|                        | 13.7.2 Stop Mode — Corrected clock source.                                                  |                                                                                                                                                                                                                                                               | 121                             |  |

|                        |                                                                                             | 16.12 Supply Current Characteristics — Updated maximum values for SI <sub>DD</sub> at both 5 V and 3 V.                                                                                                                                                       | 165                             |  |

|                        |                                                                                             | A.2.3 Improved Auto Wakeup Module (AWU) — Corrected clock source.                                                                                                                                                                                             | 194                             |  |

|                        |                                                                                             | Chapter 3 Analog-to-Digital Converter (ADC10) Module — Renamed ADCSC register to ADSCR to be consistent with development tools.                                                                                                                               | 37                              |  |

|                        |                                                                                             | Figure 15-18. Monitor Mode Entry Timing — Changed CGMXCLK to BUSCLKX4                                                                                                                                                                                         | 154                             |  |

| A!!                    |                                                                                             | 16.12 Supply Current Characteristics — Added note 6 below table                                                                                                                                                                                               | 165                             |  |

| April,<br>2007         | Chapter 17 Ordering Information and Mechanical Specifications — Updated chapter to include: |                                                                                                                                                                                                                                                               |                                 |  |

|                        |                                                                                             | Table 17-1. Consumer and Industrial Device Numbering System Table 17-2. Automotive Device Numbering System 17.3 Orderable Part Numbering System 17.3.1 Consumer and Industrial Orderable Part Numbering System 17.3.2 Automotive Orderable Part Number System | 171<br>171<br>172<br>172<br>172 |  |

| March,<br>2010         | 3                                                                                           | Clarify internal oscillator trim register information.                                                                                                                                                                                                        | 27, 30, 31,<br>34, 95, 10       |  |

# **Table of Contents**

# Chapter 1 General Description

|                | General Description                        |    |

|----------------|--------------------------------------------|----|

| 1.1            | Introduction                               | 15 |

| 1.2            | Features                                   | 15 |

| 1.3            | MCU Block Diagram                          | 17 |

| 1.4            | Pin Assignments                            | 18 |

| 1.5            | Pin Functions                              |    |

| 1.6            | Pin Function Priority                      | 20 |

| 1.7            | Unused Pin Termination                     |    |

|                | Chapter 2 Memory                           |    |

| 2.1            | Introduction                               | 21 |

| 2.2            | Unimplemented Memory Locations             |    |

| 2.3            | Reserved Memory Locations                  |    |

| 2.4            | Direct Page Registers                      |    |

| 2.5            | Random-Access Memory (RAM)                 |    |

| 2.6            | FLASH Memory (FLASH)                       |    |

| 2.6.1          | FLASH Control Register                     |    |

| 2.6.2          | FLASH Page Erase Operation                 |    |

| 2.6.3          | FLASH Mass Erase Operation                 | 31 |

| 2.6.4          | FLASH Program Operation                    |    |

| 2.6.5          | FLASH Protection                           |    |

| 2.6.6          | FLASH Block Protect Register               |    |

| 2.6.7          | EEPROM Memory Emulation Using FLASH Memory | 35 |

|                | Chapter 3                                  |    |

|                | Analog-to-Digital Converter (ADC10) Module |    |

| 3.1            | Introduction                               |    |

| 3.2            | Features                                   |    |

| 3.3            | Functional Description                     |    |

| 3.3.1          | Clock Select and Divide Circuit            |    |

| 3.3.2<br>3.3.3 | Input Select and Pin Control               |    |

| 3.3.3.1        | Conversion Control                         |    |

| 3.3.3.2        |                                            |    |

| 3.3.3.3        | · · · · · · · · · · · · · · · · · · ·      |    |

| 3.3.3.4        | $oldsymbol{\circ}$                         |    |

# 2.6 FLASH Memory (FLASH)

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire monitor mode interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths.

This subsection describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from the internal  $V_{DD}$  supply. The program and erase operations are enabled through the use of an internal charge pump.

The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section.

#### NOTE

An erased bit reads as a 1 and a programmed bit reads as a 0. A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

# 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

#### **HVEN** — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM =1 or ERASE =1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation.

- 1 = Mass erase operation selected

- 0 = Mass erase operation unselected

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Analog-to-Digital Converter (ADC10) Module

charging. If externally available, connect the  $V_{REFL}$  pin to the same potential as  $V_{SSA}$  at the single point ground location.

# 3.7.5 ADC10 Channel Pins (ADn)

The ADC10 has multiple input channels. Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. 0.01  $\mu$ F capacitors with good high-frequency characteristics are sufficient. These capacitors are not necessary in all cases, but when used they must be placed as close as possible to the package pins and be referenced to  $V_{\rm SSA}$ .

# 3.8 Registers

These registers control and monitor operation of the ADC10:

- ADC10 status and control register, ADSCR

- ADC10 data registers, ADRH and ADRL

- ADC10 clock register, ADCLK

# 3.8.1 ADC10 Status and Control Register

This section describes the function of the ADC10 status and control register (ADSCR). Writing ADSCR aborts the current conversion and initiates a new conversion (if the ADCH[4:0] bits are equal to a value other than all 1s).

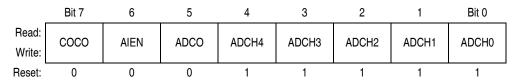

Figure 3-3. ADC10 Status and Control Register (ADSCR)

#### **COCO** — Conversion Complete Bit

COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the status and control register is written or whenever the data register (low) is read.

- 1 = Conversion completed

- 0 = Conversion not completed

#### **AIEN** — **ADC10** Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of a conversion. The interrupt signal is cleared when the data register is read or the status/control register is written.

- 1 = ADC10 interrupt enabled

- 0 = ADC10 interrupt disabled

#### ADCO — ADC10 Continuous Conversion Bit

When this bit is set, the ADC10 will begin to convert samples continuously (continuous conversion mode) and update the result registers at the end of each conversion, provided the ADCH[4:0] bits do not decode to all 1s. The ADC10 will continue to convert until the MCU enters reset, the MCU enters stop mode (if ACLKEN is clear), ADCLK is written, or until ADSCR is written again. If stop is entered (with ACLKEN low), continuous conversions will cease and can be restarted only with a write to ADSCR. Any write to ADSCR with ADCO set and the ADCH bits not all 1s will abort the current conversion and begin continuous conversions.

#### **Configuration Register (CONFIG)**

# IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- $0 = Internal pullup is connected between <math>\overline{IRQ}$  pin and  $V_{DD}$

#### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

### OSCENINSTOP— Oscillator Enable in Stop Mode Bit

OSCENINSTOP, when set, will allow the clock source to continue to generate clocks in stop mode. This function can be used to keep the auto-wakeup running while the rest of the microcontroller stops. When clear, the clock source is disabled when the microcontroller enters stop mode.

- 1 = Oscillator enabled to operate during stop mode

- 0 = Oscillator disabled during stop mode

#### RSTEN — RST Pin Function Selection

- 1 = Reset function active in pin

- 0 = Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

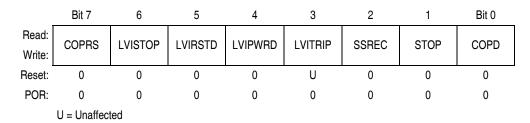

Figure 5-2. Configuration Register 1 (CONFIG1)

#### COPRS (Out of Stop Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- 0 = COP reset long cycle = 262,128 × BUSCLKX4

# COPRS (In Stop Mode) — Auto Wakeup Period Selection Bit, depends on OSCSTOPEN in CONFIG2 and external clock source

- $1 = \text{Auto wakeup short cycle} = 512 \times (INTRCOSC or BUSCLKX2)$

- 0 = Auto wakeup long cycle = 16,384 × (INTRCOSC or BUSCLKX2)

# LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

- 1 = LVI enabled during stop mode

- 0 = LVI disabled during stop mode

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

- 1 = LVI module resets disabled

- 0 = LVI module resets enabled

# **Central Processor Unit (CPU)**

# 7.7 Instruction Set Summary

Table 7-1 provides a summary of the M68HC08 instruction set.

Table 7-1. Instruction Set Summary (Sheet 1 of 6)

| Source                                                                                          | Operation                                            | Description                                              |            | Effect on CCR |   |          |    |   | Address<br>Mode                                                                              | Opcode                                           | Operand                                         | les                                  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------|------------|---------------|---|----------|----|---|----------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            | - Political                                          |                                                          |            | Н             | I | N        | Z  | С | Add                                                                                          | Opc                                              | Ope                                             | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC, X<br>ADC opr,SP<br>ADC opr,SP  | Add with Carry                                       | A ← (A) + (M) + (C)                                      | 1          | ‡             | - | 1        | 1  | ţ | IMM DIR EXT IX2 IX1 IX SP1 SP2                                                               | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2 3 4 4 3 2 4 5                      |

| ADD #opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD opr,X<br>ADD opr,SP<br>ADD opr,SP          | Add without Carry                                    | $A \leftarrow (A) + (M)$                                 | 1          | Î             | _ | 1        | Î  | Î | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB |                                                 | 2<br>3<br>4<br>3<br>2<br>4<br>5      |

| AIS #opr                                                                                        | Add Immediate Value (Signed) to SP                   | SP ← (SP) + (16 « M)                                     | -          | _             | _ | _        | _  | - | IMM                                                                                          | A7                                               | ii                                              | 2                                    |

| AIX #opr                                                                                        | Add Immediate Value (Signed) to H:X                  | H:X ← (H:X) + (16 « M)                                   | -          | _             | _ | _        | -  | _ | IMM                                                                                          | AF                                               | ii                                              | 2                                    |

| AND #opr<br>AND opr<br>AND opr,<br>AND opr,X<br>AND opr,X<br>AND, X<br>AND opr,SP<br>AND opr,SP | Logical AND                                          | A ← (A) & (M)                                            | 0          | _             | _ | ‡        | ‡  | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                    | Arithmetic Shift Left<br>(Same as LSL)               | © <b>→</b>                                               | 1          | _             | - | ‡        | Į. | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                 | Arithmetic Shift Right                               | b7 b0                                                    | ţ          | _             | ı | <b>‡</b> | ‡  | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| BCC rel                                                                                         | Branch if Carry Bit Clear                            | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                 | _          | _             | _ | _        | -  | - | REL                                                                                          | 24                                               | rr                                              | 3                                    |

| BCLR n, opr                                                                                     | Clear Bit n in M                                     | Mn ← 0                                                   | _          | _             | _ | _        | _  | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd    | 4<br>4<br>4<br>4<br>4<br>4<br>4      |

| BCS rel                                                                                         | Branch if Carry Bit Set (Same as BLO)                | PC ← (PC) + 2 + rel? (C) = 1                             | _          | _             | _ | _        | _  | _ | REL                                                                                          | 25                                               | rr                                              | 3                                    |

| BEQ rel                                                                                         | Branch if Equal                                      | $PC \leftarrow (PC) + 2 + rel? (Z) = 1$                  | _          | _             | _ | _        | -  | _ | REL                                                                                          | 27                                               | rr                                              | 3                                    |

| BGE opr                                                                                         | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 0$         | _          | -             | _ | _        | -  | - | REL                                                                                          | 90                                               | rr                                              | 3                                    |

| BGT opr                                                                                         | Branch if Greater Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel?(Z) \mid (N \oplus V) = 0$ | -          | -             | - | _        | _  | - | REL                                                                                          | 92                                               | rr                                              | 3                                    |

| BHCC rel                                                                                        | Branch if Half Carry Bit Clear                       | $PC \leftarrow (PC) + 2 + rel? (H) = 0$                  | <u> </u> – | -             | _ | _        | _  | _ | REL                                                                                          | 28                                               | rr                                              | 3                                    |

| BHCS rel                                                                                        | Branch if Half Carry Bit Set                         | PC ← (PC) + 2 + rel? (H) = 1                             | -          | _             | _ | _        | _  | _ | REL                                                                                          | 29                                               | rr                                              | 3                                    |

| BHI rel                                                                                         | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + rel? (C) \mid (Z) = 0$         | -          | -             | _ | _        | _  | _ | REL                                                                                          | 22                                               | rr                                              | 3                                    |

# Central Processor Unit (CPU)

# Table 7-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation Description            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | Effect on CCR |     |          |   |    | Address<br>Mode                                     | Opcode                                           | Operand                                   | les                                  |

|------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|-----|----------|---|----|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| Form                                                                                           | Section Section                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ٧  | Н             | I   | Ν        | Z | С  | Add                                                 | Opc                                              | Ope                                       | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                           | Clear                            | $\begin{array}{l} M \leftarrow \$00 \\ A \leftarrow \$00 \\ X \leftarrow \$00 \\ X \leftarrow \$00 \\ H \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \end{array}$                                                                                                                                                                                                                                                                                                                                          | 0  | _             | ı   | 0        | 1 | _  | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff<br>ff                            | 3<br>1<br>1<br>3<br>2<br>4           |

| CMP #opr<br>CMP opr<br>CMP opr,<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ţ  | _             |     | <b>‡</b> | ‡ | 1  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = SFF - (M) \\ A \leftarrow (A) = SFF - (M) \\ X \leftarrow (X) = SFF - (M) \\ M \leftarrow (\underline{M}) = SFF - (M) \\ M \leftarrow (\underline{M}) = SFF - (M) \\ M \leftarrow (\overline{M}) = SFF - (M) \\ M \leftarrow (\overline{M}) = SFF - (M) \end{array}$                                                                                                                                                                                                                                              | 0  | _             | - 1 | 1        | ‡ | 1  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) - (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ţ  | -             | _   | ‡        | ‡ | ‡  | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                             | 3                                    |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX ,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  | _             | _   | ‡        | 1 | Į. | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 |                                           | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U  | -             | -   | 1        | 1 | 1  | INH                                                 | 72                                               |                                           | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A)-1 \text{ or } M \leftarrow (M)-1 \text{ or } X \leftarrow (X)-1 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+4+\mathit{rel}? \text{ (result)} \neq 0 \end{array}$ | _  | _             | ı   | -        | ı | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr | 533546                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{l} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                       | Į. | _             | -   | <b>1</b> | 1 | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                            | Divide                           | $A \leftarrow (H:A)/(X)$<br>$H \leftarrow Remainder$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _  | -             | -   | -        | ‡ | ‡  | INH                                                 | 52                                               |                                           | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0  | _             | ı   | ‡        | ‡ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $M \leftarrow (M) + 1$<br>$A \leftarrow (A) + 1$<br>$X \leftarrow (X) + 1$<br>$M \leftarrow (M) + 1$<br>$M \leftarrow (M) + 1$<br>$M \leftarrow (M) + 1$                                                                                                                                                                                                                                                                                                                                                                                                          | Î  | _             | -   | 1        | ‡ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

**Keyboard Interrupt Module (KBI)**

# 9.3.2 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pullup or pulldown device to pull the pin to its deasserted level. Therefore a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting IMASKK in KBSCR.

- 2. Enable the KBI polarity by setting the appropriate KBIPx bits in KBIPR.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in KBIER.

- 4. Write to ACKK in KBSCR to clear any false interrupts.

- 5. Clear IMASKK.

An interrupt signal on an edge sensitive pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge and level sensitive pin must be acknowledged after a delay that depends on the external load.

# 9.4 Interrupts

The following KBI source can generate interrupt requests:

Keyboard flag (KEYF) — The KEYF bit is set when any enabled KBI pin is asserted based on the KBI mode and pin polarity. The keyboard interrupt mask bit, IMASKK, is used to enable or disable KBI interrupt requests.

### 9.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 9.5.1 Wait Mode

The KBI module remains active in wait mode. Clearing IMASKK in KBSCR enables keyboard interrupt requests to bring the MCU out of wait mode.

#### 9.5.2 Stop Mode

The KBI module remains active in stop mode. Clearing IMASKK in KBSCR enables keyboard interrupt requests to bring the MCU out of stop mode.

# 9.6 KBI During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

# 10.4 LVI Interrupts

The LVI module does not generate interrupt requests.

# 10.5 Low-Power Modes

The STOP and WAIT instructions put the MCU in low power-consumption standby modes.

#### 10.5.1 Wait Mode

If enabled, the LVI module remains active in wait mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of wait mode.

# 10.5.2 Stop Mode

If the LVIPWRD bit in the configuration register is cleared and the LVISTOP bit in the configuration register is set, the LVI module remains active. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of stop mode.

# 10.6 Registers

The LVI status register (LVISR) contains a status bit that is useful when the LVI is enabled and LVI reset is disabled.

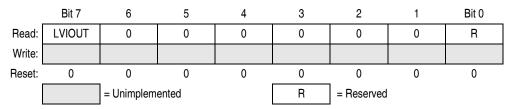

Figure 10-2. LVI Status Register (LVISR)

# LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage and is cleared when  $V_{DD}$  voltage rises above  $V_{TRIPB}$ . (See Table 10-1).

Table 10-1, LVIOUT Bit Indication

| V <sub>DD</sub>                                           | LVIOUT         |

|-----------------------------------------------------------|----------------|

| V <sub>DD</sub> > V <sub>TRIPR</sub>                      | 0              |

| V <sub>DD</sub> < V <sub>TRIPF</sub>                      | 1              |

| V <sub>TRIPF</sub> < V <sub>DD</sub> < V <sub>TRIPR</sub> | Previous value |

#### Oscillator (OSC) Module

copy the trim value from \$FFC0 or \$FFC1 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim values, so confirm with your programmer vendor that the trim values at \$FFC0 and \$FFC1 are preserved, or are re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

# 11.3.2.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, configure OSCOPT[1:0] to external crystal. To help precharge an external crystal oscillator, momentarily configure OSC2 as an output and drive it high for several cycles. This can help the crystal circuit start more robustly.

- Configure OSCOPT[1:0] and ECFS[1:0] according to 11.8.1 Oscillator Status and Control Register.

The oscillator module control logic will then enable OSC1 as an external clock input and, if the

external crystal option is selected, OSC2 will also be enabled as the clock output. If RC oscillator

option is selected, enabling the OSC2 output may change the bus frequency.

- 3. Create a software delay to provide the stabilization time required for the selected clock source (crystal, resonator, RC). A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency; i.e., for a 4-MHz crystal, wait approximately 1 ms.

- 4. After the stabilization delay has elapsed, set ECGON.

After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges. The OSC module then switches to the external clock. Logic provides a coherent transition. The OSC module first sets ECGST and then stops the internal oscillator.

#### 11.3.2.3 External to Internal Clock Switching

After following the procedures to switch to an external clock source, it is possible to go back to the internal source. By clearing the OSCOPT[1:0] bits and clearing the ECGON bit, the external circuit will be disengaged. The bus clock will be derived from the selected internal clock source based on the ICFS[1:0] bits.

#### 11.3.3 External Oscillator

The external oscillator option is designed for use when a clock signal is available in the application to provide a clock source to the MCU. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4. The OSC2EN bit will be forced clear to enable alternative functions on the pin.

#### 11.3.4 XTAL Oscillator

The XTAL oscillator circuit is designed for use with an external crystal or ceramic resonator to provide an accurate clock source. In this configuration, the OSC2 pin is dedicated to the external crystal circuit. The OSC2EN bit has no effect when this clock mode is selected.

In its typical configuration, the XTAL oscillator is connected in a Pierce oscillator configuration, as shown in Figure 11-2. This figure shows only the logical representation of the internal components and may not represent actual circuitry.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

Input/Output Ports (PORTS)

# 12.3.4 Port A Summary Table

The following table summarizes the operation of the port A pins when used as a general-purpose input/output pins.

Table 12-1. Port A Pin Functions

| PTAPUE | DDRA | PTA              | I/O Pin                               | Accesses to DDRA | Access    | ses to PTA               |

|--------|------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    | Bit  | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0    | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRA5-DDRA0      | Pin       | PTA5-PTA0 <sup>(3)</sup> |

| 0      | 0    | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRA5-DDRA0      | Pin       | PTA5-PTA0 <sup>(3)</sup> |

| Х      | 1    | Х                | Output                                | DDRA5-DDRA0      | PTA5-PTA0 | PTA5-PTA0 <sup>(5)</sup> |

- 1. X = don't care

- 2. I/O pin pulled to  $V_{DD}$  by internal pullup.

- 3. Writing affects data register, but does not affect input.

- 4. Hi-Z = high impedance

- 5. Output does not apply to PTA2

#### 12.4 Port B

Port B is an 8-bit special function port that shares two of its pins with the 10-bit ADC (see Chapter 3 Analog-to-Digital Converter (ADC10) Module).

Each port B pin also has a software configurable pullup device if the corresponding port pin is configured as an input port.

# 12.4.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the port B pins.

Figure 12-5. Port B Data Register (PTB)

#### PTB[7:0] — Port B Data Bits

These read/write bits are software programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

# 13.3.1 Bus Timing

In user mode, the internal bus frequency is the oscillator frequency (BUSCLKX4) divided by four.

# 13.3.2 Clock Start-Up from POR

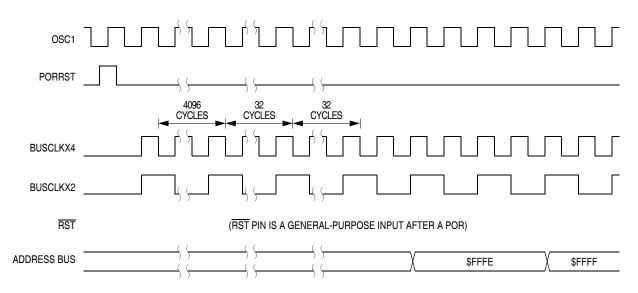

When the power-on reset module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 BUSCLKX4 cycle POR time out has completed. The IBUS clocks start upon completion of the time out.

# 13.3.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows BUSCLKX4 to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay time out. This time out is selectable as 4096 or 32 BUSCLKX4 cycles. See 13.7.2 Stop Mode.

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

# 13.4 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE\_FFFF (\$FEFE\_FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 13.5 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 13.8 SIM Registers.

#### 13.4.1 External Pin Reset

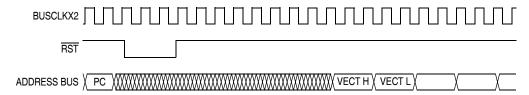

The  $\overline{RST}$  pin circuits include an internal pullup device. Pulling the asynchronous  $\overline{RST}$  pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as  $\overline{RST}$  is held low for at least the minimum  $t_{RL}$  time. Figure 13-3 shows the relative timing. The  $\overline{RST}$  pin function is only available if the RSTEN bit is set in the CONFIG2 register.

Figure 13-3. External Reset Timing

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

## 13.4.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power on has occurred. The SIM counter counts out 4096 BUSCLKX4 cycles. Sixty-four BUSCLKX4 cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables the oscillator to drive BUSCLKX4.

- Internal clocks to the CPU and modules are held inactive for 4096 BUSCLKX4 cycles to allow stabilization of the oscillator.

- The POR bit of the SIM reset status register (SRSR) is set.

# See Figure 13-6.

Figure 13-6. POR Recovery

#### 13.4.2.2 Computer Operating Properly (COP) Reset

An input to the SIM is reserved for the COP reset signal. The overflow of the COP counter causes an internal reset and sets the COP bit in the SIM reset status register (SRSR). The SIM actively pulls down the RST pin for all internal reset sources.

To prevent a COP module time out, write any value to location \$FFFF. Writing to location \$FFFF clears the COP counter and stages 12–5 of the SIM counter. The SIM counter output, which occurs at least every 4080 BUSCLKX4 cycles, drives the COP counter. The COP should be serviced as soon as possible out of reset to guarantee the maximum amount of time before the first time out.

The COP module is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

#### 13.4.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

**System Integration Module (SIM)**

#### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

## 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

# 13.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

#### 13.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

#### 13.7.1 Wait Mode

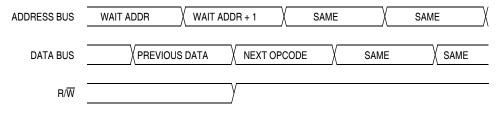

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

#### Figure 13-14. Wait Mode Entry Timing

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

## POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

#### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin (RST)

- 0 = POR or read of SRSR

# **COP** — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

## ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

# ILAD — Illegal Address Reset Bit (illegal attempt to fetch an opcode from an unimplemented address)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

#### **MODRST** — Monitor Mode Entry Module Reset bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} \neq V_{TST}$

- 0 = POR or read of SRSR

## LVI — Low Voltage Inhibit Reset bit

- 1 = Last reset caused by LVI circuit

- 0 = POR or read of SRSR

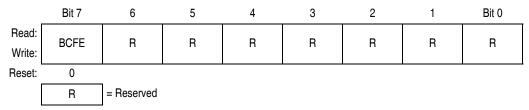

# 13.8.2 Break Flag Control Register

The break control register (BFCR) contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 13-20. Break Flag Control Register (BFCR)

#### **BCFE** — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

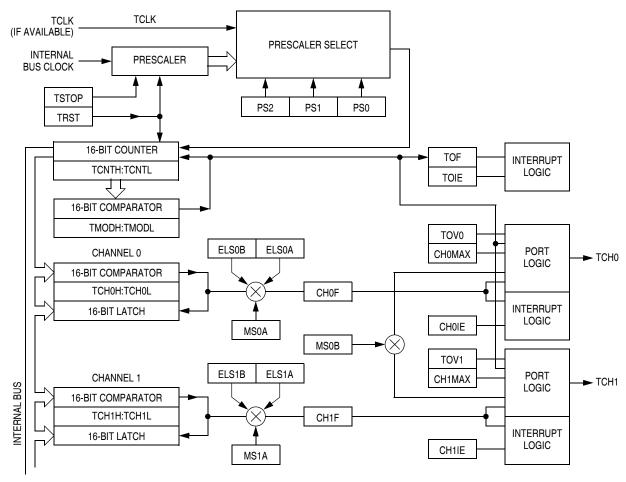

Figure 14-2. TIM Block Diagram

#### 14.3.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 14.3.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new

value in the output compare interrupt routine. The output compare interrupt occurs at the end of

the current output compare pulse. The interrupt routine has until the end of the counter overflow

period to write the new value.

- When changing to a larger output compare value, enable TIM overflow interrupts and write the new

value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the

current counter overflow period. Writing a larger value in an output compare interrupt routine (at

Case 968 page 2 of 3

# **Ordering Information and Mechanical Specifications**

Case 948F page 1 of 3