Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | -                                                          |

| Peripherals                | LVD, POR, PWM                                              |

| Number of I/O              | 13                                                         |

| Program Memory Size        | 1.5KB (1.5K x 8)                                           |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 128 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                             |

| Supplier Device Package    | 16-SOIC                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908qy1amdwe |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

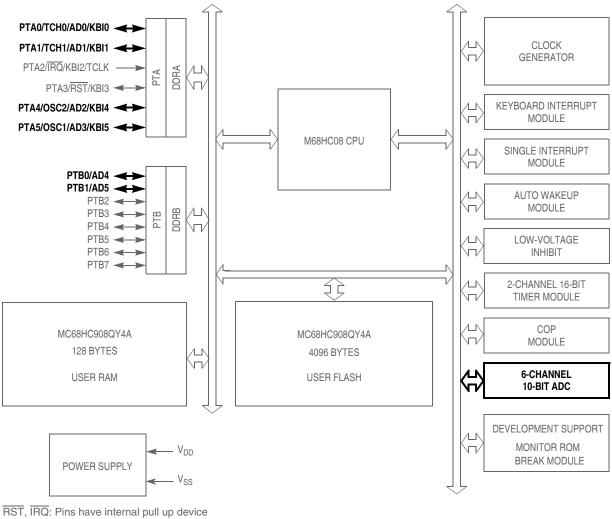

General Description

## **1.6 Pin Function Priority**

Table 1-3 is meant to resolve the priority if multiple functions are enabled on a single pin.

NOTE

Upon reset all pins come up as input ports regardless of the priority table.

| Pin Name            | Highest-to-Lowest Priority Sequence                                                             |

|---------------------|-------------------------------------------------------------------------------------------------|

| PTA0 <sup>(1)</sup> | $AD0 \rightarrow TCH0 \rightarrow KBI0 \rightarrow PTA0$                                        |

| PTA1 <sup>(1)</sup> | $AD1 \rightarrow TCH1 \rightarrow KBI1 \rightarrow PTA1$                                        |

| PTA2                | $\overline{\text{IRQ}} \rightarrow \text{TCLK} \rightarrow \text{KBI2} \rightarrow \text{PTA2}$ |

| PTA3                | $\overline{\text{RST}} \rightarrow \text{KBI3} \rightarrow \text{PTA3}$                         |

| PTA4 <sup>(1)</sup> | $OSC2 \rightarrow AD2 \rightarrow KBI4 \rightarrow PTA4$                                        |

| PTA5 <sup>(1)</sup> | $OSC1 \rightarrow AD3 \rightarrow KBI5 \rightarrow PTA5$                                        |

| PTB0 <sup>(1)</sup> | $AD4 \rightarrow PTB0$                                                                          |

| PTB1 <sup>(1)</sup> | $AD5 \rightarrow PTB1$                                                                          |

1. When a pin is to be used as an ADC pin, the I/O port function should be left as an input and all other shared modules should be disabled. The ADC does not override additional modules using the pin.

## 1.7 Unused Pin Termination

Input pins and I/O port pins that are not used in the application must be terminated. This prevents excess current caused by floating inputs, and enhances immunity during noise or transient events. Termination methods include:

- 1. Configuring unused pins as outputs and driving high or low;

- 2. Configuring unused pins as inputs and enabling internal pull-ups;

- 3. Configuring unused pins as inputs and using external pull-up or pull-down resistors.

Never connect unused pins directly to V<sub>DD</sub> or V<sub>SS</sub>.

Since some general-purpose I/O pins are not available on all packages, these pins must be terminated as well. Either method 1 or 2 above are appropriate.

#### **Direct Page Registers**

| Addr.                 | Register Name                                           |                           | Bit 7                                                                                                                                    | 6                   | 5     | 4         | 3          | 2     | 1     | Bit 0 |

|-----------------------|---------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|-----------|------------|-------|-------|-------|

|                       | LVI Status Register                                     | Read:                     | LVIOUT                                                                                                                                   | 0                   | 0     | 0         | 0          | 0     | 0     | R     |

| \$FE0C                | (LVISR)                                                 | Write:                    |                                                                                                                                          |                     |       |           |            |       |       |       |

|                       | See page 91.                                            | Reset:                    | 0                                                                                                                                        | 0                   | 0     | 0         | 0          | 0     | 0     | 0     |

| \$FE0D<br>↓<br>\$FE0F | Reserved                                                |                           |                                                                                                                                          |                     |       |           |            |       |       |       |

| \$FFBE                | FLASH Block Protect<br>Register (FLBPR)<br>See page 34. | Read:<br>Write:           | BPR7                                                                                                                                     | BPR6                | BPR5  | BPR4      | BPR3       | BPR2  | BPR1  | BPR0  |

|                       | See paye 34.                                            | Reset:                    |                                                                                                                                          |                     |       | Unaffecte | d by reset |       |       |       |

| \$FFBF                | Reserved                                                |                           |                                                                                                                                          |                     |       |           |            |       |       |       |

|                       |                                                         | г                         |                                                                                                                                          |                     | [     | [         | [          | 1     | 1     | ,     |

| \$FFC0                | Internal Oscillator Trim<br>(Factory Programmed         | Read:<br>Write:           | TRIM7                                                                                                                                    | TRIM6               | TRIM5 | TRIM4     | TRIM3      | TRIM2 | TRIM1 | TRIM0 |

|                       | VDD = 3.0 V)                                            | Reset:                    | Unaffected by reset                                                                                                                      |                     |       |           |            |       |       |       |

| \$FFC1                | Internal Oscillator Trim<br>(Factory Programmed         | Read:<br>Write:           | TRIM7                                                                                                                                    | TRIM6               | TRIM5 | TRIM4     | TRIM3      | TRIM2 | TRIM1 | TRIM0 |

|                       | VDD = 5.0 V)                                            | Reset:                    |                                                                                                                                          | Unaffected by reset |       |           |            |       |       |       |

| \$FFFF                | COP Control Register<br>(COPCTL)<br>See page 63.        | Read:<br>Write:<br>Reset: | LOW BYTE OF RESET VECTOR<br>WRITING CLEARS COP COUNTER (ANY VALUE)<br>Unaffected by reset<br>= Unimplemented R = Reserved U = Unaffected |                     |       |           |            |       |       |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 5)

#### Analog-to-Digital Converter (ADC10) Module

All port pins have programmable pull up device PTA[0:5]: Higher current sink and source capability PTB[0:7]: Not available on 8-pin devices

#### Figure 3-1. Block Diagram Highlighting ADC10 Block and Pins

#### 3.3.4.4 Code Width and Quantization Error

The ADC10 quantizes the ideal straight-line transfer function into 1024 steps (in 10-bit mode). Each step ideally has the same height (1 code) and width. The width is defined as the delta between the transition points from one code to the next. The ideal code width for an N bit converter (in this case N can be 8 or 10), defined as 1LSB, is:

$$1LSB = (V_{REFH} - V_{REFL}) / 2^{N}$$

Because of this quantization, there is an inherent quantization error. Because the converter performs a conversion and then rounds to 8 or 10 bits, the code will transition when the voltage is at the midpoint between the points where the straight line transfer function is exactly represented by the actual transfer function. Therefore, the quantization error will be  $\pm 1/2$ LSB in 8- or 10-bit mode. As a consequence, however, the code width of the first (\$000) conversion is only 1/2LSB and the code width of the last (\$FF or \$3FF) is 1.5LSB.

#### 3.3.4.5 Linearity Errors

The ADC10 may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the user should be aware of them because they affect overall accuracy. These errors are:

- Zero-Scale Error (E<sub>ZS</sub>) (sometimes called offset) This error is defined as the difference between the actual code width of the first conversion and the ideal code width (1/2LSB). Note, if the first conversion is \$001, then the difference between the actual \$001 code width and its ideal (1LSB) is used.

- Full-Scale Error (E<sub>FS</sub>) This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5LSB). Note, if the last conversion is \$3FE, then the difference between the actual \$3FE code width and its ideal (1LSB) is used.

- Differential Non-Linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral Non-Linearity (INL) This error is defined as the highest-value the (absolute value of the) running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total Unadjusted Error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function, and therefore includes all forms of error.

#### 3.3.4.6 Code Jitter, Non-Monotonicity and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

- Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the converter yields the lower code (and vice-versa). However, even very small amounts of system noise can cause the converter to be indeterminate (between two codes) for a range of input voltages around the transition voltage. This range is normally around ±1/2LSB but will increase with noise.

- Non-monotonicity is defined as when, except for code jitter, the converter converts to a lower code for a higher input voltage. Non-monotonicity is present if the apparent code jitter covers three codes (when the converter's output is indeterminate between three values for a given input voltage) or is greater than 1LSB.

- Missing codes are those which are never converted for any input value. In 8-bit or 10-bit mode, the ADC10 is guaranteed to be monotonic and to have no missing codes.

## 4.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 4.5.1 Wait Mode

The AWU module is inactive in wait mode.

#### 4.5.2 Stop Mode

When the AWU module is enabled (AWUIE = 1 in the keyboard interrupt enable register) it is activated automatically upon entering stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode. The AWU counters start from 0 each time stop mode is entered.

## 4.6 Registers

The AWU shares registers with the keyboard interrupt (KBI) module, the port A I/O module and configuration register 2. The following I/O registers control and monitor operation of the AWU:

- Port A data register (PTA)

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

- Configuration register 1 (CONFIG1)

- Configuration register 2 (CONFIG2)

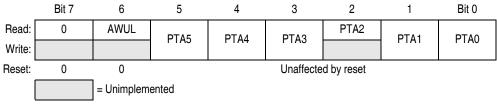

#### 4.6.1 Port A I/O Register

The port A data register (PTA) contains a data latch for the state of the AWU interrupt request, in addition to the data latches for port A.

Figure 4-2. Port A Data Register (PTA)

#### AWUL — Auto Wakeup Latch

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally. There is no PTA6 port or any of the associated bits such as PTA6 data direction or pullup bits.

- 1 = Auto wakeup interrupt request is pending

- 0 = Auto wakeup interrupt request is not pending

#### NOTE

PTA5–PTA0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 12.3.1 Port A Data Register.

Registers

#### AWUIE — Auto Wakeup Interrupt Enable Bit

This read/write bit enables the auto wakeup interrupt input to latch interrupt requests. Reset clears AWUIE.

1 = Auto wakeup enabled as interrupt input

0 = Auto wakeup not enabled as interrupt input

#### NOTE

KBIE5–KBIE0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 9.8.2 Keyboard Interrupt Enable Register (KBIER).

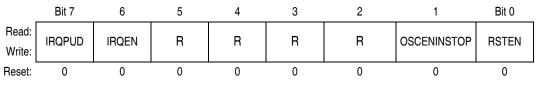

#### 4.6.4 Configuration Register 2

The configuration register 2 (CONFIG2), is used to allow the bus clock source to run in STOP. In this case, the clock, BUSCLKX2 will be used to drive the AWU request generator.

Figure 4-5. Configuration Register 2 (CONFIG2)

#### **OSCENINSTOP** — Oscillator Enable in Stop Mode Bit

OSCENINSTOP, when set, will allow the bus clock source (BUSCLKX2) to generate clocks for the AWU in stop mode. See *11.8.1 Oscillator Status and Control Register* for information on enabling the external clock sources.

1 = Oscillator enabled to operate during stop mode

0 = Oscillator disabled during stop mode

NOTE

IRQPUD, IRQEN, and RSTEN bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see Chapter 5 Configuration Register (CONFIG).

#### 4.6.5 Configuration Register 1

The configuration register 1 (CONFIG1), is used to select the period for the AWU. The timeout will be based on the COPRS bit along with the clock source for the AWU.

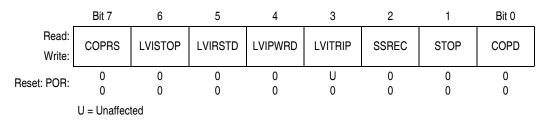

Figure 4-6. Configuration Register 1 (CONFIG1)

**Central Processor Unit (CPU)**

| Source                                                                                          | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   | Effect<br>on CCR |    |   |    | Address<br>Mode                                     | Opcode                                           | Operand                                         | es                                   |

|-------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------------------|----|---|----|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            | operation                        | Becomption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | v | Н | I                | Ν  | z | С  | Add<br>Mod                                          | Opc                                              | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR opr,X<br>CLR X<br>CLR opr,SP                | Clear                            | $\begin{array}{c} M \leftarrow \$00 \\ A \leftarrow \$00 \\ X \leftarrow \$00 \\ H \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \end{array}$                                                                                                                                                                                                                                                                                                                                           | 0 | _ | _                | 0  | 1 | _  | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F                 | dd<br>ff<br>ff                                  | 3<br>1<br>1<br>3<br>2<br>4           |

| CMP #opr<br>CMP opr<br>CMP opr,<br>CMP opr,X<br>CMP opr,X<br>CMP ,X<br>CMP opr,SP<br>CMP opr,SP | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t | _ | _                | ţ  | ţ | ţ  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>E1<br>F1<br>9EE1<br>9ED1       | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                    | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                                                                           | 0 | _ | _                | ţ  | ţ | 1  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

| CPHX #opr<br>CPHX opr                                                                           | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ţ | - | -                | \$ | ţ | ţ  | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3<br>4                               |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX ,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ţ | _ | _                | ţ  | ţ | ţ  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| DAA                                                                                             | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U | - | -                | 1  | 1 | \$ | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel       | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 4 + \mathit{rel} ? (\mathit{result}) \neq 0 \end{array}$ | _ | _ | _                | _  | _ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 5<br>3<br>3<br>5<br>4<br>6           |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                    | Decrement                        | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                   | ţ | - | _                | ţ  | ţ | -  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

| DIV                                                                                             | Divide                           | $A \leftarrow (H:A)/(X)$<br>H $\leftarrow$ Remainder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - | - | -                | -  | t | ţ  | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR ,X<br>EOR opr,SP<br>EOR opr,SP  | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 | _ | _                | ţ  | ţ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                    | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                   | ţ | _ | _                | ţ  | ţ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

# Chapter 8 External Interrupt (IRQ)

## 8.1 Introduction

The IRQ (external interrupt) module provides a maskable interrupt input.

$\overline{IRQ}$  functionality is enabled by setting configuration register 2 (CONFIG2) IRQEN bit accordingly. A zero disables the IRQ function and  $\overline{IRQ}$  will assume the other shared functionalities. A one enables the IRQ function. See Chapter 5 Configuration Register (CONFIG) for more information on enabling the IRQ pin.

The IRQ pin shares its pin with general-purpose input/output (I/O) port pins. See Figure 8-1 for port location of this shared pin.

## 8.2 Features

Features of the IRQ module include:

- A dedicated external interrupt pin IRQ

- IRQ interrupt control bits

- Programmable edge-only or edge and level interrupt sensitivity

- Automatic interrupt acknowledge

- Internal pullup device

## 8.3 Functional Description

A low level applied to the external interrupt request (IRQ) pin can latch a CPU interrupt request. Figure 8-2 shows the structure of the IRQ module.

Interrupt signals on the IRQ pin are latched into the IRQ latch. The IRQ latch remains set until one of the following actions occurs:

- IRQ vector fetch. An IRQ vector fetch automatically generates an interrupt acknowledge signal that clears the latch that caused the vector fetch.

- Software clear. Software can clear the IRQ latch by writing a 1 to the ACK bit in the interrupt status and control register (INTSCR).

- Reset. A reset automatically clears the IRQ latch.

The external IRQ pin is falling edge sensitive out of reset and is software-configurable to be either falling edge or falling edge and low level sensitive. The MODE bit in INTSCR controls the triggering sensitivity of the IRQ pin.

#### Low-Voltage Inhibit (LVI)

The LVI module contains a bandgap reference circuit and comparator. When the LVITRIP bit is cleared, the default state at power-on reset,  $V_{TRIPF}$  is configured for the lower  $V_{DD}$  operating range. The actual trip points are specified in 16.5 5-V DC Electrical Characteristics and 16.8 3-V DC Electrical Characteristics.

Because the default LVI trip point after power-on reset is configured for low voltage operation, a system requiring high voltage LVI operation must set the LVITRIP bit during system initialization.  $V_{DD}$  must be above the LVI trip rising voltage,  $V_{TRIPR}$ , for the high voltage operating range or the MCU will immediately go into LVI reset.

After an LVI reset occurs, the MCU remains in reset until  $V_{DD}$  rises above  $V_{TRIPR}$ . See Chapter 13 System Integration Module (SIM) for the reset recovery sequence.

The output of the comparator controls the state of the LVIOUT flag in the LVI status register (LVISR) and can be used for polling LVI operation when the LVI reset is disabled.

The LVI is enabled out of reset. The following bits located in the configuration register can alter the default conditions.

- Setting the LVI power disable bit, LVIPWRD, disables the LVI.

- Setting the LVI reset disable bit, LVIRSTD, prevents the LVI module from generating a reset.

- Setting the LVI enable in stop mode bit, LVISTOP, enables the LVI to operate in stop mode.

- Setting the LVI trip point bit, LVITRIP, configures the trip point voltage (V<sub>TRIPF</sub>) for the higher V<sub>DD</sub> operating range.

#### 10.3.1 Polled LVI Operation

In applications that can operate at  $V_{DD}$  levels below the  $V_{TRIPF}$  level, software can monitor  $V_{DD}$  by polling the LVIOUT bit. In the configuration register, LVIPWRD must be cleared to enable the LVI module, and LVIRSTD must be set to disable LVI resets.

#### 10.3.2 Forced Reset Operation

In applications that require  $V_{DD}$  to remain above the  $V_{TRIPF}$  level, enabling LVI resets allows the LVI module to reset the MCU when  $V_{DD}$  falls below the  $V_{TRIPF}$  level. In the configuration register, LVIPWRD and LVIRSTD must be cleared to enable the LVI module and to enable LVI resets.

#### 10.3.3 LVI Hysteresis

The LVI has hysteresis to maintain a stable operating condition. After the LVI has triggered (by having  $V_{DD}$  fall below  $V_{TRIPF}$ ), the MCU will remain in reset until  $V_{DD}$  rises above the rising trip point voltage,  $V_{TRIPR}$ . This prevents a condition in which the MCU is continually entering and exiting reset if  $V_{DD}$  is approximately equal to  $V_{TRIPF}$ .  $V_{TRIPF}$  is greater than  $V_{TRIPF}$  by the typical hysteresis voltage,  $V_{HYS}$ .

#### 10.3.4 LVI Trip Selection

LVITRIP in the configuration register selects the LVI protection range. The default setting out of reset is for the low voltage range. Because LVITRIP is in a write-once configuration register, the protection range cannot be changed after initialization.

#### NOTE

The MCU is guaranteed to operate at a minimum supply voltage. The trip point ( $V_{TRIPF}$ ) may be lower than this. See the Electrical Characteristics section for the actual trip point voltages.

#### **Oscillator (OSC) Module**

copy the trim value from \$FFC0 or \$FFC1 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim values, so confirm with your programmer vendor that the trim values at \$FFC0 and \$FFC1 are preserved, or are re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

#### 11.3.2.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, configure OSCOPT[1:0] to external crystal. To help precharge an external crystal oscillator, momentarily configure OSC2 as an output and drive it high for several cycles. This can help the crystal circuit start more robustly.

- Configure OSCOPT[1:0] and ECFS[1:0] according to 11.8.1 Oscillator Status and Control Register. The oscillator module control logic will then enable OSC1 as an external clock input and, if the external crystal option is selected, OSC2 will also be enabled as the clock output. If RC oscillator option is selected, enabling the OSC2 output may change the bus frequency.

- 3. Create a software delay to provide the stabilization time required for the selected clock source (crystal, resonator, RC). A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency; i.e., for a 4-MHz crystal, wait approximately 1 ms.

- 4. After the stabilization delay has elapsed, set ECGON.

After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges. The OSC module then switches to the external clock. Logic provides a coherent transition. The OSC module first sets ECGST and then stops the internal oscillator.

#### 11.3.2.3 External to Internal Clock Switching

After following the procedures to switch to an external clock source, it is possible to go back to the internal source. By clearing the OSCOPT[1:0] bits and clearing the ECGON bit, the external circuit will be disengaged. The bus clock will be derived from the selected internal clock source based on the ICFS[1:0] bits.

#### 11.3.3 External Oscillator

The external oscillator option is designed for use when a clock signal is available in the application to provide a clock source to the MCU. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4. The OSC2EN bit will be forced clear to enable alternative functions on the pin.

#### 11.3.4 XTAL Oscillator

The XTAL oscillator circuit is designed for use with an external crystal or ceramic resonator to provide an accurate clock source. In this configuration, the OSC2 pin is dedicated to the external crystal circuit. The OSC2EN bit has no effect when this clock mode is selected.

In its typical configuration, the XTAL oscillator is connected in a Pierce oscillator configuration, as shown in Figure 11-2. This figure shows only the logical representation of the internal components and may not represent actual circuitry.

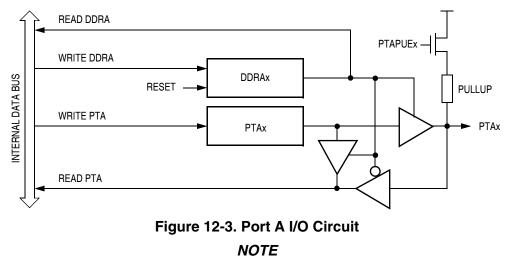

Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading PTA reads the PTAx data latch. When DDRAx is a 0, reading PTA reads the logic level on the PTAx pin. The data latch can always be written, regardless of the state of its data direction bit.

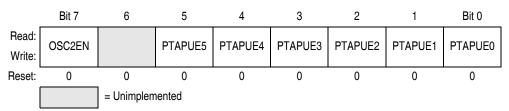

## 12.3.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each of the port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

#### OSC2EN — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

- 1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

- 0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

#### PTAPUE[5:0] — Port A Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port A pins.

- 1 = Corresponding port A pin configured to have internal pullup if its DDRA bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port A pin regardless of the state of its DDRA bit

#### 13.3.1 Bus Timing

In user mode, the internal bus frequency is the oscillator frequency (BUSCLKX4) divided by four.

#### 13.3.2 Clock Start-Up from POR

When the power-on reset module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 BUSCLKX4 cycle POR time out has completed. The IBUS clocks start upon completion of the time out.

#### 13.3.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows BUSCLKX4 to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay time out. This time out is selectable as 4096 or 32 BUSCLKX4 cycles. See 13.7.2 Stop Mode.

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

#### **13.4 Reset and System Initialization**

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE\_FFF (\$FEFE\_FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 13.5 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 13.8 SIM Registers.

#### 13.4.1 External Pin Reset

The  $\overrightarrow{RST}$  pin circuits include an internal pullup device. Pulling the asynchronous  $\overrightarrow{RST}$  pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as  $\overrightarrow{RST}$  is held low for at least the minimum t<sub>RL</sub> time. Figure 13-3 shows the relative timing. The  $\overrightarrow{RST}$  pin function is only available if the RSTEN bit is set in the CONFIG2 register.

| RST                            |  |

|--------------------------------|--|

| ADDRESS BUS / PC ///////////// |  |

Figure 13-3. External Reset Timing

The value in the TIM channel registers determines the pulse width of the PWM output. The pulse width of an 8-bit PWM signal is variable in 256 increments. Writing \$0080 (128) to the TIM channel registers produces a duty cycle of 128/256 or 50%.

#### 14.3.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 14.3.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written to the timer channel (TCHxH:TCHxL).

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- When changing to a longer pulse width, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

#### 14.3.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function, and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin, TCH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active

# NP

#### NOTE

If the reset vector is blank and monitor mode is entered, the chip will see an additional reset cycle after the initial power-on reset (POR). Once the reset vector has been programmed, the traditional method of applying a voltage,  $V_{TST}$ , to  $\overline{IRQ}$  must be used to enter monitor mode.

If monitor mode was entered as a result of the reset vector being blank, the COP is always disabled regardless of the state of IRQ.

If the voltage applied to the  $\overline{IRQ}$  is less than  $V_{TST}$ , the MCU will come out of reset in user mode. Internal circuitry monitors the reset vector fetches and will assert an internal reset if it detects that the reset vectors are erased (\$FF). When the MCU comes out of reset, it is forced into monitor mode without requiring high voltage on the  $\overline{IRQ}$  pin. Once out of reset, the monitor code is initially executing with the internal clock at its default frequency.

If IRQ is held high, all pins will default to regular input port functions except for PTA0 and PTA5 which will operate as a serial communication port and OSC1 input respectively (refer to Figure 15-11). That will allow the clock to be driven from an external source through OSC1 pin.

If IRQ is held low, all pins will default to regular input port function except for PTA0 which will operate as serial communication port. Refer to Figure 15-12.

Regardless of the state of the  $\overline{IRQ}$  pin, it will not function as a port input pin in monitor mode. Bit 2 of the Port A data register will always read 0. The BIH and BIL instructions will behave as if the  $\overline{IRQ}$  pin is enabled, regardless of the settings in the configuration register. See Chapter 5 Configuration Register (CONFIG).

The COP module is disabled in forced monitor mode. Any reset other than a power-on reset (POR) will automatically force the MCU to come back to the forced monitor mode.

#### 15.3.1.3 Monitor Vectors

In monitor mode, the MCU uses different vectors for reset, SWI (software interrupt), and break interrupt than those for user mode. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

#### NOTE

Exiting monitor mode after it has been initiated by having a blank reset vector requires a power-on reset (POR). Pulling RST (when RST pin available) low will not exit monitor mode in this situation.

Table 15-2 summarizes the differences between user mode and monitor mode regarding vectors.

|         | Functions            |        |        |                                     |        |                   |  |  |  |

|---------|----------------------|--------|--------|-------------------------------------|--------|-------------------|--|--|--|

| Modes   | Reset<br>Vector High |        |        | Break SWI<br>Vector Low Vector High |        | SWI<br>Vector Low |  |  |  |

| User    | \$FFFE               | \$FFFF | \$FFFC | \$FFFD                              | \$FFFC | \$FFFD            |  |  |  |

| Monitor | \$FEFE               | \$FEFF | \$FEFC | \$FEFD                              | \$FEFC | \$FEFD            |  |  |  |

#### Table 15-2. Mode Difference

**Ordering Information and Mechanical Specifications**

## 17.3 Orderable Part Numbering System

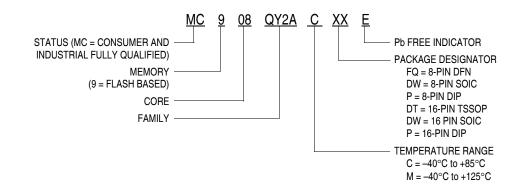

## 17.3.1 Consumer and Industrial Orderable Part Numbering System

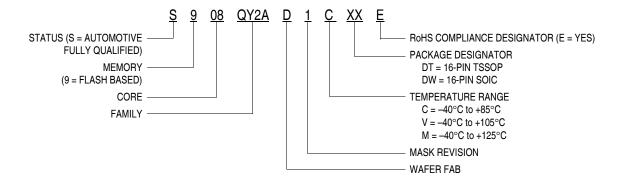

#### 17.3.2 Automotive Orderable Part Number System

## **17.4 Mechanical Drawings**

The following pages contain mechanical specifications for MC68HC908QY4/QTA series package options. See Table 17-3 for the document numbers that correspond to each package type.

| Table 17-3. | Package I | nformation |

|-------------|-----------|------------|

|-------------|-----------|------------|

| Pin Count | Туре  | Designator | Document No. |

|-----------|-------|------------|--------------|

| 8         | PDIP  | Р          | 98ASB42420B  |

| 8         | SOIC  | DW         | 98ASH70107A  |

| 8         | DFN   | FQ         | 98ARL10557D  |

| 16        | PDIP  | Р          | 98ASB42431B  |

| 16        | SOIC  | DW         | 98ASB42567B  |

| 16        | TSSOP | DT         | 98ASH70247A  |

**Mechanical Drawings**

Case 751G page 2 of 2

## Appendix A 908QTA/QYxA Conversion Guidelines

## A.1 Introduction

This engineering bulletin describes the 908QTA/QYxA. The 908QTA/QYxA is an enhanced device intended to replace the 908QT/QYx series of devices (referred to as the QY Classic in this document). Customer requests have led to the advanced design of the QYxA that has added adaptability, new features, and contains lead-free packaging.

This document:

- Provides information needed to convert from QY Classic to the enhanced QYxA

- Highlights the benefits of making this change

Sections:

- A.2 Benefits of the Enhanced QYxA

- A.3 Conversion Considerations

- A.4 Code Changes Checklist

- A.5 Development Tools

- A.6 Differences in Packaging

## A.2 Benefits of the Enhanced QYxA

The QYxA contains new and enhanced modules that add more flexibility and new features to the QY Classic. These benefits can improve the operation of an application or lead to new features for an application. For more information regarding these features refer to the QYxA data sheet (Freescale document order number MC68HC908QYxA).

#### A.2.1 New Analog-to-Digital Converter Module (ADC)

The QYxA contains a 10-bit ADC which replaces the 8-bit ADC on the QY Classic. This module allows both 10-bit and 8-bit conversion modes. The increased precision for ADC readings can be very useful in many applications.

Features of the ADC new 10-bit module include:

- There are two new ADC channels that have been placed on PTB0 and PTB1 allowing added flexibility especially when debugging in Monitor Mode.

- A limitation of QY Classic debugging is that access to the ADC channels is limited because many of the QY Classic pins are multiplexed. Having extra ADC channels on the PTB pins resolves this limitation.

- The ADC that is on the QYxA can operate while the MCU is in stop mode allowing lower power operation. This also adds a lower noise environment for precise ADC results.

- Enabling an ADC channel no longer overrides the digital I/O function of the associated pin. To prevent the digital I/O from interfering with the ADC read of the pin, the data direction bit associated with the port pin must be set as input.

- Finally, the new ADC can be configured to select two different reference clock sources:

- The internal bus x 4

- An internal asynchronous source

The internal asynchronous clock source allows the ADC to be clocked for operation in stop mode.

#### A.2.1.1 Registers Affected

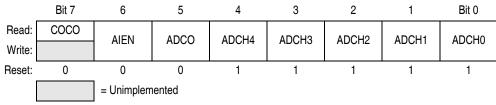

Figure A-1. ADC10 Status and Control Register (ADSCR)

The ADCHx bits can be used to select additional ADC channels or bandgap measurement.

|        | Bit 7           | 6 | 5 | 4 | 3 | 2 | 1   | Bit 0 |

|--------|-----------------|---|---|---|---|---|-----|-------|

| Read:  | 0               | 0 | 0 | 0 | 0 | 0 | AD9 | AD8   |

| Write: |                 |   |   |   |   |   |     |       |

| Reset: | 0               | 0 | 0 | 0 | 0 | 0 | 0   | 0     |

|        | = Unimplemented |   |   |   |   |   |     |       |

Figure A-2. ADC10 Data Register High (ADRH), 10-Bit Mode

10-bit ADC uses the new ADRH register for the upper 2 bits.

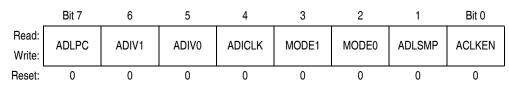

Figure A-3. ADC10 Clock Register (ADCLK)

A long sample time option has been added to conserve power at the expense of longer conversion times. This option is selected using the new ADLSMP bit in the ADCLK register. (The bit location was previously reserved.)

The ADC will now run in stop mode if the ACLKEN bit is set to enable the asynchronous clock inside the ADC module. Utilizing stop mode for an ADC conversion gives the quietest operating mode to get extremely accurate ADC readings. (This bit location now used by ACLKEN was reserved — it always read as a 0 and writes to that location had no affect.)

## A.2.2 Enhanced Oscillator Module (OSC)

The QYxA contains a much enhanced oscillator module that allows more options than the QYx Classic.

- The ICFS bits in the Oscillator Status and Control Register (OSCSC) allow the Internal Oscillator to be configured for 1-, 2-, or 3.2-MHz operation. Also, the ECFS bits in the same register allow a low, medium, or high crystal frequency range to be selected for the source of the system clock. With this option you can choose to use a 32-kHz (low range) or a 16-MHz (high range) crystal.

- Another improvement to the Oscillator Module design is that you can switch between internal

oscillator and external oscillator options at any time. For example, if you wanted the low power

advantage of running from a 32-kHz crystal but still needed some processing power to perform

math calculations you could switch back and forth between internal and external clock. The same

is true for switching between 1-, 2-, and 3.2-MHz internal oscillator options.

#### A.2.2.1 Registers Affected

|        | Bit 7           | 6       | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |

|--------|-----------------|---------|-------|-------|-------|-------|-------|-------|--|

| Read:  | OSCOPT1         | OSCOPT0 | ICFS1 | ICFS0 | ECFS1 | ECFS0 | ECGON | ECGST |  |

| Write: | 0300F11         | 0300F10 | 10131 | 10-30 | LOFST | LOFSU | LCGON |       |  |

| Reset: | 0               | 0       | 1     | 0     | 0     | 0     | 0     | 0     |  |

|        | = Unimplemented |         |       |       |       |       |       |       |  |

#### Figure A-4. Oscillator Status and Control Register (OSCSC)

The OSCOPT bits are no longer in the CONFIG2 register and now reside in the OSCSC register. Also, the ICFSx and ECFSx bits now reside in this register.

The IFS bits are used to select different Internal Oscillator speeds.

The ECFS bits are used to select the range of crystal that should be used to provide the reference clock.