Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

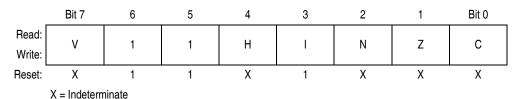

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HC08                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 8MHz                                                        |

| Connectivity               | -                                                           |

| Peripherals                | LVD, POR, PWM                                               |

| Number of I/O              | 13                                                          |

| Program Memory Size        | 1.5KB (1.5K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 128 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 6x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                              |

| Supplier Device Package    | 16-SOIC                                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908qy2acdwer |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

\_\_\_\_\_

| Chapter 1 General Description                                 |

|---------------------------------------------------------------|

| Chapter 2 Memory                                              |

| Chapter 3 Analog-to-Digital Converter (ADC10) Module          |

| Chapter 4 Auto Wakeup Module (AWU)51                          |

| Chapter 5 Configuration Register (CONFIG)57                   |

| Chapter 6 Computer Operating Properly (COP)61                 |

| Chapter 7 Central Processor Unit (CPU)65                      |

| Chapter 8 External Interrupt (IRQ)77                          |

| Chapter 9 Keyboard Interrupt Module (KBI)83                   |

| Chapter 10 Low-Voltage Inhibit (LVI)                          |

| Chapter 11 Oscillator (OSC) Module                            |

| Chapter 12 Input/Output Ports (PORTS)103                      |

| Chapter 13 System Integration Module (SIM)109                 |

| Chapter 14 Timer Interface Module (TIM)125                    |

| Chapter 15 Development Support                                |

| Chapter 16 Electrical Specifications155                       |

| Chapter 17 Ordering Information and Mechanical Specifications |

| Appendix A 908QTA/QYxA Conversion Guidelines191               |

#### Table of Contents

| 8.4   | Interrupts 8                         | 30 |

|-------|--------------------------------------|----|

|       | Low-Power Modes                      |    |

|       | Wait Mode                            |    |

| 8.5.2 | Stop Mode                            | 30 |

| 8.6   | IRQ Module During Break Interrupts 8 | 30 |

| 8.7   | I/O Signals                          | 30 |

| 8.7.1 | IRQ Input Pins (IRQ)                 | 30 |

| 8.8   | Registers                            | 31 |

# Chapter 9 Keyboard Interrupt Module (KBI)

| 9.1     | Introduction                                   | 33 |

|---------|------------------------------------------------|----|

| 9.2     | Features                                       | 33 |

| 9.3     | Functional Description                         | 33 |

| 9.3.1   | Keyboard Operation                             | 33 |

| 9.3.1.1 | MODEK = 1                                      | 34 |

| 9.3.1.2 | MODEK = 0                                      | 35 |

| 9.3.2   | Keyboard Initialization                        | 36 |

| 9.4     | Interrupts                                     | 36 |

| 9.5     | Low-Power Modes                                | 36 |

| 9.5.1   | Wait Mode                                      | 36 |

| 9.5.2   | Stop Mode                                      | 36 |

| 9.6     | KBI During Break Interrupts                    | 36 |

| 9.7     | I/O Signals                                    | 37 |

| 9.7.1   | KBI Input Pins (KBIx:KBI0)                     | 37 |

| 9.8     | Registers 8                                    |    |

| 9.8.1   | Keyboard Status and Control Register (KBSCR)   |    |

| 9.8.2   | Keyboard Interrupt Enable Register (KBIER)     |    |

| 9.8.3   | Keyboard Interrupt Polarity Register (KBIPR) 8 | 38 |

# Chapter 10 Low-Voltage Inhibit (LVI)

| 10.1   | Introduction ٤          | 39             |

|--------|-------------------------|----------------|

| 10.2   | Features                | 39             |

| 10.3   | Functional Description  |                |

| 10.3.1 | Polled LVI Operation    |                |

| 10.3.2 | Forced Reset Operation. |                |

| 10.3.3 | LVI Hysteresis          | <del>)</del> 0 |

| 10.3.4 | LVI Trip Selection      |                |

| 10.4   | LVI Interrupts          | <del>)</del> 1 |

| 10.5   | Low-Power Modes         |                |

| 10.5.1 | Wait Mode               | -              |

| 10.5.2 |                         |                |

| 10.6   | Registers               | <del>)</del> 1 |

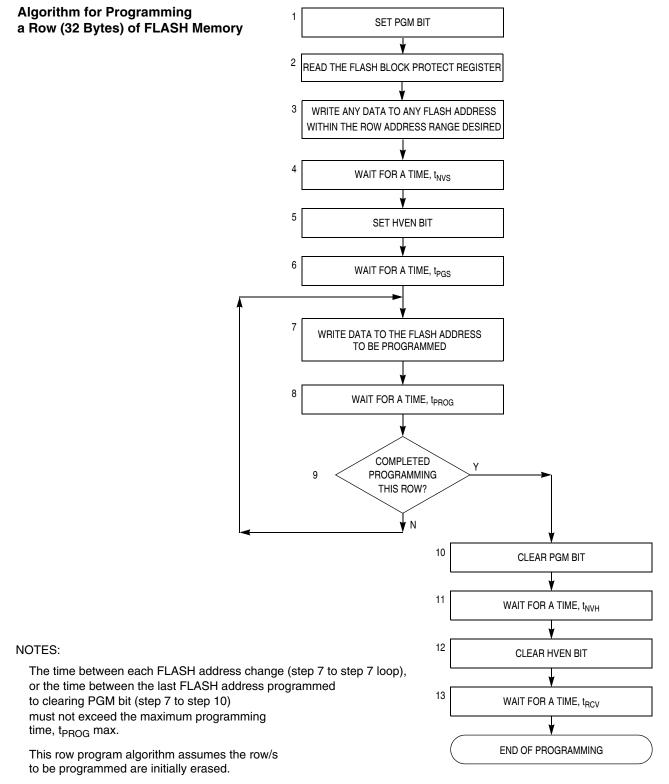

#### FLASH Memory (FLASH)

#### Analog-to-Digital Converter (ADC10) Module

# 3.4 Interrupts

When AIEN is set, the ADC10 is capable of generating a CPU interrupt after each conversion. A CPU interrupt is generated when the conversion completes (indicated by COCO being set). COCO will set at the end of a conversion regardless of the state of AIEN.

# 3.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 3.5.1 Wait Mode

The ADC10 will continue the conversion process and will generate an interrupt following a conversion if AIEN is set. If the ADC10 is not required to bring the MCU out of wait mode, ensure that the ADC10 is not in continuous conversion mode by clearing ADCO in the ADC10 status and control register before executing the WAIT instruction. In single conversion mode the ADC10 automatically enters a low-power state when the conversion is complete. It is not necessary to set the channel select bits (ADCH[4:0]) to all 1s to enter a low power state.

### 3.5.2 Stop Mode

If ACLKEN is clear, executing a STOP instruction will abort the current conversion and place the ADC10 in a low-power state. Upon return from stop mode, a write to ADSCR is required to resume conversions, and the result stored in ADRH and ADRL will represent the last completed conversion until the new conversion completes.

If ACLKEN is set, the ADC10 continues normal operation during stop mode. The ADC10 will continue the conversion process and will generate an interrupt following a conversion if AIEN is set. If the ADC10 is not required to bring the MCU out of stop mode, ensure that the ADC10 is not in continuous conversion mode by clearing ADCO in the ADC10 status and control register before executing the STOP instruction. In single conversion mode the ADC10 automatically enters a low-power state when the conversion is complete. It is not necessary to set the channel select bits (ADCH[4:0]) to all 1s to enter a low-power state.

If ACLKEN is set, a conversion can be initiated while in stop using the external hardware trigger ADEXTCO when in external convert mode. The ADC10 will operate in a low-power mode until the trigger is asserted, at which point it will perform a conversion and assert the interrupt when complete (if AIEN is set).

# 3.6 ADC10 During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. BCFE in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the

**Central Processor Unit (CPU)**

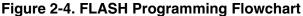

### 7.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

Figure 7-6. Condition Code Register (CCR)

### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

1 = Overflow

0 = No overflow

### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

1 = Carry between bits 3 and 4

0 = No carry between bits 3 and 4

#### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

#### NOTE

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first. A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

1 = Negative result

0 = Non-negative result

# External Interrupt (IRQ)

PTA[0:5]: Higher current sink and source capability

PTB[0:7]: Not available on 8-pin devices

### Figure 8-1. Block Diagram Highlighting IRQ Block and Pin

When set, the IMASK bit in INTSCR masks the IRQ interrupt request. A latched interrupt request is not presented to the interrupt priority logic unless IMASK is clear.

#### NOTE

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including the IRQ interrupt request.

A falling edge on the IRQ pin can latch an interrupt request into the IRQ latch. An IRQ vector fetch, software clear, or reset clears the IRQ latch.

External Interrupt (IRQ)

# 9.7 I/O Signals

The KBI module can share its pins with the general-purpose I/O pins. See Figure 9-1 for the port pins that are shared.

### 9.7.1 KBI Input Pins (KBIx:KBI0)

Each KBI pin is independently programmable as an external interrupt source. KBI pin polarity can be controlled independently. Each KBI pin when enabled will automatically configure the appropriate pullup/pulldown device based on polarity.

## 9.8 Registers

The following registers control and monitor operation of the KBI module:

- KBSCR (keyboard interrupt status and control register)

- KBIER (keyboard interrupt enable register)

- KBIPR (keyboard interrupt polarity register)

### 9.8.1 Keyboard Status and Control Register (KBSCR)

Features of the KBSCR:

- Flags keyboard interrupt requests

- Acknowledges keyboard interrupt requests

- Masks keyboard interrupt requests

- Controls keyboard interrupt triggering sensitivity

|        | Bit 7           | 6 | 5 | 4 | 3    | 2    | 1       | Bit 0 |  |

|--------|-----------------|---|---|---|------|------|---------|-------|--|

| Read:  | 0               | 0 | 0 | 0 | KEYF | 0    | IMASKK  | MODEK |  |

| Write: |                 |   |   |   |      | ACKK | INAGINI | WODEN |  |

| Reset: | 0               | 0 | 0 | 0 | 0    | 0    | 0       | 0     |  |

|        | = Unimplemented |   |   |   |      |      |         |       |  |

#### Figure 9-3. Keyboard Status and Control Register (KBSCR)

#### Bits 7–4 — Not used

KEYF — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending.

- 1 = Keyboard interrupt pending

- 0 = No keyboard interrupt pending

#### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the KBI request. ACKK always reads 0.

#### IMASKK— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the KBI latch from generating interrupt requests.

- 1 = Keyboard interrupt requests disabled

- 0 = Keyboard interrupt requests enabled

#### MODEK — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins.

- 1 = Keyboard interrupt requests on edge and level

- 0 = Keyboard interrupt requests on edge only

# 11.6 OSC During Break Interrupts

There are no status flags associated with the OSC module.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

## 11.7 I/O Signals

The OSC shares its pins with general-purpose input/output (I/O) port pins. See Figure 11-1 for port location of these shared pins.

### 11.7.1 Oscillator Input Pin (OSC1)

The OSC1 pin is an input to the crystal oscillator amplifier, an input to the RC oscillator circuit, or an input from an external clock source.

When the OSC is configured for internal oscillator, the OSC1 pin can be used as a general-purpose input/output (I/O) port pin or other alternative pin function.

#### 11.7.2 Oscillator Output Pin (OSC2)

For the XTAL oscillator option, the OSC2 pin is the output of the crystal oscillator amplifier.

When the OSC is configured for internal oscillator, external clock, or RC, the OSC2 pin can be used as a general-purpose I/O port pin or other alternative pin function. When the oscillator is configured for internal or RC, the OSC2 pin can be used to output BUSCLKX4.

| Option                                     | OSC2 Pin Function                                                                                                      |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| XTAL oscillator                            | Inverting OSC1                                                                                                         |

| External clock                             | General-purpose I/O or alternative pin function                                                                        |

| Internal oscillator<br>or<br>RC oscillator | Controlled by OSC2EN bit<br>OSC2EN = 0: General-purpose I/O or alternative pin function<br>OSC2EN = 1: BUSCLKX4 output |

Table 11-1. OSC2 Pin Function

#### System Integration Module (SIM)

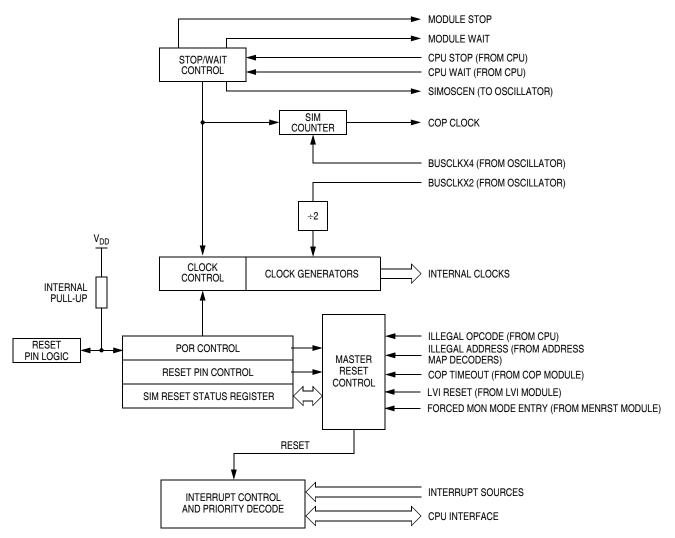

Figure 13-1. SIM Block Diagram

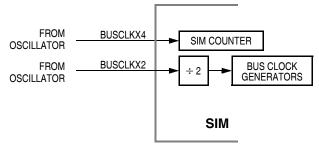

# **13.3 SIM Bus Clock Control and Generation**

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 13-2.

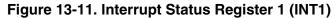

#### 13.6.2.1 Interrupt Status Register 1

|        | Bit 7 | 6          | 5   | 4   | 3   | 2   | 1 | Bit 0 |

|--------|-------|------------|-----|-----|-----|-----|---|-------|

| Read:  | IF6   | IF5        | IF4 | IF3 | IF2 | IF1 | 0 | 0     |

| Write: | R     | R          | R   | R   | R   | R   | R | R     |

| Reset: | 0     | 0          | 0   | 0   | 0   | 0   | 0 | 0     |

|        | R     | = Reserved |     |     |     |     |   |       |

#### IF1–IF6 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

1 = Interrupt request present

0 = No interrupt request present

#### Bit 0, 1 — Always read 0

#### 13.6.2.2 Interrupt Status Register 2

|        | Bit 7 | 6          | 5    | 4    | 3    | 2   | 1   | Bit 0 |

|--------|-------|------------|------|------|------|-----|-----|-------|

| Read:  | IF14  | IF13       | IF12 | IF11 | IF10 | IF9 | IF8 | IF7   |

| Write: | R     | R          | R    | R    | R    | R   | R   | R     |

| Reset: | 0     | 0          | 0    | 0    | 0    | 0   | 0   | 0     |

| [      | R     | = Reserved |      |      |      |     |     |       |

Figure 13-12. Interrupt Status Register 2 (INT2)

#### IF7–IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3.

1 = Interrupt request present

0 = No interrupt request present

#### 13.6.2.3 Interrupt Status Register 3

|        | Bit 7 | 6          | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|--------|-------|------------|------|------|------|------|------|-------|

| Read:  | IF22  | IF21       | IF20 | IF19 | IF18 | IF17 | IF16 | IF15  |

| Write: | R     | R          | R    | R    | R    | R    | R    | R     |

| Reset: | 0     | 0          | 0    | 0    | 0    | 0    | 0    | 0     |

|        | R     | = Reserved |      |      |      |      |      |       |

|        |       | _          |      | _    |      |      |      |       |

#### Figure 13-13. Interrupt Status Register 3 (INT3)

#### IF15–IF22 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

1 = Interrupt request present

0 = No interrupt request present

# Chapter 14 Timer Interface Module (TIM)

# 14.1 Introduction

This section describes the timer interface module (TIM). The TIM module is a 2-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions.

The TIM module shares its pins with general-purpose input/output (I/O) port pins. See Figure 14-1 for port location of these shared pins.

# 14.2 Features

•

Features include the following:

- Two input capture/output compare channels

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Buffered and unbuffered output compare pulse-width modulation (PWM) signal generation

- Programmable clock input

- 7-frequency internal bus clock prescaler selection

- External clock input pin if available, See Figure 14-1

- Free-running or modulo up-count operation

- Toggle any channel pin on overflow

- Counter stop and reset bits

# 14.3 Functional Description

Figure 14-2 shows the structure of the TIM. The central component of the TIM is the 16-bit counter that can operate as a free-running counter or a modulo up-counter. The counter provides the timing reference for the input capture and output compare functions. The counter modulo registers, TMODH:TMODL, control the modulo value of the counter. Software can read the counter value, TCNTH:TCNTL, at any time without affecting the counting sequence.

The two TIM channels are programmable independently as input capture or output compare channels.

### 14.3.1 TIM Counter Prescaler

The TIM clock source is one of the seven prescaler outputs or the external clock input pin, TCLK if available. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register (TSC) select the clock source.

**Timer Interface Module (TIM)**

# 14.7 I/O Signals

The TIM module can share its pins with the general-purpose I/O pins. See Figure 14-1 for the port pins that are shared.

# 14.7.1 TIM Channel I/O Pins (TCH1:TCH0)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. TCH0 can be configured as buffered output compare or buffered PWM pin.

# 14.7.2 TIM Clock Pin (TCLK)

TCLK is an external clock input that can be the clock source for the counter instead of the prescaled internal bus clock. Select the TCLK input by writing 1s to the three prescaler select bits, PS[2:0]. 14.8.1 TIM Status and Control Register The minimum TCLK pulse width is specified in the Timer Interface Module Characteristics table in the Electricals section. The maximum TCLK frequency is the least of 4 MHz or bus frequency ÷ 2.

# 14.8 Registers

The following registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM control registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

### 14.8.1 TIM Status and Control Register

The TIM status and control register (TSC) does the following:

- Enables TIM overflow interrupts

- Flags TIM overflows

- Stops the counter

- Resets the counter

- Prescales the counter clock

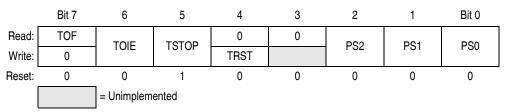

#### Figure 14-4. TIM Status and Control Register (TSC)

#### TOF — TIM Overflow Flag Bit

This read/write flag is set when the counter reaches the modulo value programmed in the TIM counter modulo registers. Clear TOF by reading the TSC register when TOF is set and then writing a 0 to TOF.

Timer Interface Module (TIM)

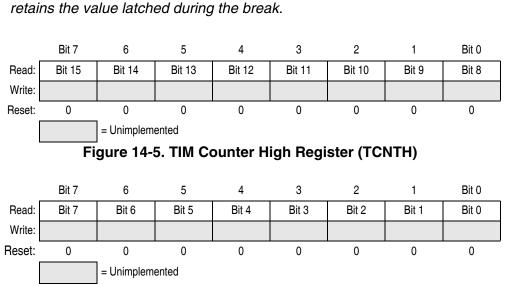

## 14.8.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

> **NOTE** If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL

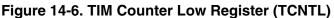

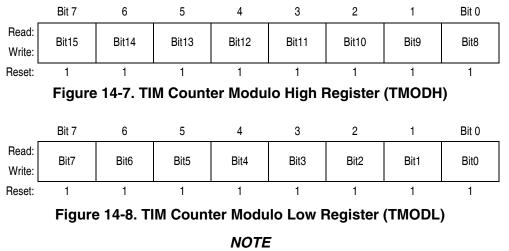

### 14.8.3 TIM Counter Modulo Registers

The read/write TIM modulo registers contain the modulo value for the counter. When the counter reaches the modulo value, the overflow flag (TOF) becomes set, and the counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIM counter modulo registers.

Reset the counter before writing to the TIM counter modulo registers.

#### **Timer Interface Module (TIM)**

Setting MS0B causes the contents of TSC1 to be ignored by the TIM and reverts TCH1 to general-purpose I/O.

1 = Buffered output compare/PWM operation enabled

0 = Buffered output compare/PWM operation disabled

### MSxA — Mode Select Bit A

When ELSxB:A  $\neq$  00, this read/write bit selects either input capture operation or unbuffered output compare/PWM operation. See Table 14-2.

1 = Unbuffered output compare/PWM operation

0 = Input capture operation

When ELSxB:A = 00, this read/write bit selects the initial output level of the TCHx pin (see Table 14-2).

1 = Initial output level low

0 = Initial output level high

#### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

#### ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to an I/O port, and pin TCHx is available as a general-purpose I/O pin. Table 14-2 shows how ELSxB and ELSxA work.

| MSxB | MSxA | ELSxB | ELSxA | Mode            | Configuration                                     |  |  |

|------|------|-------|-------|-----------------|---------------------------------------------------|--|--|

| Х    | 0    | 0     | 0     |                 | Pin under port control; initial output level high |  |  |

| Х    | 1    | 0     | 0     | Output preset   | Pin under port control; initial output level low  |  |  |

| 0    | 0    | 0     | 1     |                 | Capture on rising edge only                       |  |  |

| 0    | 0    | 1     | 0     | Input capture   | Capture on falling edge only                      |  |  |

| 0    | 0    | 1     | 1     |                 | Capture on rising or falling edge                 |  |  |

| 0    | 1    | 0     | 0     |                 | Software compare only                             |  |  |

| 0    | 1    | 0     | 1     | Output compare  | Toggle output on compare                          |  |  |

| 0    | 1    | 1     | 0     | or PWM          | Clear output on compare                           |  |  |

| 0    | 1    | 1     | 1     |                 | Set output on compare                             |  |  |

| 1    | Х    | 0     | 1     | Buffered output | Toggle output on compare                          |  |  |

| 1    | Х    | 1     | 0     | compare or      | Clear output on compare                           |  |  |

| 1    | Х    | 1     | 1     | buffered PWM    | Set output on compare                             |  |  |

### Table 14-2. Mode, Edge, and Level Selection

### NOTE

After initially enabling a TIM channel register for input capture operation and selecting the edge sensitivity, clear CHxF to ignore any erroneous edge detection flags.

# NP

### NOTE

If the reset vector is blank and monitor mode is entered, the chip will see an additional reset cycle after the initial power-on reset (POR). Once the reset vector has been programmed, the traditional method of applying a voltage,  $V_{TST}$ , to  $\overline{IRQ}$  must be used to enter monitor mode.

If monitor mode was entered as a result of the reset vector being blank, the COP is always disabled regardless of the state of IRQ.

If the voltage applied to the  $\overline{IRQ}$  is less than  $V_{TST}$ , the MCU will come out of reset in user mode. Internal circuitry monitors the reset vector fetches and will assert an internal reset if it detects that the reset vectors are erased (\$FF). When the MCU comes out of reset, it is forced into monitor mode without requiring high voltage on the  $\overline{IRQ}$  pin. Once out of reset, the monitor code is initially executing with the internal clock at its default frequency.

If IRQ is held high, all pins will default to regular input port functions except for PTA0 and PTA5 which will operate as a serial communication port and OSC1 input respectively (refer to Figure 15-11). That will allow the clock to be driven from an external source through OSC1 pin.

If IRQ is held low, all pins will default to regular input port function except for PTA0 which will operate as serial communication port. Refer to Figure 15-12.

Regardless of the state of the  $\overline{IRQ}$  pin, it will not function as a port input pin in monitor mode. Bit 2 of the Port A data register will always read 0. The BIH and BIL instructions will behave as if the  $\overline{IRQ}$  pin is enabled, regardless of the settings in the configuration register. See Chapter 5 Configuration Register (CONFIG).

The COP module is disabled in forced monitor mode. Any reset other than a power-on reset (POR) will automatically force the MCU to come back to the forced monitor mode.

### 15.3.1.3 Monitor Vectors

In monitor mode, the MCU uses different vectors for reset, SWI (software interrupt), and break interrupt than those for user mode. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

#### NOTE

Exiting monitor mode after it has been initiated by having a blank reset vector requires a power-on reset (POR). Pulling RST (when RST pin available) low will not exit monitor mode in this situation.

Table 15-2 summarizes the differences between user mode and monitor mode regarding vectors.

|         | Functions            |                     |                      |                     |                    |                   |  |  |  |  |

|---------|----------------------|---------------------|----------------------|---------------------|--------------------|-------------------|--|--|--|--|

| Modes   | Reset<br>Vector High | Reset<br>Vector Low | Break<br>Vector High | Break<br>Vector Low | SWI<br>Vector High | SWI<br>Vector Low |  |  |  |  |

| User    | \$FFFE               | \$FFFF              | \$FFFC               | \$FFFD              | \$FFFC             | \$FFFD            |  |  |  |  |

| Monitor | \$FEFE               | \$FEFF              | \$FEFC               | \$FEFD              | \$FEFC             | \$FEFD            |  |  |  |  |

#### Table 15-2. Mode Difference

#### **Electrical Specifications**

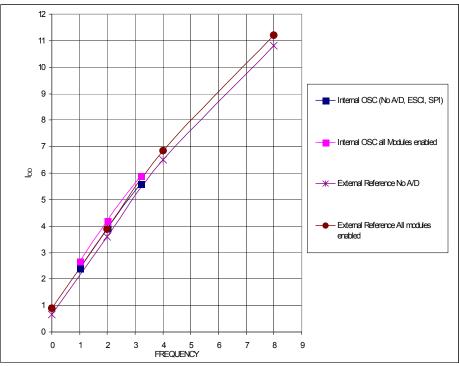

Figure 16-9. Typical 5-Volt Run Current versus Bus Frequency (25•C)

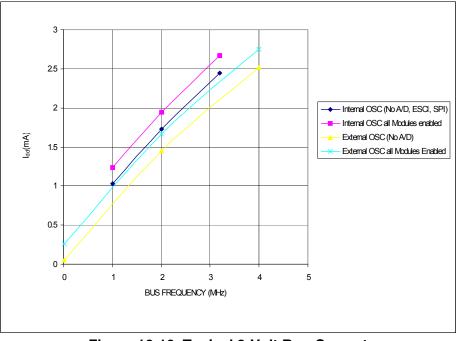

Figure 16-10. Typical 3-Volt Run Current versus Bus Frequency (25•C)

**Electrical Specifications**

# **16.15 Memory Characteristics**

| Characteristic                                      | Symbol                           | Min        | Тур    | Max        | Unit   |

|-----------------------------------------------------|----------------------------------|------------|--------|------------|--------|

| RAM data retention voltage (1)                      | V <sub>RDR</sub>                 | 1.3        | —      | _          | V      |

| FLASH program bus clock frequency                   | _                                | 1          | —      |            | MHz    |

| FLASH PGM/ERASE supply voltage (V <sub>DD</sub> )   | V <sub>PGM/ERASE</sub>           | 2.7        | —      | 5.5        | V      |

| FLASH read bus clock frequency                      | f <sub>Read</sub> <sup>(2)</sup> | 0          | _      | 8 M        | Hz     |

| FLASH page erase time<br><1 K cycles<br>>1 K cycles | t <sub>Erase</sub>               | 0.9<br>3.6 | 1<br>4 | 1.1<br>5.5 | ms     |

| FLASH mass erase time                               | t <sub>MErase</sub>              | 4          | —      |            | ms     |

| FLASH PGM/ERASE to HVEN setup time                  | t <sub>NVS</sub>                 | 10         | —      | _          | μs     |

| FLASH high-voltage hold time                        | t <sub>NVH</sub>                 | 5          | —      |            | μs     |

| FLASH high-voltage hold time (mass erase)           | t <sub>NVHL</sub>                | 100        | —      | _          | μs     |

| FLASH program hold time                             | t <sub>PGS</sub>                 | 5          | —      | _          | μs     |

| FLASH program time                                  | t <sub>PROG</sub>                | 30         | —      | 40         | μs     |

| FLASH return to read time                           | t <sub>RCV</sub> <sup>(3)</sup>  | 1          | —      | _          | μs     |

| FLASH cumulative program hv period                  | t <sub>HV</sub> <sup>(4)</sup>   | —          | —      | 4          | ms     |

| FLASH endurance <sup>(5)</sup>                      | _                                | 10 k       | 100 k  | _          | Cycles |

| FLASH data retention time <sup>(6)</sup>            | _                                | 15         | 100    | _          | Years  |

1. Values are based on characterization results, not tested in production.

2. f<sub>Read</sub> is defined as the frequency range for which the FLASH memory can be read.

3. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

4. t<sub>HV</sub> is defined as the cumulative high voltage programming time to the same row before next erase.

t<sub>HV</sub> must satisfy this condition: t<sub>NVS</sub> + t<sub>NVH</sub> + t<sub>PGS</sub> + (t<sub>PROG</sub> x 32) ≤ t<sub>HV</sub> maximum.

Typical endurance was evaluated for this product family. For additional information on how Freescale Semiconductor defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

6. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines Typical Data Retention, please refer to Engineering Bulletin EB618.

Ordering Information and Mechanical Specifications

Case 626 page 2 of 3

**Mechanical Drawings**

Case 948F page 2 of 3