## NXP USA Inc. - MC908QY4ACDTER Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 4KB (4K × 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qy4acdter |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 1 General Description

# 1.1 Introduction

The MC68HC908QY4A is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

| Device        | FLASH<br>Memory Size | ADC               | Pin<br>Count |

|---------------|----------------------|-------------------|--------------|

| MC68HC908QT1A | 1536 bytes           | —                 | 8 pins       |

| MC68HC908QT2A | 1536 bytes           | 6 channel, 10 bit | 8 pins       |

| MC68HC908QT4A | 4096 bytes           | 6 channel, 10 bit | 8 pins       |

| MC68HC908QY1A | 1536 bytes           | —                 | 16 pins      |

| MC68HC908QY2A | 1536 bytes           | 6 channel, 10 bit | 16 pins      |

| MC68HC908QY4A | 4096 bytes           | 6 channel, 10 bit | 16 pins      |

## Table 1-1. Summary of Device Variations

# 1.2 Features

Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- Software selectable 1 MHz, 2 MHz, or 3.2 MHz internal bus operation

- 8-bit trim capability

- ±25% untrimmed

- Trimmable to approximately 0.4%<sup>(1)</sup>

- Software selectable crystal oscillator range, 32–100 kHz, 1–8 MHz and 8–32 MHz

- Software configurable input clock from either internal or external source

- Auto wakeup from STOP capability using dedicated internal 32-kHz RC or bus clock source

- On-chip in-application programmable FLASH memory

- Internal program/erase voltage generation

- Monitor ROM containing user callable program/erase routines

- FLASH security<sup>(2)</sup>

<sup>1.</sup> See 16.11 Oscillator Characteristics for internal oscillator specifications

<sup>2.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Memory

| Addr.  | Register Name                                          |                 | Bit 7           | 6      | 5      | 4      | 3          | 2        | 1         | Bit 0 |

|--------|--------------------------------------------------------|-----------------|-----------------|--------|--------|--------|------------|----------|-----------|-------|

| \$FE00 | Break Status Register<br>(BSR)                         | Read:<br>Write: | R               | R      | R      | R      | R          | R        | SBSW<br>0 | R     |

|        | See page 143.                                          | Reset:          |                 |        |        |        |            |          | 0         |       |

|        | SIM Reset Status Register                              | Read:           | POR             | PIN    | COP    | ILOP   | ILAD       | MODRST   | LVI       | 0     |

| \$FE01 | (SRSR)                                                 | Write:          |                 |        |        |        |            |          |           |       |

|        | See page 122.                                          | POR:            | 1               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

|        | Break Auxiliary                                        | Read:           | 0               | 0      | 0      | 0      | 0          | 0        | 0         | PDOOD |

| \$FE02 | Register (BRKAR)                                       | Write:          |                 |        |        |        |            |          |           | BDCOP |

|        | See page 143.                                          | Reset:          | 0               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

| \$FE03 | Break Flag Control<br>Register (BFCR)                  | Read:<br>Write: | BCFE            | R      | R      | R      | R          | R        | R         | R     |

|        | See page 143.                                          | Reset:          | 0               | •      | •      |        |            |          |           |       |

|        | Interrupt Status Register 1                            | Read:           | IF6             | IF5    | IF4    | IF3    | IF2        | IF1      | 0         | 0     |

| \$FE04 | (INT1)                                                 | Write:          | R               | R      | R      | R      | R          | R        | R         | R     |

|        | See page 119.                                          | Reset:          | 0               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

|        | Interrupt Status Register 2                            | Read:           | IF14            | IF13   | IF12   | IF11   | IF10       | IF9      | IF8       | IF7   |

| \$FE05 | (INT2)                                                 | Write:          | R               | R      | R      | R      | R          | R        | R         | R     |

|        | See page 119.                                          | Reset:          | 0               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

|        | Interrupt Status Register 3                            | Read:           | IF22            | IF21   | IF20   | IF19   | IF18       | IF17     | IF16      | IF15  |

| \$FE06 | (INT3)                                                 | Write:          | R               | R      | R      | R      | R          | R        | R         | R     |

|        | See page 119.                                          | Reset:          | 0               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

| \$FE07 | Reserved                                               |                 |                 |        |        |        |            |          |           |       |

|        |                                                        | Read:           | 0               | 0      | 0      | 0      |            |          |           |       |

| \$FE08 | FLASH Control Register<br>(FLCR)                       | Write:          | 0               | , °    |        |        | HVEN       | MASS     | ERASE     | PGM   |

|        | See page 29.                                           | Reset:          | 0               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

| \$FE09 | Break Address High<br>Register (BRKH)<br>See page 142. | Read:<br>Write: | Bit 15          | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10   | Bit 9     | Bit 8 |

|        |                                                        | Reset:          | 0               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

| \$FE0A | Break Address low<br>Register (BRKL)<br>See page 142.  | Read:<br>Write: | Bit 7           | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2    | Bit 1     | Bit 0 |

|        |                                                        | Reset:          | 0               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

|        | Break Status and Control<br>Register (BRKSCR)          | Read:           |                 |        | 0      | 0      | 0          | 0        | 0         | 0     |

| \$FE0B |                                                        | Write:          | BRKE            | BRKA   |        |        |            |          |           |       |

|        | See page 143.                                          | Reset:          | 0               | 0      | 0      | 0      | 0          | 0        | 0         | 0     |

|        |                                                        |                 | = Unimplemented |        |        |        | = Reserved | U = Unaf | fected    |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 5)

#### **Direct Page Registers**

| Addr.                 | Register Name                                           |                           | Bit 7                                                                                                                                    | 6     | 5     | 4         | 3          | 2     | 1                                            | Bit 0 |

|-----------------------|---------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------|------------|-------|----------------------------------------------|-------|

|                       | LVI Status Register                                     | Read:                     | LVIOUT                                                                                                                                   | 0     | 0     | 0         | 0          | 0     | 0                                            | R     |

| \$FE0C                | (LVISR)                                                 | Write:                    |                                                                                                                                          |       |       |           |            |       |                                              |       |

|                       | See page 91.                                            | Reset:                    | 0                                                                                                                                        | 0     | 0     | 0         | 0          | 0     | 0                                            | 0     |

| \$FE0D<br>↓<br>\$FE0F | Reserved                                                |                           |                                                                                                                                          |       |       |           |            |       |                                              |       |

| \$FFBE                | FLASH Block Protect<br>Register (FLBPR)<br>See page 34. | Read:<br>Write:           | BPR7                                                                                                                                     | BPR6  | BPR5  | BPR4      | BPR3       | BPR2  | BPR1                                         | BPR0  |

|                       | See paye 34.                                            | Reset:                    |                                                                                                                                          |       |       | Unaffecte | d by reset |       | 1                                            |       |

| \$FFBF                | Reserved                                                |                           |                                                                                                                                          |       |       |           |            |       |                                              |       |

|                       |                                                         | г                         |                                                                                                                                          |       | 1     | [         | [          | 1     | 1                                            | ,     |

| \$FFC0                | Internal Oscillator Trim<br>(Factory Programmed         | Read:<br>Write:           | TRIM7                                                                                                                                    | TRIM6 | TRIM5 | TRIM4     | TRIM3      | TRIM2 | TRIM1                                        | TRIM0 |

|                       | VDD = 3.0 V)                                            | Reset:                    | Unaffected by reset                                                                                                                      |       |       |           |            |       | <u>.                                    </u> |       |

| \$FFC1                | Internal Oscillator Trim<br>(Factory Programmed         | Read:<br>Write:           | TRIM7                                                                                                                                    | TRIM6 | TRIM5 | TRIM4     | TRIM3      | TRIM2 | TRIM1                                        | TRIM0 |

| VDD = 5.0             |                                                         | Reset:                    |                                                                                                                                          |       | L     | Unaffecte | d by reset | I     |                                              |       |

| \$FFFF                | COP Control Register<br>(COPCTL)<br>See page 63.        | Read:<br>Write:<br>Reset: | LOW BYTE OF RESET VECTOR<br>WRITING CLEARS COP COUNTER (ANY VALUE)<br>Unaffected by reset<br>= Unimplemented R = Reserved U = Unaffected |       |       |           |            |       |                                              |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 5)

#### Analog-to-Digital Converter (ADC10) Module

## 3.3.4 Sources of Error

Several sources of error exist for ADC conversions. These are discussed in the following sections.

## 3.3.4.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately 15 k $\Omega$  and input capacitance of approximately 10 pF, sampling to within

1/4LSB (at 10-bit resolution) can be achieved within the minimum sample window (3.5 cycles / 2 MHz maximum ADCK frequency) provided the resistance of the external analog source (R<sub>AS</sub>) is kept below 10 k $\Omega$ . Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

## 3.3.4.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{ADVIN}$  / (4096\*I<sub>Leak</sub>) for less than 1/4LSB leakage error (at 10-bit resolution).

## 3.3.4.3 Noise-Induced Errors

System noise which occurs during the sample or conversion process can affect the accuracy of the conversion. The ADC10 accuracy numbers are guaranteed as specified only if the following conditions are met:

- There is a  $0.1\mu$ F low-ESR capacitor from V<sub>REFH</sub> to V<sub>REFL</sub> (if available).

- There is a 0.1μF low-ESR capacitor from V<sub>DDA</sub> to V<sub>SSA</sub> (if available).

- If inductive isolation is used from the primary supply, an additional 1μF capacitor is placed from V<sub>DDA</sub> to V<sub>SSA</sub> (if available).

- V<sub>SSA</sub> and V<sub>REFL</sub> (if available) is connected to V<sub>SS</sub> at a quiet point in the ground plane.

- The MCU is placed in wait mode immediately after initiating the conversion (next instruction after write to ADSCR).

- There is no I/O switching, input or output, on the MCU during the conversion.

There are some situations where external system activity causes radiated or conducted noise emissions or excessive  $V_{DD}$  noise is coupled into the ADC10. In these cases, or when the MCU cannot be placed in wait or I/O activity cannot be halted, the following recommendations may reduce the effect of noise on the accuracy:

- Place a 0.01  $\mu$ F capacitor on the selected input channel to V<sub>REFL</sub> or V<sub>SSA</sub> (if available). This will improve noise issues but will affect sample rate based on the external analog source resistance.

- Operate the ADC10 in stop mode by setting ACLKEN, selecting the channel in ADSCR, and executing a STOP instruction. This will reduce V<sub>DD</sub> noise but will increase effective conversion time due to stop recovery.

- Average the input by converting the output many times in succession and dividing the sum of the results. Four samples are required to eliminate the effect of a 1LSB, one-time error.

- Reduce the effect of synchronous noise by operating off the asynchronous clock (ACLKEN=1) and averaging. Noise that is synchronous to the ADCK cannot be averaged out.

#### Analog-to-Digital Converter (ADC10) Module

# 3.4 Interrupts

When AIEN is set, the ADC10 is capable of generating a CPU interrupt after each conversion. A CPU interrupt is generated when the conversion completes (indicated by COCO being set). COCO will set at the end of a conversion regardless of the state of AIEN.

## 3.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 3.5.1 Wait Mode

The ADC10 will continue the conversion process and will generate an interrupt following a conversion if AIEN is set. If the ADC10 is not required to bring the MCU out of wait mode, ensure that the ADC10 is not in continuous conversion mode by clearing ADCO in the ADC10 status and control register before executing the WAIT instruction. In single conversion mode the ADC10 automatically enters a low-power state when the conversion is complete. It is not necessary to set the channel select bits (ADCH[4:0]) to all 1s to enter a low power state.

## 3.5.2 Stop Mode

If ACLKEN is clear, executing a STOP instruction will abort the current conversion and place the ADC10 in a low-power state. Upon return from stop mode, a write to ADSCR is required to resume conversions, and the result stored in ADRH and ADRL will represent the last completed conversion until the new conversion completes.

If ACLKEN is set, the ADC10 continues normal operation during stop mode. The ADC10 will continue the conversion process and will generate an interrupt following a conversion if AIEN is set. If the ADC10 is not required to bring the MCU out of stop mode, ensure that the ADC10 is not in continuous conversion mode by clearing ADCO in the ADC10 status and control register before executing the STOP instruction. In single conversion mode the ADC10 automatically enters a low-power state when the conversion is complete. It is not necessary to set the channel select bits (ADCH[4:0]) to all 1s to enter a low-power state.

If ACLKEN is set, a conversion can be initiated while in stop using the external hardware trigger ADEXTCO when in external convert mode. The ADC10 will operate in a low-power mode until the trigger is asserted, at which point it will perform a conversion and assert the interrupt when complete (if AIEN is set).

# 3.6 ADC10 During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. BCFE in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the

# Chapter 4 Auto Wakeup Module (AWU)

# 4.1 Introduction

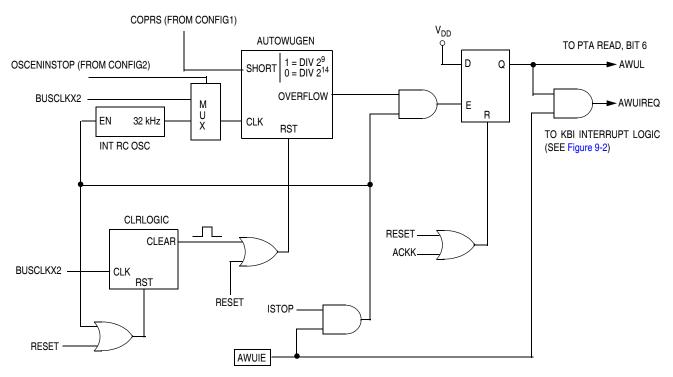

This section describes the auto wakeup module (AWU). The AWU generates a periodic interrupt during stop mode to wake the part up without requiring an external signal. Figure 4-1 is a block diagram of the AWU.

# 4.2 Features

Features of the auto wakeup module include:

- One internal interrupt with separate interrupt enable bit, sharing the same keyboard interrupt vector and keyboard interrupt mask bit

- Exit from low-power stop mode without external signals

- Selectable timeout periods

- Dedicated low-power internal oscillator separate from the main system clock sources

- Option to allow bus clock source to run the AWU if enabled in STOP

Auto Wakeup Module (AWU)

# 4.3 Functional Description

The function of the auto wakeup logic is to generate periodic wakeup requests to bring the microcontroller unit (MCU) out of stop mode. The wakeup requests are treated as regular keyboard interrupt requests, with the difference that instead of a pin, the interrupt signal is generated by an internal logic.

Entering stop mode will enable the auto wakeup generation logic. Writing the AWUIE bit in the keyboard interrupt enable register enables or disables the auto wakeup interrupt input (see Figure 4-1). A 1 applied to the AWUIREQ input with auto wakeup interrupt request enabled, latches an auto wakeup interrupt request.

Auto wakeup latch, AWUL, can be read directly from the bit 6 position of port A data register (PTA). This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data direction or PTA6 pullup exist for this bit.

There are two clock sources for the AWU. An internal RC oscillator (INTRCOSC, exclusive for the auto wakeup feature) drives the wakeup request generator provided the OSCENINSTOP bit in the CONFIG2 register Figure 4-1 is cleared. More accurate wakeup periods are possible using the BUSCLKX2 signal (from the oscillator module) which is selected by setting OSCENINSTOP.

Once the overflow count is reached in the generator counter, a wakeup request, AWUIREQ, is latched and sent to the KBI logic. See Figure 4-1.

Wakeup interrupt requests will only be serviced if the associated interrupt enable bit, AWUIE, in KBIER is set. The AWU shares the keyboard interrupt vector.

The overflow count can be selected from two options defined by the COPRS bit in CONFIG1. This bit was "borrowed" from the computer operating properly (COP) using the fact that the COP feature is idle (no MCU clock available) in stop mode. COPRS = 1 selects the short wakeup period while COPRS = 0 selects the long wakeup period.

The auto wakeup RC oscillator (INTRCOSC) is highly dependent on operating voltage and temperature. This feature is not recommended for use as a time-keeping function.

The wakeup request is latched to allow the interrupt source identification. The latched value, AWUL, can be read directly from the bit 6 position of PTA data register. This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data, PTA6 direction, and PTA6 pullup exist for this bit. The latch can be cleared by writing to the ACKK bit in the KBSCR register. Reset also clears the latch. AWUIE bit in KBI interrupt enable register (see Figure 4-1) has no effect on AWUL reading.

The AWU oscillator and counters are inactive in normal operating mode and become active only upon entering stop mode.

# 4.4 Interrupts

The AWU can generate an interrupt request:

AWU Latch (AWUL) — The AWUL bit is set when the AWU counter overflows. The auto wakeup interrupt mask bit, AWUIE, is used to enable or disable AWU interrupt requests.

The AWU shares its interrupt with the KBI vector.

# Chapter 5 Configuration Register (CONFIG)

# 5.1 Introduction

This section describes the configuration registers (CONFIG1 and CONFIG2). The configuration registers enable or disable the following options:

- Stop mode recovery time (32 × BUSCLKX4 cycles or 4096 × BUSCLKX4 cycles)

- STOP instruction

- Computer operating properly module (COP)

- COP reset period (COPRS): 8176 × BUSCLKX4 or 262,128 × BUSCLKX4

- Low-voltage inhibit (LVI) enable and trip voltage selection

- Auto wakeup timeout period

- Allow clock source to remain enabled in STOP

- Enable IRQ pin

- Disable IRQ pin pullup device

- Enable RST pin

# 5.2 Functional Description

The configuration registers are used in the initialization of various options. The configuration registers can be written once after each reset. Most of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU) it is recommended that this register be written immediately after reset. The configuration registers are located at \$001E and \$001F, and may be read at anytime.

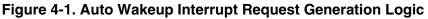

**NOTE** The CONFIG registers are one-time writable by the user after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in Figure 5-1 and Figure 5-2.

Figure 5-1. Configuration Register 2 (CONFIG2)

#### **Configuration Register (CONFIG)**

#### IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- 0 = Internal pullup is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

#### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

## **OSCENINSTOP**— Oscillator Enable in Stop Mode Bit

OSCENINSTOP, when set, will allow the clock source to continue to generate clocks in stop mode. This function can be used to keep the auto-wakeup running while the rest of the microcontroller stops. When clear, the clock source is disabled when the microcontroller enters stop mode.

- 1 = Oscillator enabled to operate during stop mode

- 0 = Oscillator disabled during stop mode

#### **RSTEN** — **RST** Pin Function Selection

1 = Reset function active in pin

0 = Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

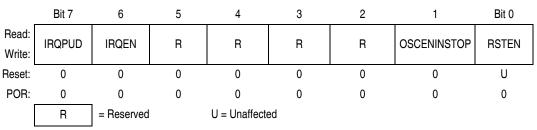

|                 | Bit 7 | 6       | 5       | 4       | 3       | 2     | 1    | Bit 0 |

|-----------------|-------|---------|---------|---------|---------|-------|------|-------|

| Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD | LVITRIP | SSREC | STOP | COPD  |

| Reset:          | 0     | 0       | 0       | 0       | U       | 0     | 0    | 0     |

| POR:            | 0     | 0       | 0       | 0       | 0       | 0     | 0    | 0     |

|                 |       |         |         |         |         |       |      |       |

U = Unaffected

#### Figure 5-2. Configuration Register 1 (CONFIG1)

#### COPRS (Out of Stop Mode) - COP Reset Period Selection Bit

1 = COP reset short cycle = 8176 × BUSCLKX4

0 = COP reset long cycle = 262,128 × BUSCLKX4

# COPRS (In Stop Mode) — Auto Wakeup Period Selection Bit, depends on OSCSTOPEN in CONFIG2 and external clock source

- 1 = Auto wakeup short cycle =  $512 \times (INTRCOSC \text{ or BUSCLKX2})$

- 0 = Auto wakeup long cycle =  $16,384 \times (INTRCOSC \text{ or BUSCLKX2})$

## LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

## LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

- 1 = LVI module resets disabled

- 0 = LVI module resets enabled

# Chapter 10 Low-Voltage Inhibit (LVI)

# **10.1 Introduction**

The low-voltage inhibit (LVI) module is provided as a system protection mechanism to prevent the MCU from operating below a certain operating supply voltage level. The module has several configuration options to allow functionality to be tailored to different system level demands.

The configuration registers (see Chapter 5 Configuration Register (CONFIG)) contain control bits for this module.

# **10.2 Features**

Features of the LVI module include:

- Programmable LVI reset

- Selectable LVI trip voltage

- Programmable stop mode operation

# **10.3 Functional Description**

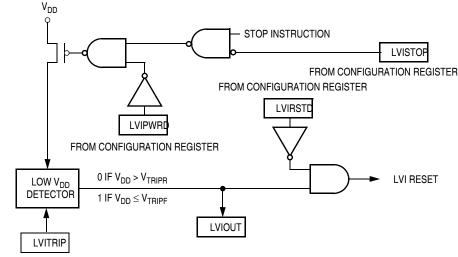

Figure 10-1 shows the structure of the LVI module. LVISTOP, LVIPWRD, LVITRIP, and LVIRSTD are user selectable options found in the configuration register.

FROM CONFIGURATION REGISTER

Figure 10-1. LVI Module Block Diagram

#### ECFS1:ECFS0 — External Crystal Frequency Select Bits

These read/write bits enable the specific amplifier for the crystal frequency range. Refer to oscillator characteristics table in the Electricals section for information on maximum external clock frequency versus supply voltage.

| ECFS1 | ECFS0 | External Crystal Frequency |

|-------|-------|----------------------------|

| 0     | 0     | 8 MHz – 32 MHz             |

| 0     | 1     | 1 MHz – 8 MHz              |

| 1     | 0     | 32 kHz – 100 kHz           |

| 1     | 1     | Reserved                   |

#### ECGON — External Clock Generator On Bit

This read/write bit enables the OSC1 pin as the clock input to the MCU, so that the switching process can be initiated. This bit is cleared by reset. This bit is ignored in monitor mode with the internal oscillator bypassed.

- 1 = External clock enabled

- 0 = External clock disabled

#### ECGST — External Clock Status Bit

This read-only bit indicates whether an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

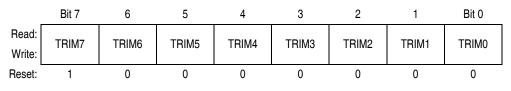

## 11.8.2 Oscillator Trim Register (OSCTRIM)

Figure 11-5. Oscillator Trim Register (OSCTRIM)

#### TRIM7–TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the internal capacitance used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed oscillator period. The oscillator period is based on the oscillator frequency selected by the ICFS bits in OSCSC.

Applications using the internal oscillator should copy the internal oscillator trim value at location \$FFC0 or \$FFC1 into this register to trim the clock source.

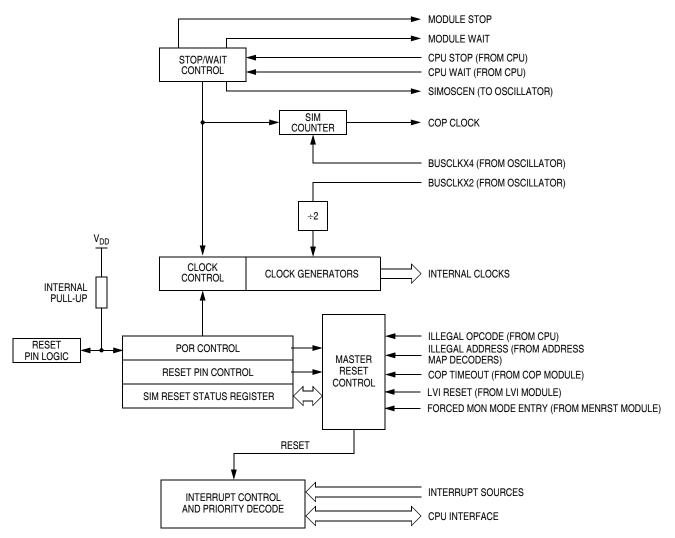

#### System Integration Module (SIM)

Figure 13-1. SIM Block Diagram

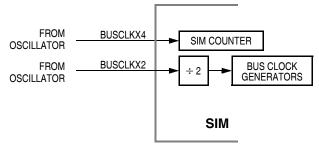

# **13.3 SIM Bus Clock Control and Generation**

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 13-2.

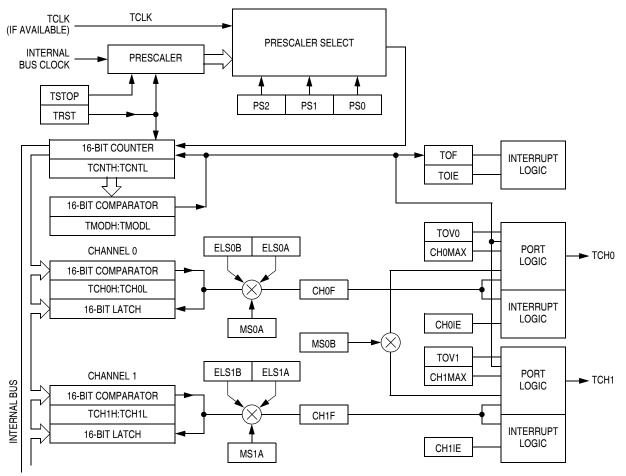

Figure 14-2. TIM Block Diagram

## 14.3.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 14.3.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current output compare pulse. The interrupt routine has until the end of the counter overflow period to write the new value.

- When changing to a larger output compare value, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current counter overflow period. Writing a larger value in an output compare interrupt routine (at

Timer Interface Module (TIM)

**Break Module (BRK)**

The break interrupt timing is:

- When a break address is placed at the address of the instruction opcode, the instruction is not executed until after completion of the break interrupt routine.

- When a break address is placed at an address of an instruction operand, the instruction is executed before the break interrupt.

- When software writes a 1 to the BRKA bit, the break interrupt occurs just before the next instruction is executed.

By updating a break address and clearing the BRKA bit in a break interrupt routine, a break interrupt can be generated continuously.

## CAUTION

A break address should be placed at the address of the instruction opcode. When software does not change the break address and clears the BRKA bit in the first break interrupt routine, the next break interrupt will not be generated after exiting the interrupt routine even when the internal address bus matches the value written in the break address registers.

## 15.2.1.1 Flag Protection During Break Interrupts

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register and the **Break Interrupts** subsection for each module.

## 15.2.1.2 TIM During Break Interrupts

A break interrupt stops the timer counter.

## 15.2.1.3 COP During Break Interrupts

The COP is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

## 15.2.2 Break Module Registers

These registers control and monitor operation of the break module:

- Break status and control register (BRKSCR)

- Break address register high (BRKH)

- Break address register low (BRKL)

- Break status register (BSR)

- Break flag control register (BFCR)

Development Support

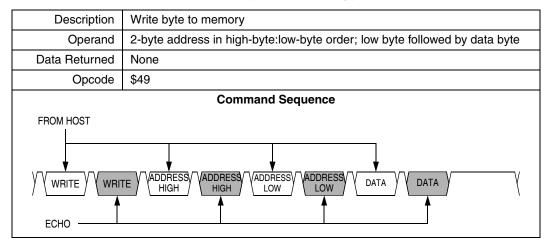

#### Table 15-4. WRITE (Write Memory) Command

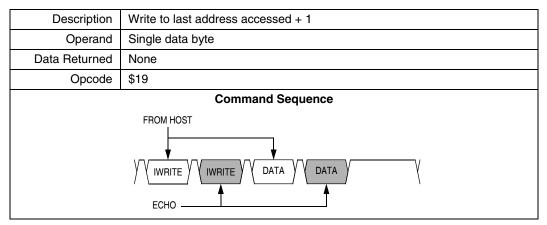

## Table 15-6. IWRITE (Indexed Write) Command

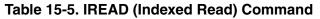

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64-Kbyte memory map.

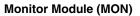

#### Table 15-7. READSP (Read Stack Pointer) Command

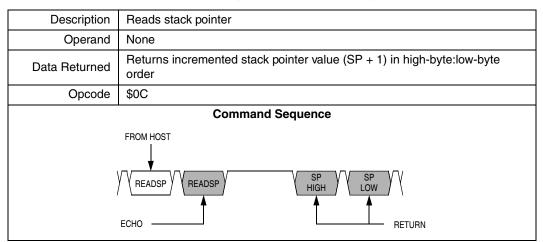

The MCU executes the SWI and PSHH instructions when it enters monitor mode. The RUN command tells the MCU to execute the PULH and RTI instructions. Before sending the RUN command, the host can modify the stacked CPU registers to prepare to run the host program. The READSP command returns the incremented stack pointer value, SP + 1. The high and low bytes of the program counter are at addresses SP + 5 and SP + 6.

|                              | SP     |

|------------------------------|--------|

| HIGH BYTE OF INDEX REGISTER  | SP + 1 |

| CONDITION CODE REGISTER      | SP + 2 |

| ACCUMULATOR                  | SP + 3 |

| LOW BYTE OF INDEX REGISTER   | SP + 4 |

| HIGH BYTE OF PROGRAM COUNTER | SP + 5 |

| LOW BYTE OF PROGRAM COUNTER  | SP + 6 |

|                              | SP + 7 |

|                              |        |

Figure 15-17. Stack Pointer at Monitor Mode Entry

**Ordering Information and Mechanical Specifications**

Case 751G page 1 of 2

**Ordering Information and Mechanical Specifications**

Case 948F page 3 of 3

# Appendix A 908QTA/QYxA Conversion Guidelines

# A.1 Introduction

This engineering bulletin describes the 908QTA/QYxA. The 908QTA/QYxA is an enhanced device intended to replace the 908QT/QYx series of devices (referred to as the QY Classic in this document). Customer requests have led to the advanced design of the QYxA that has added adaptability, new features, and contains lead-free packaging.

This document:

- Provides information needed to convert from QY Classic to the enhanced QYxA

- Highlights the benefits of making this change

Sections:

- A.2 Benefits of the Enhanced QYxA

- A.3 Conversion Considerations

- A.4 Code Changes Checklist

- A.5 Development Tools

- A.6 Differences in Packaging

# A.2 Benefits of the Enhanced QYxA

The QYxA contains new and enhanced modules that add more flexibility and new features to the QY Classic. These benefits can improve the operation of an application or lead to new features for an application. For more information regarding these features refer to the QYxA data sheet (Freescale document order number MC68HC908QYxA).

## A.2.1 New Analog-to-Digital Converter Module (ADC)

The QYxA contains a 10-bit ADC which replaces the 8-bit ADC on the QY Classic. This module allows both 10-bit and 8-bit conversion modes. The increased precision for ADC readings can be very useful in many applications.

Features of the ADC new 10-bit module include:

- There are two new ADC channels that have been placed on PTB0 and PTB1 allowing added flexibility especially when debugging in Monitor Mode.

- A limitation of QY Classic debugging is that access to the ADC channels is limited because many of the QY Classic pins are multiplexed. Having extra ADC channels on the PTB pins resolves this limitation.