Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |  |

|----------------------------|------------------------------------------------------------------------|--|

| Product Status             | Not For New Designs                                                    |  |

| Core Processor             | HC08                                                                   |  |

| Core Size                  | 8-Bit                                                                  |  |

| Speed                      | 8MHz                                                                   |  |

| Connectivity               | -                                                                      |  |

| Peripherals                | LVD, POR, PWM                                                          |  |

| Number of I/O              | 13                                                                     |  |

| Program Memory Size        | 4KB (4K x 8)                                                           |  |

| Program Memory Type        | FLASH                                                                  |  |

| EEPROM Size                | -                                                                      |  |

| RAM Size                   | 128 x 8                                                                |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |  |

| Data Converters            | A/D 6x10b                                                              |  |

| Oscillator Type            | Internal                                                               |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |  |

| Mounting Type              | Surface Mount                                                          |  |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                         |  |

| Supplier Device Package    | 16-SOIC                                                                |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qy4acdwer |  |

## **Revision History**

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History**

| Date              | Revision<br>Level | Description  Initial release                                                                                                                                                                                                                                  |                                 |

|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| December,<br>2005 | N/A               |                                                                                                                                                                                                                                                               |                                 |

|                   | 1                 | Added 1.7 Unused Pin Termination.                                                                                                                                                                                                                             | 20                              |

|                   |                   | Figure 4-1. Auto Wakeup Interrupt Request Generation Logic — Corrected clock source.                                                                                                                                                                          | 51                              |

|                   |                   | 4.3 Functional Description — Clarified operation.                                                                                                                                                                                                             | 52                              |

|                   |                   | 4.5.1 Wait Mode — Corrected operation details.                                                                                                                                                                                                                | 53                              |

|                   |                   | 4.6.4 Configuration Register 2 — Corrected clock source.                                                                                                                                                                                                      | 55                              |

| August,<br>2006   |                   | 4.6.5 Configuration Register 1 — Added SSREC bit description.                                                                                                                                                                                                 | 55                              |

| 2000              |                   | 5.2 Functional Description — Corrected clock source.                                                                                                                                                                                                          | 58                              |

|                   |                   | 12.1 Introduction — Replaced note.                                                                                                                                                                                                                            | 103                             |

|                   |                   | 13.7.2 Stop Mode — Corrected clock source.                                                                                                                                                                                                                    | 121                             |

|                   |                   | 16.12 Supply Current Characteristics — Updated maximum values for SI <sub>DD</sub> at both 5 V and 3 V.                                                                                                                                                       | 165                             |

|                   |                   | A.2.3 Improved Auto Wakeup Module (AWU) — Corrected clock source.                                                                                                                                                                                             | 194                             |

|                   | 2                 | Chapter 3 Analog-to-Digital Converter (ADC10) Module — Renamed ADCSC register to ADSCR to be consistent with development tools.                                                                                                                               | 37                              |

|                   |                   | Figure 15-18. Monitor Mode Entry Timing — Changed CGMXCLK to BUSCLKX4                                                                                                                                                                                         | 154                             |

| A!!               |                   | 16.12 Supply Current Characteristics — Added note 6 below table                                                                                                                                                                                               | 165                             |

| April,<br>2007    |                   | Chapter 17 Ordering Information and Mechanical Specifications — Updated chapter to include:                                                                                                                                                                   |                                 |

|                   |                   | Table 17-1. Consumer and Industrial Device Numbering System Table 17-2. Automotive Device Numbering System 17.3 Orderable Part Numbering System 17.3.1 Consumer and Industrial Orderable Part Numbering System 17.3.2 Automotive Orderable Part Number System | 171<br>171<br>172<br>172<br>172 |

| March,<br>2010    | 3                 | 17.3.2 Automotive Orderable Part Number System  Clarify internal oscillator trim register information.                                                                                                                                                        |                                 |

**List of Chapters**

# Chapter 11 Oscillator (OSC) Module

| 11.1    | Introduction                            | 93  |

|---------|-----------------------------------------|-----|

| 11.2    | Features                                | 93  |

| 11.3    | Functional Description                  | 93  |

| 11.3.1  | Internal Signal Definitions             |     |

| 11.3.1. |                                         |     |

| 11.3.1. |                                         |     |

| 11.3.1. | 3 RC Oscillator Clock (RCCLK)           | 95  |

| 11.3.1. | 4 Internal Oscillator Clock (INTCLK)    | 95  |

| 11.3.1. | 5 Bus Clock Times 4 (BUSCLKX4)          | 95  |

| 11.3.1. | · · · · · · · · · · · · · · · · · · ·   |     |

| 11.3.2  | Internal Oscillator                     |     |

| 11.3.2. | 3                                       |     |

| 11.3.2. | 3 · · · · · · · · · · · · · · · · · · · |     |

| 11.3.2. | $oldsymbol{\circ}$                      |     |

| 11.3.3  | External Oscillator                     |     |

| 11.3.4  | XTAL Oscillator                         |     |

| 11.3.5  | RC Oscillator                           |     |

| 11.4    | Interrupts                              |     |

| 11.5    | Low-Power Modes                         |     |

| 11.5.1  | Wait Mode                               |     |

| 11.5.2  | Stop Mode                               | 98  |

| 11.6    | OSC During Break Interrupts             | 99  |

| 11.7    | I/O Signals                             | 99  |

| 11.7.1  | Oscillator Input Pin (OSC1)             |     |

| 11.7.2  | Oscillator Output Pin (OSC2)            | 99  |

| 11.8    | Registers                               | 100 |

| 11.8.1  | Oscillator Status and Control Register  | 100 |

| 11.8.2  | Oscillator Trim Register (OSCTRIM)      | 101 |

|         | Observan 40                             |     |

|         | Chapter 12                              |     |

| 40.4    | Input/Output Ports (PORTS)              | 400 |

| 12.1    | Introduction                            |     |

| 12.2    | Unused Pin Termination                  |     |

| 12.3    | Port A                                  |     |

| 12.3.1  | Port A Data Register                    |     |

| 12.3.2  | Data Direction Register A               |     |

| 12.3.3  | Port A Input Pullup Enable Register     |     |

| 12.3.4  | Port A Summary Table                    |     |

| 12.4    | Port B                                  |     |

| 12.4.1  | Port B Data Register                    |     |

| 12.4.2  | Data Direction Register B               |     |

| 12.4.3  | Port B Input Pullup Enable Register     |     |

| 12.4.4  | Port B Summary Table                    | IUd |

| Output Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unbuffered Output Compare                                                                                                                                                                                                                                                                                                                                                                                                                                       | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Buffered Output Compare                                                                                                                                                                                                                                                                                                                                                                                                                                         | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pulse Width Modulation (PWM)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Unbuffered PWM Signal Generation                                                                                                                                                                                                                                                                                                                                                                                                                                | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I During Break Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                       | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TIM Channel I/O Pins (TCH1:TCH0)                                                                                                                                                                                                                                                                                                                                                                                                                                | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TIM Clock Pin (TCLK)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| nisters                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| This charmer registers                                                                                                                                                                                                                                                                                                                                                                                                                                          | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 15                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Development Support                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Development Support                                                                                                                                                                                                                                                                                                                                                                                                                                             | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 139<br>139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 139<br>139<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

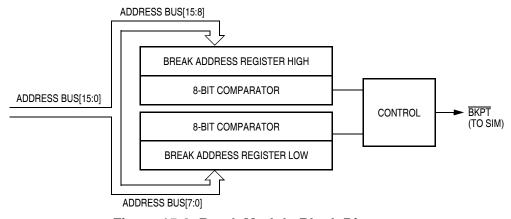

| oduction  ak Module (BRK)  Functional Description  Flag Protection During Break Interrupts  TIM During Break Interrupts                                                                                                                                                                                                                                                                                                                                         | 139<br>139<br>141<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts                                                                                                                                                                                                                                                                                                                 | 139<br>139<br>141<br>141<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers                                                                                                                                                                                                                                                                                          | 139<br>139<br>141<br>141<br>141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register                                                                                                                                                                                                                                                                 | 139<br>139<br>141<br>141<br>141<br>142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers                                                                                                                                                                                                                                         | 139<br>141<br>141<br>141<br>141<br>142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register                                                                                                                                                                                                                | 139<br>139<br>141<br>141<br>141<br>142<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register                                                                                                                                                                                          | 139<br>141<br>141<br>141<br>142<br>142<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register                                                                                                                                        | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register                                                                                                                                                                                          | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register                                                                                                                                        | 139<br>141<br>141<br>141<br>142<br>143<br>143<br>143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register Low-Power Modes                                                                                                                        | 139<br>141<br>141<br>141<br>142<br>143<br>143<br>144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON)                                                                                                                           | 139<br>139<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description                                                                                                    | 139<br>139<br>141<br>141<br>141<br>143<br>143<br>143<br>144<br>144<br>144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

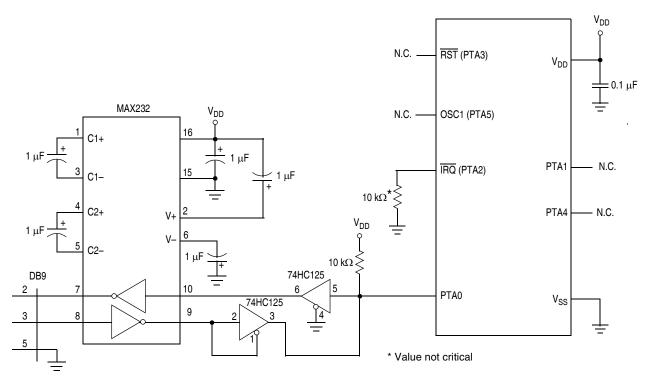

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Flag Control Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode                                           | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode Forced Monitor Mode                                      | 139<br>139<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>148<br>148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode Forced Monitor Mode Monitor Vectors                      | 139<br>139<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>148<br>148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Status Register Break Status Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode Forced Monitor Mode Monitor Vectors Data Format | 139<br>141<br>141<br>141<br>141<br>142<br>143<br>143<br>144<br>144<br>148<br>1148<br>1150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| oduction ak Module (BRK) Functional Description Flag Protection During Break Interrupts TIM During Break Interrupts COP During Break Interrupts Break Module Registers Break Status and Control Register Break Address Registers Break Auxiliary Register Break Flag Control Register Break Flag Control Register Low-Power Modes nitor Module (MON) Functional Description Normal Monitor Mode Forced Monitor Mode Monitor Vectors Data Format Break Signal    | 139<br>139<br>141<br>141<br>141<br>142<br>143<br>144<br>144<br>148<br>148<br>150<br>150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Unbuffered Output Compare Buffered Output Compare Pulse Width Modulation (PWM) Unbuffered PWM Signal Generation Buffered PWM Signal Generation PWM Initialization errupts errupts V-Power Modes Wait Mode Stop Mode I During Break Interrupts. Signals TIM Channel I/O Pins (TCH1:TCH0) TIM Clock Pin (TCLK) gisters TIM Status and Control Register TIM Counter Registers TIM Counter Registers TIM Counter Modulo Registers TIM Channel Status and Control Registers TIM Channel Status and Control Registers TIM Channel Registers |

### 3.3.4.4 Code Width and Quantization Error

The ADC10 quantizes the ideal straight-line transfer function into 1024 steps (in 10-bit mode). Each step ideally has the same height (1 code) and width. The width is defined as the delta between the transition points from one code to the next. The ideal code width for an N bit converter (in this case N can be 8 or 10), defined as 1LSB, is:

$$1LSB = (V_{REEH} - V_{REEI}) / 2^N$$

Because of this quantization, there is an inherent quantization error. Because the converter performs a conversion and then rounds to 8 or 10 bits, the code will transition when the voltage is at the midpoint between the points where the straight line transfer function is exactly represented by the actual transfer function. Therefore, the quantization error will be  $\pm$  1/2LSB in 8- or 10-bit mode. As a consequence, however, the code width of the first (\$000) conversion is only 1/2LSB and the code width of the last (\$FF or \$3FF) is 1.5LSB.

## 3.3.4.5 Linearity Errors

The ADC10 may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the user should be aware of them because they affect overall accuracy. These errors are:

- Zero-Scale Error (E<sub>ZS</sub>) (sometimes called offset) This error is defined as the difference between

the actual code width of the first conversion and the ideal code width (1/2LSB). Note, if the first

conversion is \$001, then the difference between the actual \$001 code width and its ideal (1LSB) is

used.

- Full-Scale Error (E<sub>FS</sub>) This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5LSB). Note, if the last conversion is \$3FE, then the difference between the actual \$3FE code width and its ideal (1LSB) is used.

- Differential Non-Linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral Non-Linearity (INL) This error is defined as the highest-value the (absolute value of the)

running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition

voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total Unadjusted Error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function, and therefore includes all forms of error.

### 3.3.4.6 Code Jitter, Non-Monotonicity and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

- Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the converter yields the lower code (and vice-versa). However, even very small amounts of system noise can cause the converter to be indeterminate (between two codes) for a range of input voltages around the transition voltage. This range is normally around ±1/2LSB but will increase with noise.

- Non-monotonicity is defined as when, except for code jitter, the converter converts to a lower code

for a higher input voltage. Non-monotonicity is present if the apparent code jitter covers three codes

(when the converter's output is indeterminate between three values for a given input voltage) or is

greater than 1LSB.

- Missing codes are those which are never converted for any input value. In 8-bit or 10-bit mode, the ADC10 is guaranteed to be monotonic and to have no missing codes.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

**Configuration Register (CONFIG)**

**Keyboard Interrupt Module (KBI)**

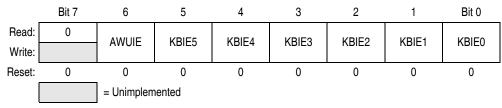

## 9.8.2 Keyboard Interrupt Enable Register (KBIER)

KBIER enables or disables each keyboard interrupt pin.

Figure 9-4. Keyboard Interrupt Enable Register (KBIER)

### KBIE5-KBIE0 — Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch KBI interrupt requests.

- 1 = KBIx pin enabled as keyboard interrupt pin

- 0 = KBIx pin not enabled as keyboard interrupt pin

### NOTE

AWUIE bit is not used in conjunction with the keyboard interrupt feature. To see a description of this bit, see Chapter 4 Auto Wakeup Module (AWU).

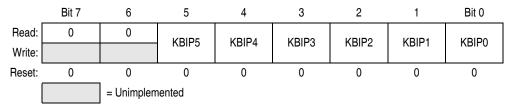

## 9.8.3 Keyboard Interrupt Polarity Register (KBIPR)

KBIPR determines the polarity of the enabled keyboard interrupt pin and enables the appropriate pullup or pulldown device.

Figure 9-5. Keyboard Interrupt Polarity Register (KBIPR)

### KBIP5-KBIP0 — Keyboard Interrupt Polarity Bits

Each of these read/write bits enables the polarity of the keyboard interrupt detection.

- 1 = Keyboard polarity is high level and/or rising edge

- 0 = Keyboard polarity is low level and/or falling edge

# 10.4 LVI Interrupts

The LVI module does not generate interrupt requests.

## 10.5 Low-Power Modes

The STOP and WAIT instructions put the MCU in low power-consumption standby modes.

### 10.5.1 Wait Mode

If enabled, the LVI module remains active in wait mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of wait mode.

## 10.5.2 Stop Mode

If the LVIPWRD bit in the configuration register is cleared and the LVISTOP bit in the configuration register is set, the LVI module remains active. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of stop mode.

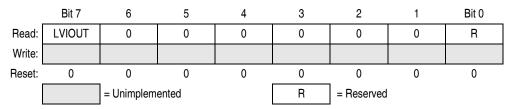

# 10.6 Registers

The LVI status register (LVISR) contains a status bit that is useful when the LVI is enabled and LVI reset is disabled.

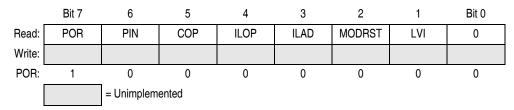

Figure 10-2. LVI Status Register (LVISR)

# LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage and is cleared when  $V_{DD}$  voltage rises above  $V_{TRIPB}$ . (See Table 10-1).

Table 10-1, LVIOUT Bit Indication

| V <sub>DD</sub>                                           | LVIOUT         |

|-----------------------------------------------------------|----------------|

| V <sub>DD</sub> > V <sub>TRIPR</sub>                      | 0              |

| V <sub>DD</sub> < V <sub>TRIPF</sub>                      | 1              |

| V <sub>TRIPF</sub> < V <sub>DD</sub> < V <sub>TRIPR</sub> | Previous value |

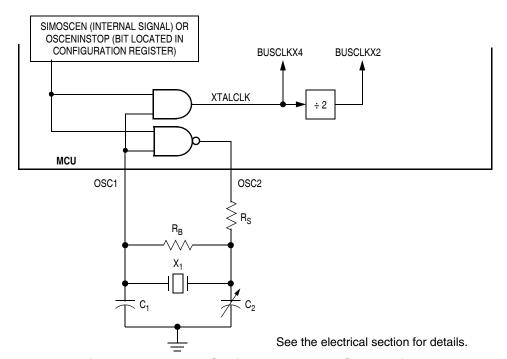

The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>B</sub>

- Series resistor, R<sub>s</sub> (optional)

### **NOTE**

The series resistor ( $R_s$ ) is included in the diagram to follow strict Pierce oscillator guidelines and may not be required for all ranges of operation, especially with high frequency crystals. Refer to the oscillator characteristics table in the Electricals section for more information.

Figure 11-2. XTAL Oscillator External Connections

# 11.6 OSC During Break Interrupts

There are no status flags associated with the OSC module.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

# 11.7 I/O Signals

The OSC shares its pins with general-purpose input/output (I/O) port pins. See Figure 11-1 for port location of these shared pins.

## 11.7.1 Oscillator Input Pin (OSC1)

The OSC1 pin is an input to the crystal oscillator amplifier, an input to the RC oscillator circuit, or an input from an external clock source.

When the OSC is configured for internal oscillator, the OSC1 pin can be used as a general-purpose input/output (I/O) port pin or other alternative pin function.

# 11.7.2 Oscillator Output Pin (OSC2)

For the XTAL oscillator option, the OSC2 pin is the output of the crystal oscillator amplifier.

When the OSC is configured for internal oscillator, external clock, or RC, the OSC2 pin can be used as a general-purpose I/O port pin or other alternative pin function. When the oscillator is configured for internal or RC, the OSC2 pin can be used to output BUSCLKX4.

Option

OSC2 Pin Function

XTAL oscillator

Inverting OSC1

External clock

General-purpose I/O or alternative pin function

Internal oscillator

or

OSC2EN = 0: General-purpose I/O or alternative pin function

OSC2EN = 1: BUSCLKX4 output

Table 11-1. OSC2 Pin Function

Oscillator (OSC) Module

# **Chapter 13 System Integration Module (SIM)**

### 13.1 Introduction

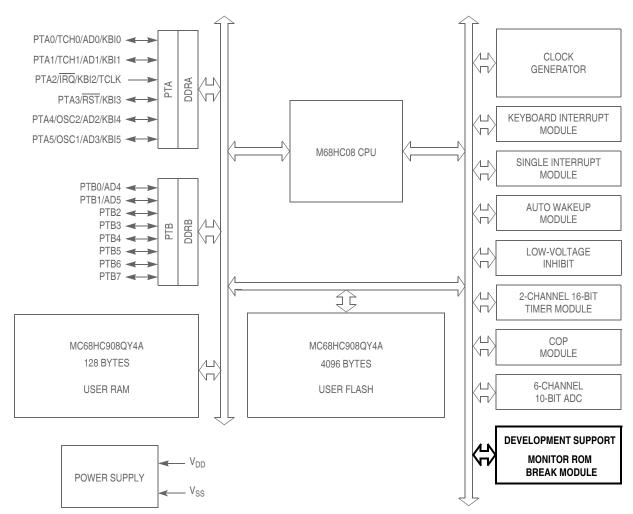

This section describes the system integration module (SIM), which supports up to 24 external and/or internal interrupts. Together with the central processor unit (CPU), the SIM controls all microcontroller unit (MCU) activities. A block diagram of the SIM is shown in Figure 13-1. The SIM is a system state controller that coordinates CPU and exception timing.

The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and computer operating properly (COP) timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- · CPU enable/disable timing

**Table 13-1. Signal Name Conventions**

| Signal Name           | Description                                                                                                                                           |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BUSCLKX4              | Buffered clock from the internal, RC or XTAL oscillator circuit.                                                                                      |  |

| BUSCLKX2              | The BUSCLKX4 frequency divided by two. This signal is again divided by two in the SIM to generate the internal bus clocks (bus clock = BUSCLKX4 ÷ 4). |  |

| Address bus           | Internal address bus                                                                                                                                  |  |

| Data bus              | Internal data bus                                                                                                                                     |  |

| PORRST                | PORRST Signal from the power-on reset module to the SIM                                                                                               |  |

| IRST                  | IRST Internal reset signal                                                                                                                            |  |

| R/W Read/write signal |                                                                                                                                                       |  |

# 13.2 RST and IRQ Pins Initialization

RST and IRQ pins come out of reset as PTA3 and PTA2 respectively. RST and IRQ functions can be activated by programing CONFIG2 accordingly. Refer to Chapter 5 Configuration Register (CONFIG).

In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.