Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

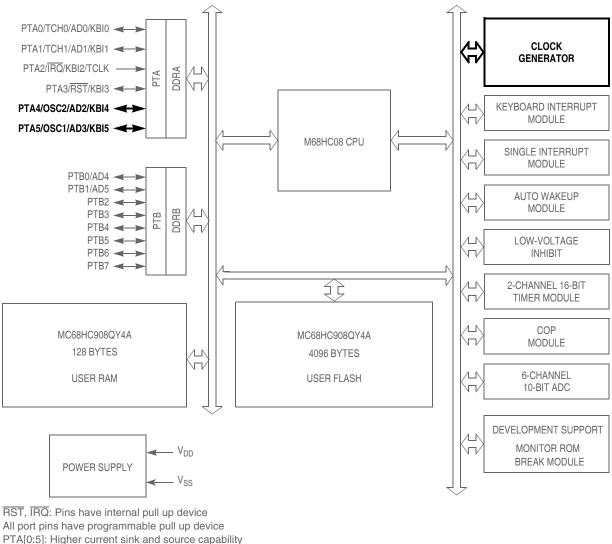

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | LVD, POR, PWM                                             |

| Number of I/O              | 13                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 128 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 6x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | 16-PDIP                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908qy4acpe |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Table of Contents**

# Chapter 16 Electrical Specifications

| 16.1  | Introduction                             | 155 |

|-------|------------------------------------------|-----|

| 16.2  | Absolute Maximum Ratings                 | 155 |

| 16.3  | Functional Operating Range               | 156 |

| 16.4  | Thermal Characteristics                  | 156 |

| 16.5  | 5-V DC Electrical Characteristics        | 157 |

| 16.6  | Typical 5-V Output Drive Characteristics | 158 |

| 16.7  | 5-V Control Timing                       | 159 |

| 16.8  | 3-V DC Electrical Characteristics        | 160 |

| 16.9  | Typical 3-V Output Drive Characteristics | 161 |

| 16.10 | 3-V Control Timing                       | 162 |

| 16.11 | Oscillator Characteristics               | 163 |

| 16.12 | Supply Current Characteristics           | 165 |

| 16.13 | ADC10 Characteristics.                   | 167 |

| 16.14 | Timer Interface Module Characteristics   | 169 |

| 16.15 | Memory Characteristics                   | 170 |

# Chapter 17

# Ordering Information and Mechanical Specifications

| 17.1   | Introduction                                            | 171 |

|--------|---------------------------------------------------------|-----|

| 17.2   | Ordering Information                                    | 171 |

| 17.3   | Orderable Part Numbering System                         | 172 |

|        | Consumer and Industrial Orderable Part Numbering System |     |

| 17.3.2 | Automotive Orderable Part Number System                 | 172 |

| 17.4   | Mechanical Drawings                                     | 172 |

# Appendix A 908QTA/QYxA Conversion Guidelines

| A.1     | Introduction                                     | 1 |

|---------|--------------------------------------------------|---|

| A.2     | Benefits of the Enhanced QYxA 19                 | 1 |

| A.2.1   | New Analog-to-Digital Converter Module (ADC) 19  | 1 |

| A.2.1.1 | Registers Affected                               | 2 |

| A.2.2   | Enhanced Oscillator Module (OSC) 19              | 3 |

| A.2.2.1 | Registers Affected                               | 3 |

| A.2.3   | Improved Auto Wakeup Module (AWU) 19             | 4 |

| A.2.3.1 | Registers Affected                               | 4 |

| A.2.4   | New Power-on Reset Module (POR) 19               | 4 |

| A.2.5   | Keyboard Interface Module (KBI) Functionality 19 |   |

| A.2.5.1 | Registers Affected                               | 5 |

| A.2.6   | On-Chip Routine Enhancements 19                  | 5 |

| A.3     | Conversion Considerations 19                     | 6 |

| A.4     | Code Changes Checklist                           | 6 |

| A.5     | Development Tools                                | 7 |

| A.6     | Differences in Packaging 19                      | 7 |

Memory

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

#### PGM — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

# 2.6.2 FLASH Page Erase Operation

Use the following procedure to erase a page of FLASH memory. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80, or \$XXC0. The user interrupt vector area resides in the \$FFC0-\$FFFF page. Any FLASH memory page can be erased alone.

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub>.

- 7. Clear the ERASE bit.

- 8. Wait for a time, t<sub>NVH</sub>.

- 9. Clear the HVEN bit.

- 10. After time, t<sub>RCV</sub>, the memory can be accessed in read mode again.

#### NOTE

The COP register at location \$FFFF should not be written between steps 5-9, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, other unrelated operations may occur between the steps.

#### CAUTION

A page erase of the vector page will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

# 2.6.3 FLASH Mass Erase Operation

Use the following procedure to erase the entire FLASH memory to read as a 1:

- 1. Set both the ERASE bit and the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH address<sup>(1)</sup> within the FLASH memory address range.

- 4. Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>MErase</sub>.

- 7. Clear the ERASE and MASS bits.

#### NOTE

Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF).

- 8. Wait for a time, t<sub>NVHL</sub>.

- 9. Clear the HVEN bit.

- 10. After time, t<sub>RCV</sub>, the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, other unrelated operations may occur between the steps.

#### CAUTION

A mass erase will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

#### 2.6.4 FLASH Program Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0, or \$XXE0. Use the following step-by-step procedure to program a row of FLASH memory

Figure 2-4 shows a flowchart of the programming algorithm.

#### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte which is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range desired.

- 4. Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

<sup>1.</sup> When in monitor mode, with security sequence failed (see 15.3.2 Security), write to the FLASH block protect register instead of any FLASH address.

FLASH Memory (FLASH)

# 2.6.7 EEPROM Memory Emulation Using FLASH Memory

In some applications, the user may want to repeatedly store and read a set of data from an area of nonvolatile memory. This is easily implemented in EEPROM memory because single byte erase is allowed in EEPROM.

When using FLASH memory, the minimum erase size is a page. However, the FLASH can be used as EEPROM memory. This technique is called "EEPROM emulation".

The basic concept of EEPROM emulation using FLASH is that a page is continuously programmed with a new data set without erasing the previously programmed locations. Once the whole page is completely programmed or the page does not have enough bytes to program a new data set, the user software automatically erases the page and then programs a new data set in the erased page.

In EEPROM emulation when data is read from the page, the user software must find the latest data set in the page since the previous data still remains in the same page. There are many ways to monitor the page erase timing and the latest data set. One example is unprogrammed FLASH bytes are detected by checking programmed bytes (non-\$FF value) in a page. In this way, the end of the data set will contain unprogrammed data (\$FF value).

A couple of application notes, describing how to emulate EEPROM using FLASH, are available on our web site. Titles and order numbers for these application notes are given at the end of this subsection.

For EEPROM emulation software to work successfully, the following items must be taken care of in the user software:

- 1. Each FLASH byte in a page must be programmed only one time until the page is erased.

- 2. A page must be erased before the FLASH cumulative program HV period ( $t_{HV}$ ) is beyond the maximum  $t_{HV}$ .  $t_{HV}$  is defined as the cumulative high-voltage programming time to the same row before the next erase. For more detailed information, refer to 16.15 Memory Characteristics.

- 3. FLASH row erase and program cycles should not exceed 10,000 cycles, respectively.

The above EEPROM emulation software can be easily developed by using the on-chip FLASH routines implemented in the MCU. These routines are located in the ROM memory and support FLASH program and erase operations. Proper utilization of the on-chip FLASH routines guarantee conformance to the FLASH specifications.

In the on-chip FLASH programming routine called PRGRNGE, the high-voltage programming time is enabled for less than 125  $\mu$ s when programming a single byte at any operating bus frequency between 1.0 MHz and 8.4 MHz. Therefore, even when a row is programmed by 32 separate single-byte programming operations, t<sub>HV</sub> is less than the maximum t<sub>HV</sub>. Hence, item 2 listed above is already taken care of by using this routine.

A page erased operation is provided in the FLASH erase routine called ERARNGE.

Application note AN2635 (On-Chip FLASH Programming Routines) describes how to use these routines.

The following application notes, available at www.freescale.com, describe how EERPOM emulation is implemented using FLASH:

AN2183 — Using FLASH as EEPROM on the MC68HC908GP32

AN2346 — EEPROM Emulation Using FLASH in MC68HC908QY/QT MCUs

AN2690 — Low Frequency EEPROM Emulation on the MC68HC908QY4

An EEPROM emulation driver, available at www.freescale.com, has been developed and qualified: AN3040 — *M68HC08 EEPROM Emulation Driver*

#### Analog-to-Digital Converter (ADC10) Module

clocks are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by the ADIV[1:0] bits and can be divide-by 1, 2, 4, or 8.

# 3.3.2 Input Select and Pin Control

Only one analog input may be used for conversion at any given time. The channel select bits in ADSCR are used to select the input signal for conversion.

# 3.3.3 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC10 module can be configured for low power operation, long sample time, and continuous conversion.

#### 3.3.3.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADSCR (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADSCR is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

#### 3.3.3.2 Completing Conversions

A conversion is completed when the result of the conversion is transferred into the data result registers, ADRH and ADRL. This is indicated by the setting of the COCO bit. An interrupt is generated if AIEN is high at the time that COCO is set.

A blocking mechanism prevents a new result from overwriting previous data in ADRH and ADRL if the previous data is in the process of being read while in 10-bit mode (ADRH has been read but ADRL has not). In this case the data transfer is blocked, COCO is not set, and the new result is lost. When a data transfer is blocked, another conversion is initiated regardless of the state of ADCO (single or continuous conversions enabled). If single conversions are enabled, this could result in several discarded conversions and excess power consumption. To avoid this issue, the data registers must not be read after initiating a single conversion until the conversion completes.

#### 3.3.3.3 Aborting Conversions

Any conversion in progress will be aborted when:

- A write to ADSCR occurs (the current conversion will be aborted and a new conversion will be initiated, if ADCH are not all 1s).

- A write to ADCLK occurs.

- The MCU is reset.

- The MCU enters stop mode with ACLK not enabled.

When a conversion is aborted, the contents of the data registers, ADRH and ADRL, are not altered but continue to be the values transferred after the completion of the last successful conversion. In the case that the conversion was aborted by a reset, ADRH and ADRL return to their reset states.

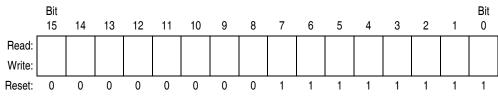

# 7.3.3 Stack Pointer

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset, the stack pointer is preset to \$00FF. The reset stack pointer (RSP) instruction sets the least significant byte to \$FF and does not affect the most significant byte. The stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

In the stack pointer 8-bit offset and 16-bit offset addressing modes, the stack pointer can function as an index register to access data on the stack. The CPU uses the contents of the stack pointer to determine the conditional address of the operand.

Figure 7-4. Stack Pointer (SP)

#### NOTE

The location of the stack is arbitrary and may be relocated anywhere in random-access memory (RAM). Moving the SP out of page 0 (\$0000 to \$00FF) frees direct address (page 0) space. For correct operation, the stack pointer must point only to RAM locations.

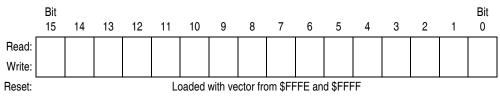

#### 7.3.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

Normally, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

During reset, the program counter is loaded with the reset vector address located at \$FFFE and \$FFFF. The vector address is the address of the first instruction to be executed after exiting the reset state.

Figure 7-5. Program Counter (PC)

# 9.7 I/O Signals

The KBI module can share its pins with the general-purpose I/O pins. See Figure 9-1 for the port pins that are shared.

# 9.7.1 KBI Input Pins (KBIx:KBI0)

Each KBI pin is independently programmable as an external interrupt source. KBI pin polarity can be controlled independently. Each KBI pin when enabled will automatically configure the appropriate pullup/pulldown device based on polarity.

# 9.8 Registers

The following registers control and monitor operation of the KBI module:

- KBSCR (keyboard interrupt status and control register)

- KBIER (keyboard interrupt enable register)

- KBIPR (keyboard interrupt polarity register)

# 9.8.1 Keyboard Status and Control Register (KBSCR)

Features of the KBSCR:

- Flags keyboard interrupt requests

- Acknowledges keyboard interrupt requests

- Masks keyboard interrupt requests

- Controls keyboard interrupt triggering sensitivity

|        | Bit 7 | 6               | 5 | 4 | 3    | 2    | 1       | Bit 0 |  |  |

|--------|-------|-----------------|---|---|------|------|---------|-------|--|--|

| Read:  | 0     | 0               | 0 | 0 | KEYF | 0    | IMASKK  | MODEK |  |  |

| Write: |       |                 |   |   |      | ACKK | INAGINI |       |  |  |

| Reset: | 0     | 0               | 0 | 0 | 0    | 0    | 0       | 0     |  |  |

|        |       | = Unimplemented |   |   |      |      |         |       |  |  |

#### Figure 9-3. Keyboard Status and Control Register (KBSCR)

#### Bits 7–4 — Not used

KEYF — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending.

- 1 = Keyboard interrupt pending

- 0 = No keyboard interrupt pending

#### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the KBI request. ACKK always reads 0.

#### IMASKK— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the KBI latch from generating interrupt requests.

- 1 = Keyboard interrupt requests disabled

- 0 = Keyboard interrupt requests enabled

#### MODEK — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins.

- 1 = Keyboard interrupt requests on edge and level

- 0 = Keyboard interrupt requests on edge only

#### Oscillator (OSC) Module

PTB[0:7]: Not available on 8-pin devices

# Figure 11-1. Block Diagram Highlighting OSC Block and Pins

# **11.3.1 Internal Signal Definitions**

The following signals and clocks are used in the functional description and figures of the OSC module.

#### 11.3.1.1 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and disables the XTAL oscillator circuit, the RC oscillator, or the internal oscillator in stop mode. OSCENINSTOP in the configuration register can be used to override this signal.

# 11.3.1.2 XTAL Oscillator Clock (XTALCLK)

XTALCLK is the XTAL oscillator output signal. It runs at the full speed of the crystal ( $f_{XCLK}$ ) and comes directly from the crystal oscillator circuit. Figure 11-2 shows only the logical relation of XTALCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of XTALCLK is unknown and may depend on the crystal and other external factors. The frequency of XTALCLK can be unstable at start up.

# 11.3.1.3 RC Oscillator Clock (RCCLK)

RCCLK is the RC oscillator output signal. Its frequency is directly proportional to the time constant of the external R ( $R_{EXT}$ ) and internal C. Figure 11-3 shows only the logical relation of RCCLK to OSC1 and may not represent the actual circuitry.

# 11.3.1.4 Internal Oscillator Clock (INTCLK)

INTCLK is the internal oscillator output signal. INTCLK is software selectable to be nominally 12.8 MHz, 8.0 MHz, or 4.0 MHz. INTCLK can be digitally adjusted using the oscillator trimming feature of the OSCTRIM register (see 11.3.2.1 Internal Oscillator Trimming).

#### 11.3.1.5 Bus Clock Times 4 (BUSCLKX4)

BUSCLKX4 is the same frequency as the input clock (XTALCLK, RCCLK, or INTCLK). This signal is driven to the SIM module and is used during recovery from reset and stop and is the clock source for the COP module.

# 11.3.1.6 Bus Clock Times 2 (BUSCLKX2)

The frequency of this signal is equal to half of the BUSCLKX4. This signal is driven to the SIM for generation of the bus clocks used by the CPU and other modules on the MCU. BUSCLKX2 will be divided by two in the SIM. The internal bus frequency is one fourth of the XTALCLK, RCCLK, or INTCLK frequency.

# 11.3.2 Internal Oscillator

The internal oscillator circuit is designed for use with no external components to provide a clock source with a tolerance of less than  $\pm 25\%$  untrimmed. An 8-bit register (OSCTRIM) allows the digital adjustment to a tolerance of ACC<sub>INT</sub>. See the oscillator characteristics in the Electrical section of this data sheet.

The internal oscillator is capable of generating clocks of 12.8 MHz, 8.0 MHz, or 4.0 MHz (INTCLK) resulting in a bus frequency (INTCLK divided by 4) of 3.2 MHz, 2.0 MHz, or 1.0 MHz respectively. The bus clock is software selectable and defaults to the 3.2-MHz bus out of reset. Users can increase the bus frequency based on the voltage range of their application.

Figure 11-3 shows how BUSCLKX4 is derived from INTCLK and OSC2 can output BUSCLKX4 by setting OSC2EN.

#### 11.3.2.1 Internal Oscillator Trimming

OSCTRIM allows a clock period adjustment of +127 and -128 steps. Increasing the OSCTRIM value increases the clock period, which decreases the clock frequency. Trimming allows the internal clock frequency to be fine tuned to the target frequency.

All devices are factory programmed with trim values that are stored in FLASH memory at locations \$FFC0 and \$FFC1. The trim value is **not** automatically loaded into the OSCTRIM register. User software must

#### ECFS1:ECFS0 — External Crystal Frequency Select Bits

These read/write bits enable the specific amplifier for the crystal frequency range. Refer to oscillator characteristics table in the Electricals section for information on maximum external clock frequency versus supply voltage.

| ECFS1 | ECFS0 | External Crystal Frequency |

|-------|-------|----------------------------|

| 0     | 0     | 8 MHz – 32 MHz             |

| 0     | 1     | 1 MHz – 8 MHz              |

| 1     | 0     | 32 kHz – 100 kHz           |

| 1     | 1     | Reserved                   |

#### ECGON — External Clock Generator On Bit

This read/write bit enables the OSC1 pin as the clock input to the MCU, so that the switching process can be initiated. This bit is cleared by reset. This bit is ignored in monitor mode with the internal oscillator bypassed.

- 1 = External clock enabled

- 0 = External clock disabled

#### ECGST — External Clock Status Bit

This read-only bit indicates whether an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

#### 11.8.2 Oscillator Trim Register (OSCTRIM)

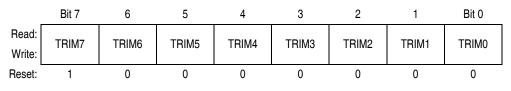

Figure 11-5. Oscillator Trim Register (OSCTRIM)

#### TRIM7–TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the internal capacitance used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed oscillator period. The oscillator period is based on the oscillator frequency selected by the ICFS bits in OSCSC.

Applications using the internal oscillator should copy the internal oscillator trim value at location \$FFC0 or \$FFC1 into this register to trim the clock source.

System Integration Module (SIM)

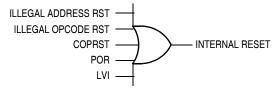

# 13.4.2 Active Resets from Internal Sources

The RST pin is initially setup as a general-purpose input after a POR. Setting the RSTEN bit in the CONFIG2 register enables the pin for the reset function. This section assumes the RSTEN bit is set when describing activity on the RST pin.

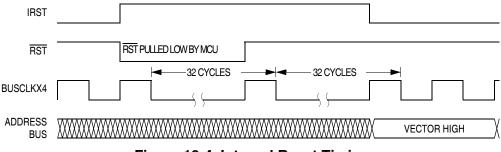

**NOTE** For POR and LVI resets, the SIM cycles through 4096 BUSCLKX4 cycles. The internal reset signal then follows the sequence from the falling edge of RST shown in Figure 13-4.

The COP reset is asynchronous to the bus clock.

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

All internal reset sources actively pull the RST pin low for 32 BUSCLKX4 cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (see Figure 13-4). An internal reset can be caused by an illegal address, illegal opcode, COP time out, LVI, or POR (see Figure 13-5).

Figure 13-4. Internal Reset Timing

Figure 13-5. Sources of Internal Reset

| Reset Recovery Type | Actual Number of Cycles |  |  |  |

|---------------------|-------------------------|--|--|--|

| POR/LVI             | 4163 (4096 + 64 + 3)    |  |  |  |

| All others          | 67 (64 + 3)             |  |  |  |

#### System Integration Module (SIM)

#### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

#### 13.6.4 Break Interrupts

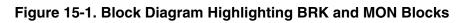

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

# 13.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

# 13.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

# 13.7.1 Wait Mode

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

| ADDRESS BUS | WAIT ADDR X WAIT ADD |  | DR + 1 | SAME  |      | SAME |      |

|-------------|----------------------|--|--------|-------|------|------|------|

| DATA BUS    | PREVIOUS DATA        |  |        | ODE X | SAME |      | SAME |

| R/W         |                      |  | /      |       |      |      |      |

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

#### Figure 13-14. Wait Mode Entry Timing

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred.

The value in the TIM channel registers determines the pulse width of the PWM output. The pulse width of an 8-bit PWM signal is variable in 256 increments. Writing \$0080 (128) to the TIM channel registers produces a duty cycle of 128/256 or 50%.

#### 14.3.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 14.3.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written to the timer channel (TCHxH:TCHxL).

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- When changing to a longer pulse width, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

#### 14.3.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function, and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin, TCH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active

The following TIM sources can generate interrupt requests:

- TIM overflow flag (TOF) The TOF bit is set when the counter reaches the modulo value programmed in the TIM counter modulo registers. The TIM overflow interrupt enable bit, TOIE, enables TIM overflow interrupt requests. TOF and TOIE are in the TSC register.

- TIM channel flags (CH1F:CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIM interrupt requests are controlled by the channel x interrupt enable bit, CHxIE. Channel x TIM interrupt requests are enabled when CHxIE =1. CHxF and CHxIE are in the TSCx register.

# 14.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

# 14.5.1 Wait Mode

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

# 14.5.2 Stop Mode

The TIM module is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions. TIM operation resumes after an external interrupt. If stop mode is exited by reset, the TIM is reset.

# 14.6 TIM During Break Interrupts

A break interrupt stops the counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

# Development Support

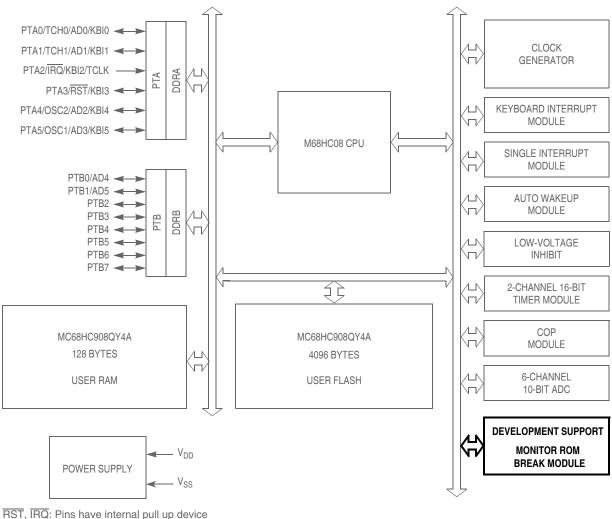

All port pins have programmable pull up device PTA[0:5]: Higher current sink and source capability PTB[0:7]: Not available on 8-pin devices

#### Monitor Module (MON)

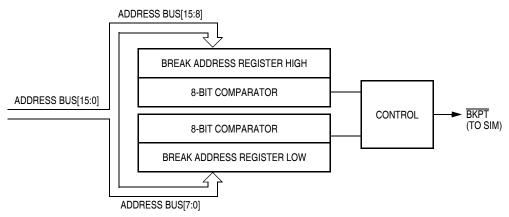

Figure 15-9. Simplified Monitor Mode Entry Flowchart

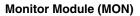

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 9600 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (3.2 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires V<sub>TST</sub> on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- IRQ = V<sub>TST</sub>

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- IRQ = V<sub>DD</sub> (this can be implemented through the internal IRQ pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- $\overline{IRQ} = V_{SS}$  (internal oscillator is selected, no external clock required)

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

Once out of reset, the MCU waits for the host to send eight security bytes (see 15.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive 0s) to the host, indicating that it is ready to receive a command.

Ordering Information and Mechanical Specifications

Case 968 page 3 of 3

**Mechanical Drawings**

Case 648 page 3 of 3

# A.2.5 Keyboard Interface Module (KBI) Functionality

The KBI module for the QYxA has the added capability of:

- Triggering a KBI interrupt on the rising or falling edge of an input while the QYx Classic has the capability of triggering on falling edges only.

- A new register (Keyboard Interrupt Polarity Register) determines the polarity of KBI and the default state of this register configures the QYxA for triggering on falling edges to be compatible with QYx Classic.

- The QYxA now has pull down resistors for the input pins that are configured for rising edge operation.

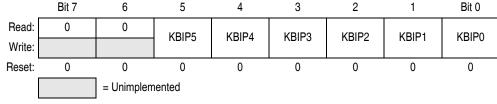

Figure A-6. Keyboard Interrupt Polarity Register (KBIPR)

The KBIPR allows the selection of polarity, if any of these bits are set the corresponding interrupt pin will be configured for rising edge and a pulldown resistor will be added to the pin.

# A.2.6 On-Chip Routine Enhancements

Enhancements have been made to the on-chip routines that are used for FLASH as EEPROM. Refer to AN2346 for information about using FLASH as EEPROM.

- A new mass erase routine requires a valid FLASH address loaded into the H:X register to perform an erase. This added step helps ensure that the erase routine is not inadvertently used to cause an unwanted erase. Also, on-chip FLASH programming routine ERARNGE variable CTRLBYT requires \$00 for page erase and \$40 for mass erase. The entire control byte must be set for proper operation.

- Separate routines will allow easy access to perform software SCI (Serial Communications Interface). For information on how to use on-chip FLASH programming routines refer to AN2635.

- Finally, there is improved security and robustness. The latest Monitor ROM implements updated security checks to make the program memory more secure.