Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qy4amdter |

**List of Chapters**

## Chapter 6 Computer Operating Properly (COP)

| 6.1            | Introduction                 | 61        |

|----------------|------------------------------|-----------|

| 6.2            | Functional Description       | 61        |

| 6.3            | I/O Signals                  | 62        |

| 6.3.1          | BUSCLKX4                     |           |

| 6.3.2          | STOP Instruction             |           |

| 6.3.3          | COPCTL Write                 |           |

| 6.3.4          | Power-On Reset.              |           |

| 6.3.5          | Internal Reset               |           |

| 6.3.6<br>6.3.7 | COPD (COP Disable)           |           |

| 6.4            | Interrupts                   |           |

|                | ·                            |           |

| 6.5            | Monitor Mode                 |           |

| 6.6            | Low-Power Modes              |           |

| 6.6.1<br>6.6.2 | Wait Mode                    |           |

|                | Stop Mode                    |           |

| 6.7            | COP Module During Break Mode |           |

| 6.8            | Register                     | 63        |

|                | Chapter 7                    |           |

|                | Central Processor Unit (CPU) |           |

| 7.1            | Introduction                 | 65        |

| 7.2            | Features                     |           |

| 7.3            | CPU Registers                |           |

| 7.3.1          | Accumulator                  |           |

| 7.3.2          | Index Register               |           |

| 7.3.3          | Stack Pointer                |           |

| 7.3.4          | Program Counter              |           |

| 7.3.5          | Condition Code Register      | 68        |

| 7.4            | Arithmetic/Logic Unit (ALU)  | <b>69</b> |

| 7.5            | Low-Power Modes              | <b>69</b> |

| 7.5.1          | Wait Mode                    |           |

| 7.5.2          | Stop Mode                    |           |

| 7.6            | CPU During Break Interrupts  | <b>69</b> |

| 7.7            | Instruction Set Summary      |           |

| 7.8            | Opcode Map                   | 75        |

|                | Chanter 0                    |           |

|                | Chapter 8                    |           |

| 0.4            | External Interrupt (IRQ)     |           |

| 8.1            | Introduction                 |           |

| 8.2            | Features                     |           |

| 8.3            | Functional Description       |           |

| 8.3.1          | MODE = 1                     |           |

| 8.3.2          | MODE = 0                     | 79        |

10.4

10.5 10.5.1

10.5.2

10.6

#### **Table of Contents** 8.4 8.5 8.5.1 8.5.2 8.6 8.7 8.7.1 8.8 **Chapter 9 Keyboard Interrupt Module (KBI)** 9.1 Introduction 9.2 9.3 9.3.1 9.3.1.1 9.3.1.2 9.3.2 9.4 9.5 9.5.1 9.5.2 9.6 9.7 9.7.1 9.8 9.8.1 Keyboard Status and Control Register (KBSCR)......87 9.8.2 Keyboard Interrupt Enable Register (KBIER)......88 9.8.3 Chapter 10 Low-Voltage Inhibit (LVI) 10.1 10.2 10.3 10.3.1 10.3.2 Forced Reset Operation......90 10.3.3 10.3.4

#### **General Description**

- On-chip random-access memory (RAM)

- 2-channel, 16-bit timer interface (TIM) module

- 6-channel, 10-bit analog-to-digital converter (ADC) with internal bandgap reference channel (ADC10)

- Up to 13 bidirectional input/output (I/O) lines and one input only:

- Six shared with KBI

- Six shared with ADC

- Two shared with TIM

- One input only shared with IRQ

- High current sink/source capability on all port pins

- Selectable pullups on all ports, selectable on an individual bit basis

- Three-state ability on all port pins

- 6-bit keyboard interrupt with wakeup feature (KBI)

- Programmable for rising/falling or high/low level detect

- Low-voltage inhibit (LVI) module features:

- Software selectable trip point

- System protection features:

- Computer operating properly (COP) watchdog

- Low-voltage detection with reset

- Illegal opcode detection with reset

- Illegal address detection with reset

- External asynchronous interrupt pin with internal pullup (IRQ) shared with general-purpose input pin

- Master asynchronous reset pin with internal pullup (RST) shared with general-purpose input/output (I/O) pin

- Memory mapped I/O registers

- Power saving stop and wait modes

- MC68HC908QY4A, MC68HC908QY2A and MC68HC908QY1A are available in these packages:

- 16-pin plastic dual in-line package (PDIP)

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline packages (TSSOP)

- MC68HC908QT4A, MC68HC908QT2A and MC68HC908QT1A are available in these packages:

- 8-pin PDIP

- 8-pin SOIC

- 8-pin dual flat no lead (DFN) package

## Features of the CPU08 include the following:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

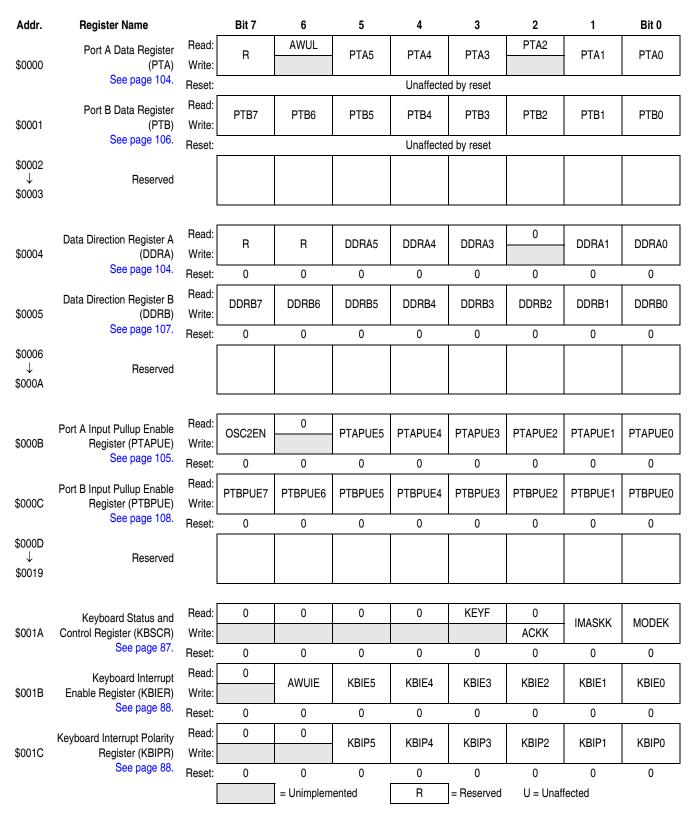

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 5)

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

## 2.6.3 FLASH Mass Erase Operation

Use the following procedure to erase the entire FLASH memory to read as a 1:

- 1. Set both the ERASE bit and the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH address<sup>(1)</sup> within the FLASH memory address range.

- Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>MErase</sub>.

- 7. Clear the ERASE and MASS bits.

#### NOTE

Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF).

- 8. Wait for a time, t<sub>NVHI</sub>.

- 9. Clear the HVEN bit.

- 10. After time, t<sub>RCV</sub>, the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, other unrelated operations may occur between the steps.

#### CAUTION

A mass erase will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

## 2.6.4 FLASH Program Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0, or \$XXE0. Use the following step-by-step procedure to program a row of FLASH memory

Figure 2-4 shows a flowchart of the programming algorithm.

#### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte which is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range desired.

- 4. Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

When in monitor mode, with security sequence failed (see 15.3.2 Security), write to the FLASH block protect register instead of any FLASH address.

21 ADCK + 3 bus clock + 5  $\mu$ s

19 ADCK

41 ADCK + 3 bus clock

41 ADCK + 3 bus clock + 5  $\mu$ s

39 ADCK

Upon reset or when a conversion is otherwise aborted, the ADC10 module will enter a low power, inactive state. In this state, all internal clocks and references are disabled. This state is entered asynchronously and immediately upon aborting of a conversion.

#### 3.3.3.4 Total Conversion Time

Single or 1st continuous

Single or 1st continuous

Single or 1st continuous

Subsequent continuous ( $f_{Bus} \ge f_{ADCK}$ )

10-Bit Mode (long sample — ADLSMP = 1):

Subsequent continuous ( $f_{Bus} \ge f_{ADCK}$ )

The total conversion time depends on many factors such as sample time, bus frequency, whether ACLKEN is set, and synchronization time. The total conversion time is summarized in Table 3-1.

| Conversion Mode                                  | ACLKEN | Maximum Conversion Time      |

|--------------------------------------------------|--------|------------------------------|

| 8-Bit Mode (short sample — ADLSMP = 0):          |        |                              |

| Single or 1st continuous                         | 0      | 18 ADCK + 3 bus clock        |

| Single or 1st continuous                         | 1      | 18 ADCK + 3 bus clock + 5 μs |

| Subsequent continuous ( $f_{Bus} \ge f_{ADCK}$ ) | X      | 16 ADCK                      |

| 8-Bit Mode (long sample — ADLSMP = 1):           |        |                              |

| Single or 1st continuous                         | 0      | 38 ADCK + 3 bus clock        |

| Single or 1st continuous                         | 1      | 38 ADCK + 3 bus clock + 5 μs |

| Subsequent continuous ( $f_{Bus} \ge f_{ADCK}$ ) | X      | 36 ADCK                      |

| 10-Bit Mode (short sample — ADLSMP = 0):         |        |                              |

| Single or 1st continuous                         | 0      | 21 ADCK + 3 bus clock        |

1

Χ

0

Χ

**Table 3-1. Total Conversion Time versus Control Conditions**

The maximum total conversion time for a single conversion or the first conversion in continuous conversion mode is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by the ADICLK and ACLKEN bits, and the divide ratio is specified by the ADIV bits. For example, if the alternate clock source is 16 MHz and is selected as the input clock source, the input clock divide-by-8 ratio is selected and the bus frequency is 4 MHz, then the conversion time for a single 10-bit conversion is:

Maximum Conversion time =

$$\frac{21 \text{ ADCK cycles}}{16 \text{ MHz/8}} + \frac{3 \text{ bus cycles}}{4 \text{ MHz}} = 11.25 \,\mu\text{s}$$

Number of bus cycles =  $11.25 \mu s \times 4 MHz = 45 cycles$

#### NOTE

The ADCK frequency must be between  $f_{ADCK}$  minimum and  $f_{ADCK}$  maximum to meet A/D specifications.

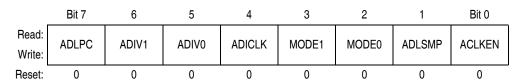

## ADIV[1:0] — ADC10 Clock Divider Bits

ADIV1 and ADIV0 select the divide ratio used by the ADC10 to generate the internal clock ADCK. Table 3-3 shows the available clock configurations.

Table 3-3. ADC10 Clock Divide Ratio

| ADIV1 | ADIV0 | Divide Ratio (ADIV) | Clock Rate      |

|-------|-------|---------------------|-----------------|

| 0     | 0     | 1                   | Input clock ÷ 1 |

| 0     | 1     | 2                   | Input clock ÷ 2 |

| 1     | 0     | 4                   | Input clock ÷ 4 |

| 1     | 1     | 8                   | Input clock ÷ 8 |

## ADICLK — Input Clock Select Bit

If ACLKEN is clear, ADICLK selects either the bus clock or an alternate clock source as the input clock source to generate the internal clock ADCK. If the alternate clock source is less than the minimum clock speed, use the internally-generated bus clock as the clock source. As long as the internal clock ADCK, which is equal to the selected input clock divided by ADIV, is at a frequency (f<sub>ADCK</sub>) between the minimum and maximum clock speeds (considering ALPC), correct operation can be guaranteed.

- 1 = The internal bus clock is selected as the input clock source

- 0 = The alternate clock source IS SELECTED

## MODE[1:0] — 10- or 8-Bit or Hardware Triggered Mode Selection

These bits select 10- or 8-bit operation. The successive approximation converter generates a result that is rounded to 8- or 10-bit value based on the mode selection. This rounding process sets the transfer function to transition at the midpoint between the ideal code voltages, causing a quantization error of  $\pm$  1/2LSB.

Reset returns 8-bit mode.

00 = 8-bit, right-justified, ADSCR software triggered mode enabled

01 = 10-bit, right-justified, ADSCR software triggered mode enabled

10 = Reserved

11 = 10-bit, right-justified, hardware triggered mode enabled

#### **ADLSMP** — Long Sample Time Configuration

This bit configures the sample time of the ADC10 to either 3.5 or 23.5 ADCK clock cycles. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption in continuous conversion mode if high conversion rates are not required.

- 1 = Long sample time (23.5 cycles)

- 0 = Short sample time (3.5 cycles)

## **ACLKEN** — Asynchronous Clock Source Enable

This bit enables the asynchronous clock source as the input clock to generate the internal clock ADCK, and allows operation in stop mode. The asynchronous clock source will operate between 1 MHz and 2 MHz if ADLPC is clear, and between 0.5 MHz and 1 MHz if ADLPC is set.

- 1 = The asynchronous clock is selected as the input clock source (the clock generator is only enabled during the conversion)

- 0 = ADICLK specifies the input clock source and conversions will not continue in stop mode

# Chapter 9 Keyboard Interrupt Module (KBI)

## 9.1 Introduction

The keyboard interrupt module (KBI) provides independently maskable external interrupts.

The KBI shares its pins with general-purpose input/output (I/O) port pins. See Figure 9-1 for port location of these shared pins.

## 9.2 Features

Features of the keyboard interrupt module include:

- Keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Programmable edge-only or edge and level interrupt sensitivity

- Edge sensitivity programmable for rising or falling edge

- Level sensitivity programmable for high or low level

- Pullup or pulldown device automatically enabled based on the polarity of edge or level detect

- Exit from low-power modes

## 9.3 Functional Description

The keyboard interrupt module controls the enabling/disabling of interrupt functions on the KBI pins. These pins can be enabled/disabled independently of each other. See Figure 9-2.

## 9.3.1 Keyboard Operation

Writing to the KBIEx bits in the keyboard interrupt enable register (KBIER) independently enables or disables each KBI pin. The polarity of the keyboard interrupt is controlled using the KBIPx bits in the keyboard interrupt polarity register (KBIPR). Edge-only or edge and level sensitivity is controlled using the MODEK bit in the keyboard status and control register (KBISCR).

Enabling a keyboard interrupt pin also enables its internal pullup or pulldown device based on the polarity enabled. On falling edge or low level detection, a pullup device is configured. On rising edge or high level detection, a pulldown device is configured.

The keyboard interrupt latch is set when one or more enabled keyboard interrupt inputs are asserted.

- If the keyboard interrupt sensitivity is edge-only, for KBIPx = 0, a falling (for KBIPx = 1, a rising) edge on a keyboard interrupt input does not latch an interrupt request if another enabled keyboard pin is already asserted. To prevent losing an interrupt request on one input because another input remains asserted, software can disable the latter input while it is asserted.

- If the keyboard interrupt is edge and level sensitive, an interrupt request is present as long as any enabled keyboard interrupt input is asserted.

Oscillator (OSC) Module

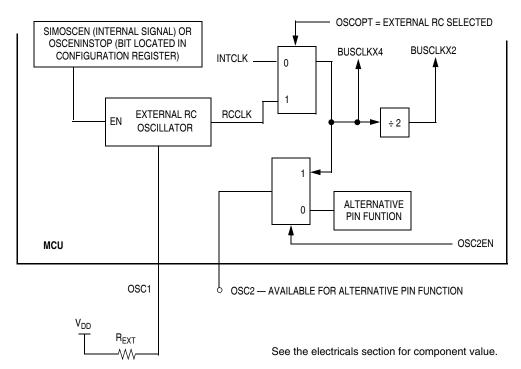

#### 11.3.5 RC Oscillator

The RC oscillator circuit is designed for use with an external resistor ( $R_{EXT}$ ) to provide a clock source with a tolerance within 25% of the expected frequency. See Figure 11-3.

The capacitor (C) for the RC oscillator is internal to the MCU. The  $R_{EXT}$  value must have a tolerance of 1% or less to minimize its effect on the frequency.

In this configuration, the OSC2 pin can be used as general-purpose input/output (I/O) port pins or other alternative pin function. The OSC2EN bit can be set to enable the OSC2 output function on the pin. Enabling the OSC2 output can affect the external RC oscillator frequency, f<sub>BCCLK</sub>.

Figure 11-3. RC Oscillator External Connections

## 11.4 Interrupts

There are no interrupts associated with the OSC module.

#### 11.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### **11.5.1 Wait Mode**

The OSC module remains active in wait mode.

## 11.5.2 Stop Mode

The OSC module can be configured to remain active in stop mode by setting OSCENINSTOP located in a configuration register.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

## ECFS1:ECFS0 — External Crystal Frequency Select Bits

These read/write bits enable the specific amplifier for the crystal frequency range. Refer to oscillator characteristics table in the Electricals section for information on maximum external clock frequency versus supply voltage.

| ECFS1 | ECFS0 | External Crystal Frequency |

|-------|-------|----------------------------|

| 0     | 0     | 8 MHz – 32 MHz             |

| 0     | 1     | 1 MHz – 8 MHz              |

| 1     | 0     | 32 kHz – 100 kHz           |

| 1     | 1     | Reserved                   |

#### ECGON — External Clock Generator On Bit

This read/write bit enables the OSC1 pin as the clock input to the MCU, so that the switching process can be initiated. This bit is cleared by reset. This bit is ignored in monitor mode with the internal oscillator bypassed.

- 1 = External clock enabled

- 0 = External clock disabled

#### **ECGST** — External Clock Status Bit

This read-only bit indicates whether an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

## 11.8.2 Oscillator Trim Register (OSCTRIM)

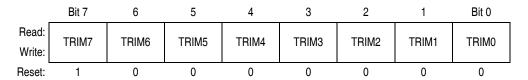

Figure 11-5. Oscillator Trim Register (OSCTRIM)

## TRIM7-TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the internal capacitance used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed oscillator period. The oscillator period is based on the oscillator frequency selected by the ICFS bits in OSCSC.

Applications using the internal oscillator should copy the internal oscillator trim value at location \$FFC0 or \$FFC1 into this register to trim the clock source.

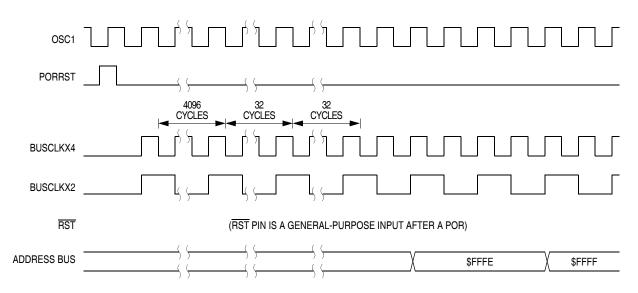

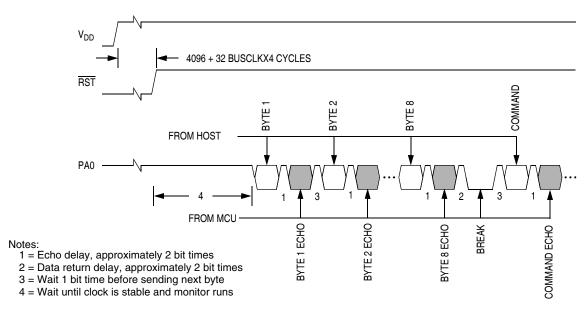

## 13.4.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power on has occurred. The SIM counter counts out 4096 BUSCLKX4 cycles. Sixty-four BUSCLKX4 cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables the oscillator to drive BUSCLKX4.

- Internal clocks to the CPU and modules are held inactive for 4096 BUSCLKX4 cycles to allow stabilization of the oscillator.

- The POR bit of the SIM reset status register (SRSR) is set.

## See Figure 13-6.

Figure 13-6. POR Recovery

#### 13.4.2.2 Computer Operating Properly (COP) Reset

An input to the SIM is reserved for the COP reset signal. The overflow of the COP counter causes an internal reset and sets the COP bit in the SIM reset status register (SRSR). The SIM actively pulls down the RST pin for all internal reset sources.

To prevent a COP module time out, write any value to location \$FFFF. Writing to location \$FFFF clears the COP counter and stages 12–5 of the SIM counter. The SIM counter output, which occurs at least every 4080 BUSCLKX4 cycles, drives the COP counter. The COP should be serviced as soon as possible out of reset to guarantee the maximum amount of time before the first time out.

The COP module is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

#### 13.4.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

#### **System Integration Module (SIM)**

If the stop enable bit, STOP, in the mask option register is 0, the SIM treats the STOP instruction as an illegal opcode and causes an illegal opcode reset. The SIM actively pulls down the  $\overline{\text{RST}}$  pin for all internal reset sources.

## 13.4.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset. The SIM actively pulls down the RST pin for all internal reset sources. See Figure 2-1. Memory Map for memory ranges.

### 13.4.2.5 Low-Voltage Inhibit (LVI) Reset

The LVI asserts its output to the SIM when the  $V_{DD}$  voltage falls to the LVI trip voltage  $V_{TRIPF}$ . The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin ( $\overline{RST}$ ) is held low while the SIM counter counts out 4096 BUSCLKX4 cycles after  $V_{DD}$  rises above  $V_{TRIPR}$ . Sixty-four BUSCLKX4 cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the ( $\overline{RST}$ ) pin for all internal reset sources.

#### 13.5 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as a prescaler for the computer operating properly module (COP). The SIM counter uses 12 stages for counting, followed by a 13th stage that triggers a reset of SIM counters and supplies the clock for the COP module. The SIM counter is clocked by the falling edge of BUSCLKX4.

## 13.5.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit asserts the signal PORRST. Once the SIM is initialized, it enables the oscillator to drive the bus clock state machine.

## 13.5.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt, break, or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the configuration register 1 (CONFIG1). If the SSREC bit is a 1, then the stop recovery is reduced from the normal delay of 4096 BUSCLKX4 cycles down to 32 BUSCLKX4 cycles. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode. External crystal applications should use the full stop recovery time, that is, with SSREC cleared in the configuration register 1 (CONFIG1).

### 13.5.3 SIM Counter and Reset States

External reset has no effect on the SIM counter (see 13.7.2 Stop Mode for details.) The SIM counter is free-running after all reset states. See 13.4.2 Active Resets from Internal Sources for counter control and internal reset recovery sequences.

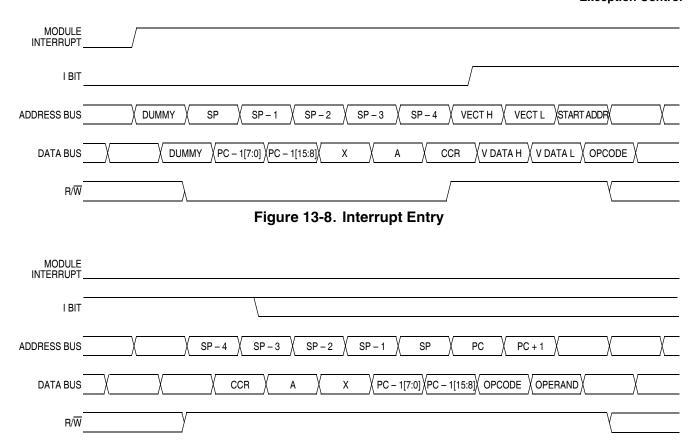

Figure 13-9. Interrupt Recovery

Figure 13-10. Interrupt Recognition Example

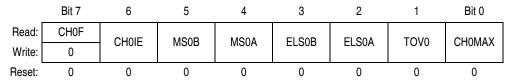

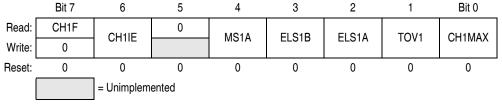

## 14.8.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- · Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Figure 14-9. TIM Channel 0 Status and Control Register (TSC0)

Figure 14-10. TIM Channel 1 Status and Control Register (TSC1)

#### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the counter registers matches the value in the TIM channel x registers.

Clear CHxF by reading the TSCx register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

## CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM interrupt service requests on channel x.

- 1 = Channel x interrupt requests enabled

- 0 = Channel x interrupt requests disabled

#### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TSC0.

The break interrupt timing is:

- When a break address is placed at the address of the instruction opcode, the instruction is not executed until after completion of the break interrupt routine.

- When a break address is placed at an address of an instruction operand, the instruction is executed before the break interrupt.

- When software writes a 1 to the BRKA bit, the break interrupt occurs just before the next instruction is executed.

By updating a break address and clearing the BRKA bit in a break interrupt routine, a break interrupt can be generated continuously.

#### **CAUTION**

A break address should be placed at the address of the instruction opcode. When software does not change the break address and clears the BRKA bit in the first break interrupt routine, the next break interrupt will not be generated after exiting the interrupt routine even when the internal address bus matches the value written in the break address registers.

## 15.2.1.1 Flag Protection During Break Interrupts

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register and the **Break Interrupts** subsection for each module.

## 15.2.1.2 TIM During Break Interrupts

A break interrupt stops the timer counter.

#### 15.2.1.3 COP During Break Interrupts

The COP is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

#### 15.2.2 Break Module Registers

These registers control and monitor operation of the break module:

- Break status and control register (BRKSCR)

- Break address register high (BRKH)

- Break address register low (BRKL)

- Break status register (BSR)

- Break flag control register (BFCR)

#### **Development Support**

## 15.3.2 Security

A security feature discourages unauthorized reading of FLASH locations while in monitor mode. The host can bypass the security feature at monitor mode entry by sending eight security bytes that match the bytes at locations \$FFF6\_\$FFFD. Locations \$FFF6\_\$FFFD contain user-defined data.

#### NOTE

Do not leave locations \$FFF6-\$FFFD blank. For security reasons, program locations \$FFF6-\$FFFD even if they are not used for vectors.

During monitor mode entry, the MCU waits after the power-on reset for the host to send the eight security bytes on pin PTA0. If the received bytes match those at locations \$FFF6—\$FFFD, the host bypasses the security feature and can read all FLASH locations and execute code from FLASH. Security remains bypassed until a power-on reset occurs. If the reset was not a power-on reset, security remains bypassed and security code entry is not required. See Figure 15-18.

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6—\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a FLASH location returns an invalid value and trying to execute code from FLASH causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

#### NOTE

The MCU does not transmit a break character until after the host sends the eight security bytes.

Figure 15-18. Monitor Mode Entry Timing

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$80 is set. If it is, then the correct security code has been entered and FLASH can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the FLASH module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

MC68HC908QYA/QTA Family Data Sheet, Rev. 3

## 16.11 Oscillator Characteristics

| Characteristic                                                                                                                                                                                                                                                      | Symbol                                                                      | Min                        | Тур                                                      | Max                  | Unit                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|----------------------------------------------------------|----------------------|----------------------------------|

| Internal oscillator frequency <sup>(1)</sup> ICFS1:ICFS0 = 00 ICFS1:ICFS0 = 01 ICFS1:ICFS0 = 10 (not allowed if V <sub>DD</sub> <2.7V)                                                                                                                              | f <sub>INTCLK</sub>                                                         |                            | 4<br>8<br>12.8                                           | _<br>_<br>_          | MHz                              |

| Trim accuracy <sup>(2)(3)</sup>                                                                                                                                                                                                                                     | $\Delta_{TRIM\_ACC}$                                                        | _                          | ± 0.4                                                    | _                    | %                                |

| Deviation from trimmed Internal oscillator <sup>(3)(4)</sup> 4, 8, 12.8MHz, V <sub>DD</sub> ± 10%, 0 to 70°C 4, 8, 12.8MHz, V <sub>DD</sub> ± 10%, –40 to 125°C                                                                                                     | $\Delta_{INT\_TRIM}$                                                        | _<br>_                     | ± 2<br>—                                                 | —<br>±5              | %                                |

| External RC oscillator frequency, RCCLK (1)(3)                                                                                                                                                                                                                      | f <sub>RCCLK</sub>                                                          | 2                          | _                                                        | 10                   | MHz                              |

| External clock reference frequencyy $^{(1)(5)(6)}$<br>$V_{DD} \ge 4.5V$<br>$V_{DD} < 4.5V$                                                                                                                                                                          | foscxclk                                                                    | dc<br>dc                   | _                                                        | 32<br>16             | MHz                              |

| RC oscillator external resistor <sup>(3)</sup> $V_{DD} = 5 V$ $V_{DD} = 3 V$                                                                                                                                                                                        | R <sub>EXT</sub>                                                            |                            | See Figure 16-7<br>See Figure 16-8                       |                      | _                                |

| Crystal frequency, XTALCLK <sup>(1)(7)(8)</sup> ECFS1:ECFS0 = 00 ( $V_{DD} \ge 4.5 \text{ V}$ ) ECFS1:ECFS0 = 00 ECFS1:ECFS0 = 01 ECFS1:ECFS0 = 10                                                                                                                  | foscxclk                                                                    | 8<br>8<br>1<br>30          | _                                                        | 32<br>16<br>8<br>100 | MHz<br>MHz<br>MHz<br>kHz         |

| ECFS1:ECFS0 = 00 <sup>(9)</sup> Feedback bias resistor Crystal load capacitance <sup>(10)</sup> Crystal capacitors <sup>(10)</sup>                                                                                                                                  | R <sub>B</sub><br>C <sub>L</sub><br>C <sub>1</sub> ,C <sub>2</sub>          | _<br>_<br>_                | 1<br>20<br>(2 x C <sub>L</sub> ) – 5pF                   | _<br>_<br>_          | MΩ<br>pF<br>pF                   |

| ECFS1:ECFS0 = 01 <sup>(9)</sup> Crystal series damping resistor foscxclk = 1 MHz foscxclk = 4 MHz foscxclk = 8 MHz Feedback bias resistor Crystal load capacitance <sup>(10)</sup> Crystal capacitors <sup>(10)</sup> AWI I module internal BC oscillator frequency | R <sub>S</sub> R <sub>B</sub> C <sub>L</sub> C <sub>1</sub> ,C <sub>2</sub> | _<br>_<br>_<br>_<br>_<br>_ | 20<br>10<br>0<br>5<br>18<br>(2 x C <sub>L</sub> ) –10 pF | <br><br><br>         | kΩ<br>kΩ<br>kΩ<br>MΩ<br>pF<br>pF |

| AWU module internal RC oscillator frequency                                                                                                                                                                                                                         | f <sub>INTRC</sub>                                                          | _                          | 32                                                       |                      | KHZ                              |

- 1. Bus frequency,  $f_{\mbox{\scriptsize OP}}$ , is oscillator frequency divided by 4.

- 2. Factory trimmed to provided 12.8MHz accuracy requirement (± 5%, @25•C) for forced monitor mode communication. User should trim in-circuit to obtain the most accurate internal oscillator frequency for the application.

- 3. Values are based on characterization results, not tested in production.

- 4. Deviation values assumes trimming in target application @25•C and midpoint of voltage range, for example 5.0 V for 5 V ± 10% operation.

- 5. No more than 10% duty cycle deviation from 50%.

- 6. When external oscillator clock is greater than 1MHz, ECFS1:ECFS0 must be 00 or 01

- 7. Use fundamental mode only, do not use overtone crystals or overtone ceramic resonators

- 8. Due to variations in electrical properties of external components such as, ESR and Load Capacitance, operation above 16 MHz is not guaranteed for all crystals or ceramic resonators. Operation above 16 MHz requires that a Negative Resistance Margin (NRM) characterization and component optimization be performed by the crystal or ceramic resonator vendor for every different type of crystal or ceramic resonator which will be used. This characterization and optimization must be performed at the extremes of voltage and temperature which will be applied to the microcontroller in the application. The NRM must meet or exceed 10x the maximum ESR of the crystal or ceramic resonator for acceptable performance.

- 9. Do not use damping resistor when ECFS1:ECFS0 = 00 or 10

- 10. Consult crystal vendor data sheet.

Case 626 page 3 of 3

- The ADC that is on the QYxA can operate while the MCU is in stop mode allowing lower power operation. This also adds a lower noise environment for precise ADC results.

- Enabling an ADC channel no longer overrides the digital I/O function of the associated pin. To prevent the digital I/O from interfering with the ADC read of the pin, the data direction bit associated with the port pin must be set as input.

- Finally, the new ADC can be configured to select two different reference clock sources:

- The internal bus x 4

- An internal asynchronous source

The internal asynchronous clock source allows the ADC to be clocked for operation in stop mode.

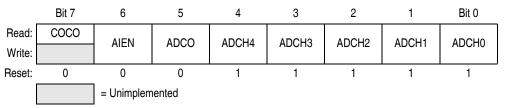

## A.2.1.1 Registers Affected

Figure A-1. ADC10 Status and Control Register (ADSCR)

The ADCHx bits can be used to select additional ADC channels or bandgap measurement.

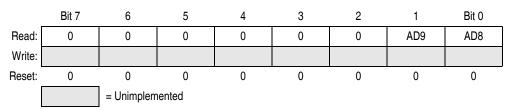

Figure A-2. ADC10 Data Register High (ADRH), 10-Bit Mode

10-bit ADC uses the new ADRH register for the upper 2 bits.

Figure A-3. ADC10 Clock Register (ADCLK)

A long sample time option has been added to conserve power at the expense of longer conversion times. This option is selected using the new ADLSMP bit in the ADCLK register. (The bit location was previously reserved.)

The ADC will now run in stop mode if the ACLKEN bit is set to enable the asynchronous clock inside the ADC module. Utilizing stop mode for an ADC conversion gives the quietest operating mode to get extremely accurate ADC readings. (This bit location now used by ACLKEN was reserved — it always read as a 0 and writes to that location had no affect.)

MC68HC908QYA/QTA Family Data Sheet, Rev. 3